# MONOLITHIC LAMP DIMMER

- HIGH EFFICIENCY DUE TO PWM CONTROL AND POWER DMOS DRIVER

- LOAD CONNECTED TO GROUND

- CURRENT LIMITATION

- OVER AND UNDERVOLTAGE PROTECTION

- ON CHIP THERMAL PROTECTION

- LIMITED AND PROGRAMMABLE OUTPUT VOLTAGE SLEW RATE

- OPEN GROUND PROTECTION

- VERY LOW STANDBY POWER CONSUMP-TION

- LOAD DUMP PROTECTION

- MINIMIZED ELECTROMAGNETIC INTER-FERENCE

- WIDE CHOICE IN PWM FREQUENCY RANGE

- LOAD POWER LIMITATION

#### **MULTIPOWER BCD TECHNOLOGY**

#### **DESCRIPTION**

The L9830 high side driver is a monolithic integrated circuit realized with Multipower BCD mixed technology to drive resistive or inductive loads in PWM mode with one side connected to ground.

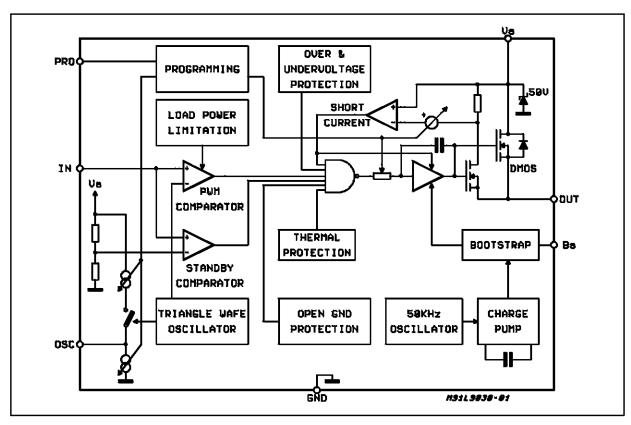

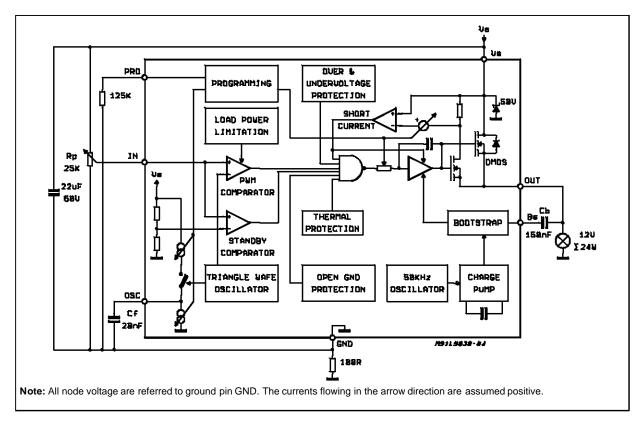

#### **BLOCK DIAGRAM**

November 1992 1/8

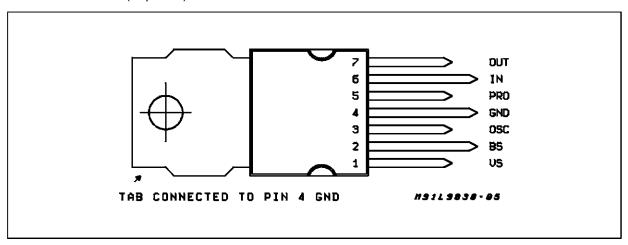

## **PIN CONNECTION** (Top view)

## **PIN FUNCTION**

| PIN | NAME | DESCRIPTION                                                                                                                                                                  |  |  |  |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | Vs   | Common supply connection also Drain of the power DMOS.                                                                                                                       |  |  |  |

| 2   | BS   | A capacitor connected between this pin and the Source of the power DMOS pin Out gives the possibility to bootstrap the gate driving voltage of the power DMOS.               |  |  |  |

| 3   | osc  | A capacitance CT connected between GND and this terminal determines the PWM switching frequency.                                                                             |  |  |  |

| 4   | GND  | Common ground connection.                                                                                                                                                    |  |  |  |

| 5   | PRO  | A resistor connected between this pin and GND provide the possibility to programming the output voltage slew rate, the PWM oscillator frequency and the short current value. |  |  |  |

| 6   | IN   | Analog input for controlling the PWM ratio, related to V <sub>S</sub> .                                                                                                      |  |  |  |

| 7   | OUT  | Source connection of the internal power DMOS.                                                                                                                                |  |  |  |

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                     | Value                            | Unit |

|------------------|-----------------------------------------------|----------------------------------|------|

| Vs               | Supply Voltage                                | 60                               | V    |

| V <sub>DS</sub>  | Drain Source Voltage                          | 60                               | V    |

| ViN              | Input Voltage                                 | -0.3V up to V <sub>S</sub> +0.3V |      |

| Is               | Supply Current                                | ±0.2                             | Α    |

| I <sub>OR</sub>  | Output Reverse Current                        | -2                               | Α    |

| P <sub>tot</sub> | Power Dissipation at T <sub>case</sub> ≤ 75°C | 37.5                             | W    |

| T <sub>amb</sub> | Operating Ambient Temperature Range           | -40 to +85                       | °C   |

| Tj               | Operating Junction Temperature Range          | -40 to 150                       | °C   |

| T <sub>stg</sub> | Storage Temperature                           | -65 to 150                       | °C   |

## THERMAL DATA

| Symbol                 | Description                      |     | Value | Unit |

|------------------------|----------------------------------|-----|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case | Max | 2     | °C/W |

# **ELECTRICAL CHARACTERISTICS** (6V $\leq$ V<sub>S</sub> $\leq$ 16V; -40°C $\leq$ T<sub>amb</sub> $\leq$ 85°C, unless otherwise specified)

| Symbol               | Parameter                                                                               | Test Condition                                                                                                 | Min.     | Тур.       | Max.                 | Unit         |

|----------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------|------------|----------------------|--------------|

| I <sub>qo</sub>      | Operating Quiescent Current                                                             | V <sub>IN</sub> = Vs                                                                                           |          |            |                      |              |

|                      | $I_{qo} = 11.3 \frac{V_S - 0.7V}{RP} + 0.67mA$                                          | $R_P \to \infty$ $R_P = 30K\Omega$                                                                             |          | 2.4<br>8.5 | 6<br>18              | mA<br>mA     |

| I <sub>qs</sub>      | Standby Current                                                                         | $ V_{IN} = 0 $ $ T_j \le 100^{\circ}C $                                                                        | 0        | 200        | 600                  | μΑ           |

| V <sub>INSB</sub>    | Input Standby High Threshold V <sub>IN</sub> /V <sub>S</sub>                            |                                                                                                                | 0.1      | 0.15       | 0.2                  |              |

| V <sub>INSBhys</sub> | Input Standby Hysteresis                                                                |                                                                                                                | -350     | -190       | -50                  | mV           |

| V <sub>INH</sub>     | Input High Threshold                                                                    | $f_0 \times t_{on} = 1  V_S \le VS_{LPL}$                                                                      | 0.95VS   |            | V <sub>S</sub> +0.3V |              |

| I <sub>IN</sub>      | Input Current                                                                           | $-0.3 \le V_{IN} \le V_{S} + 0.3V$                                                                             |          | 1          | 5                    | μΑ           |

| VSL                  | Low Supply Voltage Disable<br>High Threshold                                            |                                                                                                                | 5        | 5.5        | 6                    | V            |

| VS <sub>Lhys</sub>   | Low Supply Voltage Disable<br>Hysteresis                                                |                                                                                                                | -300     | -100       | -50                  | mV           |

| VS <sub>LPL</sub>    | Load Power Limitation Start<br>Supply Voltage                                           | $V_{IN} \ge V_{INH}$ , $f_{on} \cdot t_{on} = 0.96$                                                            | 12       | 13.0       | 17                   | V            |

| VS <sub>H</sub>      | High Supply Voltage Disable<br>High Threshold                                           |                                                                                                                | 16       | 17.8       | 20                   | V            |

| VS <sub>Hhys</sub>   | High Supply Voltage Disable<br>Hysteresis                                               |                                                                                                                | -350     | -190       | -50                  | mV           |

| VS <sub>LD</sub>     | Load Dump Supply Voltage<br>Threshold                                                   | I <sub>q</sub> = 50mA                                                                                          | 45       | 52         | 55                   | V            |

| I <sub>CLD</sub>     | Load Dump Clamping Current                                                              | VS = 60V                                                                                                       | 100      | 150        | 300                  | mA           |

| T <sub>ST</sub>      | Thermal Shutdown Temperature                                                            |                                                                                                                | 150      | 175        | 200                  | °C           |

| T <sub>SThys</sub>   | Thermal Shutdown Temperature Hysteresis                                                 |                                                                                                                | -50      | -40        | -30                  | °C           |

| K <sub>Ti</sub>      | Internal PWM Frequency Constant (without RP)                                            | $f_0 = K_{T/CT}$                                                                                               | 1000     | 2000       | 3000                 | Hznf         |

| K <sub>Te</sub>      | External PWM Frequency<br>Constant                                                      | $f_0 = \frac{1}{C_T R_P} K_{Te}$                                                                               | 0.220    | 0.250      | 0.350                |              |

|                      |                                                                                         | $30 \text{K}\Omega \le R_P \le 500 \text{K}\Omega$                                                             |          |            |                      |              |

| l <sub>osi</sub>     | Internal Short Current Limitation (without R <sub>P</sub> ) (4)                         | V <sub>S</sub> = 12V                                                                                           | 3        | 6          | 9                    | Α            |

| l <sub>ose</sub>     | External Programmable Short Current Limit $(30K\Omega \le R_P \le 500K\Omega)$ (3)      | $V_S = 12V, R_P = 125K\Omega$                                                                                  | 5        | 6          | 10                   | А            |

| R <sub>DS</sub>      | Static Drain Source on Resistance                                                       | $V_S \ge 9V$ , $I_O = 1A$                                                                                      |          | 190        | 380                  | mΩ           |

| Si                   | Internal Fixed Output Voltage<br>Slew Rate (without R <sub>P</sub> ) (1)                | $V_S = 12V; 5\Omega \le R_L \le 7\Omega$ $T_{amb} = \le 25^{\circ}C$                                           | 50<br>50 | 120<br>120 | 230<br>250           | V/ms<br>V/ms |

| Se                   | External Programmable Output Voltage Slew Rate $(30K\Omega \le R_P \le 500K\Omega)$ (2) | $\begin{aligned} V_S &= 12V,  R_P = 125K\Omega \\ R_L &= 6\Omega \\ T_{amb} &= \leq 25^{\circ}C \end{aligned}$ | 50<br>50 | 120<br>120 | 200<br>250           | V/ms<br>V/ms |

|                      | (OUINZE 2 INP 2 OUUINZE) (Z)                                                            | 1 amb - ≥ 25 C                                                                                                 | 50       | 120        | 230                  | V/1113       |

Notes:

(1)

$$S_i = VS \cdot 11.16 \frac{1}{ms} - 7.26 \text{ V/ms}$$

(3)

$$I_{OSP} = (VS - 0.6V) \cdot \frac{64260}{R_P}$$

(4)

$$I_{OS} = (VS - 0.6V) \cdot 0.514 \frac{A}{V}$$

If R  $_P$  is not present in application an internal equivalent resistor can be inserted in the calculation with a typical value of  $R_P=125K\Omega$

#### **FUNCTIONAL DESCRIPTION**

To control the power of the load with a POWER-MOS transistor in the switched mode, its gate must be driven with a PWM signal. The amplitude of the gate driving pulse must guarantee that the Power DMOS transistor will be completely saturated during the ON phase. To generate the necessary gate driving voltage a charge pump circuit is required. With this circuit a gate voltage of  $2 \cdot (V_S - 1.5V) \le VS + 16V$  typically will be obtained.

The slope of the leading and trailing edge of the gate driving pulse is defined with an internal capacitor. The important criteria for the dimensioning of the output voltage slope are the electromagnetic radiation and the power dissipation of the Power DMOS. The typical value of the output pulse slope is in the range of 120V/ms to fullfill automotive radiation requirements.

The output pulse slope is directly related to the value of the supply voltage VS and in a wide range programmable through the programming resistance R<sub>P</sub>.

$$S = \frac{dV_{out}}{dt} = R_L \cdot \frac{dI_{load}}{dt} = \frac{R_L}{R_P} \cdot \frac{VS - 0.65V}{R_L + 0.32\Omega} \cdot 1.47 \frac{10^6 \text{ V}}{Ams}$$

The value of the gate voltage slope due to the POWERMOS parasitic capacitors must be in a relation to the charge pump performance. For fast gate voltage variation the bootstrap option can be used. The bootstrap capacitance should have a relation greater than 50 to the DMOS parasitic ca-

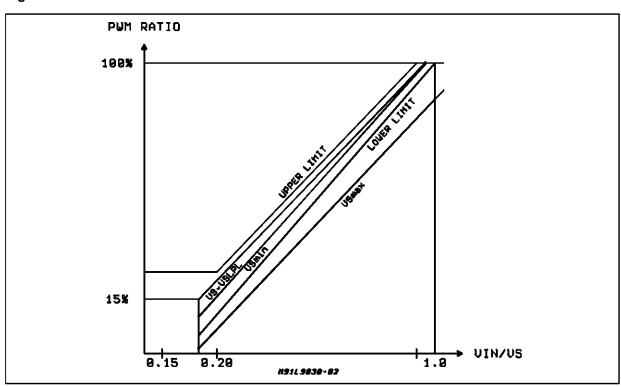

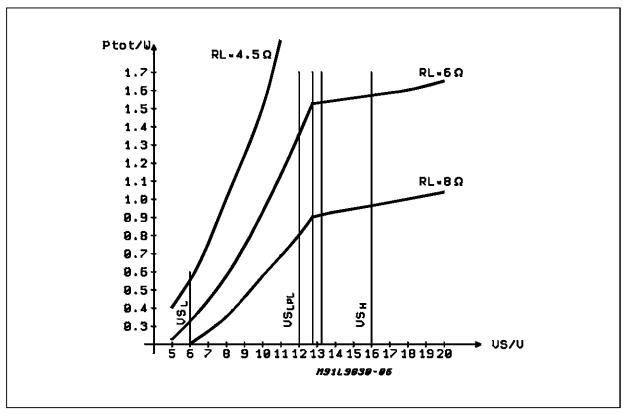

Figure 1: Transfer Characteristc

pacitors and should be in the range of

$$C_{BS} \ge 100 nF$$

The switching frequency "fo" is defined with a triangle oscillator and it's programmed with the capacitor  $C_T$ , or  $C_T$  and  $R_P$  if a greater precision is required.

$$f_O = K_T/C_T$$

(without  $R_P$ )

$$f_O = \frac{1}{4C_T R_P} (with R_{P)}$$

The modulation factor of the PWM driving signal of the external Power DMOS transistor is defined with the voltage level at the analog input. Fig. 1 shows the typical transfer curve giving the PWM factor as a function of the input/supply voltage ratio

For higher supply voltage values, the power limitation circuitry will linearly reduce the PWM ratio to achive a constant load power to extend the lamps life time.

The input voltage is referred to the supply voltage. The regulation of the PWM factor can be realized with a potentiometer connected to the supply voltage and the analog input, see the typical application circuit diagram.

The maximum load current in the short circuit condition is limited internally with a sense DMOS cell.

The value of the short current is a multiple of the programming current flowing through R<sub>P</sub> or the internal fixed resistance. Threfore this short current

value is supply voltage dependent to achieve in any condition the lamp required warm up current which will be normally two or three times higher.

$$I_{OSe} = \frac{VS - 0.6V}{R_P} \cdot 64260$$

If the short current condition is detected the gate will be driven with a DC voltage which value is regulated to maintain the specified current. With this function the switch ON phase for each load will be speeded up.

The circuit features also a protection which allows to withstand high overvoltage for a limited time (load dump in automotive application). Above the  $VS_{\text{H}}$  threshold the gate driving of the POWER-

MOS transistor is switched OFF and the gate is held at the GND potential. When the  $V_{BAT}$  rises above the internal supply clamp voltage  $V_{SLD}$  the clamping diode becomes active with a serial resistance of  $R_{LD}$  and the gate voltage is floating with the GND potential. At this time the current flowing through the load is not limited. In this condition the load voltage can be calculated to

$$V_L = VS = VS_{LD} - VS_{GS}$$

$V_{GS} \ll VS_{LD}$

This device is protected against temperature destruction through an internal power dissipation protection. The total power dissipation of the device can be calculated with:

for  $VS_L \le VS \le VS_{LPL}$ :

$$P_{tot} = VS^{2} \cdot \left( \frac{R_{DS}}{(R_{DS} + R_{L})^{2}} + \frac{f_{O}}{S} \cdot \left( 1 - \frac{R_{DS}}{R_{DS} + R_{L}} \right) \cdot \left( 1 - \frac{R_{DS}}{R_{DS} + R_{L}} \right) \cdot \left( 1 + \frac{2VS}{R_{DS} + R_{L}} \right) \right)$$

and for  $VS_{LPL} \le VS \le VS_H$ :

$$P_{tot} = V^{2}_{SLPL} \cdot \frac{R_{DS}}{(R_{DS} + R_{L})} + \frac{VS^{2}_{S} f_{O}}{S} \cdot (1 - \frac{R_{ON}^{2}}{R_{ON} + R_{L}})$$

Figure 2: Total Power Dissipation Characteristic

Figure 3: Application Circuit Diagram for Dashboard Dimming

Figure 4: Application Circuit Diagram for Dashboard Dimming with Optimized Device Power Dissipation

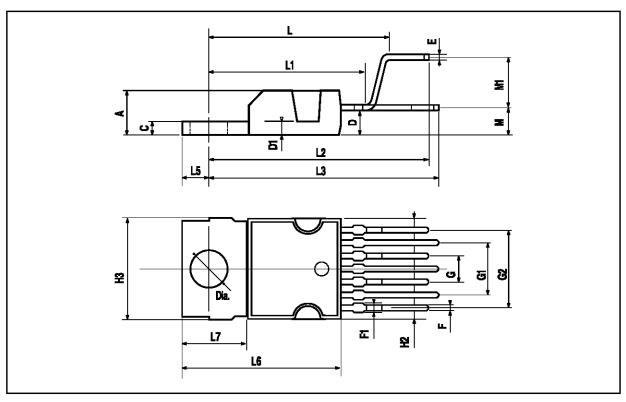

## **HEPTAWATT PACKAGE MECHANICAL DATA**

| DIM.  | mm    |       |      | inch  |       |       |  |

|-------|-------|-------|------|-------|-------|-------|--|

| DINI. | MIN.  | TYP.  | MAX. | MIN.  | TYP.  | MAX.  |  |

| Α     |       |       | 4.8  |       |       | 0.189 |  |

| С     |       |       | 1.37 |       |       | 0.054 |  |

| D     | 2.4   |       | 2.8  | 0.094 |       | 0.110 |  |

| D1    | 1.2   |       | 1.35 | 0.047 |       | 0.053 |  |

| E     | 0.35  |       | 0.55 | 0.014 |       | 0.022 |  |

| F     | 0.6   |       | 0.8  | 0.024 |       | 0.031 |  |

| F1    |       |       | 0.9  |       |       | 0.035 |  |

| G     | 2.41  | 2.54  | 2.67 | 0.095 | 0.100 | 0.105 |  |

| G1    | 4.91  | 5.08  | 5.21 | 0.193 | 0.200 | 0.205 |  |

| G2    | 7.49  | 7.62  | 7.8  | 0.295 | 0.300 | 0.307 |  |

| H2    |       |       | 10.4 |       |       | 0.409 |  |

| H3    | 10.05 |       | 10.4 | 0.396 |       | 0.409 |  |

| L     |       | 16.97 |      |       | 0.668 |       |  |

| L1    |       | 14.92 |      |       | 0.587 |       |  |

| L2    |       | 21.54 |      |       | 0.848 |       |  |

| L3    |       | 22.62 |      |       | 0.891 |       |  |

| L5    | 2.6   |       | 3    | 0.102 |       | 0.118 |  |

| L6    | 15.1  |       | 15.8 | 0.594 |       | 0.622 |  |

| L7    | 6     |       | 6.6  | 0.236 |       | 0.260 |  |

| М     |       | 2.8   |      |       | 0.110 |       |  |

| M1    |       | 5.08  |      |       | 0.200 |       |  |

| Dia   | 3.65  |       | 3.85 | 0.144 |       | 0.152 |  |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1995 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thaliand - United Kingdom - U.S.A.