# SOLENOID DRIVER + SWITCH MODE POWER SUPPLY

ADVANCE DATA

- OPERATING SUPPLY VOLTAGE UP TO 46V

- 1A POWER SUPPLY (5V)

- 5A SOLENOID DRIVER

- PRECISE ON CHIP REFERENCE VOLTAGE

- DISCONTINUOUS MODE FREQUENCY VARIABLE

- VERY HIGH EFFICIENCY

- $1\Omega$  OUTPUT DMOS (SMPS)

- INTERNAL CURRENT LIMIT (SMPS SECTION)

- EXTERNALLY PROGRAMMABLE SOLENOID CURRENT RISING SLOPE

- EXTERNALLY PROGRAMMABLE FIXED HYSTERESIS CONTROL

- OPTIMIZED DMOS R<sub>DS</sub> ON FOR HIGH SIDE CHOPPING

#### **DESCRIPTION**

The L6213 is an IC containing a S.M.P.S. delivering 1A at a voltage of 5V and a section designed to drive a solenoid with a current up to 5A.

The device is realized in BCD mixed technology, which combines isolated DMOS power transistor with CMOS and Bipolar circuits on the same chip.

The SMPS section can deliver 1A DC with an out-

#### MULTIPOWER BCD TECHNOLOGY

put voltage of 5V, including current limiting, reset and power fail for microprocessor and thermal protection.

The solenoid driver section is designed for high current applications like hammer driver in electronic typewriter.

The solenoid output section contains a high side and a low side DMOS, which R<sub>DS ON</sub> are optimized for high side chopping. The current rising slope is externally programmable through an external capacitor.

The level of hysteresis of the current can be changed through an external resistor.

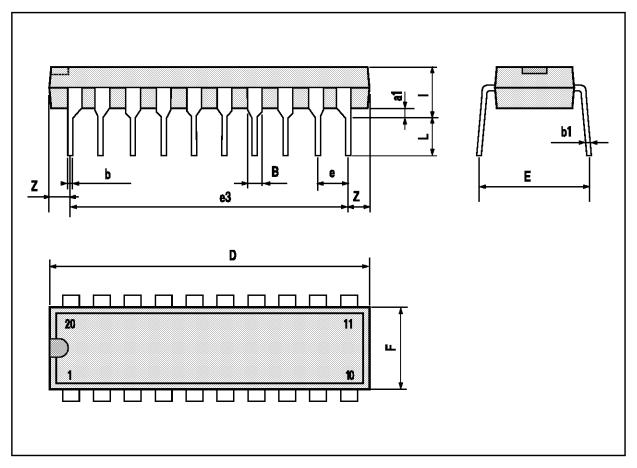

The device is supplied in Powerdip 16+2+2, and use the four center pins to conduct heat to the printed circuit.

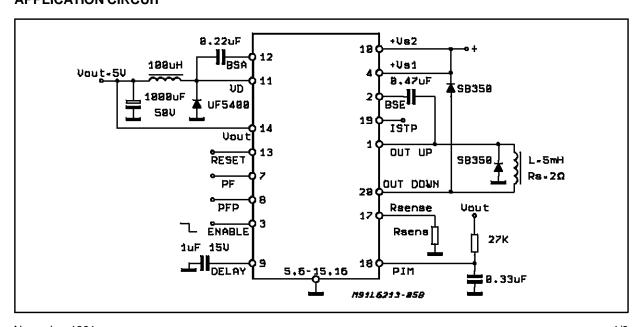

## **APPLICATION CIRCUIT**

November 1991 1/9

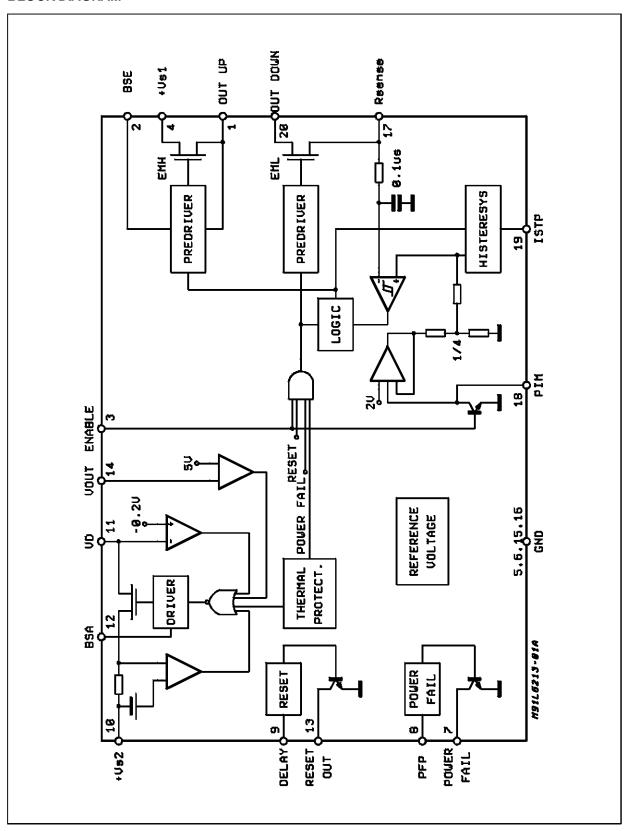

## **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                               | Parameter                                                    | Value                | Unit |

|--------------------------------------|--------------------------------------------------------------|----------------------|------|

| Vs                                   | Supply Voltage                                               | 52                   | V    |

| V <sub>D</sub> ; V <sub>OUT-UP</sub> | Output Negative Voltage DC                                   | -1.3                 | V    |

| $V_D$                                | Output Negative Voltage peak at t = 0.1μs f = 100KHz         | -5V                  | V    |

| V <sub>OUT-DOWN</sub>                | Output Positive Voltage DC                                   | V <sub>S</sub> + 1.3 | V    |

|                                      | Output Positive Voltage peak at $t = 0.1 \mu s$ $f = 25 KHz$ | V <sub>S</sub> + 5   | V    |

| V <sub>OUT-UP</sub>                  | Output Negative Voltage peak at t = 0.1µs f = 25KHz          | -5                   | V    |

| PFP                                  | Input Voltage                                                | 25                   | V    |

| V <sub>O</sub> , Enable<br>PIM       | Input Voltage                                                | 7                    | V    |

| Reset, PF                            | Output Voltage                                               | 20                   | V    |

| CD, ISTP                             | Input Voltage                                                | 5.5                  | V    |

| Out-Up<br>Out-Down                   | Output Current DC = 10% T <sub>ON</sub> = 3.5ms              | 5.5                  | A    |

| T <sub>stg</sub>                     | Storage Temperature                                          | -50 to 150           | °C   |

#### THERMAL DATA

| Symbol                 | Description                         |      | Value | Unit |

|------------------------|-------------------------------------|------|-------|------|

| R <sub>th j-pins</sub> | Thermal Resistance Junction-pins    | Max. | 14    | °C/W |

| R <sub>th j-amb</sub>  | Thermal Resistance Junction-ambient | Max. | 60    | °C/W |

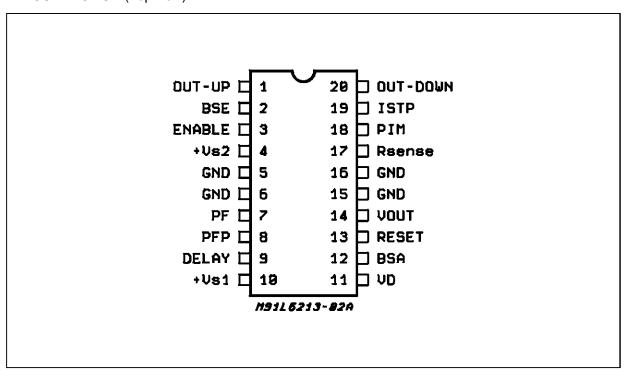

## **PIN CONNECTION** (Top view)

## **PIN DESCRIPTION**

| Nr.    | Name             | Description                                                                                                                                                                                                                                                              |

|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Out-Up           | Solenoid section upper DMOS output.                                                                                                                                                                                                                                      |

| 2      | BSE              | Solenoid section upper DMOS bootstrap. A capacitor connected between pin 2 and pin 1 ensures the efficient driving of the solenoid section upper DMOS.                                                                                                                   |

| 3      | ENABLE           | Solenoid control input - TTL compatible.                                                                                                                                                                                                                                 |

| 4      | +V <sub>S1</sub> | Unregulated voltage input - Solenoid section.                                                                                                                                                                                                                            |

| 5, 6   | GND              | Ground.                                                                                                                                                                                                                                                                  |

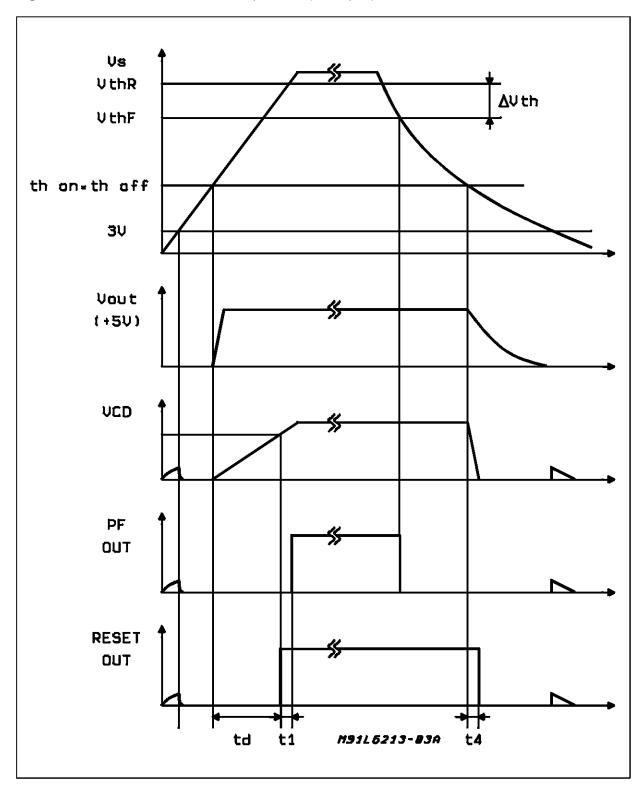

| 7      | PF               | Power fail output, the saturation of PF is guaranteed if VPS exceed 3V. PF is at logic 1 a time T <sub>1</sub> after RESET reached the high level. PF came back to logic 0 when VPS goes down under 18V. (see fig. 1)                                                    |

| 8      | PFP              | Power fail programming. A resistor divider connected to VPS changes the Power fail threshold levels.                                                                                                                                                                     |

| 9      | CD               | Capacitor delay. A capacitor connected to this pin determines the Reset signal delay time $t_{\text{d}}$ .                                                                                                                                                               |

| 10     | $V_{S2}$         | Unregulated voltage input - SMPS sections.                                                                                                                                                                                                                               |

| 11     | VD               | Regulator output and diode voltage control.                                                                                                                                                                                                                              |

| 12     | BSA              | SMPS section DMOS bootstrap. A capacitor connected between pin 12 and pin 11 ensures efficient driving of SMPS DMOS.                                                                                                                                                     |

| 13     | RESET            | Reset output. The saturation of Reset is guaranteed if VPS exceeds 3V. The Reset output reaches the logic level 1 a time delay (set by capacitor CD) after VPS has reached a rising threshold voltage. Reset reaches 0 level when VPS goes down below folling threshold. |

| 14     | $V_{out}$        | Feed back input of the regulation loop.                                                                                                                                                                                                                                  |

| 15, 16 | GND              | Ground.                                                                                                                                                                                                                                                                  |

| 17     | $R_{sense}$      | Connection for solenoid sensing resistor.                                                                                                                                                                                                                                |

| 18     | PIM              | Programming of solenoid current rising edge. An RC network connected to this pin determines the slope of the solenoid current rising edge.                                                                                                                               |

| 19     | ISTP             | Programming of solenoid current histeresys.                                                                                                                                                                                                                              |

| 20     | Out-Down         | Solenoid section lower DMOS output.                                                                                                                                                                                                                                      |

**ELECTRICAL CHARACTERISTICS** (Refer to the application circuit,  $T_J$  =25°C,  $I_{out}$  Power Supply = 50mA, VPS from 12V to 46V; unless otherwise specified.

| Pin   | Symbol             | Parameter                             | Test Condition                                  | Min. | Тур. | Max. | Unit |  |  |

|-------|--------------------|---------------------------------------|-------------------------------------------------|------|------|------|------|--|--|

| STEP  | STEP-DOWN SECTION  |                                       |                                                 |      |      |      |      |  |  |

| 10, 4 | Vi                 | Supply Voltage                        |                                                 | 14   |      | 46   | V    |  |  |

| 14    | Vo                 | Output Voltage                        | I <sub>O</sub> = 0.05 to 1A                     | 4.85 |      | 5.2  | V    |  |  |

|       | R <sub>DS on</sub> | On State Drain Resistance             | T <sub>J</sub> = 25°C; VPS = 15 to 46V          |      | 0.56 | 0.7  | Ω    |  |  |

| 10    | t <sub>h on</sub>  | Turn-on Threshold                     | VPS Rising Fig. 1                               | 10   |      | 12   | V    |  |  |

| 10    | t <sub>h off</sub> | Turn-off Threshold                    | VPS Falling Fig. 1                              | 10   |      | 12   | V    |  |  |

| 10    | lΒ                 | Input Bias Current                    |                                                 |      |      | 15   | mA   |  |  |

| 11    | l <sub>lim</sub>   | Static Current Limiting               |                                                 | 2.2  |      | 3.4  | Α    |  |  |

| 2, 10 | li                 | Total Input Current                   | ENABLE = 1, VPS = 46V,<br>I <sub>load</sub> = 0 |      |      | 13   | mA   |  |  |

| 2, 10 | li                 | Total Input Current                   | ENABLE = 1, VPS = 15V,<br>I <sub>load</sub> = 0 |      |      | 18   | mA   |  |  |

| 11    | t <sub>dp</sub>    | Protection Current Maximum Delay Time |                                                 |      |      | 1    | μs   |  |  |

|       | t <sub>off</sub>   | Minimum Power off State               | VPS = 46V I <sub>O</sub> = 50mA                 | 4.2  |      | 7.8  | μs   |  |  |

# **ELECTRICAL CHARACTERISTICS** (continued)

| Pin  | Symbol               | Parameter                            | Test Condition                                                                                                                                                | Min.                        | Тур.            | Max.            | Unit           |

|------|----------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|-----------------|----------------|

| POWE | R FAIL               |                                      |                                                                                                                                                               |                             |                 |                 |                |

| 10   | $V_{thR}$            | Rising Threshold Voltage             | PFP open Fig. 1                                                                                                                                               | 19.5                        | 20              | 23              | V              |

| 10   | V <sub>thF</sub>     | Falling Threshold Voltage            | PFP open Fig. 1                                                                                                                                               | 16.6                        | 18.1            | 19.5            | V              |

| 10   | $\Delta V_{th}$      | Threshold Hysteresis                 | PFP open Fig. 1                                                                                                                                               | 0.5                         |                 |                 | V              |

| 8    | I <sub>PFI</sub>     | Divided Internal Current             | 3                                                                                                                                                             |                             |                 | 130             | μА             |

| 8    | $V_{th-PFP}$         | Rising Threshold Voltage             | VPS = 24V                                                                                                                                                     | 1.1                         | 1.21            | 1.29            | V              |

| 8    | V <sub>th-PFP</sub>  | Falling Threshold Voltage            | VPS = 24V                                                                                                                                                     | 0.98                        | 1.06            | 1.13            | V              |

| 8    | $\Delta V_{th}$ -PFP | Threshold Hysteresis                 | VPS = 24V                                                                                                                                                     | 30                          |                 |                 | mV             |

| 7    | $V_{sat}$            | Output PF Saturation                 | PF current = 2.5mA<br>VPS = 3 to 46V                                                                                                                          |                             |                 | 0.4             | <b>V</b>       |

| 7    | l <sub>leak</sub>    | Output Leakage Current               | VPS = 46V VPF = 20V                                                                                                                                           |                             |                 | 50              | μΑ             |

| 7    | t1                   | Delay to Reset                       | RESET High to PF high Delay Time (fig. 1)                                                                                                                     | 0                           |                 | 1               | μs             |

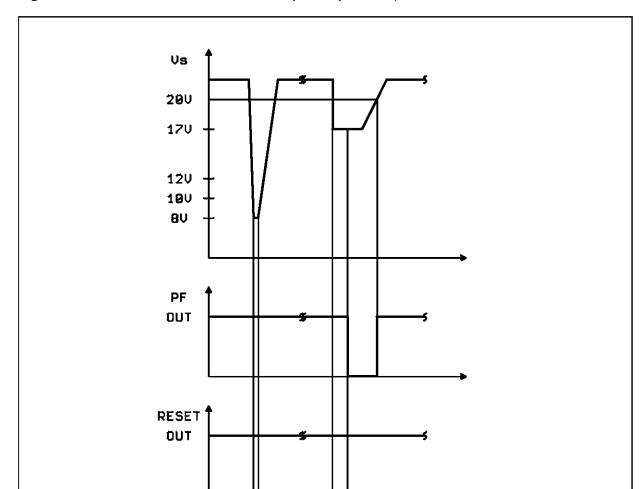

| 7    | t2                   | Noise Immunity                       | When VPS drops to 8V for a time from 0 to t2, PF must be at 1 logic level (fig. 2)                                                                            | 0                           |                 | 1               | μs             |

| 7    | t3                   | Noise Immunity                       | When VPS drops to 17V for a time greater than t3, PF must be at 0 logic level (fig. 2)                                                                        | 4                           |                 |                 | μs             |

| RESE | Т                    |                                      |                                                                                                                                                               |                             |                 |                 |                |

| 9    | I <sub>d</sub>       | Delay Source Current                 | $V_D = 0 \text{ to } 4.1 \text{V}$                                                                                                                            | 70                          |                 | 140             | μΑ             |

| 9    | Id                   | Delay Sink Current                   | VD = 4.3 to 2V                                                                                                                                                | 10                          |                 |                 | mA             |

| 13   | $V_{sat}$            | Output RESET Saturation              | RESET Current = 2.5mA<br>VPS = 3 to 46V                                                                                                                       |                             |                 | 0.4             | >              |

| 13   | I <sub>leak</sub>    | Output Leakage Current               | VPS = 46V RD = 4 to 5V<br>V <sub>RESET</sub> = 20V                                                                                                            |                             |                 | 50              | μΑ             |

| 13   | t4                   | Noise Immunity                       | When VPS drops to 10V for a time greater than t4 RESET must be at 0 logic level (fig. 1)                                                                      | 4                           |                 |                 | μs             |

| SOLE | NOID CON             | NTROL SECTION                        | <b>3</b> ( <b>3</b> )                                                                                                                                         |                             |                 |                 |                |

| 18   | Vsat                 | Saturation Voltage                   | ENABLE = 1   PIM = 5mA                                                                                                                                        |                             |                 | 0.2             | V              |

| 18   | I <sub>leak</sub>    | Leakage Current                      | PIM = 0.2 to 2.5V ENABLE = 0                                                                                                                                  |                             |                 | <u>+</u> 100    | μΑ             |

| 18   | V <sub>clamp</sub>   | Clamp Voltage                        |                                                                                                                                                               | 1.9                         | 2               | 2.1             |                |

| 17   |                      | Minimum Offset Threshold             | PIM = GND V <sub>sens</sub> = 10mV<br>ENABLE = 0                                                                                                              | lower MOS must be in conduc |                 | nduction        |                |

| 17   |                      | MAximum Offset Voltage               | PIM = GND V <sub>sens</sub> = 50mV<br>ENABLE = 0                                                                                                              | lower MOS must be open      |                 |                 | pen            |

| 17   | V <sub>sense</sub>   | Static Voltage Limiting<br>Threshold | V <sub>sens</sub> going from 0 to 0.6V<br>PIM = 3V, the EMH DMOS<br>goes to high resistance state<br>when V <sub>sens</sub> is within: (see<br>Block Diagram) | 0.475                       | 0.5             | 0.525           | V              |

| 17   |                      | Maximum Delay Time                   |                                                                                                                                                               |                             |                 | 1               | μs             |

|      | tp                   | Protection Time                      |                                                                                                                                                               | 2                           |                 | 4               | μs             |

|      | EMH Ron              | On State Drain to Source Resistance  | $T_j = 25^{\circ}C$ , VPS 15 to 46V                                                                                                                           |                             | 0.35            | 0.45            | Ω              |

|      | EML Ron              | On State Drain to Source Resistance  | Tj = 25°C, VPS 15 to 46V                                                                                                                                      |                             | 0.28            | 0.4             | Ω              |

| 17   | V <sub>sense</sub>   | Vsense Hysteresis                    | IST = Open<br>IST = 0.75V<br>IST = 3V                                                                                                                         | 35<br>15<br>80              | 50<br>25<br>100 | 65<br>35<br>120 | mV<br>mV<br>mV |

Figure 1: Power Fail and Reset Static Operation. (PFP open)

t3

H91L6213-04A

ll t2

Figure 2: Power Fail and Reset Noise Immunity and Dynamic Operation.

# POWERDIP20 PACKAGE MECHANICAL DATA

| DIM. |      | mm    |       |       | inch  |       |

|------|------|-------|-------|-------|-------|-------|

|      | MIN. | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |

| a1   | 0.51 |       |       | 0.020 |       |       |

| В    | 0.85 |       | 1.40  | 0.033 |       | 0.055 |

| b    |      | 0.50  |       |       | 0.020 |       |

| b1   | 0.38 |       | 0.50  | 0.015 |       | 0.020 |

| D    |      |       | 24.80 |       |       | 0.976 |

| E    |      | 8.80  |       |       | 0.346 |       |

| е    |      | 2.54  |       |       | 0.100 |       |

| e3   |      | 22.86 |       |       | 0.900 |       |

| F    |      |       | 7.10  |       |       | 0.280 |

| I    |      |       | 5.10  |       |       | 0.201 |

| L    |      | 3.30  |       |       | 0.130 |       |

| Z    |      |       | 1.27  |       |       | 0.050 |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thaliand - United Kingdom - U.S.A.