## SEMICONDUCTOR TECHNICAL DATA

### **KIA2092N**

BIPOLAR LINEAR INTEGRATED CIRCUIT SILICON MONOLITHIC

#### POWER DRIVER IC FOR CD PLAYER

The KIA2092N is a power driver IC developed for CD players.

This IC have built-in 4 channel BTL power amplifiers which drives focus-coil, tracking-coil for 3-beam pick-up head, disc motor and feed motor.

#### **FEATURES**

- · 4 channel BTL linear drivers

- Fixed voltage gain : G<sub>V</sub>=15dB (Typ.)

- · High output power

- :  $V_{OM1}$ =5 $V_{P-P}$  (Typ.) @ $V_{CC}$ =5V,  $R_L$ =5 $\Omega$

- :  $V_{OM2}$ =6 $V_{P-P}$  (Typ.) @ $V_{CC}$ =6V,  $R_L$ =5 $\Omega$

- · Thermal shutdown circuit.

- · Input reference voltage short protection

- · Operating Voltage range

- :  $V_{CC(opr)}=4.0\sim10.0V$  (Ta=25°C)

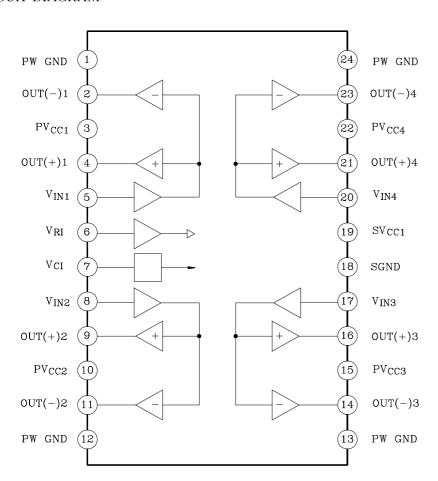

#### **BLOCK DIAGRAM**

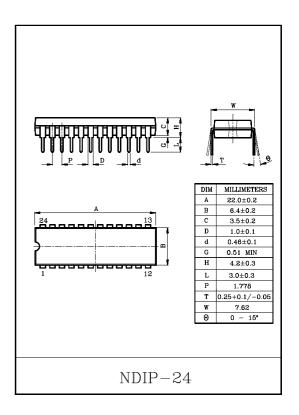

Weight: 1.2g (Typ.)

## **KIA2092N**

#### MAXIMUM RATINGS (Ta=25℃)

| CHARACTERISTIC        | SYMBOL                  | RATING       | UNIT         |

|-----------------------|-------------------------|--------------|--------------|

| Supply Voltage        | $V_{CC}$                | 14           | V            |

| Power Dissipation     | P <sub>D</sub> (Note 1) | (2) (Note 2) | W            |

| Operating Temperature | $T_{opr}$               | -30~85       | $^{\circ}$ C |

| Storage Temperature   | $T_{\mathrm{stg}}$      | -55~150      | $^{\circ}$   |

(Note 1): Mounted on 50mm×50mm×1.6mm size board with copper area 60% over.

(Note 2) : Derated above Ta=25°C, in the proportion of 62.5mW/°C

#### ELECTRICAL CHARACTERISTICS

(Unless otherwise specified,  $V_{CC}$ =5V,  $R_L$ =5 $\Omega$ , Rg=620 $\Omega$ ,  $V_{RI}$ =2.1V, f=1kHz, Ta=25 $^{\circ}$ C)

| CHARACTERISTIC                             | SYMBOL              | TEST CONDITION                                          | MIN. | TYP. | MAX. | UNIT         |

|--------------------------------------------|---------------------|---------------------------------------------------------|------|------|------|--------------|

| Operating Voltage                          | $V_{CC}$            | -                                                       | 4.0  | -    | 10.0 | V            |

| Quiescent Current                          | $I_{CCQ}$           | V <sub>in</sub> =0, R <sub>L</sub> =OPEN                | 20   | 35   | 60   | mA           |

| Input Offset Current                       | $I_{\mathrm{IN}}$   | V <sub>IN</sub> =2.1V                                   | -    | 250  | 800  | nA           |

| V <sub>RI</sub> Terminal Offset Current    | $I_{10}$            | $V_{RI}$ =2.1 $V$                                       | =    | 35   | 120  | μΑ           |

|                                            | Vo osi              | $V_{CC}$ =5V, Rg=0 $\Omega$                             | -30  | -    | 30   |              |

| Output Offset Voltage                      | Vo os2              | $V_{CC}$ =8 $V$ , $Rg$ =0 $\Omega$                      | -50  | -    | 50   | mV           |

|                                            | Vo osa              | $V_{CC}$ =12V, Rg=0 $\Omega$                            | -100 | -    | 100  |              |

| Reference Output Voltage                   | $V_{\mathrm{OUT}}$  | -                                                       | -    | 2.1  | -    | V            |

| Maximum Output Voltage                     | $V_{\mathrm{OM1}}$  | V <sub>CC</sub> =5V                                     | 4.0  | 5.0  | -    | T.7          |

|                                            | V <sub>OM2</sub>    | V <sub>CC</sub> =6V                                     | 5.0  | 6.0  | -    | $ m V_{P-P}$ |

| Voltage Gain                               | G <sub>V</sub>      | $V_{\rm in}$ =100m $V_{\rm rms}$                        | 14.5 | 15.5 | 16.5 | dB           |

| Frequency Response                         | $f_{\mathrm{C}}$    | $V_{in}$ =100m $V_{rms}$                                | -    | 100  | -    | kHz          |

| Total Harmonic Distortion                  | THD                 | $V_{\rm in}$ =100m $V_{\rm rms}$                        | -    | -50  | -    | dB           |

| Slew Rate                                  | S.R.                | Vout=2V <sub>P-P</sub>                                  | -    | 1.0  | -    | V/µS         |

| Cross Talk                                 | C.T.                | Vout=1V <sub>rms</sub>                                  | -    | -60  | _    | dB           |

| Ripple Rejection Ratio                     | R.R.                | $f_{\rm rip}$ =100Hz, $V_{\rm rip}$ =100m $V_{\rm rms}$ | -    | -60  | -    | dB           |

| Thermal Shut Down<br>Temperature           | $T_{TSD}$           | Chip temperature                                        | -    | 150  | -    | $^{\circ}$   |

| $V_{RI} \sim GND$ Short Protection Voltage | V <sub>RI</sub> OFF | -                                                       | 1.4  | 1.6  | 1.8  | V            |

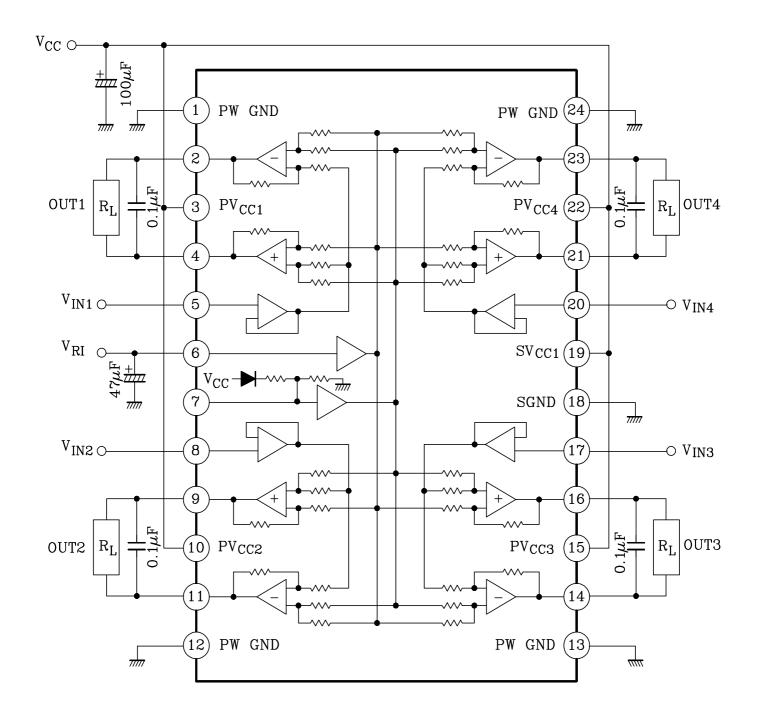

#### TEST CIRCUIT

# **KIA2092N**

#### TERMINAL EXPLANATION

| TERMINAL<br>No. | SYMBOL                       | FUNCTION                                                                                                                                                                                                                                                                           | EQUIVALENT CIRCUIT                                      |  |

|-----------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| 1               | PW GND                       | Power GND  Connected to substrate.  D, ②, ③, ② pin are connected inside.                                                                                                                                                                                                           | SV <sub>CC</sub> PV <sub>CC</sub>                       |  |

| 2               | OUT(-) 1                     | Inverted output for CH1                                                                                                                                                                                                                                                            |                                                         |  |

| 3               | $\mathrm{PV}_{\mathrm{CC1}}$ | Supply terminal of output stage for CH1  • Supply terminal of output stage are not connected to other channel terminal.                                                                                                                                                            | OUT                                                     |  |

| 4               | OUT(+) 1                     | Non-inverted output for CH1                                                                                                                                                                                                                                                        | PGND                                                    |  |

| 5               | $ m V_{IN1}$                 | Input for CH1 • Not biased inside                                                                                                                                                                                                                                                  | SGND SGND                                               |  |

| 6               | $ m V_{RI}$                  | $\label{eq:local_local_local_local_local} \begin{tabular}{ll} Input reference voltage \\ \bullet \ Under \ condition \ of \ V_{RI} {\le} 1.8V, \ internal \ bias \\ circuit \ is \ shut \ off. \\ \bullet \ No \ signal \ input \ condition \ : \ V_{RI} {=} V_{IN} \end{tabular}$ | V <sub>RI</sub> CHO |  |

| 7               | $ m V_{CI}$                  | Output reference voltage $ \cdot \ V_{OUT} = V_{CI} = (V_{CC} - V_F)/2 $                                                                                                                                                                                                           | SV <sub>CC</sub> V <sub>CI</sub> SGND  SGND             |  |

| 8               | $ m V_{IN2}$                 | Input for CH2                                                                                                                                                                                                                                                                      |                                                         |  |

| 9               | OUT(+)2                      | Non-inverted output for CH2                                                                                                                                                                                                                                                        |                                                         |  |

| 10              | $\mathrm{PV}_{\mathrm{CC2}}$ | Supply terminal of output stage for CH2                                                                                                                                                                                                                                            | Same as channel 1                                       |  |

| 11              | OUT(-)2                      | Inverted output for CH2                                                                                                                                                                                                                                                            |                                                         |  |

| 12              | PW GND                       | Power GND                                                                                                                                                                                                                                                                          |                                                         |  |

| 13              | PW GND                       | Power GND                                                                                                                                                                                                                                                                          |                                                         |  |

| 14              | OUT(-)3                      | Inverted output for CH3                                                                                                                                                                                                                                                            |                                                         |  |

| 15              | $PV_{CC3}$                   | Supply terminal of output stage for CH3                                                                                                                                                                                                                                            | Same as channel 1                                       |  |

| 16              | OUT(+)3                      | Non-inverted output for CH3                                                                                                                                                                                                                                                        |                                                         |  |

| 17              | $ m V_{IN3}$                 | Input for CH3                                                                                                                                                                                                                                                                      |                                                         |  |

| 18              | S GND                        | Supply terminal of small signal GND                                                                                                                                                                                                                                                | -                                                       |  |

| 19              | S VCC                        | Small signal GND                                                                                                                                                                                                                                                                   | -                                                       |  |

| 20              | $ m V_{IN4}$                 | Input for CH4                                                                                                                                                                                                                                                                      |                                                         |  |

| 21              | OUT(+)4                      | Non-inverted output for CH4                                                                                                                                                                                                                                                        |                                                         |  |

| 22              | PV <sub>CC4</sub>            | Supply terminal of output stage for CH4                                                                                                                                                                                                                                            | Same as channel 1                                       |  |

| 23              | OUT(-)4                      | Inverted output for CH4                                                                                                                                                                                                                                                            | 1                                                       |  |

| 24              | PW GND                       | Power GND                                                                                                                                                                                                                                                                          |                                                         |  |

## **KIA2092N**

#### PRECAUTION USE

- Input Stage

- · Input stages are consisted of differential circuit of NPN Tr, and have built-in IB compensation circuit.

- Built-in Driver

- · Each channel driver consists of BTL configuration linear amplifier.

- Voltage gain is fixed : G<sub>V</sub>=15.5dB (Typ.)

- Voltage loss for output stage is  $2V_{BE}=V_{CE}(sat)$  for positive cycle,  $V_{CE}(sat)$  for negative cycle, because of no-bootstrap circuit. So, output DC voltage is designed as less than  $1/2~V_{CC}$ .

- V<sub>RI</sub> Terminal

- · V<sub>RI</sub> is reference voltage terminal for input signal.

- If reference voltage from servo IC drop less than 1.8V, protection circuit operates and shut off bias circuit inside. This operation is to prevent load from moving undesirably in case of  $V_{RI}$  drop for accident or some reason.

- V<sub>CI</sub> Terminal

- Output DC voltage is determined by circuit of this terminal inside as ;  $V_{\text{CI}} = V_{\text{OUT}(DC)} = (V_{\text{CC}} V_F)/2$

- Output signal dynamic range is depend on  $V_{\text{CC}}$  On the other hand, input signal dynamic range is determined by  $V_{\text{RI}}$  as mentioned and voltage gain is fixed inside. So, maximum output voltage does not increase as  $V_{\text{CC}}$  increases.

- Because of BTL configuration, Ripple Rejection Ratio does not improve not much when capacitor is connected to V<sub>CI</sub> terminal to GND.

#### • GND

- Large signal GND is for output stage and small signal GND is for stages from input circuit to pro-output stage.

- · These GND pins are not connected inside.

- The heat of power dissipation is transferred to PCB, through these PW-GND pin, because, ①, ②, ③ pin are connected each other and to substrate of pellet to connected copper foil area as large as possible.

- Oscillation preventive capacitor

- We recommend to use the capacitor of  $0.1\mu\text{F}$ , between each output terminals. But perform the temperature test to check the oscillation allowance, since the oscillation allowance is varied according to the causes described below.

- 1) Supply voltage

- 2) Ambient temperature

- 3) Load impedance

- 4) Capacity value of condenser

- 5) Kind of condenser

- 6) Layout of printed board

- We recommend to connect Pass-condenser, which is about 10 to 100μF between V<sub>RI</sub> terminal and GND.

- V<sub>CI</sub> terminal is recommend to use "OPEN".