# Addendum to MC68HC05P9 HCMOS Microcontroller Unit Technical Data

This addendum provides additions and corrections to the *MC68HC05P9 Technical Data*, Rev. 0 (Motorola document number MC68HC05P9/D).

1. Page 1-1, section **1.1 Features** — Change the third bulleted item as follows:

## From:

• 2112 Bytes of User ROM including 16 User Vector Locations

## To:

• 2104 Bytes of User ROM including 8 User Vector Locations

This document contains information on a new product. Specifications and information herein are subject to change without notice.

Page 2-7, section 2.6.3 Port C and Analog-to-Digital Converter — Replace the second paragraph with the following:

## From:

When the A/D converter is enabled, PC7 becomes  $V_{RH}$ , and PC6–PC3 become AN3–AN0 (analog inputs 3–0). The values of CH1 and CH0 in the A/D status and control register (ADSCR) select one of the four pins as the input to the A/D converter. When the A/D converter is enabled, a digital read of port C gives a logical zero from the selected analog input pin. A digital read of port C's remaining pins gives their correct digital values.  $V_{RH}$  is the positive (high) reference voltage for the A/D converter.  $V_{SS}$  is the negative (low) reference voltage. A reset turns off the A/D converter and configures port C as a general-purpose I/O port. (Refer to **SECTION 8 ANALOG-TO-DIGITAL CONVERTER**.)

#### To:

When the A/D converter is enabled, PC7 becomes  $V_{\rm RH}$ , and PC6–PC3 become AN3–AN0 (analog inputs 3–0). The values of CH1 and CH0 in the A/D status and control register (ADSCR) select one of the four pins as the input to the A/D converter.

Unused analog inputs can be used as digital inputs, but no analog input can be used as a digital output while the ADC is on. Only pins PC0–PC2 can be used as digital outputs when the ADC is on.

When the A/D converter is enabled, a digital read of port C gives a logical zero from the selected analog input pin. A digital read of the remaining port C pins gives their correct digital values.

$V_{RH}$  is the positive (high) reference voltage for the A/D converter.  $V_{SS}$  is the negative (low) reference voltage. A reset turns off the A/D converter and configures port C as a general-purpose I/O port. (Refer to **SECTION 8 ANALOG-TO-DIGITAL CONVERTER**.)

3. Page 3-23, Table 3-13. Opcode Map — Replace the opcode map with the opcode map on page 3. The new opcode map contains data corrections for the following opcodes:

| Opcode | Mnemonic  | Opcode | Mnemonic |

|--------|-----------|--------|----------|

| 13     | BCLR1     | 68     | ASL/LSL  |

| 25     | BCS/BLO   | 69     | ROL      |

| 38     | ASL/LSL   | 6A     | DEC      |

| 48     | ASLA/LSLA | 6C     | INC      |

| 50     | NEGX      | 6D     | TST      |

| 58     | ASLX/LSLX | 6F     | CLR      |

|        |           | 78     | ASL/LSL  |

MOTOROLA MC68HC05P9AD/D

Table 3-13. Opcode Map

|                   |      | MSB      | 0                 | -              | 2              | က                                                                                               | 4                                | 5                | 9                                               | 7                        | 8                           | 6                           | 4                           | Ф               | ပ                                                             | ٥                           | Ш              | ч                   |                                  |                                                             |

|-------------------|------|----------|-------------------|----------------|----------------|-------------------------------------------------------------------------------------------------|----------------------------------|------------------|-------------------------------------------------|--------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------|---------------------------------------------------------------|-----------------------------|----------------|---------------------|----------------------------------|-------------------------------------------------------------|

|                   | ×    | ш        | SUB 3             | CMP 3          | SBC 3          | CPX 3                                                                                           | AND X                            | BIT IX           | S<br>LDA IX                                     | STA 4                    | EOR IX                      | ADC IX                      | ORA IX                      | ADD X           | JMP IX                                                        | JSR 5                       | XI CDX         | STX 4               |                                  |                                                             |

|                   | X    | ш        | SUB 1X11          | CMP 4          | SBC 4          | CPX   1X1   1                                                                                   | AND 4                            | BIT 4            | LDA<br>IX1                                      | STA IX1 1                | EOR IX1                     | ADC 4                       | ORA<br>IX1                  | ADD 4           | 3<br>JMP<br>IX1                                               | JSR<br>IX1                  | LDX 4          | STX<br>IX1          | kadecima                         | O TO                                                        |

| emorv             | X2   | ۵        | SUB 5             | CMP 5          | SBC 5          | CPX 5                                                                                           | AND 5                            | BIT 5            | LDA<br>IX2 2                                    | STA 6                    | EOR 1X2 2                   | ADC 5                       | ORA<br>IX2 2                | ADD 5           | JMP 4                                                         | JSR 7                       | LDX 5<br>IX2 2 | STX 6               | ode in He                        | cles<br>nonic                                               |

| Register/Memory   | EXT  | U        | SUB 4<br>EXT 3    | CMP 4<br>EXT 3 | SBC 4<br>EXT 3 | CPX 4<br>EXT 3                                                                                  | AND 4<br>EXT 3                   | BIT 4<br>EXT 3   | LDA<br>EXT 3                                    | STA EXT 3                | EOR EXT 3                   | ADC 4<br>EXT 3              | ORA<br>EXT 3                | ADD 4<br>EXT 3  | JMP 3                                                         | JSR 6<br>EXT 3              | LDX 4<br>EXT 3 | STX 5<br>EXT 3      | MSB of Opcode in Hexadecimal     | 5 Number of Cycles Opcode Mnemonic                          |

| 8                 | DIR  | <u> </u> | SUB 3             | CMP 3          | SBC 3          | CPX 3                                                                                           |                                  |                  |                                                 |                          | EOR 3                       |                             | 3<br>ORA<br>DIR 3           | ADD 3           |                                                               | JSR<br>DIR 3                |                |                     | 0                                | BRSET0 Opcode Mnemonic                                      |

|                   | Z    | <        | SUB 2             | CMP 2          | SBC 2          | CPX 2 IMM 2                                                                                     | AND 2<br>IMM 2                   | BIT 2 IMM 2      | LDA IMM 2                                       | 2                        | EOR 2 IMM 2                 | ADC 2 IMM 2                 | ORA IMM 2                   | ADD 2 IMM 2     |                                                               | BSR 6<br>REL 2              |                |                     | MSB                              | 0<br>B                                                      |

|                   | Ŧ    |          | 7                 | 8              | 8              | 2                                                                                               | . 8                              | 2                | 2                                               | TAX 2                    | CLC 2 INH 2                 | SEC 2                       | $\frac{2}{ NH ^2}$          | SEI 2<br>INH 2  | RSP 2                                                         | NOP 2<br>INH 2              | 2              | TXA INH             | <u> </u>                         | ecimal                                                      |

| Control           | ¥    |          | RTI 9             | RTS 6          |                | 10<br>SWI<br>INH                                                                                |                                  |                  |                                                 |                          | -                           |                             | -                           |                 |                                                               |                             | STOP INH       | WAIT 2 .            | •                                | LSB of Opcode in Hexadecimal                                |

| 5                 | ×    |          | NEG 5             |                |                | COM 5 S                                                                                         | LSR 5                            |                  | ROR IX                                          | ASR IX                   | ASL/LSL<br>IX               | ROL 5                       | DEC 5                       |                 | INC 5                                                         | 4 TST XI                    | s t            | $\frac{5}{10}$ V    |                                  | of Opcode                                                   |

| ji<br>D           | ×    | 9        | NEG 6<br>IX11     |                |                | $com \frac{6}{1X1} c$                                                                           | LSR 6 L                          |                  | ROR 6 R                                         | ASR   ASR   A            | ASL/LSL AS                  | ROL 6 F                     | DEC 6 C                     |                 | INC 6 IX                                                      | TST 5 T                     |                | $\frac{6}{ X_1 ^4}$ | •                                | LSB                                                         |

| Read-Modify-Write | H    |          | NEGX 3<br>INH2    |                |                | $\frac{3}{\text{COMX}} = 0$                                                                     |                                  |                  | $\frac{3}{1000}$ Religion                       | ASRX A INH2              | ASLX/LSLX ASI               | ROLX R                      |                             |                 | INCX 3 IN INCX IN INCX IN | TSTX T                      |                | CLRX 3 C            | •                                |                                                             |

| Read-Mo           |      |          | NEGA NE           |                | _ = _ <u>=</u> | $\begin{array}{c} 3 \\ \text{COMA} \\ \text{INH} \end{array} = \begin{array}{c} CO \end{array}$ | LSRA LS                          |                  | RORA RO                                         | ASRA AS                  |                             | ROLA RC                     | DECA DE                     |                 | INCA IN                                                       |                             |                | CLRA CL             | į ta                             | offset<br>Offset                                            |

|                   | Ĭ    | 4        | 5<br>NEG          |                | MUL<br>I       | 5 COIV                                                                                          | 5<br>LSR                         |                  | 5<br>R 1                                        | S ASR<br>DIR 1           | < √ −                       | _                           | 5<br>R 1                    |                 | _                                                             | _                           |                | 5<br>R 1            | Ro Offisi                        | , 8-Bit O<br>, 16-Bit                                       |

|                   | DIR  | က        | NEG 5<br>2 DIR 1  |                |                | COM 5                                                                                           |                                  |                  | ROR 1                                           |                          | ASL/LSL<br>2 DIR            | ROL<br>2 DIR                | DEC 5                       |                 | INC 5<br>2 DIR                                                | TST 2                       |                | CLR 5               | REL = Relative<br>IX = Indexed N | IX1 = Indexed, 8-Bit Offset<br>IX2 = Indexed, 16-Bit Offset |

| Branch            | REL  | 2        | BRA<br>2 REL 2    | BRN 2          | BHI 3          | BLS 3                                                                                           | BCC 3                            | BCS/BLO<br>2 REL | BNE 2                                           | BEQ 3                    | BHCC<br>2 REL               | BHCS<br>2 REL               | BPL 3                       | BMI<br>2 REL    | BMC<br>2 REL                                                  | BMS 2                       | BIL<br>2 REL   | BIH 3               | REL:                             | X1<br> X2<br> =                                             |

| ulation           | PR - | -        | BSET0<br>DIR      | BCLR0<br>DIR   | SSET1<br>DIR   |                                                                                                 |                                  | 5<br>CLR2<br>DIR |                                                 |                          |                             |                             |                             | BCLR5           | 5<br>SSET6<br>DIR                                             | SCLR6<br>DIR                | SSET7<br>DIR   | SCLR7<br>DIR        | rent<br>ediate                   | nded                                                        |

| Bit Manipulation  | - H  | 0        | BRSET0<br>3 DIR 2 |                | BRSET1 E       | BRCLR1 BCLR1<br>3 DIR 2 DIR                                                                     | 5<br>BRSET2 BSET2<br>3 DIR 2 DIR | BRCLR2 B         | 5<br>BRSET3<br>BRSET3<br>3 DIR <sub>2</sub> DIR | BRCLR3 BCLR3 3 DIR 2 DIR | 8RSET4 BSET4<br>3 DIR 2 DIR | BRCLR4 BCLR4<br>3 DIR 2 DIR | BRSET5 BSET5<br>3 DIR 2 DIR | BRCLR5<br>3 DIR | BRSET6<br>3 DIR                                               | BRCLR6 BCLR6<br>3 DIR 2 DIR | BRSET7 E       | BRCLR7<br>3 DIR2    | NH = Inhe                        | DIR = Direct<br>EXT = Extended                              |

|                   |      | MSB      | 0                 | -              | 8              | 8                                                                                               | 4                                | 2                | 9                                               | 2                        | 8                           | 6                           | <b>V</b>                    | <b>a</b>        | ິ່ວ                                                           | ۵                           | ш              | 4                   |                                  |                                                             |

4. Page 4-1, section 4.1 Resets — Change the first bulleted item in the second paragraph as follows:

MOTOROLA 3 MC68HC05P9AD/D

## From:

• All implemented data direction register bits are cleared to logical zero, so the corresponding I/O pins become high-impedance inputs.

# To:

- All implemented data direction register bits are cleared to logical zero, so the

corresponding I/O pins become high-impedance inputs. (When an external

reset or power-on reset occurs, I/O port pins become high-impedance inputs

even if the system clock is absent.)

- 5. Page 4-2, section **4.1.3 Computer Operating Properly (COP) Watchdog Reset** In the fourth sentence in the first paragraph, change the 64 ms to 65.5 ms as follows:

## From:

The COP system is implemented with an 18-stage ripple counter that provides a timeout period of 64 ms at an internal clock rate of 2 MHz.

#### To:

The COP system is implemented with an 18-stage ripple counter that provides a timeout period of 65.5 ms at an internal clock rate of 2 MHz.

MOTOROLA MC68HC05P9AD/D

6. Page 4-2, section 4.1.3 Computer Operating Properly (COP) Watchdog Reset

— Replace the second paragraph as follows:

From:

The write-only COP register is used to prevent a COP timer reset. This location contains user-defined ROM data. Figure 4-1 shows the COP register.

To:

The write-only COP register is used to prevent a COP timer reset. This location contains user-defined ROM data. Figure 4-1 shows the COP register.

Use the following formula to calculate the COP timeout period:

COP Timeout Period =

$$\frac{131,072}{f_{BUS}}$$

where

$$f_{BUS} = \frac{crystal\ frequency}{2}$$

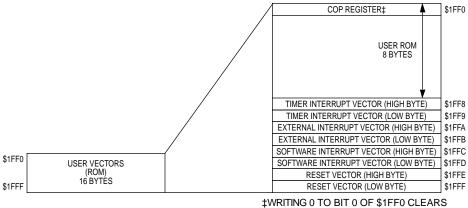

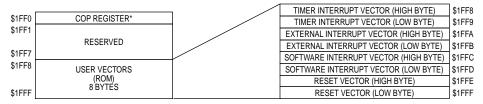

7. Page 5-2, **Figure 5-1. Memory Map** — Change the USER VECTORS portion at the bottom of the map as follows:

From:

‡WRITING 0 TO BIT 0 OF \$1FF0 CLEARS COP TIMER. READING \$1FF0 RETURNS USER ROM DATA.

Figure 5-1. Memory Map

To:

<sup>\*</sup>Writing zero to bit 0 of \$1FF0 clears the COP timer.

Figure 5-1. Memory Map

8. Page 5-4, section **5.1.3 ROM** — Change the first paragraph as follows:

## From:

On-chip user ROM includes 48 bytes at addresses \$0020–\$004F, 2048 bytes at \$0100–\$08FF, and 16 bytes at \$1FF0–\$1FFF that contain user-defined vectors for servicing interrupts and resets.

To:

On-chip user ROM includes 48 bytes at addresses \$0020–\$004F, 2048 bytes at \$0100–\$08FF, and 8 bytes at \$1FF8–\$1FFF that contain user-defined vectors for servicing interrupts and resets.

Page 7-3, section 7.2 SIOP Pin Descriptions — Add the following note after the last paragraph:

#### NOTE

Enabling and then disabling the SIOP configures data direction register B for SIOP operation and can also change the port B data register. After disabling the SIOP, initialize data direction register B and the port B data register as your application requires.

10. Page 7-4, section 7.2.3 SIOP Data Output — Change the paragraph as follows:

#### From:

The SDO pin becomes a serial output and goes to a logical one as soon as the SIOP is enabled. Between transfers, the state of the SDO pin reflects the value of the last bit received on the previous transmission. SDO cannot be used as a standard output while the SIOP is enabled, because it is coupled to the last stage of the serial shift register. On the first falling edge of SCK, the first data bit to be shifted out is presented to the SDO pin.

To:

Enabling the SIOP configures the SDO pin as an output. The state of the SDO pin:

- · Is logic one if the SIOP has not been used since the last reset

- Reflects the last bit received if the SIOP has been used since the last reset

- Is unpredictable if SCK was low during reset or if SCK went low after reset

Between transfers, the state of the SDO pin reflects the value of the last bit received on the previous transmission. SDO cannot be used as a standard output while the SIOP is enabled, because it is coupled to the last stage of the serial shift register. On the first falling edge of SCK, the first data bit to be shifted out is presented to the SDO pin.

11. Page 8-1, section **8.1 ADC Operation** — Change the second paragraph as follows:

#### From:

A multiplexer selects one of four analog input channels (AN3, AN2, AN1, or AN0) for sampling. A comparator successively compares the output of an internal D/A converter to the sampled analog input. Control logic changes the D/A converter input one bit at a time, starting with the MSB, until the D/A converter output matches the sampled analog input. The conversion is monotonic and has no missing codes.

#### To:

A multiplexer selects one of four analog input channels (ANO, AN1, AN2, or AN3) for sampling. The conversion takes 32 cycles. The first 12 cycles sample the voltage on the selected input pin by charging an internal capacitor. In the last 20 cycles, a comparator successively compares the output of an internal D/A converter to the sampled analog input. Control logic changes the D/A converter input one bit at a time, starting with the MSB, until the D/A converter output matches the sampled analog input. The conversion is monotonic and has no missing codes. At the end of the conversion, the conversion complete flag (CC) becomes set, and the CPU takes 2 cycles to move the result to the ADC data register (ADDR).

12. Page 8-2, section **8.2 A/D Status and Control Register (ADSCR)** — Change the CCF bit description as follows:

# From:

### CCF — Conversion Complete Flag

This read-only bit is automatically set when an analog-to-digital conversion is complete, and a new result can be read from the A/D data register. CCF is automatically cleared when a new conversion begins or when either the A/D status and control register or the A/D data register is accessed. Writing to or reading the A/D status and control register or the A/D data register starts a new conversion sequence. Data from the previous conversion is overwritten regardless of the state of the CCF bit. While CCF is a logical zero, the requested A/D result is not yet available in the A/D data register.

## To:

## CCF — Conversion Complete Flag

This read-only bit is automatically set when an analog-to-digital conversion is complete, and a new result can be read from the A/D data register. Clear the CCF bit by writing to the A/D data register or by reading the A/D data register. Reset clears the CCF bit.

MOTOROLA MC68HC05P9AD/D

13. Page 10-7, **Table 10-5. A/D Converter Characteristics** — Change the **Max** column in the second row of Table 10-5 as follows:

From:

Table 10-5. A/D Converter Characteristics

| Characteristic                                                                    | Min | Max     | Unit |

|-----------------------------------------------------------------------------------|-----|---------|------|

| Absolute Accuracy (4.0 > V <sub>RH</sub> > V <sub>DD</sub> )<br>(refer to NOTE 1) | _   | ± 1-1/2 | LSB  |

To:

Table 10-5. A/D Converter Characteristics

| Characteristic                                                                    | Min | Max   | Unit |

|-----------------------------------------------------------------------------------|-----|-------|------|

| Absolute Accuracy (4.0 > V <sub>RH</sub> > V <sub>DD</sub> )<br>(refer to NOTE 1) | _   | ± 1.5 | LSB  |

14. Page 10-8, **Figure 10-6. TCAP Timing** — Change the  $t_{TLTL}$  parameter to  $t_{ILIL}$  as follows:

From:

Figure 10-6. TCAP Timing

To:

Figure 10-6. TCAP Timing

15. Page 10-12, **Table 10-8. SIOP Timing (V<sub>DD</sub> = 5.0 Vdc)** — Change the first row as follows:

From:

Table 10-8. SIOP Timing  $(V_{DD} = 5.0 \text{ Vdc})$

| Characteristic                            | Symbol                                       | Min        | Max         | Unit                   |

|-------------------------------------------|----------------------------------------------|------------|-------------|------------------------|

| Frequency of Operation<br>Master<br>Slave | f <sub>SIOP(M)</sub><br>f <sub>SIOP(S)</sub> | 0.25<br>dc | 0.25<br>525 | f <sub>OP</sub><br>kHz |

To:

Table 10-8. SIOP Timing ( $V_{\rm DD}$  = 5.0 Vdc)

| Characteristic                            | Symbol                                       | Min                        | Max                        | Unit       |

|-------------------------------------------|----------------------------------------------|----------------------------|----------------------------|------------|

| Frequency of Operation<br>Master<br>Slave | f <sub>SIOP(M)</sub><br>f <sub>SIOP(S)</sub> | f <sub>osc</sub> /64<br>dc | f <sub>osc</sub> /8<br>525 | MHz<br>kHz |

Change NOTE 1 at the bottom of the table as follows:

# From:

1.  $f_{OP} = f_{OSC} \div 2 = 2.1$  MHz maximum;  $t_{CYC} = 1 \div f_{OP}$

To:

1.  $f_{OSC}$  = crystal frequency;  $f_{OP}$  =  $f_{OSC}$  ÷ 2;  $t_{CYC}$  = 1 ÷  $f_{OP}$  (See Table 10-6. Control Timing ( $V_{DD}$  = 5.0 Vdc).)

Delete NOTE 2 at the bottom of the table.

16. Page 10-13, **Table 10-9. SIOP Timing (V<sub>DD</sub> = 3.3 Vdc)** — Change the first row as follows:

From:

Table 10-9. SIOP Timing ( $V_{DD} = 3.3 \text{ Vdc}$ )

| Characteristic                            | Symbol                                       | Min        | Max         | Unit                   |

|-------------------------------------------|----------------------------------------------|------------|-------------|------------------------|

| Frequency of Operation<br>Master<br>Slave | f <sub>SIOP(M)</sub><br>f <sub>SIOP(S)</sub> | 0.25<br>dc | 0.25<br>250 | f <sub>OP</sub><br>kHz |

To:

Table 10-9. SIOP Timing ( $V_{\rm DD}$  = 3.3 Vdc)

| Characteristic                            | Symbol                                       | Min                        | Max                        | Unit       |

|-------------------------------------------|----------------------------------------------|----------------------------|----------------------------|------------|

| Frequency of Operation<br>Master<br>Slave | f <sub>SIOP(M)</sub><br>f <sub>SIOP(S)</sub> | f <sub>OSC</sub> /64<br>dc | f <sub>osc</sub> /8<br>250 | MHz<br>kHz |

Change the note at the bottom of the table as follows:

From:

NOTE:  $f_{OP} = 1.0 \text{ MHz maximum}$

To:

NOTE:  $f_{OSC}$  = crystal frequency;  $f_{OP}$  =  $f_{OSC}$  ÷ 2;  $t_{CYC}$  = 1 ÷  $f_{OP}$  (See Table 10-7. Control Timing ( $V_{DD}$  = 3.3 Vdc).)

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (M) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### **Literature Distribution Centers:**

USA/EUROPE: : Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan.

ASIA-PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong