# DSP56L811

# 16-bit Digital Signal Processor User's Manual

Motorola, Incorporated Semiconductor Products Sector DSP Division 6501 William Cannon Drive West Austin, TX 78735-8598

# TABLE OF CONTENTS

| SECTIC   | ON 1 DSP56L811 OVERVIEW                      | . 1-1 |

|----------|----------------------------------------------|-------|

| 1.1      |                                              | . 1-3 |

| 1.2      | MANUAL ORGANIZATION                          | . 1-4 |

| 1.3      | MANUAL CONVENTIONS                           | . 1-5 |

| 1.4      | DSP56800 CORE DESCRIPTION                    | . 1-6 |

| 1.4.1    | Data ALU                                     |       |

| 1.4.2    | Address Generation Unit                      | 1-10  |

| 1.4.3    | Program Controller and Hardware Looping Unit | 1-10  |

| 1.4.4    | Address and Data Buses                       | 1-10  |

| 1.4.5    | Bus and Bit Manipulation Unit                | 1-11  |

| 1.4.6    | On-Chip Emulation (OnCE) Unit                |       |

| 1.5      | DSP56L811 ARCHITECTURE OVERVIEW              | 1-12  |

| 1.5.1    | DSP56L811 Peripheral Blocks                  | 1-13  |

| 1.5.1.1  | On-chip Memory                               | 1-14  |

| 1.5.1.2  | External Memory Interface                    | 1-14  |

| 1.5.1.3  | General Purpose I/O Module                   | 1-14  |

| 1.5.1.4  | Programmable I/O Module                      | 1-14  |

| 1.5.1.5  | Serial Peripheral Interface                  |       |

| 1.5.1.6  | Synchronous Serial Interface                 | 1-15  |

| 1.5.1.7  | General-Purpose Timer Module                 |       |

| 1.5.1.8  | On-chip Clock Synthesis Block                |       |

| 1.5.1.9  | COP/RTI Module                               |       |

| 1.5.1.10 |                                              |       |

| 1.5.2    | DSP56L811 Peripheral Interrupts              |       |

| 1.6      | CODE DEVELOPMENT ON THE DSP56L811            | 1-16  |

| SECTIC   | ON 2 PIN DESCRIPTIONS                        | . 2-1 |

| 2.1      |                                              | . 2-3 |

| 2.2      | PIN DESCRIPTIONS                             | . 2-6 |

| SECTIO  | ON 3 MEMORY CONFIGURATION               |        |

|---------|-----------------------------------------|--------|

|         | AND OPERATING MODES                     | 3-1    |

| 3.1     | INTRODUCTION                            | 3-3    |

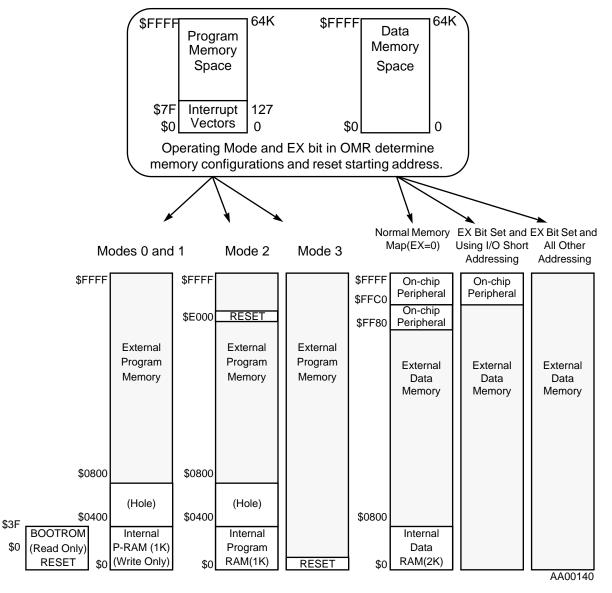

| 3.2     | DSP56L811 MEMORY MAP DESCRIPTION        | 3-3    |

| 3.2.1   | Program Memory Map                      | 3-6    |

| 3.2.2   | On-Chip Peripheral Memory Map           | 3-7    |

| 3.3     | DSP56L811 OPERATING MODES               | 3-9    |

| 3.3.1   | Bootstrap Mode (Mode 0)                 | . 3-10 |

| 3.3.2   | Bootstrap Mode (Mode 1)                 | . 3-10 |

| 3.3.3   | Normal Expanded Mode (Mode 2)           | . 3-10 |

| 3.3.4   | Development Mode (Mode 3)               |        |

| 3.4     | DSP56L811 BOOTSTRAPPING                 |        |

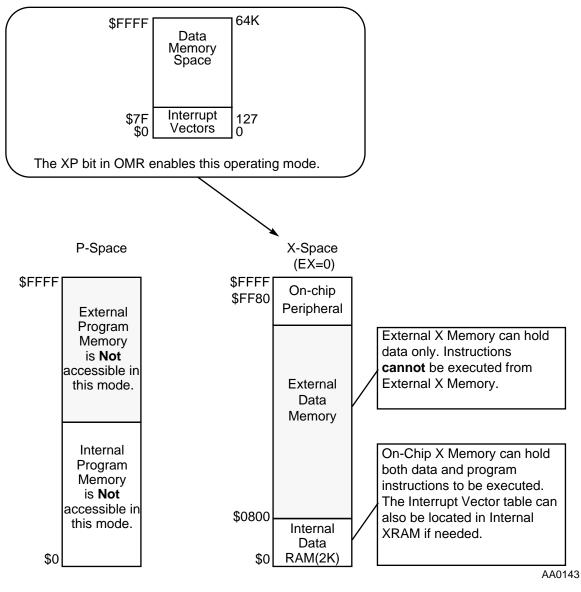

| 3.5     | EXECUTING PROGRAMS FROM XRAM            | . 3-12 |

| 3.5.1   | Description of the XRAM Execution Mode  | . 3-12 |

| 3.5.2   | Interrupts in the XRAM Execution Mode   | . 3-14 |

| 3.5.3   | Entering the XRAM Execution Mode        | . 3-14 |

| 3.5.4   | Exiting the XRAM Execution Mode         |        |

| 3.5.5   | Restrictions in the XRAM Execution Mode |        |

| 3.6     | DSP56L811 RESET AND INTERRUPT VECTORS   | . 3-15 |

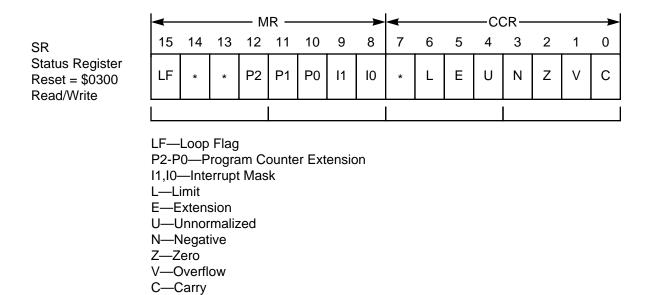

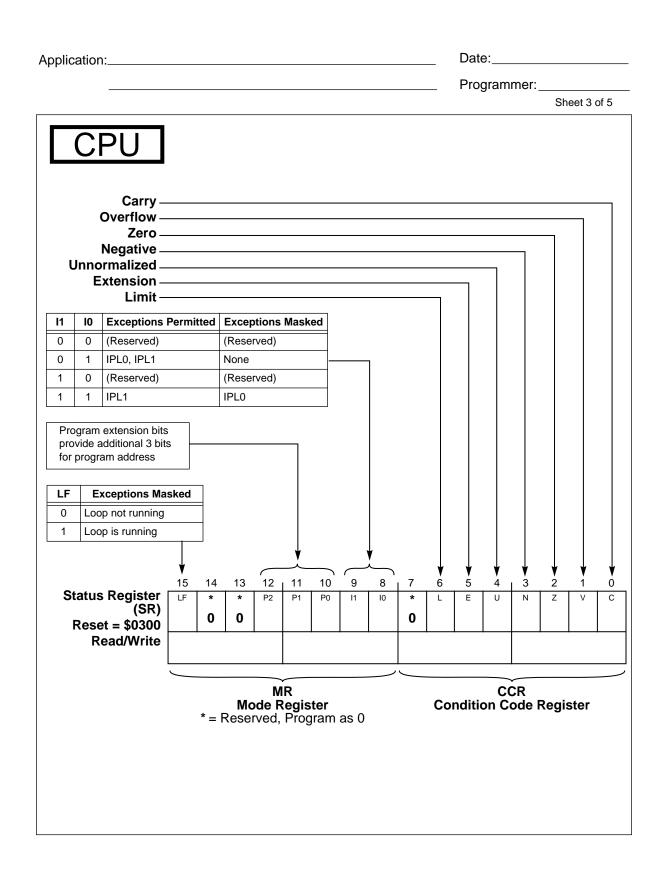

| 3.6.1   | DSP56L811 Status Register               | . 3-17 |

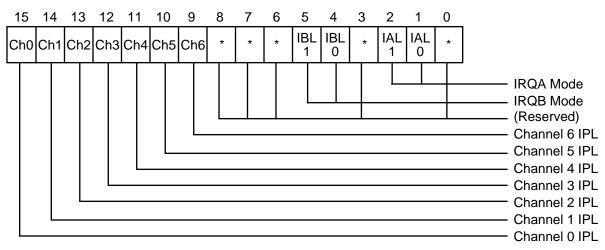

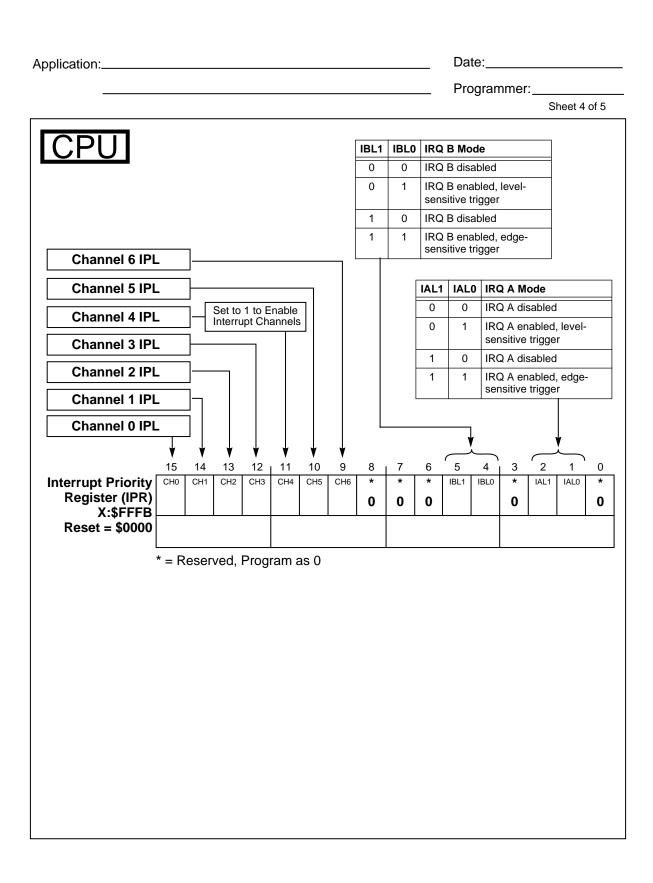

| 3.6.2   | DSP56L811 Interrupt Priority Register   | . 3-19 |

| SECTIO  | N 4 EXTERNAL MEMORY INTERFACE           | 4-1    |

| 4.1     | INTRODUCTION                            |        |

| 4.2     | EXTERNAL MEMORY PORT ARCHITECTURE       |        |

| 4.3     | EXTERNAL MEMORY PORT DESCRIPTION        |        |

| 4.3.1   | External Memory Port Programing Model   |        |

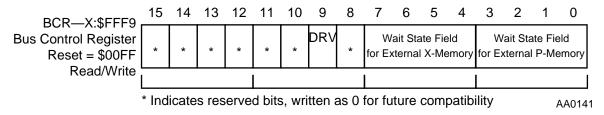

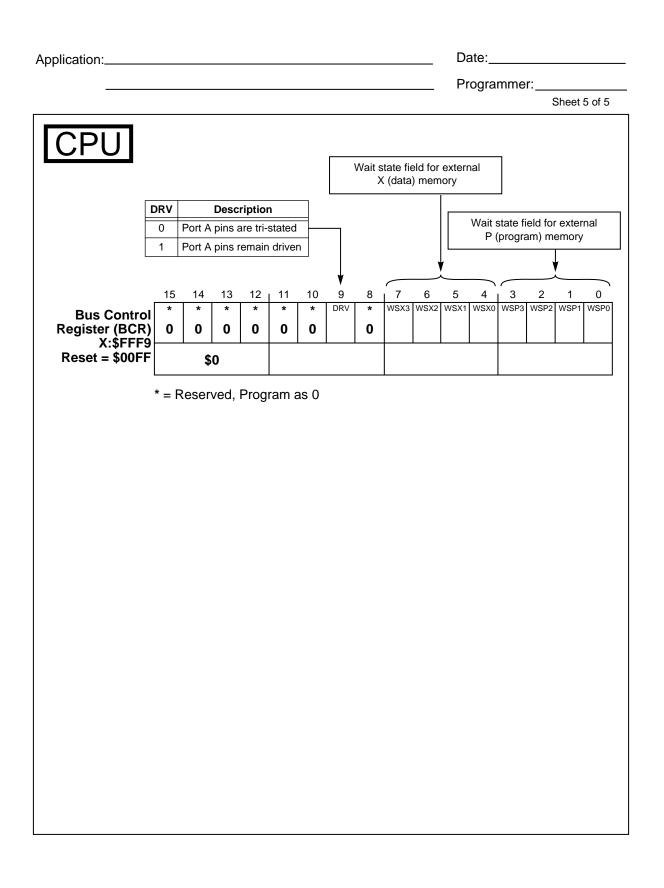

| 4.3.1.1 | Bus Control Register (BCR)              |        |

| 4.3.1.2 | Drive (DRV) Bit 9                       |        |

| 4.3.1.3 | Wait State X-Data Memory (WSX) Bits 7-4 |        |

| 4.3.1.4 | Wait State P Memory (WSPM) Bits 3-0     |        |

| 4.3.1.5 | Reserved BCR Register Bits              |        |

| -       | 5                                       | -      |

| 4.3.2   | Pins in Different Processing States           |

|---------|-----------------------------------------------|

| SECTIC  | ON 5 PORT B GPIO FUNCTIONALITY                |

| 5.1     | INTRODUCTION                                  |

| 5.2     | PORT B PROGRAMMING MODEL                      |

| 5.2.1   | Port B Data Direction Register (PBDDR)5-6     |

| 5.2.2   | Port B Data Register (PBD)                    |

| 5.2.2.1 | PBD Bit Values for General Purpose Inputs     |

| 5.2.2.2 | PBD Bit Values for General Purpose Outputs5-6 |

| 5.2.2.3 | PBD Bit Values for Interrupt Inputs           |

| 5.2.3   | Port B Interrupt Register (PBINT)5-7          |

| 5.2.3.1 | Interrupt Mask (MSK7-MSK0) Bits 15-8          |

| 5.2.3.2 | Interrupt Invert (INV7-INV0) Bits 7-05-8      |

| 5.3     | PORT B INTERRUPT GENERATION                   |

| 5.4     | PORT B PROGRAMMING EXAMPLES                   |

| 5.4.1   | Receiving Data on Port B5-10                  |

| 5.4.2   | Sending Data on Port B5-11                    |

| 5.4.3   | Looping Data on Port B                        |

| 5.4.4   | Generating Interrupts on Port B               |

| SECTIC  | ON 6 PORT C GPIO FUNCTIONALITY                |

| 6.1     | INTRODUCTION                                  |

| 6.2     | PORT C PROGRAMMING MODEL                      |

| 6.2.1   | Port C Control Register (PCC)6-5              |

| 6.2.2   | Port C Data Direction Register (PCDDR)6-6     |

| 6.2.3   | Port C Data Register (PCD)6-7                 |

| 6.3     | PORT C PROGRAMMING EXAMPLES                   |

| 6.3.1   | Receiving Data on Port C GPIO Pins            |

| 6.3.2   | Sending Data on Port C GPIO Pins              |

| 6.3.3   | Looping Data on Port C GPIO Pins              |

| SECTIC  | N 7 SERIAL PERIPHERAL INTERFACE               |

| 7.1     | INTRODUCTION                                  |

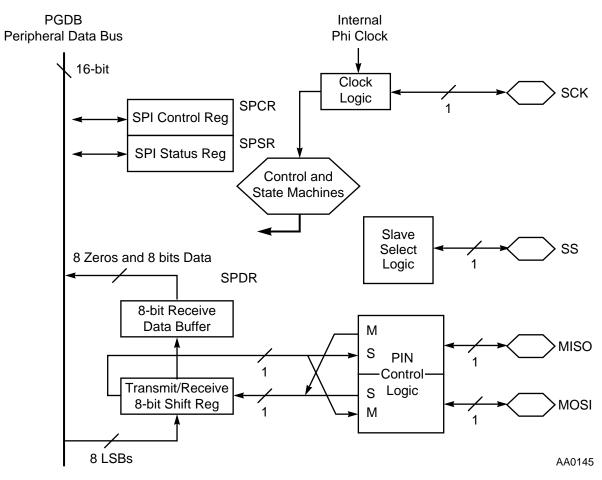

| 7.2     | SPI ARCHITECTURE7-5                           |

| 7.3     | SPI PROGRAMMING MODEL7-6                      |

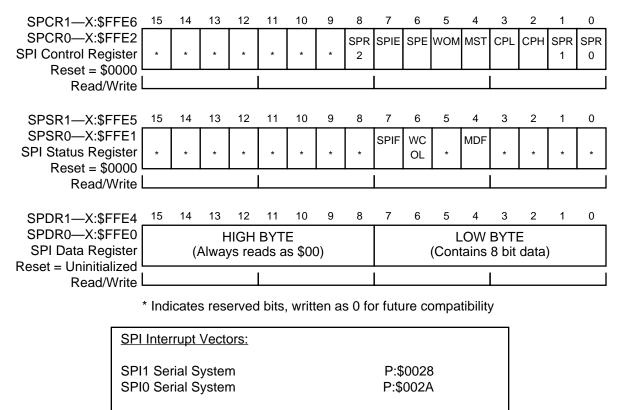

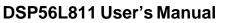

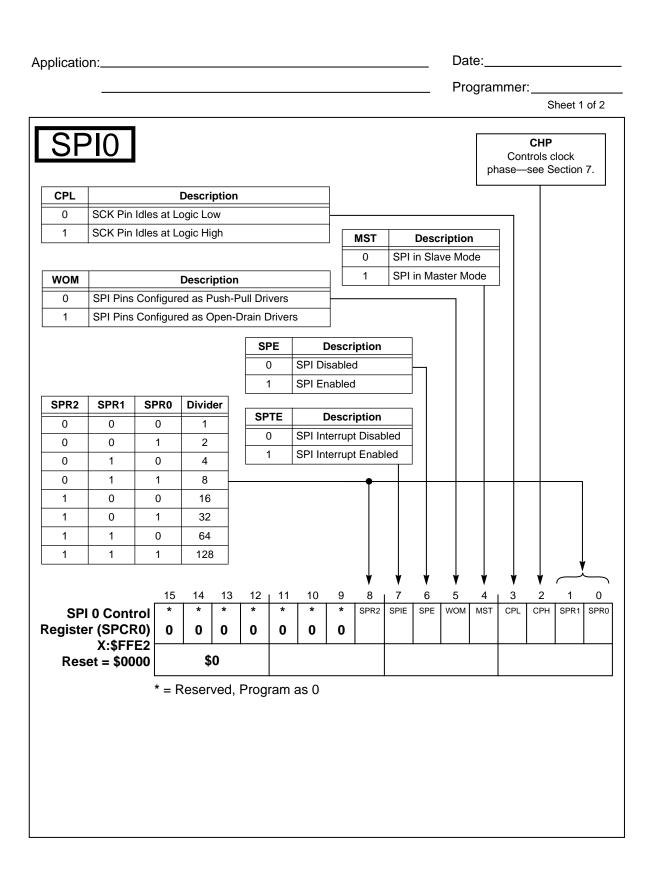

| 7.3.1   | SPI Control Registers (SPCR0 and SPCR1)7-7    |

| 7.3.1.1 | SPI Clock Rate Select (SPR2-0) Bits 8, 1-0 | 70           |

|---------|--------------------------------------------|--------------|

| 7.3.1.1 |                                            |              |

|         | SPI Interrupt Enable (SPIE) Bit 7          |              |

| 7.3.1.3 | SPI Enable (SPE) Bit 6                     | 7-9          |

| 7.3.1.4 | Wired-OR Mode (WOM) Bit 5.                 |              |

| 7.3.1.5 | Master Mode Select (MST) Bit 4             |              |

| 7.3.1.6 | Clock Polarity (CPL) Bit 3                 | -10          |

| 7.3.1.7 | Clock Phase (CPH) Bit 2                    |              |

| 7.3.1.8 | Reserved SPCR Register Bits                |              |

| 7.3.2   | SPI Status Register (SPSR0 and SPSR1)7     |              |

| 7.3.2.1 | SPI Interrupt Complete Flag (SPIF) Bit 7 7 | <b>'-10</b>  |

| 7.3.2.2 | Write Collision (WCOL) Bit 6               | '-11         |

| 7.3.2.3 | Mode Fault (MDF) Bit 4                     |              |

| 7.3.2.4 | Reserved SPSR Register Bits                |              |

| 7.3.3   | SPI Data Registers (SPDR0 and SPDR1)7      | '-11         |

| 7.4     | SPI DATA AND CONTROL PINS                  |              |

| 7.5     | SPI SYSTEM ERRORS7                         | <b>'-14</b>  |

| 7.5.1   | SPI Mode-Fault Error7                      | <b>'-1</b> 4 |

| 7.5.2   | SPI Write-Collision Error                  |              |

| 7.5.3   | SPI Overrun                                |              |

| 7.6     | CONFIGURING PORT C FOR SPI FUNCTIONALITY 7 |              |

| 7.6.1   | SPI Low Power Operation7                   | <b>'-17</b>  |

| 7.7     | PROGRAMMING EXAMPLES                       |              |

| 7.7.1   | Configuring an SPI Port as Master          |              |

| 7.7.2   | Configuring an SPI Port as Slave           |              |

| 7.7.3   | Sending Data from Master to Slave          |              |

|         |                                            |              |

| SECTIC  | ON 8 SYNCHRONOUS SERIAL INTERFACE          | 8-1          |

| 8.1     |                                            | 8-3          |

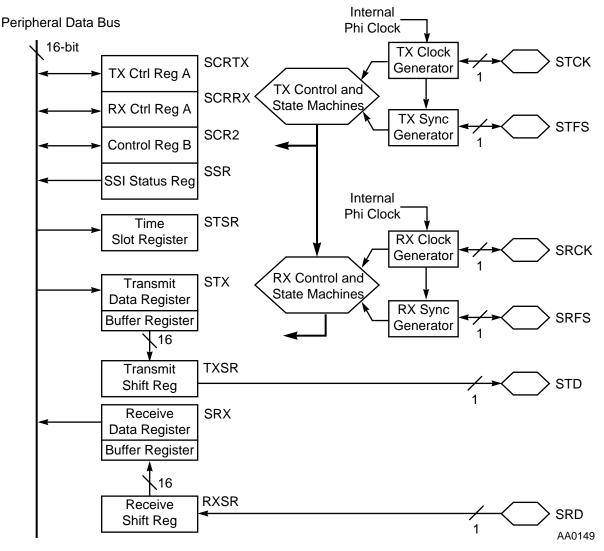

| 8.2     | SSI ARCHITECTURE                           |              |

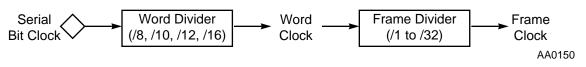

| 8.2.1   | SSI Clocking                               |              |

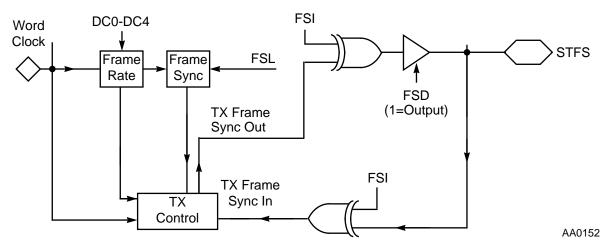

| 8.2.2   | SSI Clock and Frame Sync Generation        |              |

| 8.3     | SSI PROGRAMMING MODEL                      |              |

| 8.3.1   | SSI Transmit Shift Register (TXSR)         |              |

| 8.3.2   | SSI Transmit Data Buffer Register          |              |

| 8.3.3   | SSI Transmit Data Register (STX)           |              |

| 8.3.4   | SSI Receive Shift Register (RXSR)          |              |

| 0.0.1   |                                            | , , ,        |

| 8.3.5    | SSI Receive Data Buffer Register                | 8-11 |

|----------|-------------------------------------------------|------|

| 8.3.6    | SSI Receive Data Register (SRX)                 | 8-12 |

| 8.3.7    | SSI Transmit and Receive Control Registers      |      |

|          | (SCRTX and SCRRX)8-12                           |      |

| 8.3.7.1  | Prescaler Range (PSR) Bit 15                    | 8-12 |

| 8.3.7.2  | Word Length Control (WL1-WL0) Bits 14-13        | 8-13 |

| 8.3.7.3  | Frame Rate Divider (DC4-DC0) Bits 12-8          | 8-13 |

| 8.3.7.4  | Prescale Modulus Select (PM7-PM0) Bits 7-0      | 8-13 |

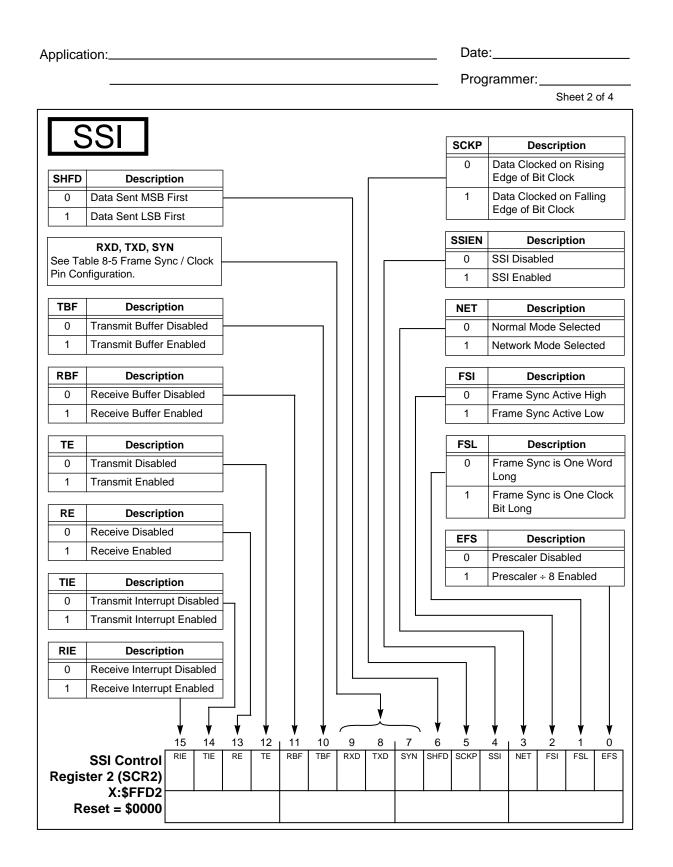

| 8.3.8    | SSI Control Register 2 (SCR2)                   |      |

| 8.3.8.1  | Receive Interrupt Enable (RIE) Bit 15           | 8-15 |

| 8.3.8.2  | Transmit Interrupt Enable (TIE) Bit 14          | 8-15 |

| 8.3.8.3  | Receive Enable (RE) Bit 13                      | 8-16 |

| 8.3.8.4  | Transmit Enable (TE) Bit 12                     | 8-16 |

| 8.3.8.5  | Receive Buffer Enable (RBF) Bit 11              | 8-17 |

| 8.3.8.6  | Transmit Buffer Enable (TBF) Bit 10             | 8-17 |

| 8.3.8.7  | Receive Direction (RXD) Bit 9                   | 8-17 |

| 8.3.8.8  | Transmit Direction (TXD) Bit 8                  | 8-18 |

| 8.3.8.9  | Synchronous Mode (SYN) Bit 7                    | 8-18 |

| 8.3.8.10 | Shift Direction (MSB/LSB Position) (SHFD) Bit 6 | 8-18 |

| 8.3.8.11 | Clock Polarity (SCKP) Bit 5                     |      |

| 8.3.8.12 | SSI Enable (SSIEN) Bit 4                        | 8-18 |

| 8.3.8.13 | Network Mode (NET) Bit 3                        | 8-19 |

| 8.3.8.14 | Frame Sync Invert (FSI) Bit 2                   | 8-19 |

| 8.3.8.15 | Frame Sync Length (FSL) Bit 1                   | 8-19 |

| 8.3.8.16 | Early Frame Sync (EFS) Bit 0                    | 8-19 |

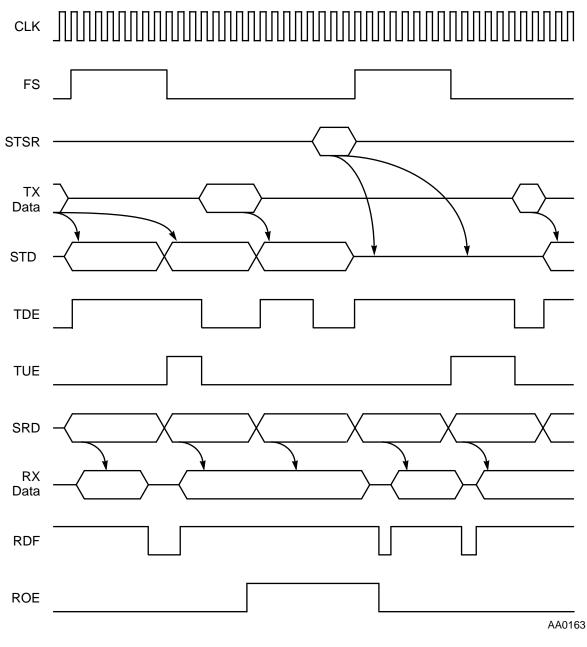

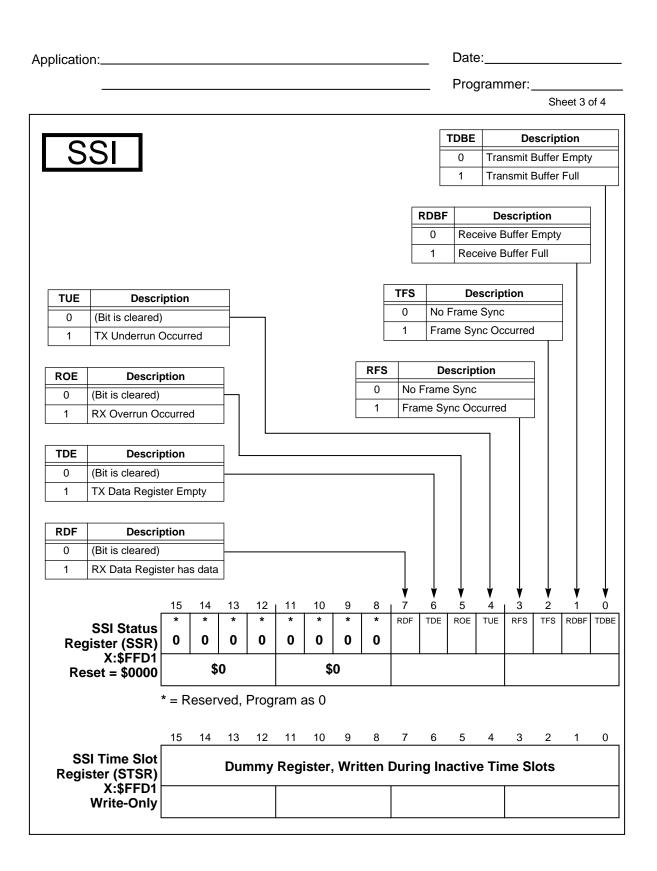

| 8.3.9    | SSI Status Register (SSR)                       | 8-19 |

| 8.3.9.1  | Receive Data Register Full (RDF) Bit 7          | 8-19 |

| 8.3.9.2  | Transmit Data Register Empty (TDE) Bit 6        | 8-20 |

| 8.3.9.3  | Receive Overrun Error (ROE) Bit 5               | 8-20 |

| 8.3.9.4  | Transmit Underrun Error (TUE) Bit 4             | 8-20 |

| 8.3.9.5  | Transmit Frame Sync (TFS) Bit 3                 |      |

| 8.3.9.6  | Receive Frame Sync (RFS) Bit 2                  | 8-21 |

| 8.3.9.7  | Receive Data Buffer Full (RDBF) Bit 1           | 8-21 |

| 8.3.9.8  | Transmit Data Buffer Empty (TDBE) Bit 0         | 8-22 |

| 8.3.9.9  | Reserved SSR Register Bits                      | 8-22 |

| 8.3.10   | SSI Time Slot Register (STSR)                   | 8-22 |

| 8.4     | SSI DATA AND CONTROL PINS                           | 8-22 |

|---------|-----------------------------------------------------|------|

| 8.4.1   | SSI Pin Definitions                                 |      |

| 8.5     | SSI OPERATING MODES                                 |      |

| 8.5.1   | Normal Mode.                                        |      |

| 8.5.1.1 | Normal Mode Transmit                                | 8-28 |

| 8.5.1.2 | Normal Mode Receive                                 | 8-29 |

| 8.5.2   | Network Mode                                        | 8-31 |

| 8.5.2.1 | Network Mode Transmit                               | 8-31 |

| 8.5.2.2 | Network Mode Receive                                | 8-32 |

| 8.5.3   | Gated Clock Operation                               |      |

| 8.6     | SSI RESET AND INITIALIZATION PROCEDURE              | 8-35 |

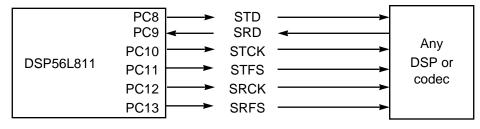

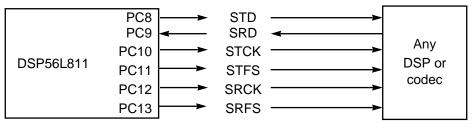

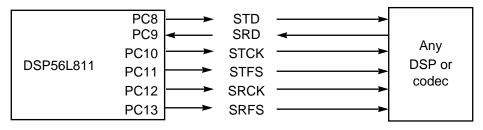

| 8.7     | CONFIGURING PORT C FOR SSI FUNCTIONALITY            | 8-36 |

| SECTIC  | ON 9 TIMERS                                         | 0_1  |

| 9.1     |                                                     |      |

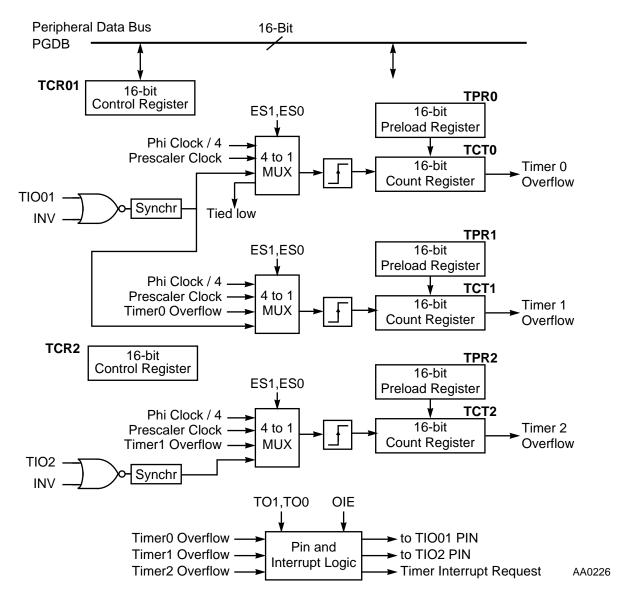

| 9.2     | TIMER PROGRAMMING MODEL.                            |      |

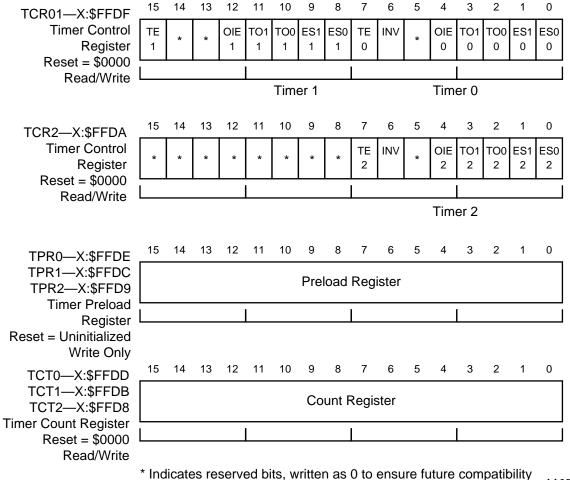

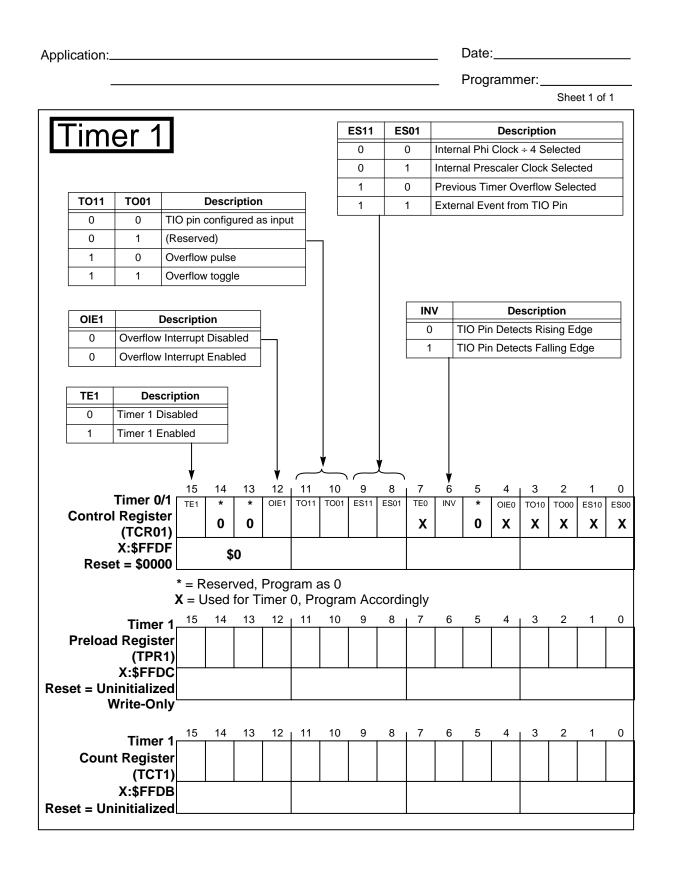

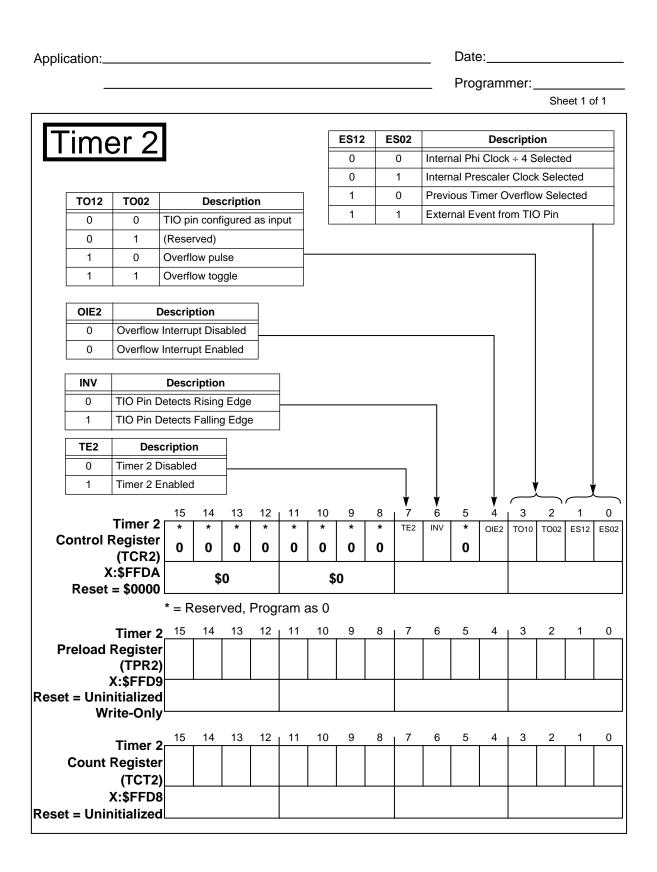

| 9.2.1   | Timer Control Registers (TCR01 and TCR2)            |      |

| 9.2.1.1 | Timer Enable (TE) Bit 15, Bit 7                     |      |

| 9.2.1.2 | Invert (INV) Bit 6                                  |      |

| 9.2.1.3 | Overflow Interrupt Enable (OIE) Bit 12, Bit 4       |      |

| 9.2.1.4 | Timer Output Enable (TO1-TO0) Bits 11-10, Bits 3-2. |      |

| 9.2.1.5 | Event Select (ES1-ES0) Bits 9-8, Bits 1-0           |      |

| 9.2.1.6 | Reserved TCR Register Bits                          |      |

| 9.2.2   | Timer Preload Register (TPR).                       |      |

| 9.2.3   | Timer Count Register (TCT)                          |      |

| 9.3     | TIMER RESOLUTION                                    |      |

| 9.4     | TIMER INTERRUPT PRIORITIES.                         |      |

| 9.5     | EVENT COUNTING WITH THE TIMER MODULE                | 9-11 |

| 9.6     | TIMER MODULE LOW POWER OPERATION                    | 9-19 |

| 9.6.1   | Turning Off the Entire Timer Module                 | 9-19 |

| 9.6.2   | Turning Off Any Timer Not in Use                    | 9-20 |

| 9.6.3   | Low Frequency Timer Operation.                      | 9-20 |

| 9.6.4   | Running A Timer in Wait Mode                        |      |

| 9.6.5   | Running A Timer in Stop Mode                        | 9-20 |

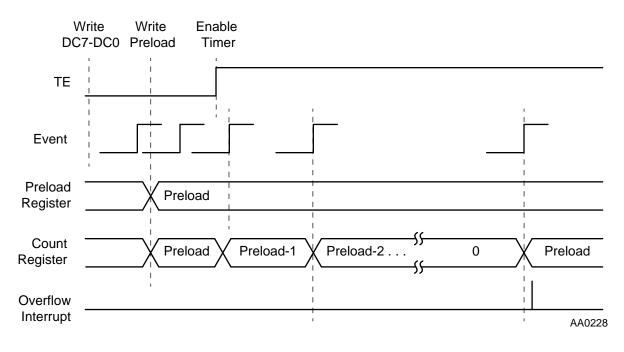

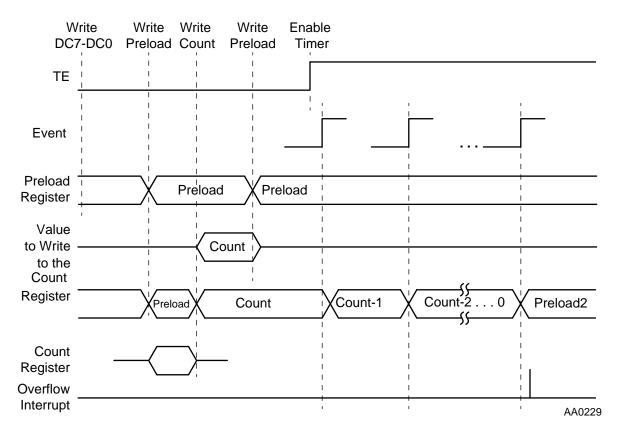

| 9.7     | TIMER MODULE TIMING DIAGRAMS                        | 9-21 |

| <b>SECTION 10 ON-CHIP CL</b>        | OCK SYNTHESIS 10-1                        |

|-------------------------------------|-------------------------------------------|

|                                     |                                           |

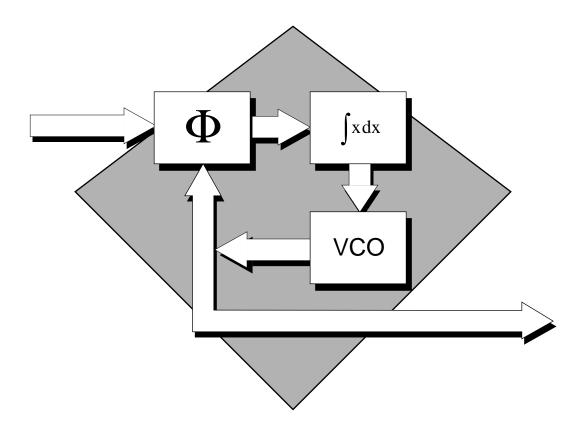

| 10.2 DSP56L811 TIMIN                | G SYSTEM ARCHITECTURE 10-3                |

|                                     |                                           |

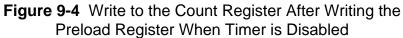

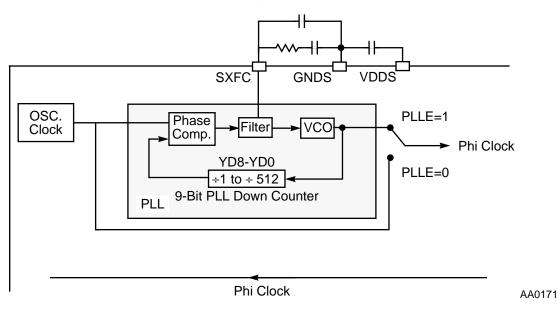

| 10.2.2 Phase-Locked L               | oop (PLL)10-5                             |

|                                     |                                           |

| 10.2.4 Clockout MUX .               |                                           |

| <b>U</b>                            | rs10-7                                    |

|                                     | IS PROGRAMMING MODEL                      |

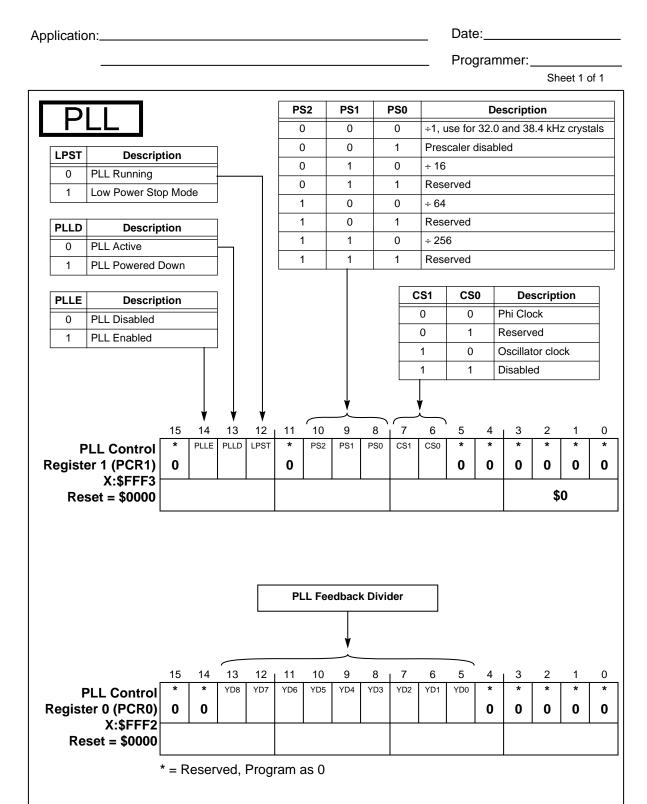

|                                     | gister 1 (PCR1) 10-8                      |

| 10.3.1.1 PLL Enable (<br>and 1310-8 | PLLE) and PLL Power Down (PLLD) Bits 14   |

|                                     | top (LPST) Bit 12                         |

|                                     | rider (PS2-PS0) Bits 10-8                 |

|                                     | (CS1-CS0) Bits 7-6 10-10                  |

|                                     | R1 Register Bits                          |

|                                     | gister 0 (PCR0)                           |

|                                     | vider (YD8-YD0) Bits 13-5                 |

|                                     | R0 Register Bits                          |

| 10.4 DSP56L811 STOP                 | AND WAIT MODES10-12                       |

| 10.4.1 Options for Cloc             | k Synthesis in Stop Mode10-12             |

| 10.4.2 Stop Mode—PL                 | L, COP, Realtime Clock, Timer Module and  |

| CLKO Pin Enab                       | led10-13                                  |

| 10.4.3 Stop Mode—CC<br>10-13        | OP, Realtime Clock and CLKO Pin Enabled . |

| 10.4.4 Stop Mode—PL                 | L and CLKO Pin Enabled 10-14              |

|                                     | KO Pin Enabled 10-14                      |

| -                                   | erything Disabled                         |

| •                                   |                                           |

|                                     | ng Sequence                               |

| -                                   | LL Frequency                              |

| •••                                 | PLL Before Entering Stop Mode 10-16       |

| •                                   | V-POWER OPERATION                         |

| 10.6.1 Turning Off the              | Entire Clock Synthesis Module 10-17       |

| 10.6.2 Turning Off the Prescaler Divider When Not in Use 10-1 | 7  |

|---------------------------------------------------------------|----|

| 10.6.3 Turning Off the PLL When Not in Use                    | 7  |

| 10.6.4 Turning Off the CLKO Pin When Not in Use 10-1          | 8  |

|                                                               |    |

| SECTION 11 COP/RTI MODULE 11-                                 | 1  |

| 11.1 INTRODUCTION 11-                                         | .3 |

| 11.2 COP AND RTI 11-                                          | .3 |

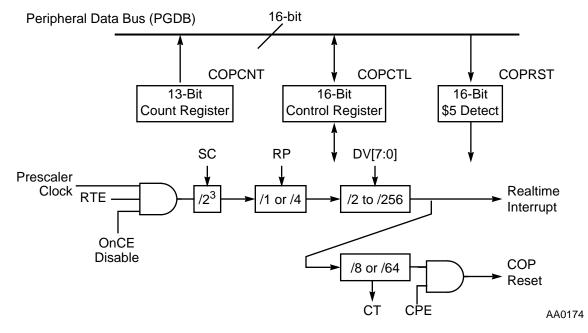

| 11.2.1 COP and Realtime Timer Architecture                    |    |

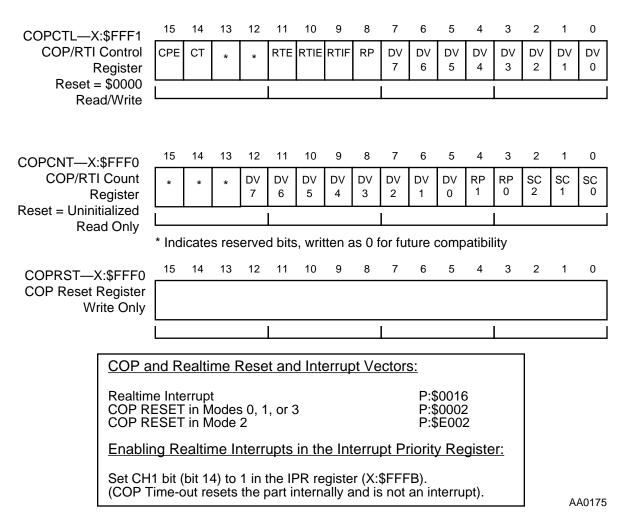

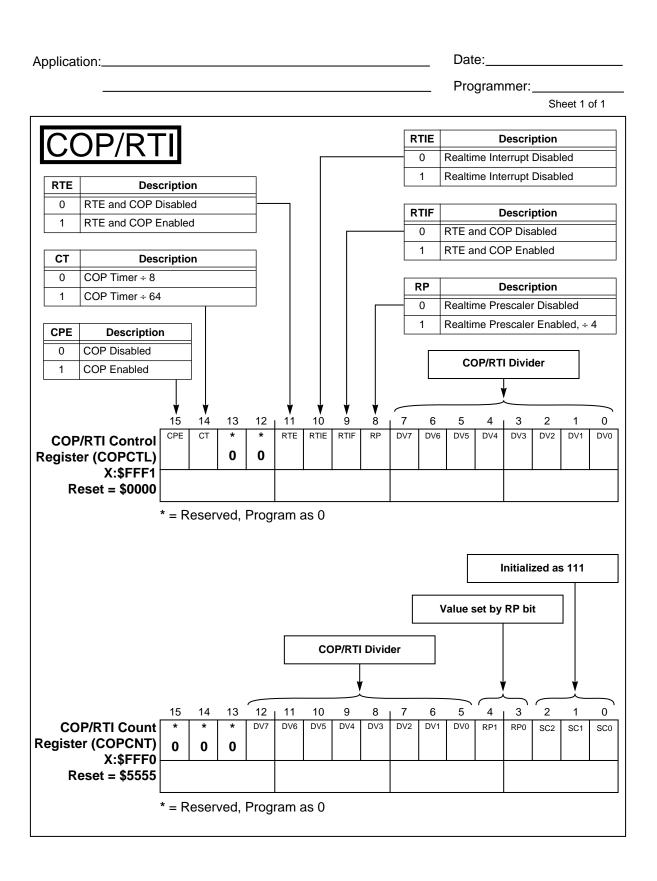

| 11.2.2 COP and Realtime Timer Programming Model 11-           |    |

| 11.2.3 COP and RTI Control Register (COPCTL) 11-              | -6 |

| 11.2.3.1 COP Enable (CPE) Bit 15                              |    |

| 11.2.3.2 COP Timer Divider (CT) Bit 14 11-                    | 7  |

| 11.2.3.3 Realtime Timer Enable (RTE) Bit 11 11-               | 7  |

| 11.2.3.4 Realtime Timer Interrupt Enable (RTIE) Bit 10 11-    | 7  |

| 11.2.3.5 Realtime Timer Interrupt Flag (RTIF) Bit 9 11-       | .8 |

| 11.2.3.6 Realtime Prescaler (RP) Bit 8 11-                    | .8 |

| 11.2.3.7 Realtime/COP Divider (DV7-DV0) Bits 7-0 11-          | .8 |

| 11.2.3.8 Reserved COPCTL Register Bits                        | .8 |

| 11.2.4 COP and RTI Count Register (COPCNT) 11-                | .8 |

| 11.2.4.1 Realtime/COP Divider (DV7-DV0) Bits 12-5 11-         | .9 |

| 11.2.4.2 Realtime Prescaler (RP) Bits 4-3                     | .9 |

| 11.2.4.3 Scaler (SC2-SC0) Bits 2-0                            | .9 |

| 11.2.4.4 Reserved COPCNT Register Bits                        | .9 |

| 11.2.5 COP Reset Register (COPRST) 11-                        | .9 |

| 11.3 PROGRAMMING THE COP AND RTI TIMERS 11-1                  | 0  |

| 11.3.1 COP and Realtime Timer Resolution 11-1                 |    |

| 11.3.2 COP/Realtime Timer Low Power Operation 11-1            | 1  |

| 11.3.3 Programming Example 11-1                               | 2  |

|                                                               |    |

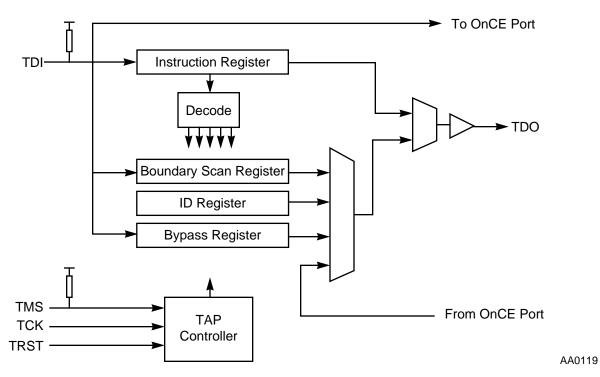

| SECTION 12 JTAG PORT                                          |    |

| 12.1 INTRODUCTION                                             |    |

| 12.2 JTAG PORT ARCHITECTURE                                   |    |

| 12.3 JTAG/ONCE PORT PINOUT                                    |    |

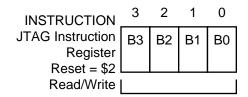

| 12.4 JTAG REGISTERS                                           |    |

| 12.4.1 JTAG Instruction Register and Decoder                  |    |

| 12.4.1.1 EXTEST (B[3:0]=0000)                                 | 8  |

| 12.4.1.2 | SAMPLE/PRELOAD (B[3:0]=0001)      |       |

|----------|-----------------------------------|-------|

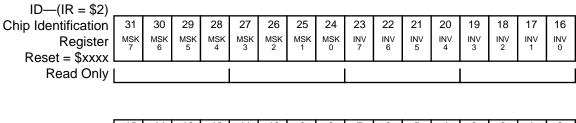

| 12.4.1.3 | IDCODE (B[3:0]=0010)              |       |

| 12.4.1.4 | EXTEST_PULLUP (B[3:0]=0011)       |       |

| 12.4.1.5 | HIGHZ (B[3:0]=0100)               |       |

| 12.4.1.6 | CLAMP (B[3:0]=0101)               |       |

| 12.4.1.7 | ENABLE_ONCE (B[3:0]=0110)         |       |

| 12.4.1.8 | DEBUG_REQUEST (B[3:0]=0111)       |       |

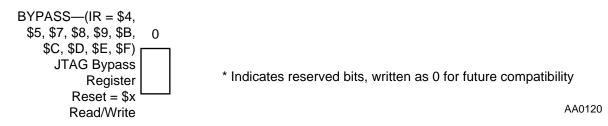

| 12.4.1.9 | BYPASS (B[3:0]=1111)              |       |

| 12.4.2   | JTAG Chip Identification Register |       |

| 12.4.3   | JTAG Boundary-Scan Register       |       |

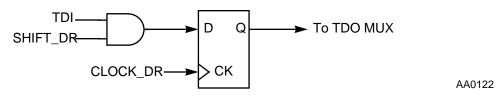

| 12.4.4   | JTAG Bypass Register              |       |

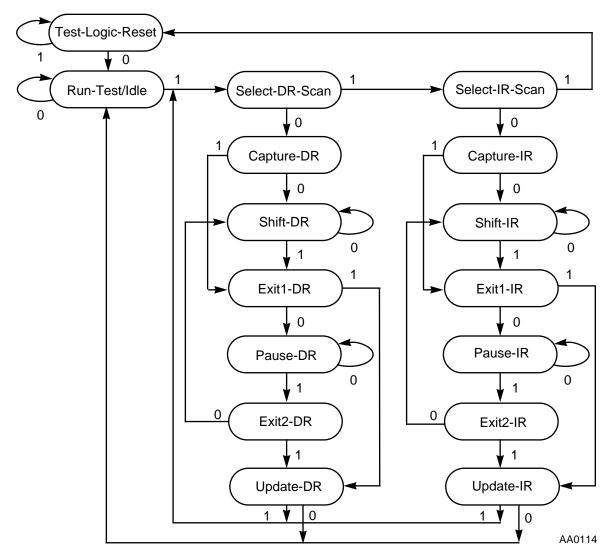

| 12.4.5   | TAP Controller                    |       |

| 12.5 DS  | SP56L811 RESTRICTIONS             | 12-18 |

| APPENDIX | A BOOTSTRAP PROGRAM               | A-1   |

| APPENDIX | B PROGRAMMER'S SHEETS             | B-1   |

| INDEX    |                                   | I-1   |

# **LIST OF FIGURES**

| Figure 1-1 | DSP56800 Core Block Diagram                                           |

|------------|-----------------------------------------------------------------------|

| Figure 1-2 | DSP56800 Bus Block Diagram1-8                                         |

| Figure 1-3 | DSP56L811 Functional Block Diagram                                    |

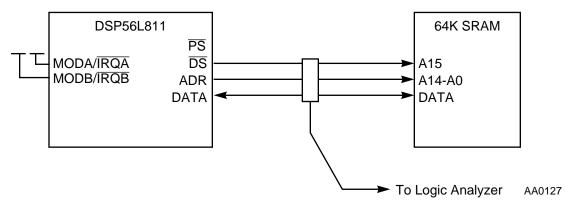

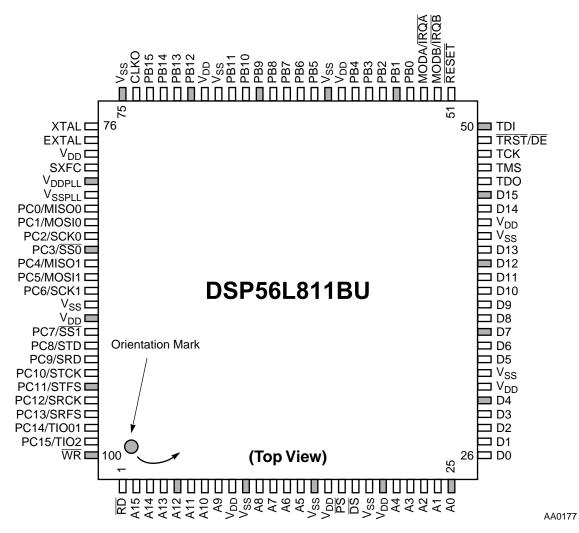

| Figure 1-4 | Example of Code Development with Visibility on All Memory<br>Accesses |

| Figure 2-1 | Top View of the DSP56L811 100-pin Plastic Thin Quad<br>Flat Package   |

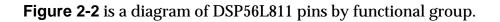

| Figure 2-2 | Functional Group Pin Allocations                                      |

| Figure 3-1 | DSP56L811 On-chip Memory Map                                          |

| Figure 3-2 | Bus Control Register Programming Model                                |

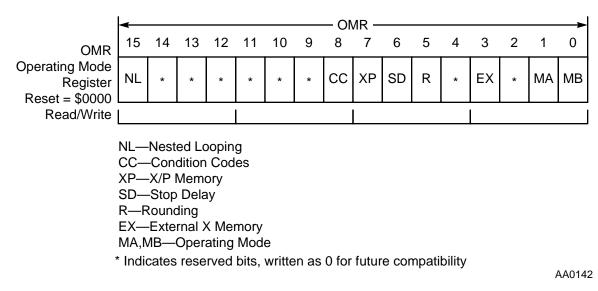

| Figure 3-3 | Operating Mode Register Programming Model                             |

| Figure 3-4 | DSP56L811 Memory Map (XRAM Execution Mode)                            |

| Figure 3-5 | Status Register Programming Model                                     |

| Figure 3-6 | DSP56L811 Interrupt Priority Register (IPR), X:\$FFFB 3-19            |

| Figure 4-1 | DSP56L811 Input/Output Block Diagram                                  |

| Figure 4-2 | External Memory Port Programming Model 4-5                            |

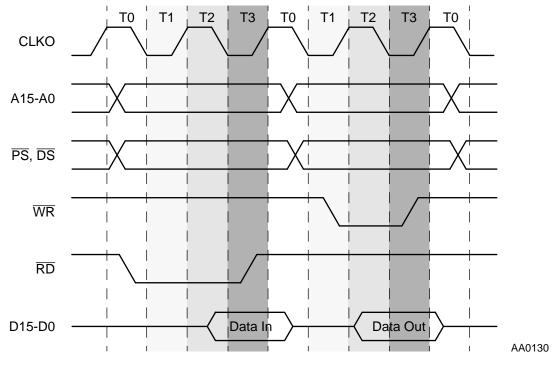

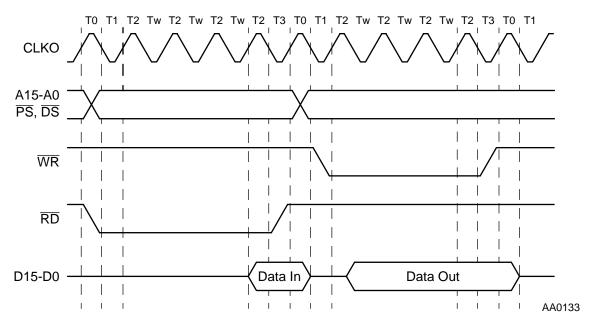

| Figure 4-3 | Bus Operation (Read/Write, Zero Wait States)                          |

| Figure 4-4 | Bus Operation (Read/Write—Three Wait States) 4-8                      |

| Figure 5-1 | DSP56L811 Input/Output Block Diagram                                  |

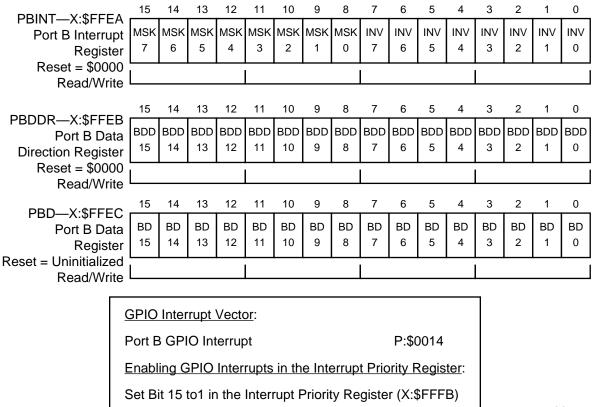

| Figure 5-2 | DSP56L811 Port B Programming Model                                    |

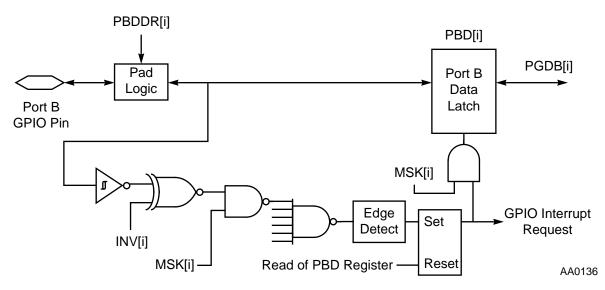

| Figure 5-3 | Port B interrupt Block Diagram5-9                                     |

| Figure 6-1  | DSP56L811 Input/Output Block Diagram 6-4                  |

|-------------|-----------------------------------------------------------|

| Figure 6-2  | DSP56L811 Port C Programming Model 6-5                    |

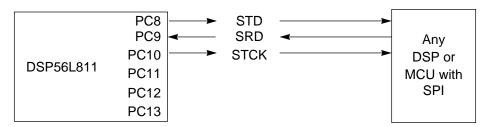

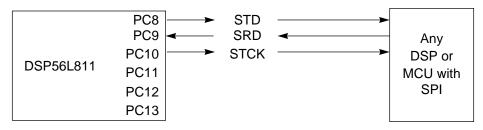

| Figure 7-1  | DSP56L811 Input/Output Block Diagram 7-4                  |

| Figure 7-2  | SPI Block Diagram                                         |

| Figure 7-3  | SPI Programming Model                                     |

| Figure 8-1  | DSP56L811 Input/Output Block Diagram 8-4                  |

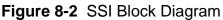

| Figure 8-2  | SSI Block Diagram 8-5                                     |

| Figure 8-3  | SSI Clocking 8-6                                          |

| Figure 8-4  | SSI Transmit Clock Generator Block Diagram 8-7            |

| Figure 8-5  | SSI Transmit Frame Sync Generator Block Diagram 8-7       |

| Figure 8-6  | SSI Programming Model—Register Set 8-9                    |

| Figure 8-7  | SSI Interrupt Vectors                                     |

| Figure 8-8  | SSI Bit Clock Equation 8-13                               |

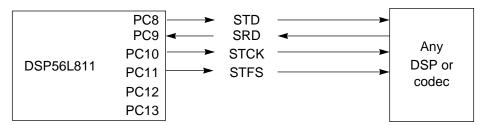

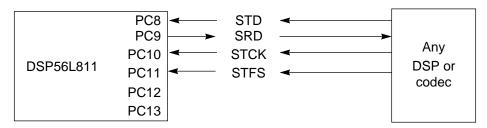

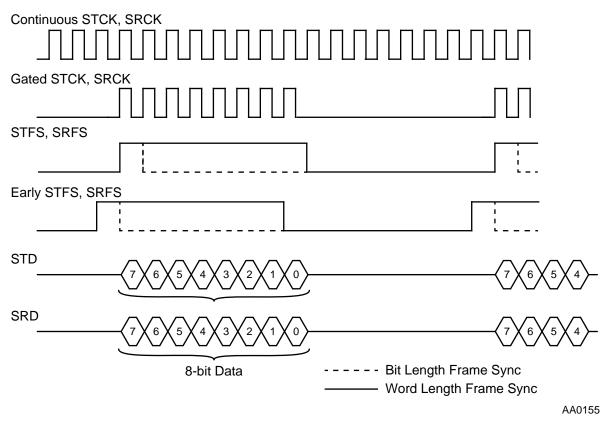

| Figure 8-9  | Asynchronous SSI Configurations—Continuous Clock 8-23     |

| Figure 8-10 | Synchronous SSI Configurations—Continuous and Gated Clock |

| Figure 8-11 | Serial Clock and Frame Sync Timing 8-26                   |

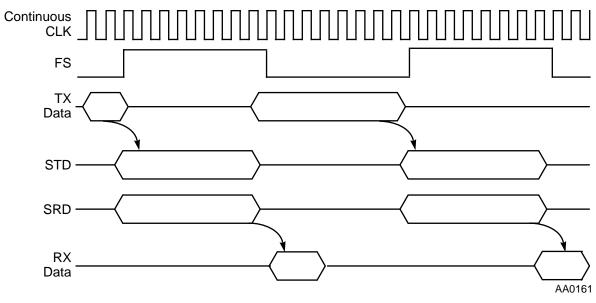

| Figure 8-12 | Normal Mode Timing—Continuous Clock 8-30                  |

| Figure 8-13 | Normal Mode Timing—Gated Clock 8-30                       |

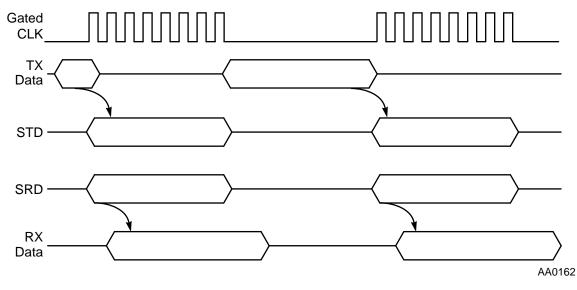

| Figure 8-14 | Network Mode Timing—Continuous Clock 8-34                 |

| Figure 9-1  | General Purpose Timer Module 9-4                          |

| Figure 9-2  | General Purpose Timer Programming Model 9-5               |

| Figure 9-3  | Standard Timer Operation with Overflow Interrupt 9-21                                    |

|-------------|------------------------------------------------------------------------------------------|

| Figure 9-4  | Write to the Count Register After Writing the Preload Register<br>When Timer is Disabled |

| Figure 10-1 | DSP56L811 Timing System                                                                  |

| Figure 10-2 | PLL Block Diagram                                                                        |

| Figure 10-3 | Prescaler Clock Equations                                                                |

| Figure 10-4 | Clock Synthesis Programming Model 10-8                                                   |

| Figure 11-1 | Realtime and COP Timer Block Diagram                                                     |

| Figure 11-2 | Realtime Interrupt and COP Timer Programming Model 11-6                                  |

| Figure 12-1 | JTAG Block Diagram 12-5                                                                  |

| Figure 12-2 | JTAG Port Programming Model 12-7                                                         |

| Figure 12-3 | Bypass Register                                                                          |

| Figure 12-4 | Chip Identification Register Configuration                                               |

| Figure 12-5 | TAP Controller State Diagram                                                             |

# LIST OF TABLES

| Table 1-1  | High True / Low True Signal Conventions                 |

|------------|---------------------------------------------------------|

| Table 1-2  | Data Buses                                              |

| Table 2-1  | Functional Group Pin Allocations 2-5                    |

| Table 2-2  | Power Pins 2-6                                          |

| Table 2-3  | Ground Pins                                             |

| Table 2-4  | PLL and Clock Pins 2-6                                  |

| Table 2-5  | Address Bus Pins 2-7                                    |

| Table 2-6  | Data Bus Pins                                           |

| Table 2-7  | Bus Control Pins 2-8                                    |

| Table 2-8  | Interrupt and Mode Control Pins                         |

| Table 2-9  | Programmable Interrupt GPIO Pins                        |

| Table 2-10 | Dedicated General Purpose Input/Output (GPIO) Pins 2-10 |

| Table 2-11 | Serial Peripheral Interface (SPI0 and SPI1) Pins 2-11   |

| Table 2-12 | Synchronous Serial Interface (SSI) Pins                 |

| Table 2-13 | Timer Module Pins                                       |

| Table 2-14 | JTAG/On-Chip Emulation (OnCE) Pins                      |

| Table 3-1  | DSP56L811 I/O and On-Chip Peripheral Memory Map 3-7     |

| Table 3-2  | DSP56L811 Program RAM Chip Operating Modes 3-9          |

| Table 3-3  | Interrupt Priority Structure                            |

| Table 3-4  | Reset and Interrupt Vector Map 3-16                     |

| Table 3-5 | Interrupt Mask Bit Definition 3-18                                |

|-----------|-------------------------------------------------------------------|

| Table 4-1 | Programming WSX Bits for Wait States                              |

| Table 4-2 | Programming WSP Bits for Wait States                              |

| Table 4-3 | Port A Operation with DRV Bit Set to 0 4-9                        |

| Table 4-4 | Port A Operation with DRV Bit Set to 1 4-9                        |

| Table 5-1 | PBDDR Bit Definition                                              |

| Table 5-2 | Reading the PBD Register                                          |

| Table 5-3 | MSK Bit Definition                                                |

| Table 5-4 | INV Bit Definition                                                |

| Table 6-1 | PCC Bit Definition                                                |

| Table 6-2 | PCDDR Bit Definition                                              |

| Table 7-1 | SPR Divider Programming                                           |

| Table 7-2 | SPI Interrupt                                                     |

| Table 7-3 | SPI Mode Programming7-10                                          |

| Table 7-4 | PCC Register Programming for the SS Pin                           |

| Table 8-1 | SSI Data Word Lengths 8-13                                        |

| Table 8-2 | SSI Bit Clock as a Function of Phi Clock and Prescale Modulus8-14 |

| Table 8-3 | SSI Receive Data Interrupts                                       |

| Table 8-4 | SSI Transmit Data Interrupts 8-16                                 |

| Table 8-5 | Frame Sync / Clock Pin Configuration                              |

| Table 8-6 | SSI Operating Modes8-27                                           |

| Table 8-7 | SSI Control Bits Requiring Reset Before Change                    |

| Table 9-1  | Timer Control Registers TCR01 and TCR02                          |

|------------|------------------------------------------------------------------|

| Table 9-2  | INV Bit Definition                                               |

| Table 9-3  | Timer Interrupt Vectors                                          |

| Table 9-4  | TIO Pin Function                                                 |

| Table 9-5  | ES Bit Definition                                                |

| Table 9-6  | Timer Range and Resolution                                       |

| Table 9-7  | Timer Interrupt Priorities                                       |

| Table 10-1 | PLL Operations                                                   |

| Table 10-2 | PS Divider Programming 10-10                                     |

| Table 10-3 | CLKOUT Pin Control                                               |

| Table 11-1 | COP Timer Divider Definition 11-7                                |

| Table 11-2 | Realtime Prescaler Definition 11-8                               |

| Table 11-3 | Realtime Prescaler Bits in COPCNT 11-9                           |

| Table 11-4 | COP Timer Range and Resolution 11-11                             |

| Table 12-1 | JTAG Pin Descriptions 12-6                                       |

| Table 12-2 | JTAG Instruction Register Encodings 12-8                         |

| Table 12-3 | Device ID Register Bit Assignment 12-12                          |

| Table 12-4 | Boundary-Scan Register Contents for DSP56L811 12-13              |

| Table B-1  | Instruction Set Summary B-3                                      |

| Table B-2  | Condition Code Register (CCR) Symbols (Standard Definitions) B-8 |

| Table B-3  | Condition Code Register Notation B-8                             |

| Table B-4  | Interrupt Priority Structure                                     |

| Table B-5 | Reset and Interrupt Vectors                       | B-9 |

|-----------|---------------------------------------------------|-----|

| Table B-6 | DSP56L811 I/O and On-Chip Peripheral Memory Map B | -11 |

| Table B-7 | List of Programmer's SheetsB                      | -13 |

# LIST OF EXAMPLES

| Example 1-1  | Sample Code Listing 1-5                       |

|--------------|-----------------------------------------------|

| Example 1-2  | On-Chip and Off-Chip Instruction Fetches 1-17 |

| Example 5-1  | Receiving Data on Port B 5-10                 |

| Example 5-2  | Sending Data on Port B 5-11                   |

| Example 5-3  | Loop-back Example 5-13                        |

| Example 5-4  | Generating Interrupts on Port B 5-15          |

| Example 6-1  | Receiving Data on Port C GPIO Pins            |

| Example 6-2  | Sending Data on Port C GPIO Pins 6-9          |

| Example 6-3  | Loop-back Example 6-11                        |

| Example 7-1  | Configuring an SPI Port as Master             |

| Example 7-2  | Configuring an SPI Port as Slave              |

| Example 7-3  | Sending Data from Master to Slave             |

| Example 9-1  | Counting Events on a Pin 9-12                 |

| Example 9-2  | Decrementing to 0 and Generating an Interrupt |

| Example 9-3  | Timer Using 25% Duty Cycle                    |

| Example 10-1 | Programming the PLL 10-15                     |

| Example 11-1 | Sending a COP Reset 11-12                     |

| Example A-1  | DSP56L811 Bootstrap Code A-4                  |

# SECTION 1 DSP56L811 OVERVIEW

| 1.1 |                                     | 1-3 |

|-----|-------------------------------------|-----|

| 1.2 | MANUAL ORGANIZATION                 | 1-4 |

| 1.3 | MANUAL CONVENTIONS                  | 1-5 |

| 1.4 | DSP56800 CORE DESCRIPTION           | 1-6 |

| 1.5 | DSP56L811 ARCHITECTURE OVERVIEW 1   | -12 |

| 1.6 | CODE DEVELOPMENT ON THE DSP56L811 1 | -16 |

# 1.1 INTRODUCTION

This manual describes the DSP56L811 16-bit digital signal processor (DSP), its memory and operating modes, and its peripheral modules. This manual is intended to be used with the *DSP56800 Family Manual (DSP56800FAM/AD)*, which describes the central processing unit, programming models, and instruction set details. The *DSP56L811 Data Sheet (DSP568L11/D)* provides electrical specifications, timing, pinout, and packaging descriptions. These documents as well as Motorola's DSP development tools can be obtained through a local Motorola Semiconductor Sales Office or authorized distributor.

To receive the latest information, access the Motorola DSP home page located at http://motserv.indirect.com/dsp/DSPhome.html

The DSP56L811 is a member of the DSP56800 core-based family of DSPs. This general-purpose DSP combines processing power with configuration flexibility, making it an excellent cost-effective solution for signal processing and control functions. To achieve its design goals, the DSP56L811 uses an efficient MPU-style, general-purpose, 16-bit DSP core, program and data memories, and support circuitry.

The central processing unit, the DSP56800 core, consists of three execution units operating in parallel, allowing up to six operations during each instruction cycle. The MPU-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set is also highly efficient for C compilers.

The DSP56L811 supports program execution from internal or external memories. Two data operands can be accessed per instruction cycle from the on-chip data RAM. The programmable peripherals and ports provide support for interfacing multiple external devices such as codecs, microprocessors, or other DSPs. The DSP56L811 also provides 16 to 32 GPIO lines, depending on how peripherals are configured, and two external dedicated interrupt lines. Because of its configuration flexibility, compact program code, and low cost, the DSP56800 core family is well-suited for cost-sensitive applications including digital wireless messaging, digital answering machines/feature phones, wireline and wireless modems, servo and AC motor control, and digital cameras.

#### **Manual Organization**

# 1.2 MANUAL ORGANIZATION

This manual is arranged in the following sections:

- *Section 1—Introduction* provides a brief overview of the DSP56L811, describes the structure of this document, and lists other documentation necessary to use the DSP56L811.

- *Section 2—Pin Descriptions* provides a description of the pins on the DSP56L811 chip and how the pins are grouped into the various interfaces.

- *Section 3—Memory Configuration and Operating Modes* describes the on-chip memory, structures, registers, and interfaces.

- *Section 4—External Memory Interface* describes the DSP56L811 external memory interface, which is also referred to as Port A.

- *Section 5—Port B GPIO Functionality* describes the dedicated GPIO interface, which is also referred to as Port B.

- *Section 6—Port C* describes the 16 dual-function pins that constitute Port C; this section defines the GPIO functions, and sections 5, 10, and 11 describe these pins' alternate functionality.

- *Section 7—Serial Peripheral Interface* describes the Serial Peripheral Interface (SPI), which communicates with external devices such as LCDs and MCUs, and is a part of Port C.

- *Section 8—Synchronous Serial Interface* describes the Synchronous Serial Interface (SSI), which communicates with devices such as codecs, other DSPs, microprocessors, and peripherals, to provide the primary data input path, and is a part of Port C.

- *Section 9—Timers* describes the three internal timer/counter devices that are a part of Port C.

- *Section 10—On-Chip Clock Synthesis* describes the internal oscillator, PLL, and timer distribution chain for the DSP56L811 chip.

- *Section 11—COP/RTI Module* describes the on-chip watchdog timer and the realtime interrupt generator.

- Section 12—JTAG Port describes the specifics of the DSP56L811's JTAG port. The OnCE<sup>™</sup> module, which is accessed through the JTAG port, is described in the DSP56800 Family Manual (DSP56800FAM/AD).

- *Appendix A—Bootstrap Program* provides a listing of the bootstrap code used to start or reset the DSP56L811.

- *Appendix B—Programmer's Sheets* provides programming references and master programming sheets used to program the DSP56L811 registers.

- *Index* provides a cross-reference to topics in this manual.

## 1.3 MANUAL CONVENTIONS

The following conventions are used in this manual:

• Bits within registers are always listed from most significant byte (MSB) to least significant byte (LSB).

Note: Other manuals use the opposite convention, with bits listed from LSB to MSB.

- Bits within a register are indicated AA[n:0] when more than one bit is involved in a description. For purposes of description, the bits are presented as if they are contiguous within a register. However, this is not always the case. Refer to the programming model diagrams or to the programmer's sheets to see the exact location of bits within a register.

- When a bit is described as "set," its value is set to 1. When a bit is described as "cleared," its value is set to 0.

- Pins or signals that are asserted low (made active when pulled to ground) have an overbar over their name, for example, the  $\overline{SS0}$  pin is asserted low.

- Hex values are indicated with a dollar sign (\$) preceding the hex value, as follows: \$FFFB is the X memory address for the Interrupt Priority Register (IPR).

- Code examples are displayed in a monospaced font, as shown in **Example 1-1**.

| BFSET #\$0007,X:PCC; | Configure:                        | line 1 |

|----------------------|-----------------------------------|--------|

| ;                    | MISOO, MOSIO, SCKO for SPI master | line 2 |

| i                    | ~SSO as PC3 for GPIO              | line 3 |

Example 1-1 Sample Code Listing

- Pins or signals listed in code examples that are asserted low have a tilde in front of their names. In the previous example, line 3 refers to the  $\overline{SS0}$  pin (shown as ~ss0).

- The word "assert" means that a high true (active high) signal is pulled high to  $V_{CC}$  or that a low true (active low) signal is pulled low to ground. The word

#### DSP56800 Core Description

"deassert" means that a high true signal is pulled low to ground or that a low true signal is pulled high to  $V_{CC}$ . See **Table 1-1**.

| Signal/Symbol | Logic State | Signal State | Voltage             |

|---------------|-------------|--------------|---------------------|

| PIN           | True        | Asserted     | Ground <sup>1</sup> |

| PIN           | False       | Deasserted   | $V_{CC}^{2}$        |

| PIN           | True        | Asserted     | V <sub>CC</sub>     |

| PIN           | False       | Deasserted   | Ground              |

**Table 1-1**High True / Low True Signal Conventions

- 1. Ground is an acceptable low voltage level. See the appropriate data sheet for the range of acceptable low voltage levels (typically a TTL logic low).

- 2.  $V_{CC}$  is an acceptable high voltage level. See the appropriate data sheet for the range of acceptable high voltage levels (typically a TTL logic high).

- The word "reset" is used in three different contexts in this manual. There is a reset pin that is always written as "RESET," a reset instruction that is always written as "RESET," and the word reset that refers to the reset function and is written in lower case with a leading capital letter as grammar dictates. PIN is a generic term for any pin on the chip.

# 1.4 DSP56800 CORE DESCRIPTION

The DSP56800 core consists of functional units that operate in parallel to increase throughput of the machine. Major features of the DSP56800 core include the following:

- Data Arithmetic Logic Unit (ALU)

- Address Generation Unit

- Program Controller and Hardware Looping Unit

- Bus and Bit Manipulation Unit

- Address buses

- Data buses

- JTAG/OnCE port

• Clock generator

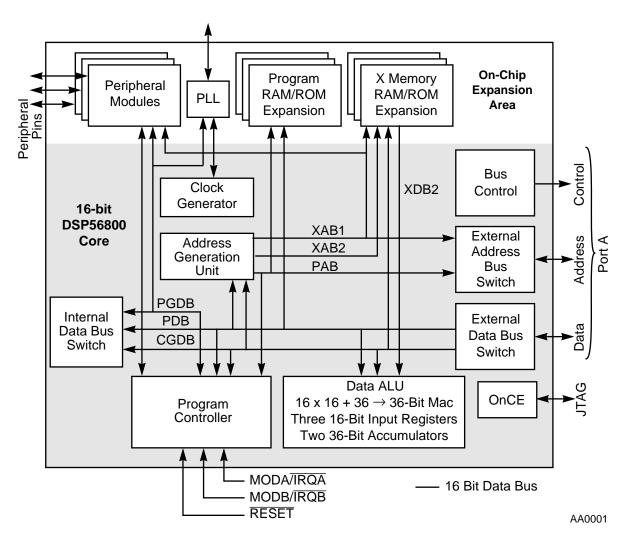

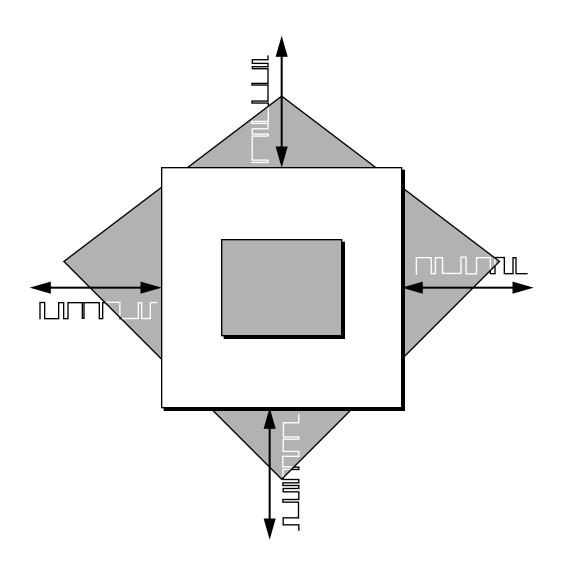

An overall block diagram of the DSP56800 core architecture is shown in **Figure 1-1**. The DSP56800 core is fed by internal program memory, a single internal data memory, an external memory interface, an on-chip phase-locked loop (PLL), 16 dedicated GPIO pins (eight of which can be programmed as interrupt inputs), two serial peripheral interface (SPI) ports for MCU support, a synchronous serial interface (SSI) port for codec support, three 16-bit general purpose timer/event counters, real-time and computer-operating-properly (COP) timers, two external mode select/interrupt lines, an external reset line, and a JTAG/On-Chip Emulation (OnCE) port.

Figure 1-1 DSP56800 Core Block Diagram

#### **DSP56800** Core Description

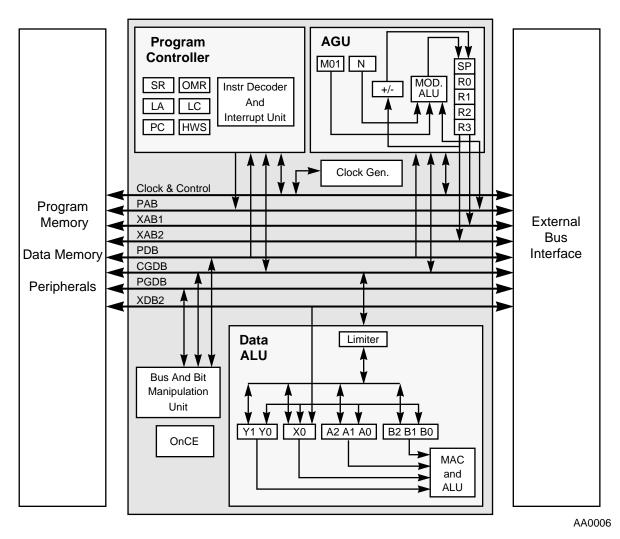

The Program Controller, Address Generation Unit, and Data (ALU) each contain a discrete register set and control logic, so that each can operate independently and in parallel with the others. Likewise, each functional unit interfaces with other units, with memory, and with memory-mapped peripherals over the core's internal address and data buses, as shown in **Figure 1-2**.

Figure 1-2 DSP56800 Bus Block Diagram

It is possible in a single instruction cycle for the Program Controller to be fetching a first instruction, the Address Generation Unit to generate two addresses for a second instruction, and the Data ALU to perform a multiply in a third instruction. In a similar manner, the Bitfield Unit can perform an operation of the third instruction described above instead of the multiplication in the Data ALU. The architecture is

pipelined to take advantage of the parallel units and significantly decrease the execution time of each instruction.

### 1.4.1 Data ALU

The Data ALU performs all of the arithmetic and logical operations on data operands. It consists of:

- Three 16-bit input registers

- Two 32-bit accumulator register

- Two 4-bit accumulator extension register

- Limiter

- Multi-bit shifting unit

- Parallel, single cycle, non-pipelined Multiply-Accumulator (MAC) unit.

The Data ALU is capable of performing the following in one instruction cycle:

- Multiplication

- Multiply-accumulate with positive or negative accumulation

- Addition

- Subtraction

- Shifting

- Logical operations

Arithmetic operations are done using 2s complement fractional or integer arithmetic. Support is also provided for unsigned and multi-precision arithmetic.

Data ALU source operands can be 16, 32, or 36 bits and can originate from input registers and/or accumulators. ALU results are stored in one of the accumulators. In addition, some arithmetic instructions store their 16-bit results in any of the three Data ALU input registers, or write directly to memory. Arithmetic operations and shifts have a 16-bit or 36-bit result and logical operations are performed on 16-bit operands yielding 16-bit results. Data ALU registers can be read or written by the CGDB data bus as 16-bit operands, and the X0 register can also be written by the XDB2 data bus with a 16-bit operand.

#### **DSP56800 Core Description**

## 1.4.2 Address Generation Unit

The Address Generation Unit performs all of the effective address calculations and address storage necessary to address data operands in memory. This unit operates in parallel with other chip resources to minimize address generation overhead. It contains two ALUs, allowing the generation of up to two 16-bit addresses every instruction cycle—one for either the XAB1 or PAB bus and one for the XAB2 bus. The ALU can directly address 65,536 locations on the XAB1 or XAB2 bus and 65,536 locations on the PAB bus, for a total capability of 131,072 16-bit data words. Hooks are provided on the DSP56800 core to expand this address space. Its arithmetic unit can perform linear and modulo arithmetic.

## 1.4.3 **Program Controller and Hardware Looping Unit**

The program controller performs instruction prefetch, instruction decoding, hardware loop control and interrupt (exception) processing. Instruction execution is carried out in other core units such as the Data ALU or Address Generation Unit. The program controller consists of a program counter unit, hardware looping control logic, interrupt control logic, and status and control registers.

Two mode and interrupt control pins provide input to the program interrupt controller. The Mode Select A/External Interrupt Request A(MODA/IRQA) and Mode Select B/External Interrupt Request B (MODB/IRQB) pins select the DSP56L811 operating mode and receive interrupt requests from external sources.

The  $\overline{\text{RESET}}$  pin resets the DSP56L811. When it is asserted, it initializes the chip and places it in the reset state. When the  $\overline{\text{RESET}}$  pin is deasserted, the DSP56L811 assumes the operating mode indicated by the MODA and MODB pins.

#### 1.4.4 Address and Data Buses

Addresses are provided to the internal X Data Memory on two unidirectional 16-bit buses, X Address Bus One (XAB1) and X Address Bus Two (XAB2). Program memory addresses are provided on the unidirectional 19-bit Program Address Bus (PAB). Note that XAB1 can provide addresses for accessing both internal and external memory, whereas XAB2 can only provide addresses for accessing internal read-only memory. The External Address Bus (EAB) provides addresses for external memory.

#### **DSP56800** Core Description

Data movement on the DSP56L811 occurs over three bidirectional 16-bit buses—the Core Global Data Bus (CGDB), the Program Data Bus (PDB) and the Peripheral Data Bus (PGDB), and also over one unidirectional 16-bit bus, the X Data Bus Two (XDB2). Data transfer between the Data ALU and the X Data Memory occurs over the CGDB bus when one memory access is performed, over the CGDB bus and the XDB2 Data Bus when two simultaneous memory reads are performed. All other data transfers to core blocks occur over the CGDB bus, and all transfers to and from peripherals occur over the PGDB bus. Instruction word fetches occur simultaneously over the PDB bus. The External Data Bus (EDB) provides bi-directional access to external data memory.

The bus structure supports general register to register, register to memory, and memory to register, and can transfer up to three 16-bit words in the same instruction cycle. Transfers between buses are accomplished in the Bus and Bit Manipulation Unit. **Table 1-2** lists the address and data buses for the DSP56800 core.

| Bus  | Bus Name             | Bus width, direction, and use                                |

|------|----------------------|--------------------------------------------------------------|

| XAB1 | X Address Bus 1      | 16-bit, unidirectional, internal and external memory address |

| XAB2 | X Address Bus 2      | 16-bit, unidirectional, internal memory address              |

| PAB  | Program Address Bus  | 19-bit, unidirectional, internal memory address              |

| EAB  | External Address Bus | 16-bit, unidirectional, external memory address              |

| CGDB | Core Global Data Bus | 16-bit, bi-directional, internal data movement               |

| PDB  | Program Data Bus     | 16-bit, bi-directional, instruction word fetches             |

| PGDB | Peripheral Data Bus  | 16-bit, bi-directional, internal data movement               |

| XDB2 | X Data Bus 2         | 16-bit, unidirectional, internal data movement               |

| EDB  | External Data Bus    | 16-bit, bi-directional, external data movement               |

# 1.4.5 Bus and Bit Manipulation Unit

Transfers between buses are accomplished in the bus unit. The bus unit is similar to a switch matrix and can connect any two of the three data buses together without adding any pipeline delays. This is required for transferring a core register to a peripheral register, for example, because the core register is connected to the CGDB bus and the peripheral register is connected to the PGDB bus.

#### DSP56L811 Architecture Overview

The bit manipulation unit performs bitfield manipulations on X memory words, peripheral registers, and registers on the DSP56800 core. It is capable of testing, setting, clearing, or inverting any bits specified in a 16-bit mask. For branch-on-bitfield instructions, this unit tests bits on the upper or lower byte of a 16-bit word. In other words, the mask tests a maximum of 8 bits at a time.

As a general rule, when reading any register less than 16 bits wide, unused bits are read as 0. Reserved and unused bits should always be written with 0 to insure future compatibility.

# 1.4.6 On-Chip Emulation (OnCE) Unit

The on-chip emulation (OnCE) unit allows the user to interact in a debug environment with the DSP56800 core and its peripherals non-intrusively. Its capabilities include examining registers, memory, or on-chip peripherals; setting breakpoints in memory; and stepping or tracing instructions. It provides simple, inexpensive, and speed independent access to the DSP56800 core for sophisticated debugging and economical system development. The JTAG port allows access to the OnCE module and through the DSP56L811 to its target system, retaining debug control without sacrificing other user accessible on-chip resources. This technique eliminates the costly cabling and the access to processor pins required by traditional emulator systems.

#### 1.5 DSP56L811 ARCHITECTURE OVERVIEW

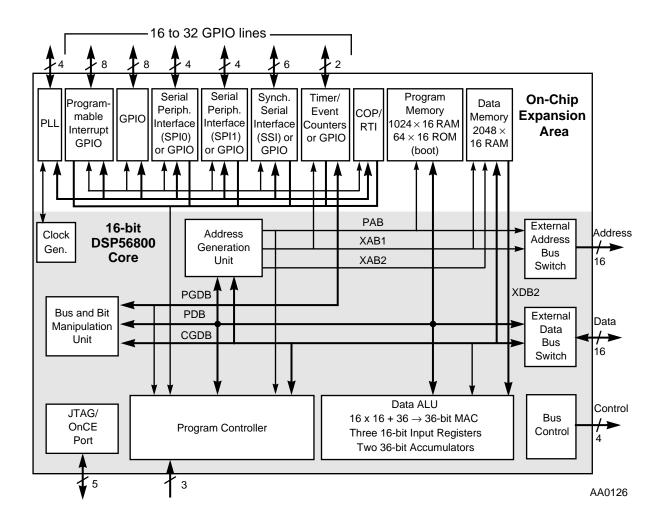

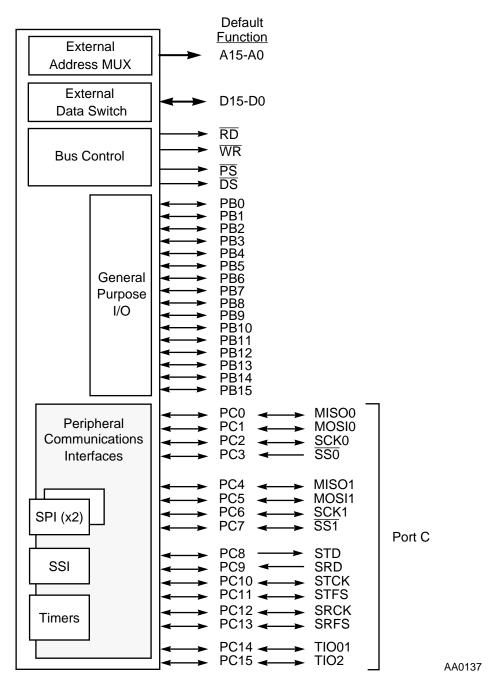

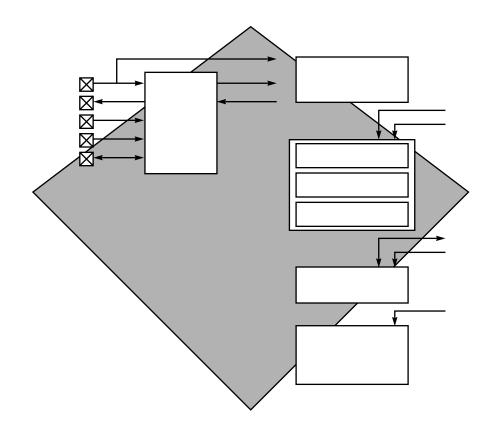

The DSP56L811 consists of the DSP56800 core, program and data memory, and peripherals useful for embedded control applications. **Figure 1-3** shows a block diagram of the DSP56L811 chip.

#### **DSP56L811** Architecture Overview

Figure 1-3 DSP56L811 Functional Block Diagram

#### 1.5.1 DSP56L811 Peripheral Blocks

The DSP56L811 provides the following peripheral blocks:

- Program RAM

- Data RAM

- External Memory Interface

- General Purpose I/O Module

- Programmable I/O Module

#### DSP56L811 Architecture Overview

- Serial Peripheral Interface (two provided)

- Synchronous Serial Interface

- General-Purpose Timer Module

- On-chip Clock Synthesis Block (PLL)

- COP/RTI

- JTAG/OnCE Port

#### 1.5.1.1 On-chip Memory

The DSP56L811 uses a Harvard architecture, which provides independent data and program memory. On-chip RAM is provided for both the X data (2K x 16-bit) and program (P) memory (1K x 16-bit), and both the program and data memories can be expanded off-chip. A 64 x 16-bit bootstrap ROM is also provided on-chip.

#### 1.5.1.2 External Memory Interface

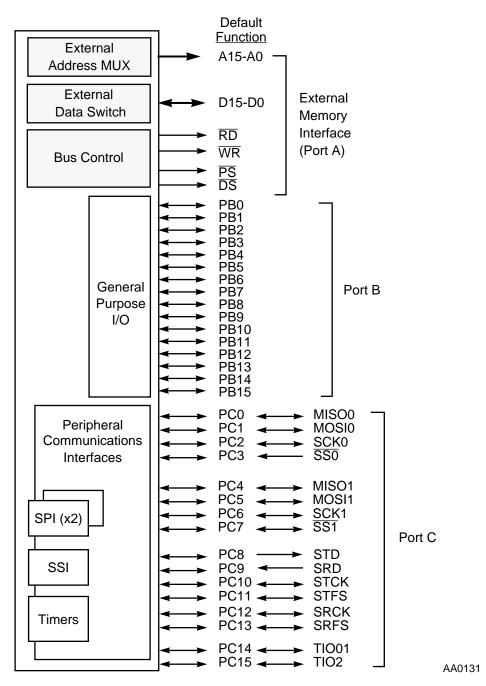

The DSP56L811 provides a port for external memory interfacing, also known as Port A. This port provides a total of 36 pins—16 pins for an external address bus, 16 pins for an external data bus, and four pins for bus control.

#### 1.5.1.3 General Purpose I/O Module

A dedicated general-purpose input-output (GPIO) port, also known as Port B, provides 16 programmable I/O pins. This port is configured so that it is possible to generate interrupts when a transition is detected on any of its lower eight pins.

#### 1.5.1.4 Programmable I/O Module

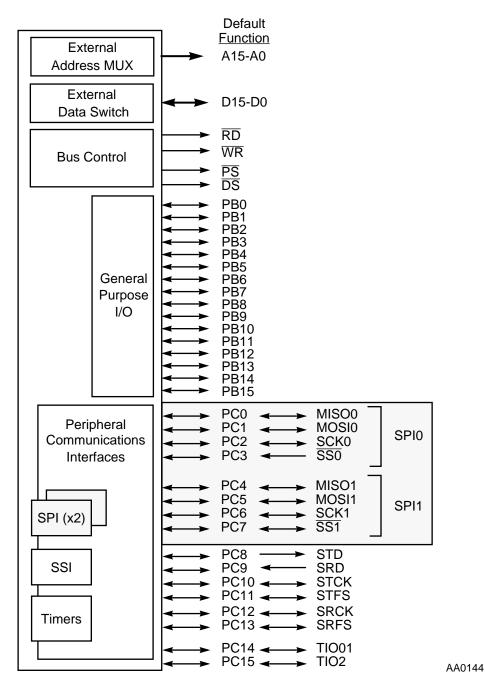

Port C provides 16 multiplexed general-purpose programmable I/O pins. Each pin can be individually selected as a GPIO pin, or allocated to on-chip peripherals—the general-purpose timer module, two Serial Peripheral Interfaces (SPI), and a Synchronous Serial Interface (SSI). Unlike the GPIO pins on Port B, the Port C pins cannot be configured to provide GPIO interrupts, but interrupts are available for the timer module, the two SPI ports, and the SSI port on Port C.

#### 1.5.1.5 Serial Peripheral Interface

The Serial Peripheral Interface (SPI) is an independent serial communications subsystem that allows the DSP56L811 to communicate synchronously with peripheral devices such as LCD display drivers, A/D subsystems, and MCU microprocessors. The SPI is also capable of inter-processor communication in a multiple master system. The SPI system can be configured as either a master or a slave device with high data rates. The SPI works in a demand-driven mode. In master mode, a transfer is initiated when data is written to the SPI Data Register. In slave mode, a transfer is initiated by the reception of a clock signal. Two separate SPIs are implemented on Port C.

#### 1.5.1.6 Synchronous Serial Interface

The Synchronous Serial Interface (SSI) is a full-duplex serial port that allows the DSP56L811 to communicate with a variety of multiple serial devices, including industry-standard codecs, other DSPs, microprocessors, and peripherals that implement the Motorola SPI interface. It is typically used to transfer samples in a periodic manner. The SSI interface consists of independent transmitter and receiver sections with independent clock generation and frame synchronization. The SSI is implemented on Port C.

#### 1.5.1.7 General-Purpose Timer Module

The timer module provides three independently programmable 16-bit timer/event counters. All three timer/counters can be clocked with clocks coming from one of three internal sources, including one of the other timers. In addition, the counters can be clocked with external clocking from the Timer Input / Output pins (TIO01 or TIO2) on Port C to count external events when configured as inputs. The same pins can be used as a timer pulse or for timer clock generation when used as outputs. The timer/event counters can be used to either interrupt the DSP56L811 or to signal an external device at periodic intervals. The timer I/O pins are implemented as part of Port C.

## 1.5.1.8 On-chip Clock Synthesis Block

The clock synthesis module generates the clocking for the DSP56L811. It generates three different clocks used by the DSP56800 core and DSP56L811 peripherals. It contains a phase-locked loop (PLL) that can multiply up the frequency or can be bypassed, as well as a prescaler/divider used to distribute clocks to peripherals and to lower power consumption on the DSP56L811. It also selects which clock, if any, is routed to the CLKO pin of the DSP56L811.

#### 1.5.1.9 COP/RTI Module

The Computer Operating Properly (COP) and Real Time Interrupt (RTI) module provides two separate functions: a watchdog timer, and an interrupt generator. These two functions monitor processor activity and provide an automatic reset signal if a failure occurs. Both functions are contained in the same block because the input clock for both comes from a common clock divider.

#### 1.5.1.10 JTAG/OnCE Port

The JTAG/OnCE port allows the user to insert the DSP56L811 into a target system while retaining debug control. The JTAG port provides board-level testing capability in conformance with the *IEEE 1149.1a-1993 IEEE Standard Test Access Port and Boundary Scan Architecture* specification defined by the Joint Test Action Group (JTAG). Five dedicated pins interface to a test access port (TAP) that contains a 16-state controller.

#### Code Development on the DSP56L811

In addition, on-chip emulation of the DSP56L811 is provided via the OnCE port, a Motorola-designed module used in DSP chips to debug application software used with the chip. The port is a separate on-chip block that allows non-intrusive interaction with the DSP and is accessible through the JTAG interface. The OnCE port makes it possible to examine registers, memory or on-chip peripherals contents in a special debug environment. This avoids sacrificing any user accessible on-chip resources to perform debugging.

The *DSP56800 Family Manual (DSP56800FAM/AD*), provides complete details on the OnCE port.

# 1.5.2 DSP56L811 Peripheral Interrupts

The peripherals on the DSP56L811 use the interrupt channels found on the DSP56800 core. Each peripheral has its own interrupt vector (often more than one interrupt vector for each peripheral) and can selectively be enabled or disabled via the Interrupt Priority Register (IPR) found on the DSP56800 core.

Section 3 provides complete details on interrupt vectors.

# 1.6 CODE DEVELOPMENT ON THE DSP56L811

The DSP56L811 instruction set, described in detail in the *DSP56800 Family Manual* (*DSP56800FAM/AD*), provides assembly level programming for this product. This manual provides a number of samples of source code to demonstrate the programming of certain features. These examples should not be considered as complete examples of how to program the DSP56L811, but as samples. See the *DSP56800 Family Manual* (*DSP56800FAM/AD*) for more information on development hardware and software products for the DSP56L811, including a low-cost evaluation module that allows access to most DSP56L811 functions and peripherals.

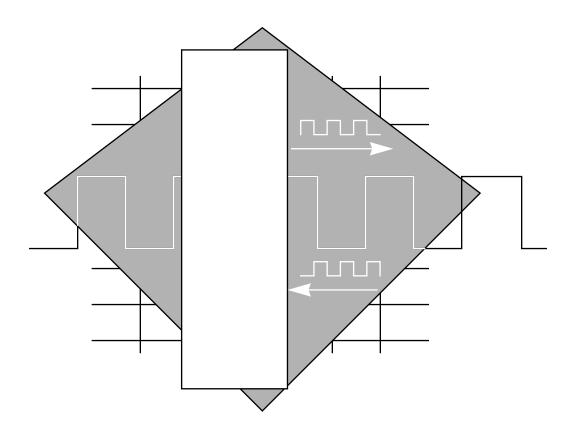

Two mechanisms on the DSP56L811 aid code development—full access by all instructions to the external data bus, and On-Chip Emulation (OnCE) hooks. The first is useful when code is first being developed on a hardware platform. The second is useful in all phases of debugging, especially when a unit is near completion and in its final packaging. This section describes the first option. The OnCE interface is fully described in the *DSP56800 Family Manual (DSP56800FAM/AD)*.

Instructions on the DSP56L811 can be executed without regard for whether the instruction fetch is on-chip or off-chip, and whether any data access is on-chip or

#### Code Development on the DSP56L811

off-chip. However, executing an instruction (including parallel moves) may require as many as three memory accesses. If more than one of these memory accesses occurs off-chip, an additional instruction cycle is required for every external access, because only one access to external memory can occur at a time. This is shown in **Example 1-2** and in the following discussion.

#### **Example 1-2** On-Chip and Off-Chip Instruction Fetches

mac x0,y0,a x:(r0)+,y0 x:(r3)+,x0

- Case 1. Instruction located on-chip, both x:() data accesses performed to on-chip memory

- In this case, since all memories are located on-chip, no external accesses are performed and the instruction runs in one instruction cycle, correctly performing all three accesses to on-chip memory.

- Case 2. Instruction located off-chip, both x:() data accesses performed to on-chip memory

- In this case only one external memory access occurs off-chip. The instruction fetch occurs over the external bus and the data accesses are made to on-chip memory. The instruction still runs in one instruction cycle, correctly performing all three accesses.

- Case 3. Instruction located on-chip, one x:() data access performed to off-chip memory

- In this case only one external memory access occurs off-chip. The instruction fetch is done to on-chip memory, one data access occurs over the external bus, and one data access is done to on-chip memory. The instruction still runs in one instruction cycle, correctly performing all three accesses.

- Case 4. Instruction located off-chip, one x:() data access performed to off-chip memory

- In this case, two external memory access occur off-chip. The instruction fetch occurs over the external bus, followed by the external data access. A data access to internal memory also takes place. The instruction now runs in two instruction cycles, correctly performing all three accesses.

Case 4 is often used during code development to provide the best visibility. This feature allows a logic analyzer to be placed on the external bus during code development on target hardware so that all memory accesses are visible. Separate  $\overline{PS}$  and  $\overline{DS}$  pins are provided to indicate whether the access is to external program or data memory.

#### Code Development on the DSP56L811

**Note:** In this mode, accesses to on-chip peripherals are not visible because these memory-mapped registers are on-chip.

An example of a system where all program and memory accesses are visible is shown in **Figure 1-4**.

Figure 1-4 Example of Code Development with Visibility on All Memory Accesses

In this example, the DSP56L811 is programmed for Operating Mode 3, Development Mode, in the Operating Mode Register (OMR) to specify that all program accesses are done externally. See **3.2 DSP56L811 Memory Map Description** on page 3-3 for a detailed description of the OMR. Likewise, the EX bit (in the OMR) is set to specify that data accesses are done externally. An exception to this is the second access on any instruction which performs two reads in a single instruction. In this case, the second read using the R3 pointer always occurs to on-chip memory. If this is an issue, the instruction performing two data memory reads can be replaced by two instructions, each performing one of the two data memory accesses.

dsp

# SECTION 2 PIN DESCRIPTIONS

| 2.1 | INTRODUCTION     | 2-3 |

|-----|------------------|-----|

| 2.2 | PIN DESCRIPTIONS | 2-5 |

# 2.1 INTRODUCTION

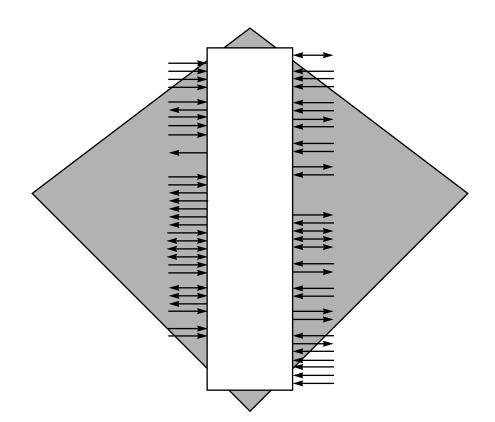

The DSP56L811 is provided in a 100-pin TQFP package. **Figure 2-1** provides a pin-out diagram. For complete electrical specifications, refer to the *DSP56L811 Data Sheet (DSP56L811/D)*.

#### Introduction

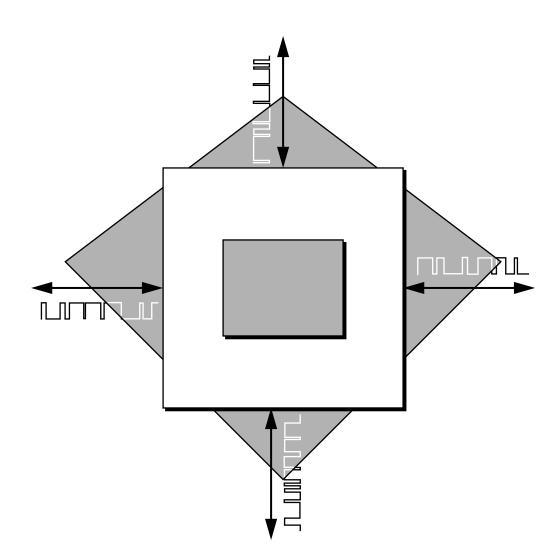

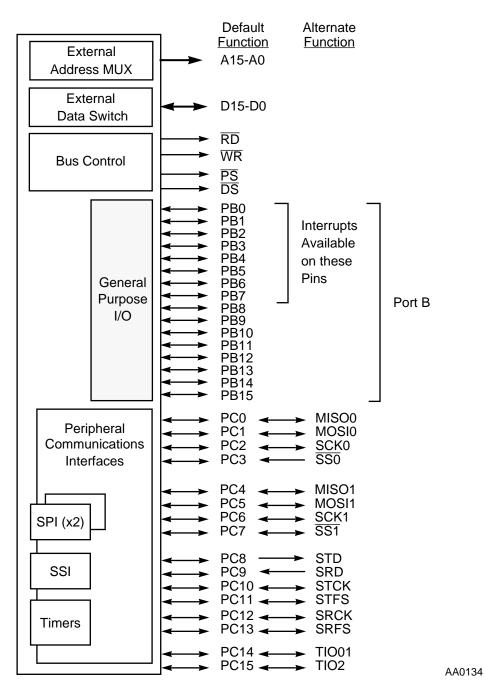

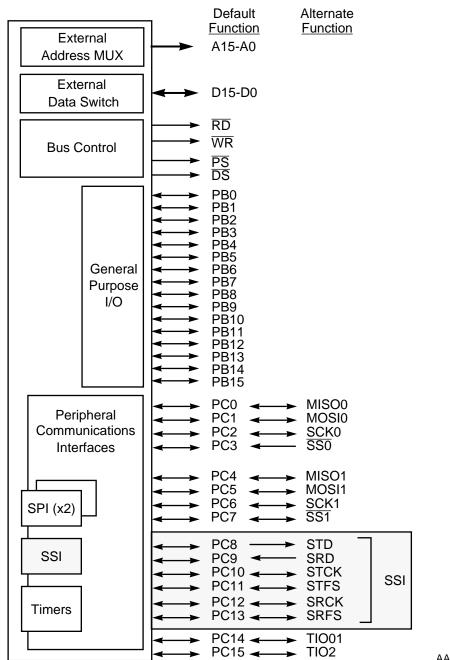

Figure 2-2 Functional Group Pin Allocations

The I/O signals are organized into the functional groups as summarized in Table 2-1.

| Functional Group                                       | Number of<br>Pins | Detailed<br>Description |

|--------------------------------------------------------|-------------------|-------------------------|

| Power (V <sub>DD</sub> or V <sub>DDPLL</sub> )         | 10                | Table 2-2               |

| Ground (V <sub>SS</sub> or V <sub>SSPLL</sub> )        | 10                | Table 2-3               |

| PLL and Clock                                          | 4                 | Table 2-4               |

| Address Bus                                            | 16                | Table 2-5               |

| Data Bus                                               | 16                | Table 2-6               |

| Bus Control                                            | 4                 | Table 2-7               |

| Interrupt and Mode Control                             | 3                 | Table 2-8               |

| Programmable Interrupt General Purpose<br>Input/Output | 8                 | Table 2-9               |

| Dedicated General Purpose Input/Output                 | 8                 | Table 2-10              |

| Serial Peripheral Interface (SPI) Ports <sup>1</sup>   | 8                 | Table 2-11              |

| Synchronous Serial Interface (SSI) Port <sup>1</sup>   | 6                 | Table 2-12              |

| Timer Module <sup>1</sup>                              | 2                 | Table 2-13              |

| JTAG/On-chip emulation (OnCE)                          | 5                 | Table 2-14              |

| Note: 1. Alternately, general purpose I/O pins         |                   |                         |

Table 2-1

Functional Group Pin Allocations

**Note:** All unused port pins configured as inputs should be properly terminated through a pull-up resistor. All power and ground pins should be connected to the appropriate low-impedance power and ground paths.

# 2.2 PIN DESCRIPTIONS

#### Table 2-2Power Pins

| Pin Name            | Pin Description                                                                                             |

|---------------------|-------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> (9) | Power—power pins                                                                                            |

| V <sub>DDPLL</sub>  | <b>PLL Power</b> —This pin supplies a quiet power source to the VCO to provide greater frequency stability. |

## Table 2-3 Ground Pins

| Pin Name            | Pin Description                                                                                        |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------|--|--|

| V <sub>SS</sub> (9) | GND—ground pins                                                                                        |  |  |

| V <sub>SSPLL</sub>  | <b>PLL Ground</b> —This pin supplies a quiet ground to the VCO to provide greater frequency stability. |  |  |

#### Table 2-4PLL and Clock Pins

| Pin<br>Name | Signal<br>Type | State<br>during<br>Reset | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAL       | Input          | Input                    | <b>External Clock/Crystal Input</b> —This input should be<br>connected to an external clock or to an external oscillator.<br>After being squared, the input clock can be selected to<br>provide the clock directly to the DSP core. The minimum<br>instruction time is two input clock periods, broken up into<br>four phases named T0, T1, T2, and T3. This input clock can<br>also be selected as input clock for the on-chip PLL. |

| XTAL        | Output         | Chip-<br>driven          | <b>Crystal Output</b> —This output connects the internal crystal oscillator output to an external crystal. If an external clock is used, XTAL should not be connected.                                                                                                                                                                                                                                                               |

| Table 2-4 | PLL and Clock Pins | (Continued) |

|-----------|--------------------|-------------|

|-----------|--------------------|-------------|

| Pin<br>Name | Signal<br>Type | State<br>during<br>Reset | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|----------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKO        | Output         | Chip-<br>driven          | <b>Clock Output</b> —This pin outputs a buffered clock signal.<br>By programming two bits (CS1, CS0) inside the PLL<br>control register PCR1, the user can select between<br>outputting a squared version of the signal applied to<br>EXTAL and a version of the DSP master clock at the output<br>of the PLL. The clock frequency on this pin can also be<br>disabled by programming the CS1, CS0 bits in the PLL<br>control register, PCR1. |

| SXFC        | Input          | Input                    | <b>External Filter Capacitor</b> —This pin is used to add an external filter circuit to the phase locked loop.                                                                                                                                                                                                                                                                                                                                |

| Table 2-5 | Address Bus Pins |

|-----------|------------------|

|-----------|------------------|

| Pin<br>Names | Signal<br>Type | State<br>during<br>Reset | Pin Description                                                                                                                                                                                                                                                                                                                           |

|--------------|----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A15       | Output         | Tri-stated               | Address Bus—Signals A0-A15 change in T0, and specify<br>the address for an external program or data memory<br>access. The value of the DRV bit in the bus control register<br>(BCR) causes the address bus to retain the last external<br>address (DRV = 1) or tri-stated (DRV = 0) during an<br>internal access or in stop or wait mode. |

| <b>Table 2-6</b> | Data Bus Pins |

|------------------|---------------|

|------------------|---------------|

| Pin<br>Names | Signal<br>Type   | State<br>during<br>Reset | Pin Description                                                                                                                                                                                                                                          |

|--------------|------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D15       | Input/<br>Output | Tri-stated               | <b>Data Bus</b> —Read data is sampled in on the trailing edge of T2, while write data output is enabled on the leading edge of T2 and tri-stated on the leading edge of T0. D0-D15 are always tri-stated during internal access or in stop or wait mode. |

#### Pin Descriptions

Table 2-7Bus Control Pins

| Pin<br>Name | Signal<br>Type | State<br>during<br>Reset     | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PS          | Output         | Pulled<br>high<br>internally | <b>Program Memory Select</b> — $\overline{PS}$ is asserted low for external program memory access. If the external bus is not used during an instruction cycle (T0, T1, T2, T3), PS is deasserted high in T0. During an internal access, in stop mode, or in wait mode, the value of the DRV bit in the Bus Control Register (BCR) determines whether the chip continues to drive PS (DRV = 1) or tri-states PS (DRV = 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DS          | Output         | Pulled<br>high<br>internally | <b>Data Memory Select</b> — $\overline{\text{DS}}$ is asserted low during T0 for<br>external data memory access. If the external bus is not<br>accessed during an instruction cycle (T0, T1, T2, T3), $\overline{\text{DS}}$ is<br>deasserted high in T0. During an internal access, in stop<br>mode, or in wait mode, the value of the DRV bit in the BCR<br>register determines whether the chip continues to drive $\overline{\text{DS}}$<br>(DRV = 1) or tri-states $\overline{\text{DS}}$ (DRV = 0).                                                                                                                                                                                                                                                                                                                                                                            |