## DSP56603

## 16-bit Digital Signal Processor User's Manual

Motorola, Incorporated Semiconductor Products Sector DSP Division 6501 William Cannon Drive West Austin, TX 78735-8598 This document (and other documents) can be viewed on the World Wide Web at http://www.motorola-dsp.com.

This manual is one of a set of three documents. You need the following manuals to have complete product information: Family Manual, User's Manual, and Technical Data.

OnCE<sup>TM</sup> is a trademark of Motorola, Inc.

© MOTOROLA INC., 1996

Order this document by DSP56603UM/AD

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity / Affirmative Action Employer.

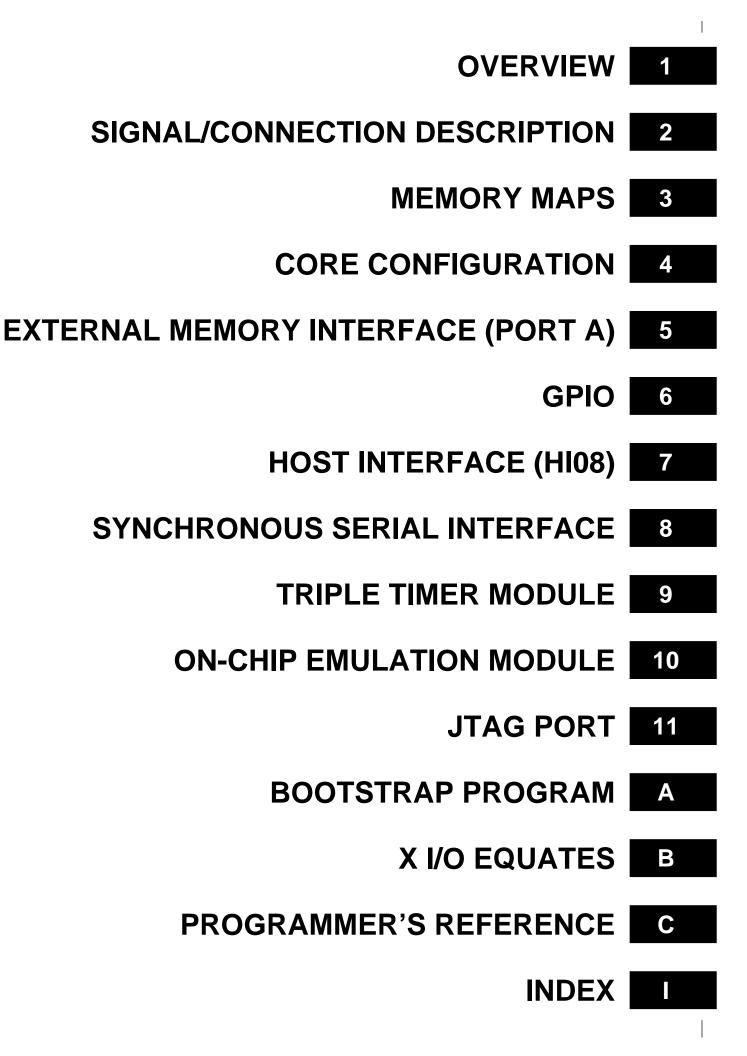

# TABLE OF CONTENTS

| SECTIO  | N 1 OVERVIEW                                       |

|---------|----------------------------------------------------|

| 1.1     | INTRODUCTION                                       |

| 1.2     | MANUAL ORGANIZATION1-3                             |

| 1.3     | MANUAL CONVENTIONS                                 |

| 1.4     | DSP56600 CORE DESCRIPTION                          |

| 1.5     | DSP56600 CORE FUNCTIONAL BLOCKS                    |

| 1.5.1   | Data ALU                                           |

| 1.5.1.1 | Data ALU Registers1-7                              |

| 1.5.1.2 | Multiply-Accumulator (MAC)                         |

| 1.5.2   | Address Generation Unit                            |

| 1.5.3   | Program Control Unit                               |

| 1.5.4   | Program Patch Logic 1-9                            |

| 1.5.5   | PLL and Clock Oscillator                           |

| 1.5.6   | Expansion Port (Port A)1-10                        |

| 1.5.7   | JTAG Test Access Port and On-Chip Emulation (OnCE) |

|         | Module1-11                                         |

| 1.5.8   | On-Chip Memory                                     |

| 1.6     | INTERNAL BUSES1-11                                 |

| 1.7     | DSP56603 ARCHITECTURE OVERVIEW1-13                 |

| 1.7.1   | GPIO Functionality1-14                             |

| 1.7.2   | Host Interface (HI08)                              |

| 1.7.3   | Synchronous Serial Interface (SSI)                 |

| 1.7.4   | Triple Timer                                       |

|         |                                                    |

| SECTIO  |                                                    |

| 2.1     | INTRODUCTION                                       |

| 2.2     | POWER                                              |

| 2.3     | GROUND                                             |

| 2.4     | CLOCK AND PHASE LOCK LOOP                          |

| 2.5     | INTERRUPT AND MODE CONTROL                         |

| 2.6     | EXPANSION PORT (PORT A)                            |

| 2.7     | HOST INTERFACE (HI08)                              |

| <b>0</b> |                                               |

|----------|-----------------------------------------------|

| 2.7.1    | Host Port Usage Considerations                |

| 2.7.2    | Host Port Configuration                       |

| 2.8      | SYNCHRONOUS SERIAL INTERFACE 0 (SSI0) 2-18    |

| 2.9      | SYNCHRONOUS SERIAL INTERFACE 1 (SSI1) 2-21    |

| 2.10     | GENERAL PURPOSE I/O, GPIO 2-24                |

| 2.11     | TRIPLE TIMER         2-25                     |

| 2.12     | JTAG/ONCE INTERFACE 2-26                      |

| SECTIO   | • • • • • • • • • • • • • • • • • • • •       |

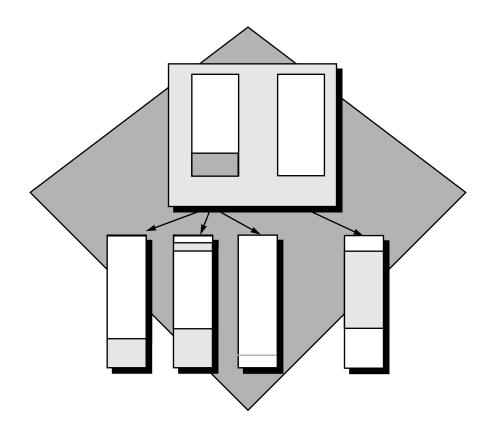

| 3.1      | INTRODUCTION                                  |

| 3.2      | DSP56603 MEMORY MAP DESCRIPTION               |

| 3.2.1    | On-Chip Program Memory 3-4                    |

| 3.2.2    | On-Chip X Data Memory                         |

| 3.2.3    | On-Chip Y Data Memory 3-5                     |

| 3.3      | MEMORY-MAPPED I/O REGISTERS                   |

| SECTIO   | N 4 CORE CONFIGURATION                        |

| 4.1      | INTRODUCTION                                  |

| 4.2      | DSP56600 CORE-SPECIFIC ATTRIBUTES             |

| 4.2.1    | Program Patch Detector JUMP Targets           |

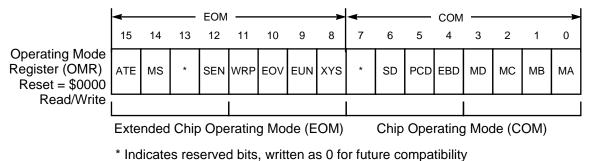

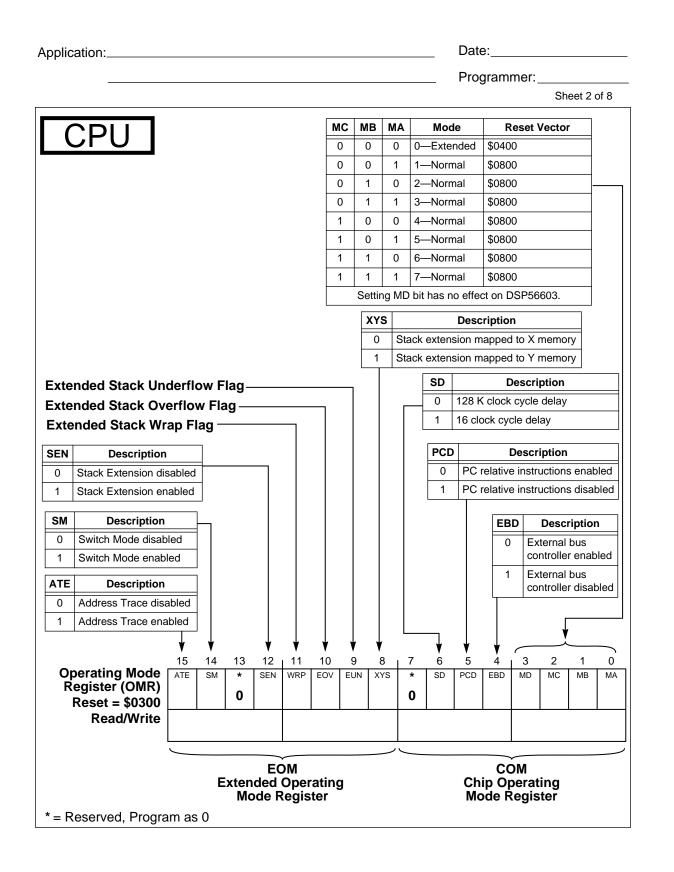

| 4.2.2    | Operating Mode Register (OMR) 4-4             |

| 4.2.2.1  | Chip Operating Mode Bits—Bits 0–3             |

| 4.2.2.2  | External Bus Disable (EDB)—Bit 4              |

| 4.2.2.3  | PC Relative Logic Disable (PCD)—Bit 5 4-5     |

| 4.2.2.4  | Stop Delay (SD)—Bit 6                         |

| 4.2.2.5  | XY Select for Stack Extension (XY)—Bit 8 4-5  |

| 4.2.2.6  | Extended Stack Underflow Flag (EUN)—Bit 9 4-5 |

| 4.2.2.7  | Extended Stack Overflow Flag (EOV)—Bit 10 4-6 |

| 4.2.2.8  | Extended Stack Wrap Flag (WR)—Bit 11 4-6      |

| 4.2.2.9  | Extended Stack Enable (EN)—Bit 12             |

| 4.2.2.10 | Memory Switch Mode Bit (MS)—Bit 14            |

| 4.2.2.11 | Address Trace Enable (ATE)—Bit 15             |

| 4.2.2.12 | Reserved Bits (Bit 7, 13) 4-7                 |

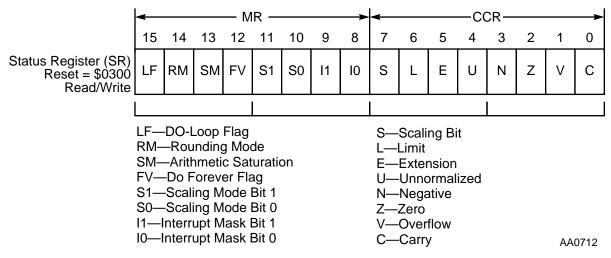

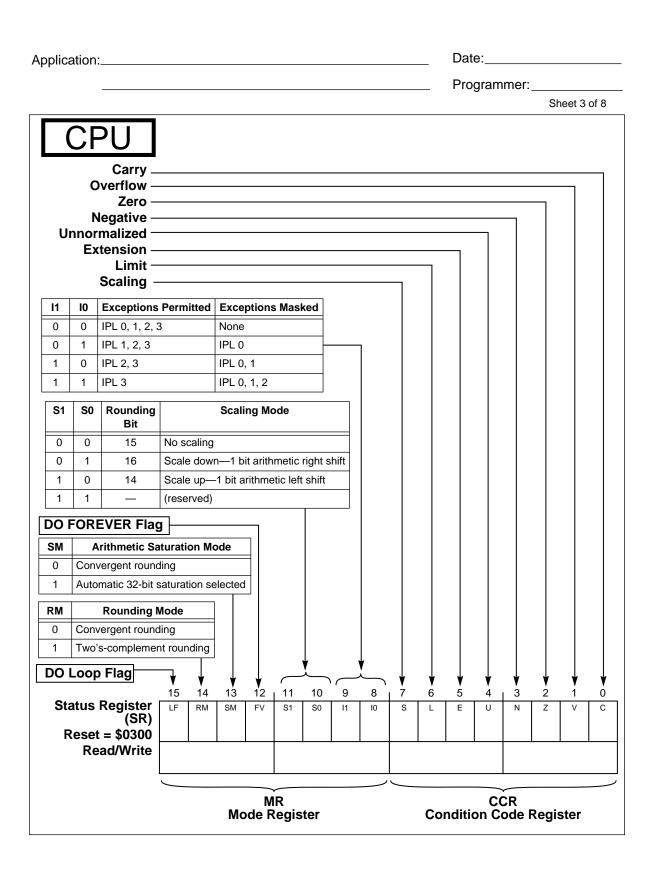

| 4.2.3    | Status Register (SR) 4-7                      |

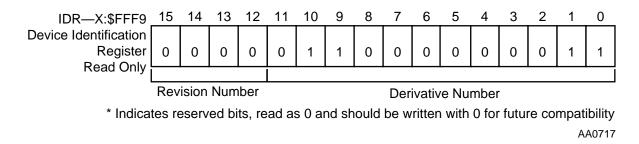

| 4.2.4    | Device Identification Register (IDR) 4-8      |

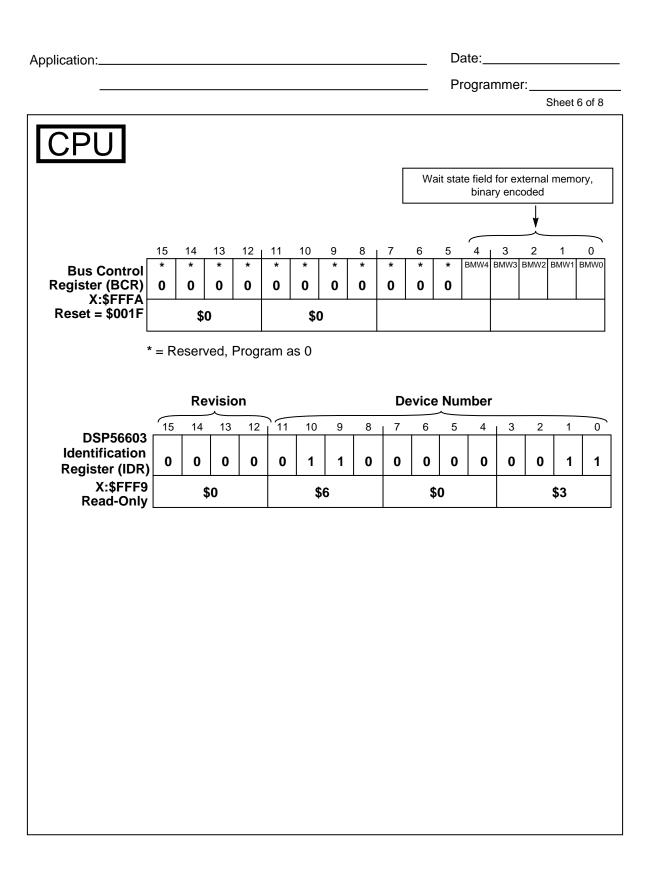

| 4.2.5    | Bus Control Register (BCR)                    |

| 4.3     | BOOTSTRAP PROGRAM                               |        |

|---------|-------------------------------------------------|--------|

| 4.4     | CHIP OPERATING MODES                            | 4-9    |

| 4.4.1   | Expanded Mode (Mode 0)                          |        |

| 4.4.2   | Normal Mode (Modes 1–7)                         | . 4-10 |

| 4.4.2.1 | Mode 1—Reserved                                 | . 4-11 |

| 4.4.2.2 | Mode 2—Bootstrap from 68338                     | . 4-11 |

| 4.4.2.3 | Mode 3—Bootstrap from 24-Bit Memory             | . 4-11 |

| 4.4.2.4 | Mode 4—Bootstrap from 8-Bit Memory              | . 4-11 |

| 4.4.2.5 | Mode 5—Bootstrap from ISA Bus                   | . 4-11 |

| 4.4.2.6 | Mode 6—Bootstrap from 68HC11                    | . 4-11 |

| 4.4.2.7 | Mode 7—Reserved                                 | . 4-11 |

| 4.5     | INTERRUPTS                                      | . 4-11 |

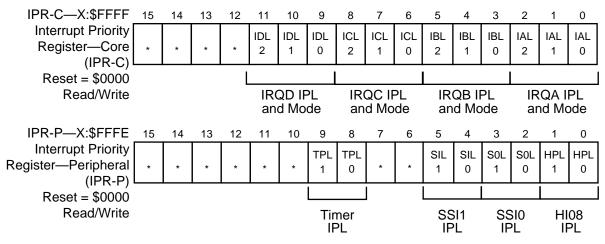

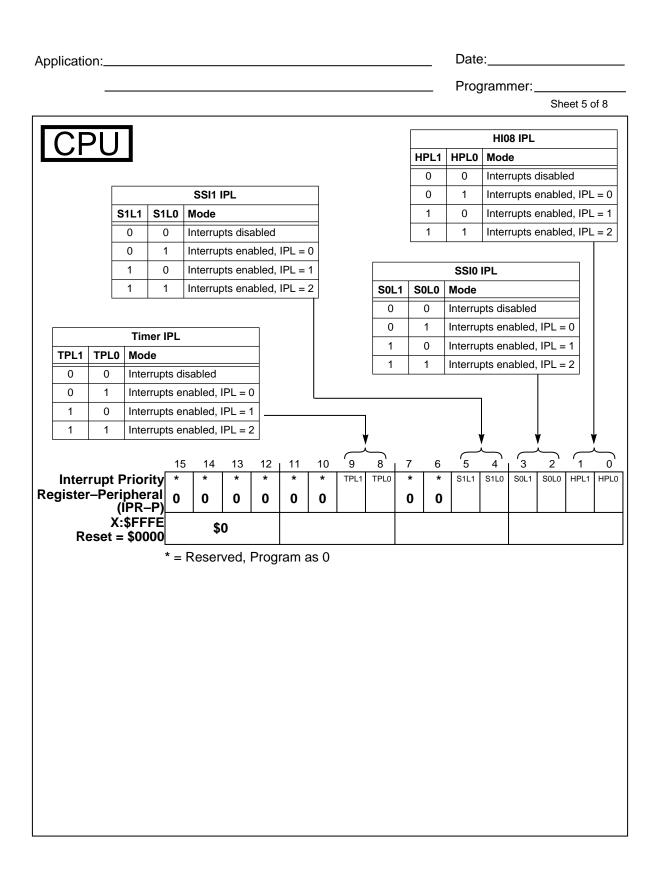

| 4.5.1   | Interrupt Priority Levels                       |        |

| 4.5.2   | Interrupt Sources Priorities within an IPL      | . 4-15 |

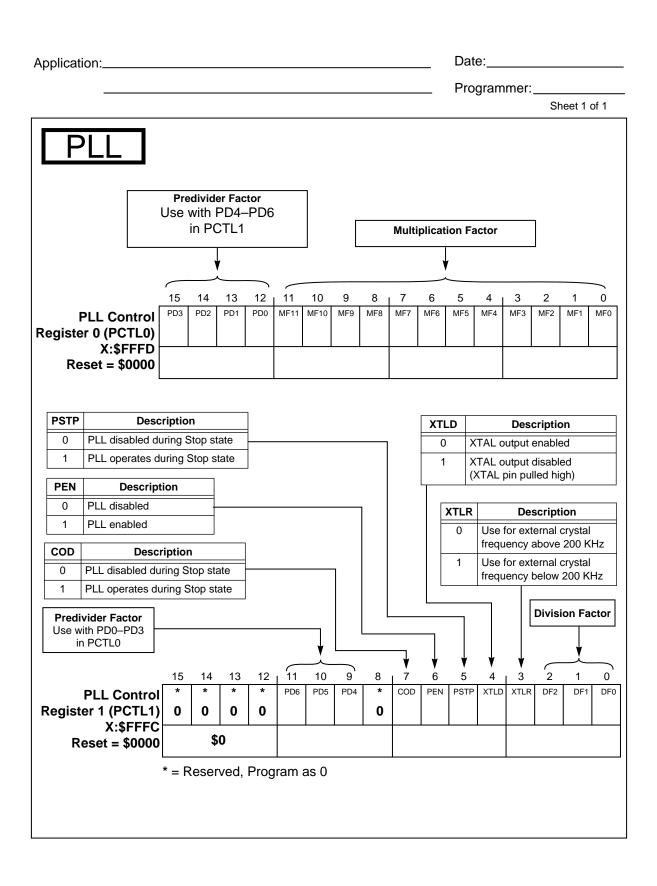

| 4.6     | PHASE LOCK LOOP                                 | . 4-17 |

| 4.6.1   | PLL Control Register 0 (PCTL0)                  | . 4-17 |

| 4.6.1.1 | Multiplication Factor Bits (MF0–MF11)—Bits 0–11 | . 4-17 |

| 4.6.1.2 | Predivider Factor Bits PD0–PD3—Bits 12–15       | . 4-18 |

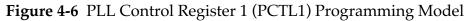

| 4.6.2   | PLL Control Register 1 (PCTL1)                  | . 4-18 |

| 4.6.2.1 | Division Factor Bits (DF2–DF0)—Bits 0–2         | . 4-19 |

| 4.6.2.2 | Crystal Range Bit (XTLR)—Bit 3                  |        |

| 4.6.2.3 | Crystal Disable Bit (XTLD)—Bit 4                | . 4-19 |

| 4.6.2.4 | Stop Processing State Bit (PSTP)–Bit 5          | . 4-20 |

| 4.6.2.5 | PLL Enable Bit (PEN)—Bit 6                      | . 4-20 |

| 4.6.2.6 | Clock Output Disable Bit (COD)—Bit 7            | . 4-20 |

| 4.6.2.7 | Predivider Factor Bits PD4–PD6—Bits 9–11        | . 4-20 |

| 4.6.2.8 | Reserved Bits 8, 12–15                          | . 4-20 |

| SECTIO  | ON 5 EXTERNAL MEMORY INTERFACE (PORT A) .       | 5-1    |

| 5.1     |                                                 | 5-3    |

| 5.2     | EXPANSION PORT SIGNAL DESCRIPTION               | 5-3    |

| 5.2.1   | Address Bus—A0–A15                              | 5-3    |

| 5.2.2   | Data Bus—D0–D23                                 |        |

| 5.2.3   | Memory Chip Select—MCS                          |        |

| 5.2.4   | Read Enable—RD                                  |        |

| 5.2.5   | Write Enable—WR                                 | 5-4    |

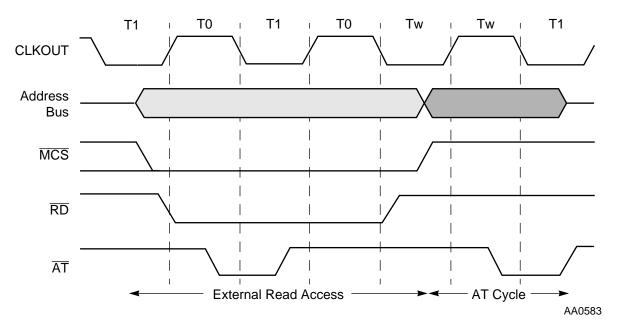

| 5.2.6   | Address Trace—AT                            | 5-4    |

|---------|---------------------------------------------|--------|

| 5.3     | EXPANSION PORT OPERATION.                   | 5-4    |

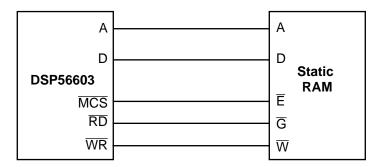

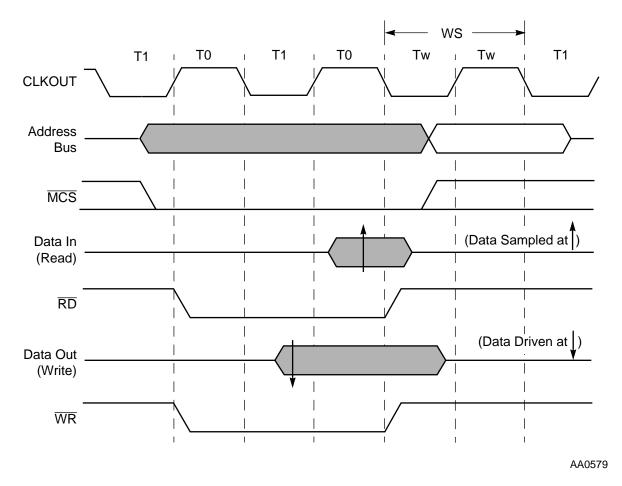

| 5.3.1   | Static RAM Support                          |        |

| 5.3.2   | Expansion Port Disable                      |        |

| 5.4     | PORT A CONTROL AND DATA TRANSFER            |        |

| 5.4.1   | Bus Control Register (BCR)                  |        |

| 5.4.1.1 | Expansion Bus Memory Wait—Bits 0–4          |        |

| 5.4.1.2 | Reserved Bits—Bits 5–15                     |        |

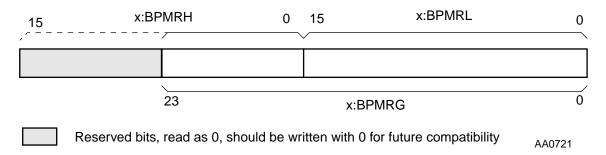

| 5.4.2   | Bus Switch Program Memory Register (BPMR)   |        |

| 5.4.2.1 | BPMR Mapping                                |        |

| 5.4.2.2 | 24-bit Access to BPMR                       |        |

| 5.4.2.3 | 16-bit Access to BPMR                       | 5-9    |

| 5.4.2.4 | BPMR Usage Typical Examples                 | 5-9    |

| 5.5     | PROGRAM ADDRESS TRACING MODE                |        |

|         |                                             |        |

| SECTIO  | • • • • • • • • • • • • • • • • • • • •     |        |

| 6.1     |                                             |        |

| 6.2     | GPIO CONFIGURATION                          |        |

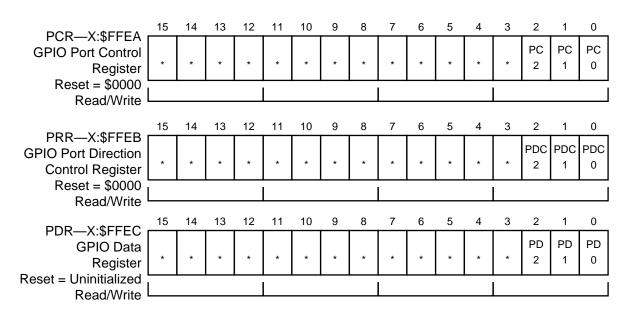

| 6.3     | PORT CONTROL REGISTER (PCR)                 | 6-5    |

| 6.4     | PORT DIRECTION REGISTER (PRR)               |        |

| 6.5     | PORT DATA REGISTER (PDR)                    | 6-6    |

| SECTIO  | N 7 HOST INTERFACE (HI08)                   | 7-1    |

| 7.1     |                                             |        |

| 7.2     | INTERFACE                                   |        |

| 7.2.1   | DSP Side                                    |        |

| 7.2.2   | Host Side                                   | 7-4    |

| 7.3     | HI08 HOST PORT                              | 7-6    |

| 7.4     | HOST INTERFACE—DSP PROGRAMMER'S MODEL       | 7-8    |

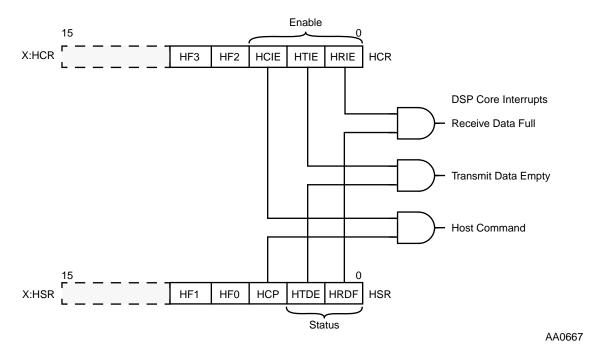

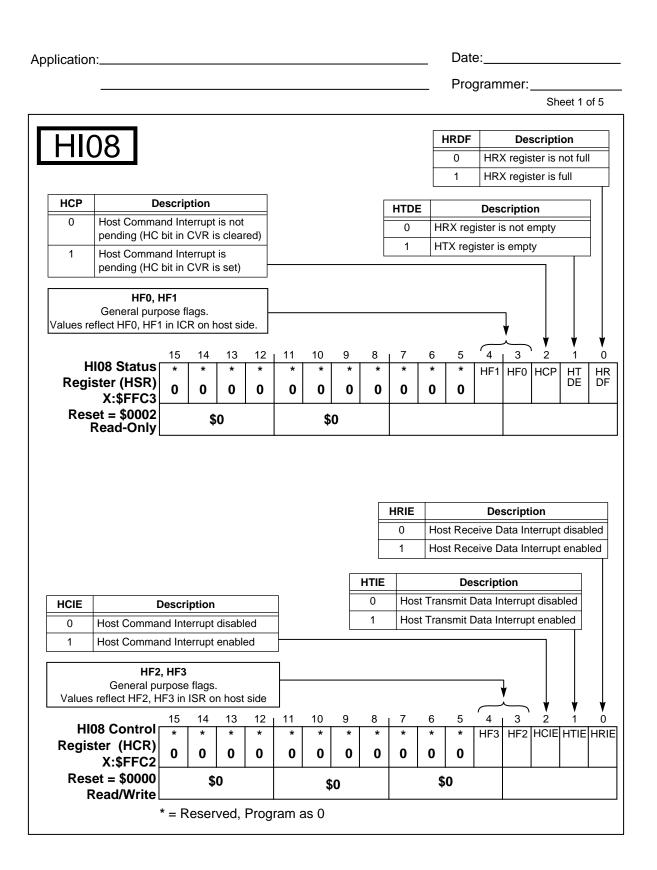

| 7.4.1   | HI08 Control Register (HCR)                 | 7-8    |

| 7.4.1.1 | Host Receive Interrupt Enable (HRIE)—Bit 0  | 7-9    |

| 7.4.1.2 | Host Transmit Interrupt Enable (HTIE)—Bit 1 | 7-9    |

| 7.4.1.3 | Host Command Interrupt Enable (HCIE)—Bit 2  | 7-9    |

| 7.4.1.4 | Host Flags 2 and 3 (HF2–HF3)—Bits 3–4       | . 7-10 |

| 7.4.1.5 | Reserved Bits—Bits 5–15                     | . 7-10 |

| 7.4.2   | HI08 Status Register (HSR)                  | . 7-10 |

| 7.4.2.1  | Host Receive Data Full (HRDF)—Bit 0        | 7-10             |

|----------|--------------------------------------------|------------------|

| 7.4.2.2  | Host Transmit Data Empty (HTDE)—Bit 1      |                  |

| 7.4.2.2  | Host Command Pending (HCP)—Bit 2           |                  |

| 7.4.2.3  | Host Flags 0 and 1 (HF0–HF1)—Bits 3–4      |                  |

| 7.4.2.4  | Reserved Bits—Bits 5–15                    |                  |

|          |                                            |                  |

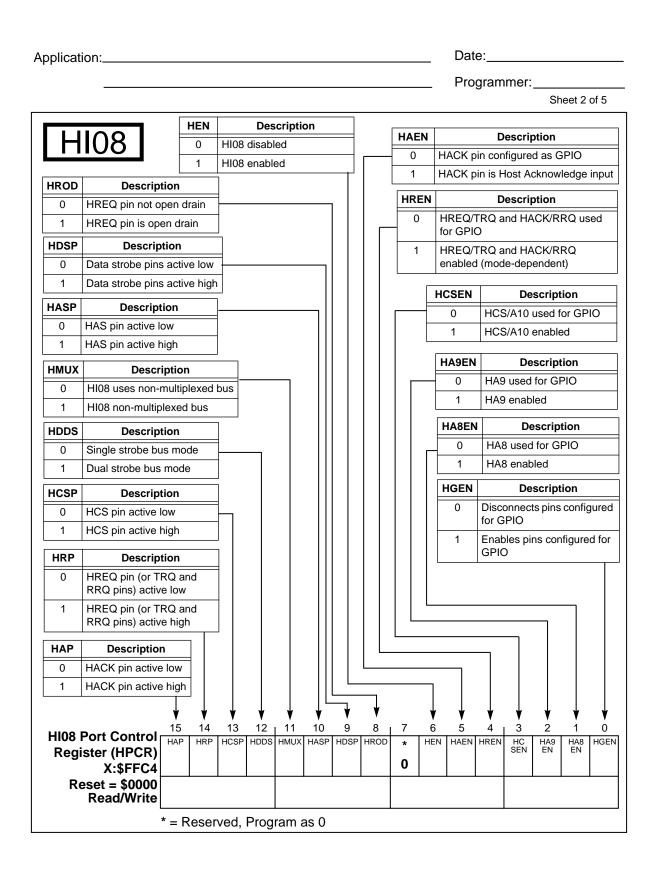

| 7.4.3    | HI08 Port Control Register (HPCR)          |                  |

| 7.4.3.1  | Host GPIO Port Enable (HGEN)—Bit 0         |                  |

| 7.4.3.2  | Host Address Line 8 Enable (HA8EN)—Bit 1   |                  |

| 7.4.3.3  | Host Address Line 9 Enable (HA9EN)—Bit 2   |                  |

| 7.4.3.4  | Host Chip Select Enable (HCSEN)—Bit 3      |                  |

| 7.4.3.5  | Host Request Enable (HREN)—Bit 4           |                  |

| 7.4.3.6  | Host Acknowledge Enable (HAEN)—Bit 5       |                  |

| 7.4.3.7  | Host Enable (HEN)—Bit 6                    |                  |

| 7.4.3.8  | Reserved Bit—Bit 7                         |                  |

| 7.4.3.9  | Host Request Open Drain (HROD)—Bit 8       |                  |

| 7.4.3.10 | Host Data Strobe Polarity (HDSP)—Bit 9     |                  |

| 7.4.3.11 | Host Address Strobe Polarity (HASP)—Bit 10 |                  |

| 7.4.3.12 | Host Multiplexed Bus (HMUX)—Bit 11         | 7-14             |

| 7.4.3.13 | Host Dual Data Strobe (HDDS)—Bit 12        | 7-14             |

| 7.4.3.14 | Host Chip Select Polarity (HCSP)—Bit 13    | 7-15             |

| 7.4.3.15 | Host Request Polarity (HRP)—Bit 14         | 7-15             |

| 7.4.3.16 | Host Acknowledge Polarity (HAP)—Bit 15     | 7-16             |

| 7.4.4    | HI08 Data Direction Register (HDDR)        | 7-16             |

| 7.4.5    | HI08 Data Register (HDR)                   | 7-16             |

| 7.4.6    | HI08 Base Address Register (HBAR)          |                  |

| 7.4.7    | HI08 Receive Data Register (HRX)           | 7-18             |

| 7.4.8    | HI08 Transmit Data Register (HTX)          |                  |

| 7.4.9    | DSP Side Registers After Reset             |                  |

| 7.4.10   | HI08 DSP Core Interrupts                   |                  |

| 7.5 HI   | 08—EXTERNAL HOST PROGRAMMER'S MODEL        |                  |

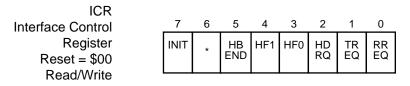

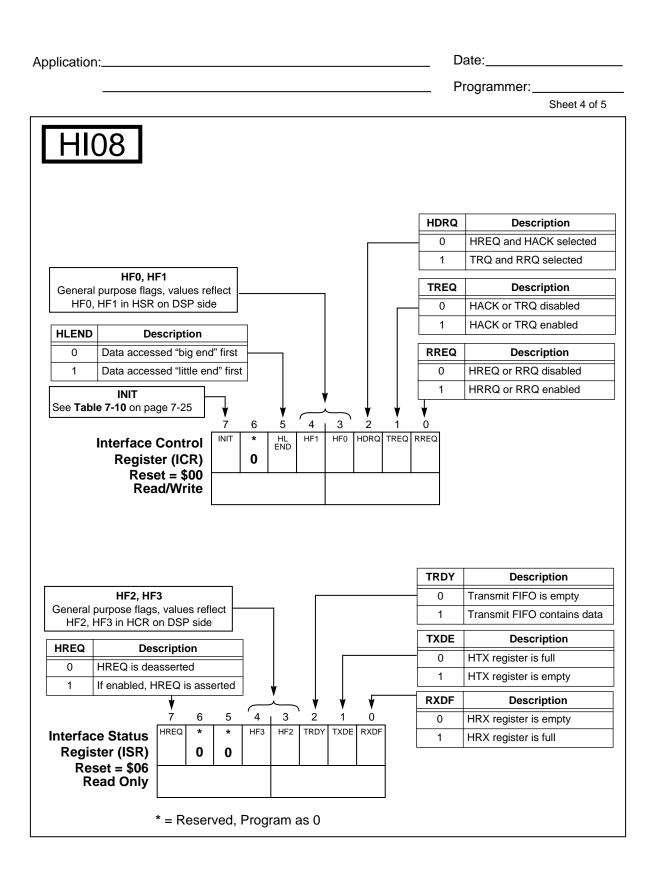

| 7.5.1    | Interface Control Register (ICR)           |                  |

| 7.5.1.1  | Receive Request Enable (RREQ)—Bit 0        |                  |

| 7.5.1.2  | Transmit Request Enable (TREQ)–Bit 1       |                  |

| 7.5.1.3  | Double Host Request (HDRQ)—Bit 2           |                  |

| 7.5.1.4  | Host Flag 0 (HF0)—Bit 3                    |                  |

| 7.5.1.5  | Host Flag 1 (HF1)—Bit 4                    |                  |

|          |                                            | · · · <b>- ·</b> |

| 7.5.1.6 | Host Big Endian (HBEND)—Bit 5               | 7-24 |

|---------|---------------------------------------------|------|

| 7.5.1.7 | Initialize Bit (INIT)—Bit 7                 | 7-24 |

| 7.5.1.8 | Reserved Bit—Bit 6                          |      |

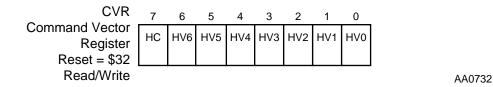

| 7.5.2   | Command Vector Register (CVR)               | 7-25 |

| 7.5.2.1 | Host Vector (HV)—Bits 0–6                   | 7-25 |

| 7.5.2.2 | Host Command Bit (HC)—Bit 7                 |      |

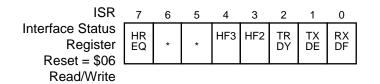

| 7.5.3   | Interface Status Register (ISR)             | 7-26 |

| 7.5.3.1 | Receive Data Register Full (RXDF)—Bit 0     | 7-26 |

| 7.5.3.2 | Transmit Data Register Empty (TXDE)—Bit 1   | 7-27 |

| 7.5.3.3 | Transmitter Ready (TRDY)—Bit 2              | 7-27 |

| 7.5.3.4 | Host Flag 2 (HF2)—Bit 3                     | 7-27 |

| 7.5.3.5 | Host Flag 3 (HF3)–Bit 4                     |      |

| 7.5.3.6 | Reserved Bits–Bits 5 and 6                  | 7-27 |

| 7.5.3.7 | ISR Host Request (HREQ)—Bit 7               | 7-28 |

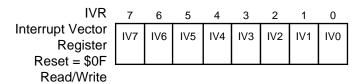

| 7.5.4   | Interrupt Vector Register (IVR)             | 7-28 |

| 7.5.5   | Receive Byte Registers (RXH, RXL)           | 7-29 |

| 7.5.6   | Transmit Byte Registers (TXH, TXL)          | 7-29 |

| 7.5.7   | Host Side Registers After Reset             | 7-29 |

| 7.6     | GENERAL PURPOSE I/O                         | 7-30 |

| 7.6.1   | Servicing the Host Interface                | 7-31 |

| 7.6.2   | HI08 Host Processor Data Transfer           | 7-31 |

| 7.6.3   | Polling                                     | 7-31 |

| 7.6.4   | Servicing Interrupts                        | 7-32 |

| SECTIC  | N 8 SYNCHRONOUS SERIAL INTERFACE            | 8-1  |

| 8.1     | INTRODUCTION                                |      |

| 8.2     | SSI DATA AND CONTROL PINS                   |      |

| 8.2.1   | Serial Control 0 (SC0)                      |      |

| 8.2.2   | Serial Control 1 (SC1)                      |      |

| 8.2.3   | Serial Control 2 (SC2)                      |      |

| 8.2.4   | Serial Clock (SCK)                          |      |

| 8.2.5   | Serial Receive Data (SRD)                   |      |

| 8.2.6   | Serial Transmit Data (STD)                  |      |

| 8.3     | SSI PROGRAMMING MODEL                       | 8-7  |

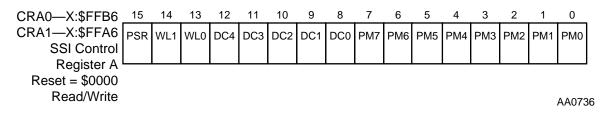

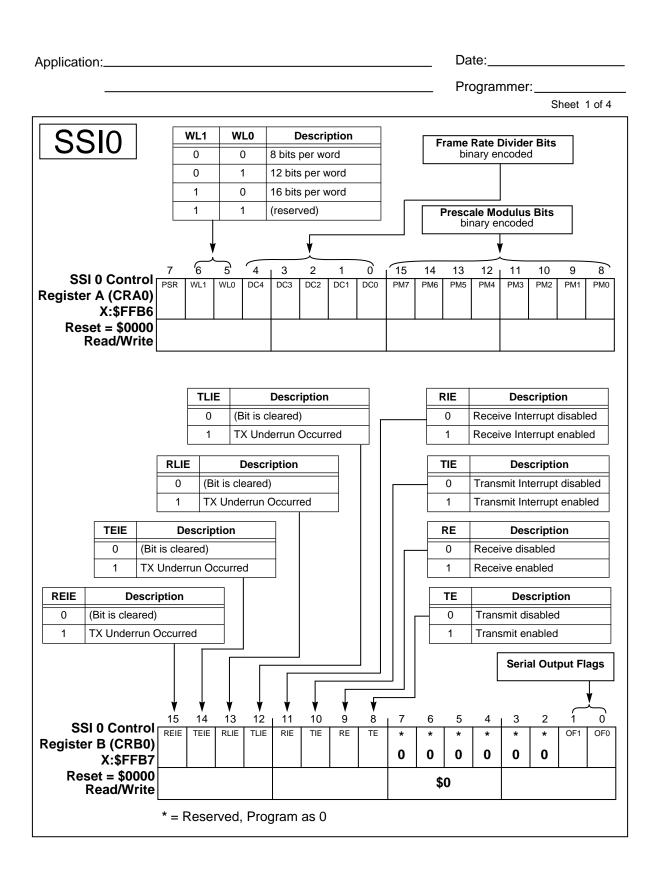

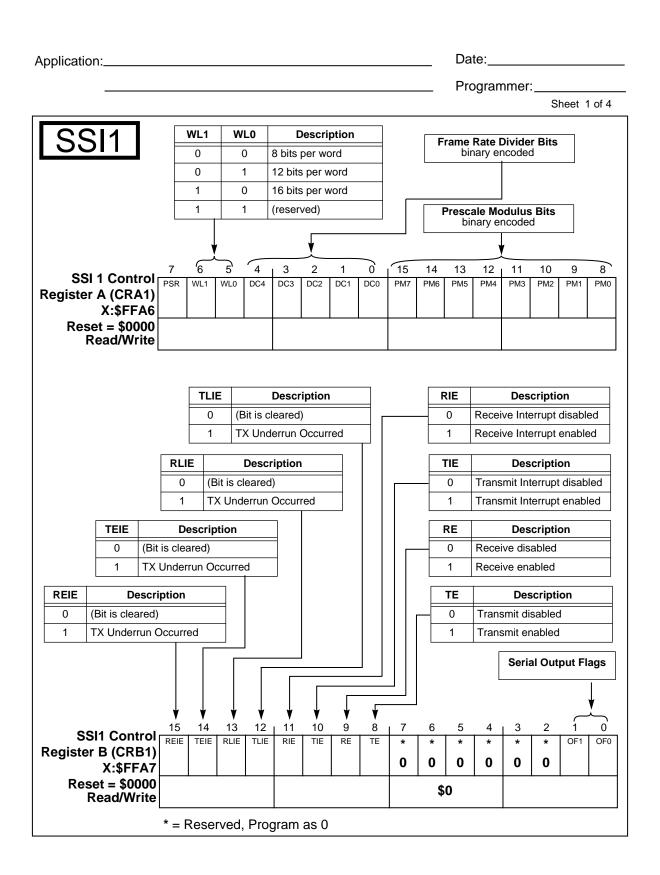

| 8.3.1   | SSI Control Register A (CRA)                | 8-7  |

| 8.3.1.1 | Prescale Modulus Select (PM0–PM7)—Bits 0–7. | 8-8  |

| 8.3.1.2<br>8.3.1.3 | Frame Rate Divider Control (DC4–DC0)—Bits 8–12<br>Word Length Control (WL0–WL1)—Bits 13–14 |        |

|--------------------|--------------------------------------------------------------------------------------------|--------|

| 8.3.1.4            | Prescaler Range (PSR)—Bit 15                                                               |        |

| 8.3.2              | SSI Control Register B (CRB)                                                               |        |

| 8.3.2.1            | Serial Output Flag 0 (OF0)—Bit 0                                                           |        |

| 8.3.2.2            | Serial Output Flag 1 (OF1)—Bit 1                                                           |        |

| 8.3.2.3            | Reserved Bits 2–7.                                                                         |        |

| 8.3.2.4            | Transmit Enable (TE)—Bit 8                                                                 |        |

| 8.3.2.5            | Receive Enable (RE)—Bit 9                                                                  |        |

| 8.3.2.6            | Transmit Interrupt Enable (TIE)—Bit 10                                                     |        |

| 8.3.2.7            | Receive Interrupt Enable (RIE)—Bit 11                                                      |        |

| 8.3.2.8            | Transmit Last Slot Interrupt Enable (TLIE)—Bit 12.                                         |        |

| 8.3.2.9            | Receive Last Slot Interrupt Enable (RLIE)—Bit 13.                                          |        |

| 8.3.2.10           | Transmit Exception Interrupt Enable (TEIE)—Bit 14.                                         |        |

| 8.3.2.11           | Receive Exception Interrupt Enable (REIE)—Bit 15.                                          |        |

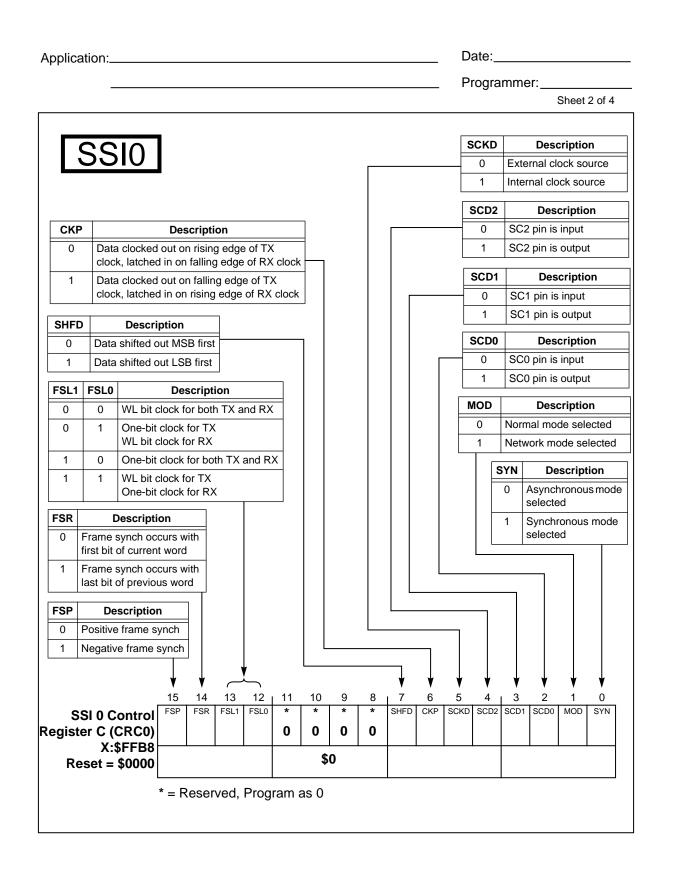

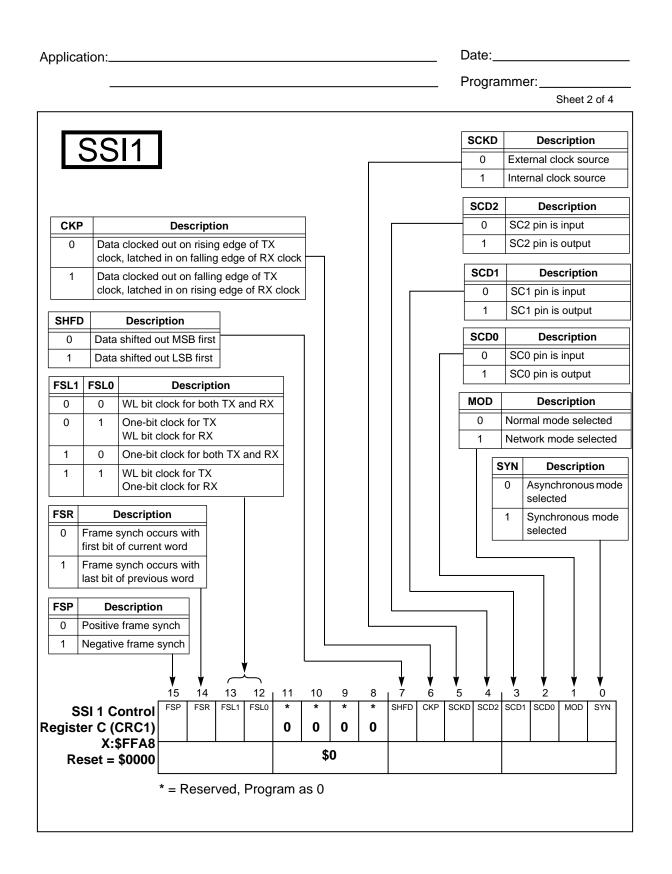

| 8.3.3              | SSI Control Register C (CRC)                                                               |        |

| 8.3.3.1            | Asynchronous /Synchronous (SYN)—Bit 0                                                      | . 8-14 |

| 8.3.3.2            | SSI Mode Select (MOD)—Bit 1                                                                | . 8-14 |

| 8.3.3.3            | Serial Control 0 Direction (SCD0)—Bit 2                                                    | . 8-14 |

| 8.3.3.4            | Serial Control 1 Direction (SCD1) —Bit 3                                                   | . 8-14 |

| 8.3.3.5            | Serial Control 2 Direction (SCD2)—Bit 4                                                    | . 8-14 |

| 8.3.3.6            | Clock Source Direction (SCKD)—Bit 5                                                        | . 8-15 |

| 8.3.3.7            | Clock Polarity (CKP)—Bit 6                                                                 | . 8-15 |

| 8.3.3.8            | Shift Direction (SHFD)—Bit 7                                                               | . 8-15 |

| 8.3.3.9            | Reserved Bits 8–11                                                                         | . 8-15 |

| 8.3.3.10           | Frame Sync Length (FSL0–FSL1)—Bits 12–13                                                   |        |

| 8.3.3.11           | Frame Sync Relative Timing (FSR)—Bit 14                                                    | . 8-16 |

| 8.3.3.12           | Frame Sync Polarity (FSP)—Bit 15                                                           |        |

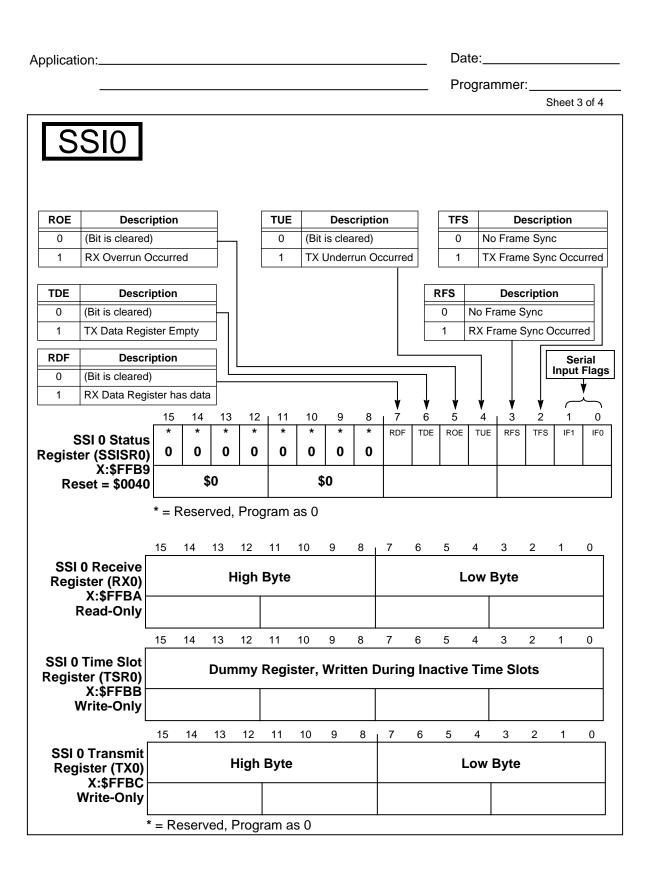

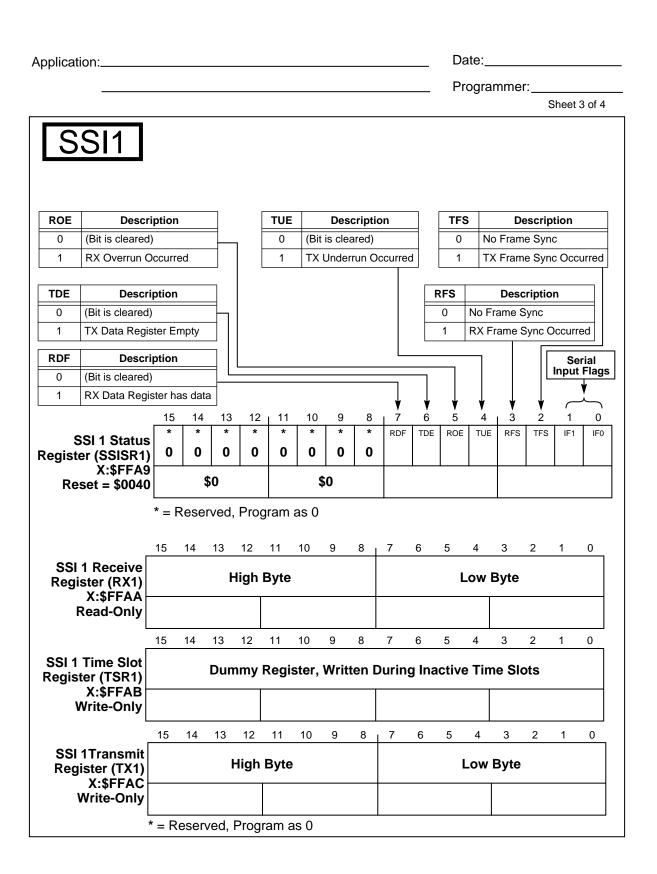

| 8.3.4              | SSI Status Register (SSISR)                                                                |        |

| 8.3.4.1            | Serial Input Flag 0 (IF0)—Bit 0                                                            |        |

| 8.3.4.2            | Serial Input Flag 1 (IF1)—Bit 1                                                            |        |

| 8.3.4.3            | Transmit Frame Sync Flag (TFS)—Bit 2                                                       |        |

| 8.3.4.4            | Receive Frame Sync Flag (RFS)—Bit 3                                                        |        |

| 8.3.4.5            | Transmitter Underrun Error Flag (TUE)—Bit 4                                                |        |

| 8.3.4.6            | Receiver Overrun Error Flag (ROE)—Bit 5                                                    |        |

| 8.3.4.7            | Transmit Data Register Empty (TDE)—Bit 6                                                   | . 8-18 |

| 8.3.4.8  | Receive Data Register Full (RDF)—Bit 7            | 8-19  |

|----------|---------------------------------------------------|-------|

| 8.3.4.9  | Reserved Bits 8–15                                | 8-19  |

| 8.3.5    | Receive Shift Register                            | 8-19  |

| 8.3.6    | Receive Data Register (RX)                        | 8-19  |

| 8.3.7    | Transmit Shift Register                           | 8-19  |

| 8.3.8    | Transmit Data Register (TX)                       | 8-20  |

| 8.3.9    | Time Slot Register (TSR)                          | 8-20  |

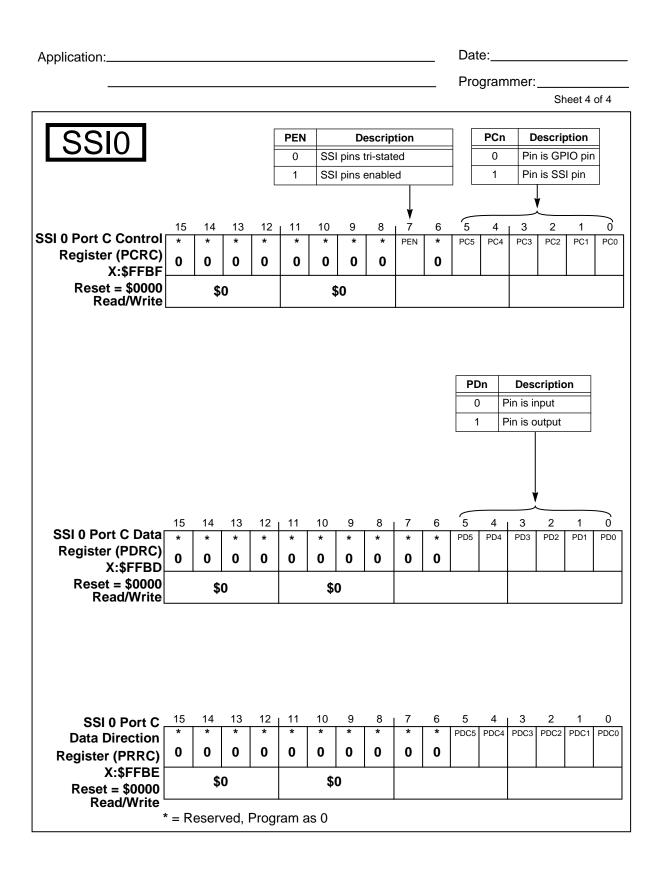

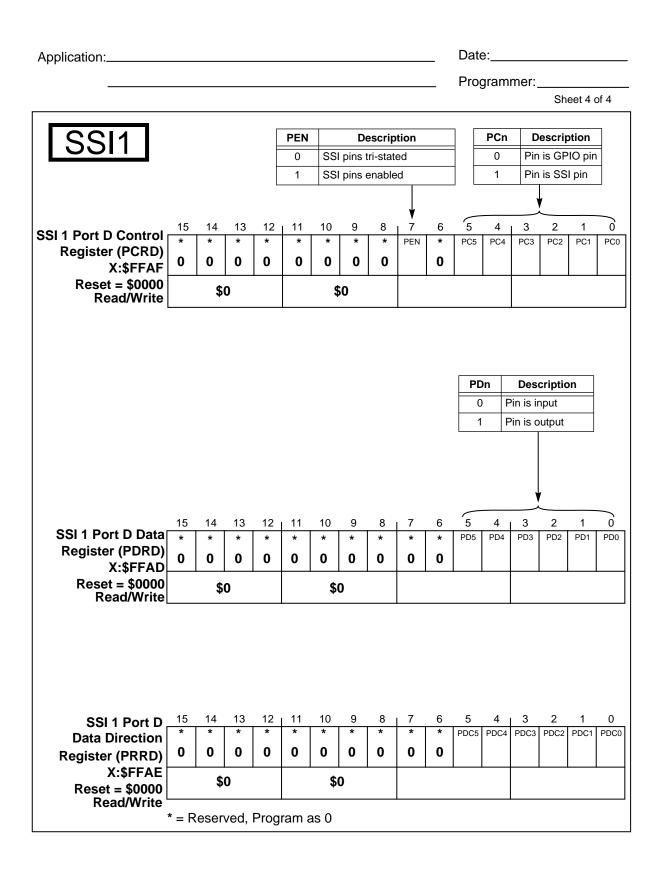

| 8.3.10   | Port Control Register (PCR)                       | 8-20  |

| 8.3.10.1 | Port Control (PC0–PC5)—Bits 0–5                   |       |

| 8.3.10.2 | Port Enable (PEN)—Bit 7                           | 8-21  |

| 8.3.10.3 |                                                   | 8-21  |

| 8.3.11   | Port Direction Register (PRR)                     | 8-21  |

| 8.3.12   | Port Data Register (PDR)                          | 8-22  |

| 8.4      | OPERATING MODES                                   | 8-23  |

| 8.4.1    | SSI Exceptions                                    | 8-24  |

| 8.4.2    | Operating Modes–Normal, Network, and On-Demand    | 8-25  |

| 8.4.2.1  | Operating Mode Selection                          | 8-25  |

| 8.4.2.2  | Synchronous/Asynchronous Operating Modes          | 8-25  |

| 8.4.2.3  | Frame Sync Selection                              | 8-26  |

| 8.4.2.4  | Shift Direction Selection                         | 8-27  |

| 8.4.3    | Serial I/O Flags                                  | 8-27  |

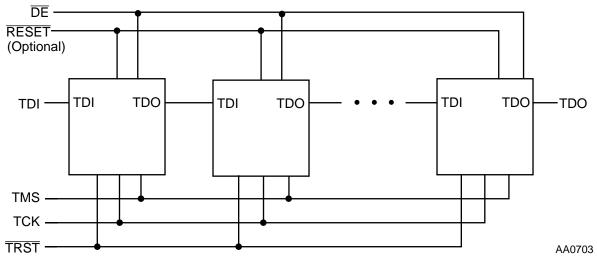

| SECTIO   | N 9 TRIPLE TIMER MODULE                           | . 9-1 |

| 9.1      | INTRODUCTION                                      | . 9-3 |

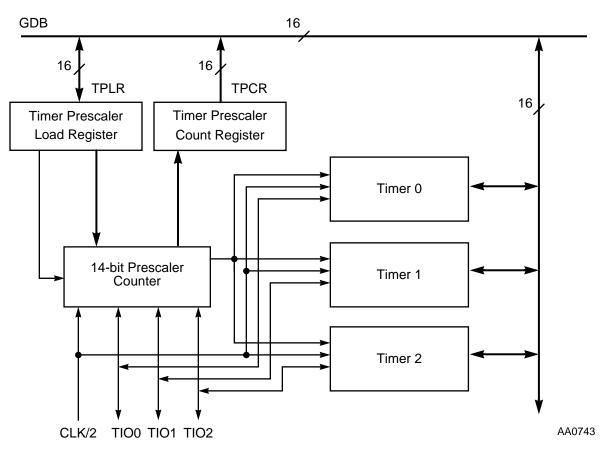

| 9.2      | TRIPLE TIMER MODULE ARCHITECTURE                  |       |

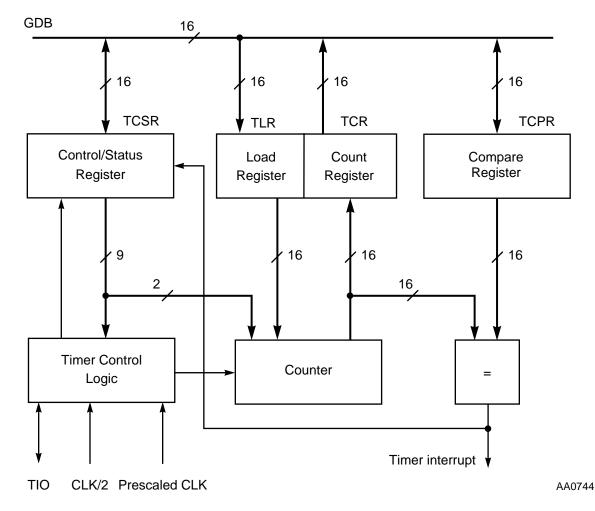

| 9.3      | TIMER ARCHITECTURE                                | . 9-4 |

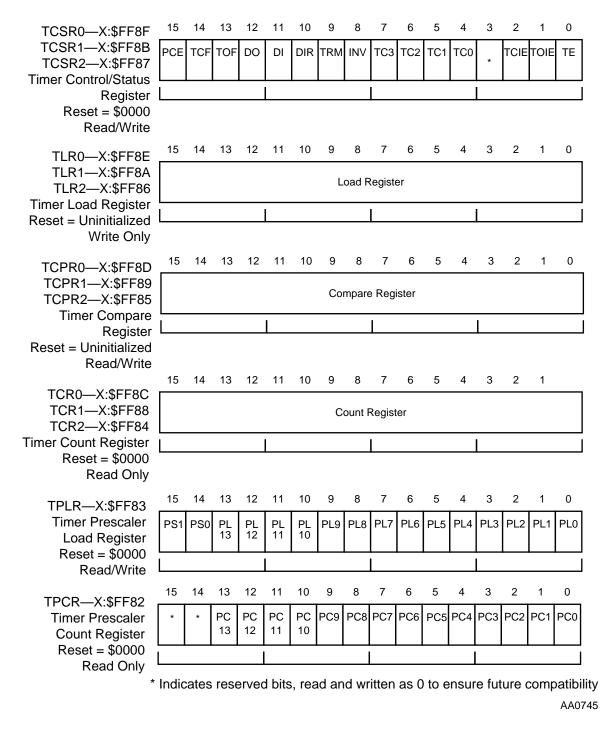

| 9.4      | TRIPLE TIMER MODULE PROGRAMMING MODEL             | . 9-6 |

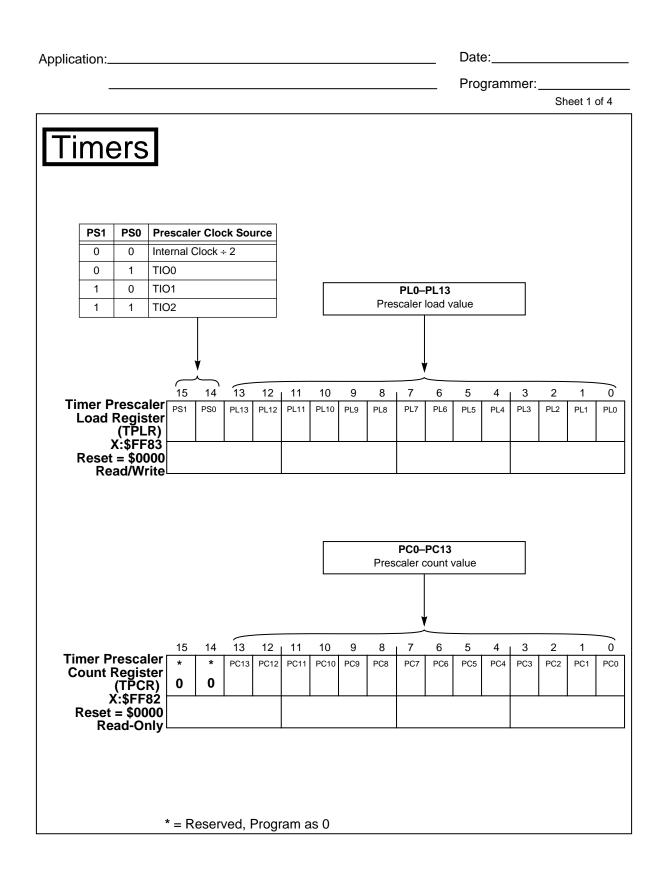

| 9.4.1    | Timer Prescaler Load Register (TPLR)              | . 9-7 |

| 9.4.1.1  | Prescaler Preload Value Bits (PL0-PL13)-Bits 0-13 |       |

| 9.4.1.2  | Prescaler Source Bits (PS0–PS1)—Bits 14–15        | . 9-7 |

| 9.4.2    | Timer Prescaler Count Register (TPCR)             | . 9-8 |

| 9.4.2.1  | Prescaler Counter Value Bits                      |       |

|          | (PC0–PC13)—Bits 0–13                              | . 9-8 |

| 9.4.2.2  | Reserved Bits (Bits 14–15)                        | . 9-8 |

| 9.4.3    | Timer Count Register (TCR)                        | . 9-8 |

| 9.4.4    | Timer Load Register (TLR)                         | . 9-8 |

| 9.4.5    | Timer Compare Register (TCPR)                        |

|----------|------------------------------------------------------|

| 9.4.6    | Timer Control/Status Register (TCSR)                 |

| 9.4.6.1  | Timer Enable Bit (TE)—Bit 0                          |

| 9.4.6.2  | Timer Overflow Interrupt Enable Bit (TOIE)—Bit 1 9-9 |

| 9.4.6.3  | Timer Compare Interrupt Enable Bit (TCIE)–Bit 29-9   |

| 9.4.6.4  | Timer Control Bits (TC0–TC3)—Bits 4–7                |

| 9.4.6.5  | Inverter Bit (INV)—Bit 8                             |

| 9.4.6.6  | Timer Reload Mode Bit (TRM)—Bit 9                    |

| 9.4.6.7  | Direction Bit (DIR)—Bit 10                           |

| 9.4.6.8  | Data Input Bit (DI)—Bit 11                           |

| 9.4.6.9  | Data Output Bit (DO)—Bit 12                          |

| 9.4.6.10 | Timer Overflow Flag Bit (TOF)—Bit 139-12             |

| 9.4.6.11 | Timer Compare Flag Bit (TCF)—Bit 149-12              |

| 9.4.6.12 | Prescaled Clock Enable Bit (PCE)—Bit 15 9-12         |

| 9.4.6.13 | Reserved Bit 3                                       |

| 9.5      | TIMER MODES OF OPERATION9-13                         |

| 9.5.1    | Timer Modes                                          |

| 9.5.1.1  | Mode 0—Timer Mode, No Output (Internal Clock) 9-14   |

| 9.5.1.2  | Mode 1—Timer Mode, Output Pulse Enable               |

|          | (Internal Clock)                                     |

| 9.5.1.3  | Mode 2—Timer Mode, Output Toggle Enable              |

|          | (Internal Clock)                                     |

| 9.5.1.4  | Mode 3—Timer Mode, Event Counter                     |

|          | (External Clock)9-15                                 |

| 9.5.2    | Measurement Modes 9-16                               |

| 9.5.2.1  | Mode 4—Pulse Width Measurement Mode9-16              |

| 9.5.2.2  | Mode 5—Period Measurement Mode                       |

| 9.5.2.3  | Mode 6—Capture Mode                                  |

| 9.5.3    | PWM Mode9-17                                         |

| 9.5.3.1  | Mode 7—Pulse Width Modulation Mode, Output           |

|          | Toggle Enable (Internal Clock)                       |

| 9.5.4    | Watchdog Modes9-18                                   |

| 9.5.4.1  | Mode 9—Watchdog Mode, Output Pulse Enable            |

|          | (Internal Clock)                                     |

| 9.5.4.2  | Mode 10—Watchdog Mode, Output Toggle Enable          |

|          | (Internal Clock)                                     |

| 9.5.5 Reserved Modes                                      | 9  |

|-----------------------------------------------------------|----|

| 9.5.6 Timer Behavior During WAIT and STOP Instructions9-1 | 9  |

|                                                           |    |

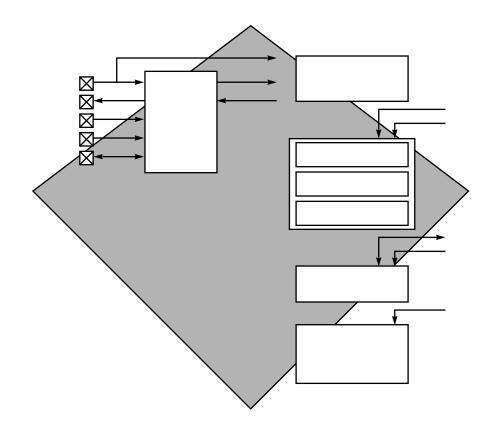

| SECTION 10 ON-CHIP EMULATION MODULE                       |    |

| 10.1 INTRODUCTION                                         |    |

| 10.2 ONCE MODULE PINS                                     | -3 |

| 10.2.1 Debug Event (DE)                                   |    |

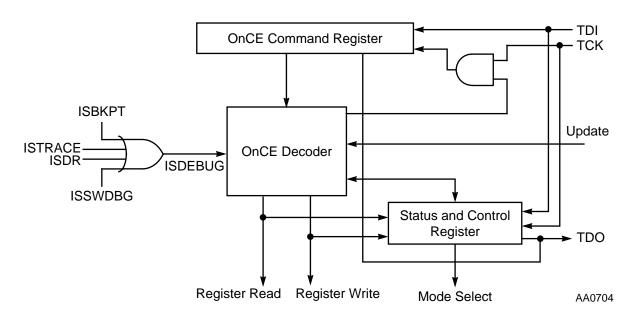

| 10.3 ONCE CONTROLLER                                      |    |

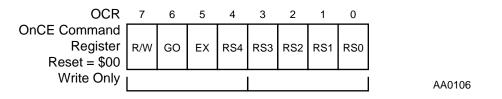

| 10.3.1 OnCE Command Register (OCR)                        | -5 |

| 10.3.1.1 Register Select Bits (RS4–RS0)—Bits 0–4 10-      | -6 |

| 10.3.1.2 Exit Command Bit (EX)—Bit 5                      | -7 |

| 10.3.1.3 GO Command Bit (GO)—Bit 6                        | -7 |

| 10.3.1.4 Read/Write Command Bit (R/W)—Bit 7 10-           |    |

| 10.3.2 OnCE Decoder (ODEC) 10-                            | -8 |

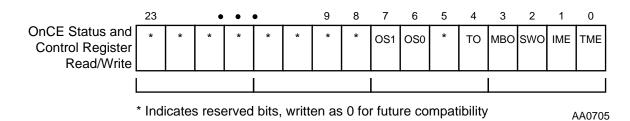

| 10.3.3 OnCE Status and Control Register (OSCR) 10-        | -8 |

| 10.3.3.1 Trace Mode Enable Bit (TME)—Bit 0 10-            | -9 |

| 10.3.3.2 Interrupt Mode Enable Bit (IME)—Bit 1 10-        | -9 |

| 10.3.3.3 Software Debug Occurrence Bit (SWO)—Bit 2 10-    | -9 |

| 10.3.3.4 Memory Breakpoint Occurrence Bit (MBO)—Bit 3 10- | -9 |

| 10.3.3.5 Trace Occurrence Bit (TO)—Bit 4                  | -9 |

| 10.3.3.6 Reserved Bit 5                                   | -9 |

| 10.3.3.7 Core Status Bits (OS0–OS1)—Bits 6-7 10-          | -9 |

| 10.3.3.8 Reserved Bits 8–23                               | 0  |

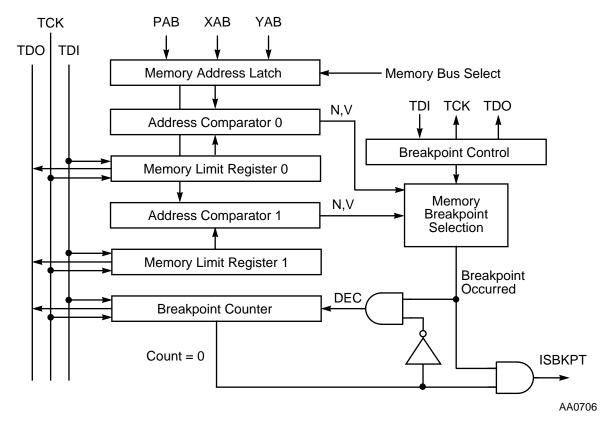

| 10.4 ONCE MEMORY BREAKPOINT LOGIC                         | 0  |

| 10.4.1 OnCE Memory Address Latch (OMAL)                   | 1  |

| 10.4.2 OnCE Memory Limit Register 0 (OMLR0) 10-1          | 2  |

| 10.4.3 OnCE Memory Address Comparator 0 (OMAC0) 10-1      | 2  |

| 10.4.4 OnCE Memory Limit Register 1 (OMLR1) 10-1          | 2  |

| 10.4.5 OnCE Memory Address Comparator 1 (OMAC1) 10-1      | 2  |

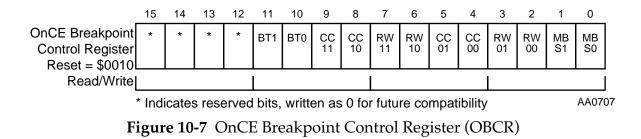

| 10.4.6 OnCE Breakpoint Control Register (OBCR) 10-1       | 2  |

| 10.4.6.1 Memory Breakpoint Select Bits                    |    |

| (MBS0–MBS1)–Bits 0–1                                      | 3  |

| 10.4.6.2 Breakpoint 0 Read/Write Select Bits              |    |

| (RW00–RW01)—Bits 2–3                                      | 3  |

| 10.4.6.3 Breakpoint 0 Condition Code Select Bits          |    |

| (CC00–CC01)—Bits 4–5                                      | 3  |

| 10.4.6.4 | Breakpoint1 Read/Write Select Bits              |       |

|----------|-------------------------------------------------|-------|

|          | (RW10–RW11)—Bits 6–7                            | 10-14 |

| 10.4.6.5 | Breakpoint1 Condition Code Select Bits          |       |

|          | (CC10–CC11)—Bits 8–9                            | 10-14 |

| 10.4.6.6 | Breakpoint 0 and 1 Event Select Bits            |       |

|          | (BT0–BT1)—Bits 10–11                            | 10-15 |

| 10.4.6.7 | Reserved Bits 12–15                             | 10-15 |

| 10.4.7   | OnCE Memory Breakpoint Counter (OMBC)           | 10-15 |

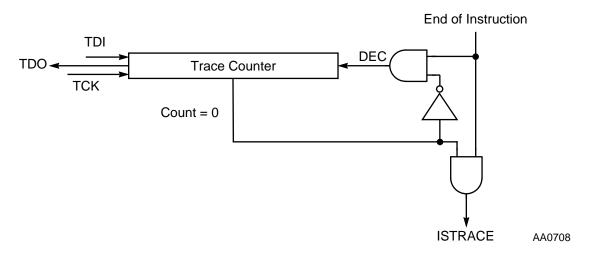

| 10.5     | ONCE TRACE LOGIC                                |       |

| 10.5.1   | OnCE Trace Counter (OTC)                        | 10-17 |

| 10.6     | METHODS OF ENTERING THE DEBUG MODE              | 10-17 |

| 10.6.1   | External Debug Request During RESET Assertion   | 10-17 |

| 10.6.2   | External Debug Request During Normal Activity   | 10-17 |

| 10.6.3   | Executing the JTAG DEBUG_REQUEST Instruction    | 10-18 |

| 10.6.4   | External Debug Request During Stop              | 10-18 |

| 10.6.5   | External Debug Request During Wait              | 10-18 |

| 10.6.6   | Software Request During Normal Activity         | 10-19 |

| 10.6.7   | Enabling Trace Mode                             |       |

| 10.6.8   | Enabling Memory Breakpoints                     | 10-19 |

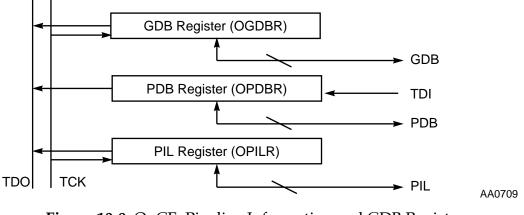

| 10.7     | PIPELINE INFORMATION AND OGDB REGISTER          | 10-19 |

| 10.7.1   | OnCE PDB Register (OPDBR)                       | 10-20 |

| 10.7.2   | OnCE PIL Register (OPILR)                       | 10-20 |

| 10.7.3   | OnCE GDB Register (OGDBR)                       | 10-21 |

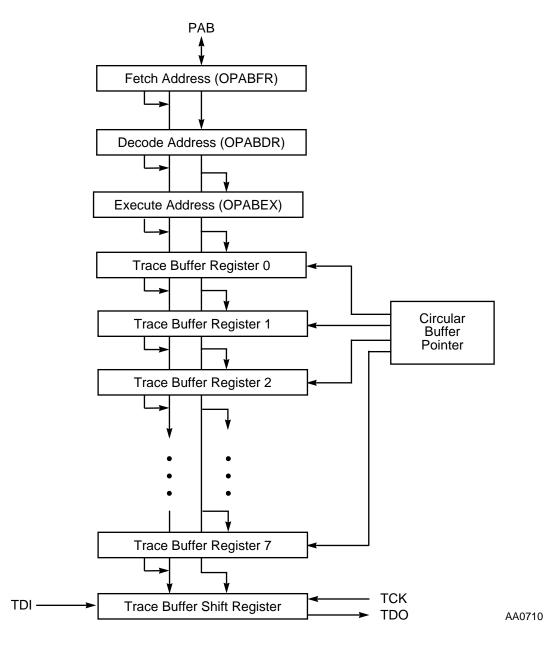

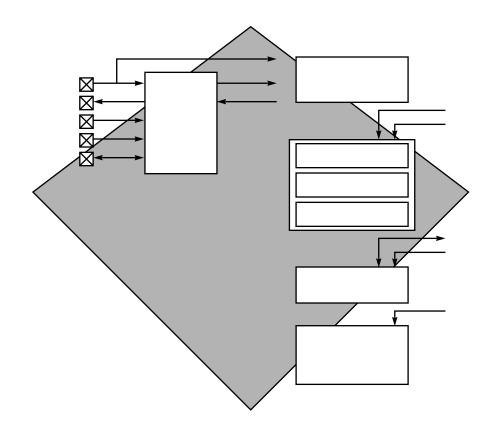

| 10.8     | TRACE BUFFER                                    | 10-21 |

| 10.8.1   | OnCE PAB Register for Fetch (OPABFR)            |       |

| 10.8.2   | PAB Register for Decode (OPABDR)                | 10-21 |

| 10.8.3   | OnCE PAB Register for Execute (OPABEX)          | 10-22 |

| 10.8.4   | Trace Buffer                                    |       |

| 10.9     | SERIAL PROTOCOL DESCRIPTION                     | 10-24 |

| 10.9.1   | OnCE Commands                                   |       |

| 10.10    | TARGET SITE DEBUG SYSTEM REQUIREMENTS           |       |

| 10.11    | EXAMPLES OF USING THE ONCE                      | 10-25 |

| 10.11.1  | Checking Whether the Chip has Entered the Debug |       |

|          | Mode                                            |       |

| 10.11.2  | Polling the JTAG Instruction Shift Register     |       |

| 10.11.3  | Saving Pipeline Information                     | 10-26 |

| 10.11.4 Decision the Trees Duffer                           | 10.00      |

|-------------------------------------------------------------|------------|

| 10.11.4 Reading the Trace Buffer                            |            |

| 10.11.5 Displaying a Specified Register                     |            |

| 10.11.6 Displaying X Memory Area Starting at Address \$xxxx | . 10-28    |

| 10.11.7 Returning from Debug Mode to Normal Mode to         |            |

| Current Program                                             | . 10-29    |

| 10.11.8 Returning from Debug Mode to Normal Mode to a       |            |

| New Program                                                 | . 10-30    |

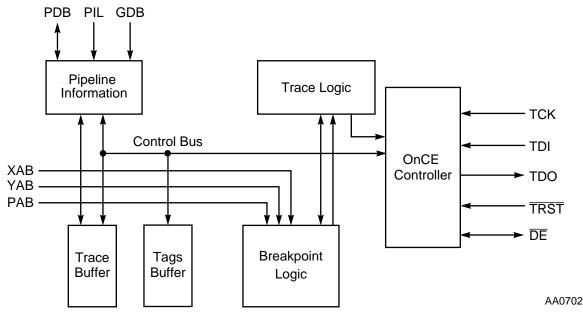

| 10.12 EXAMPLES OF JTAG AND ONCE INTERACTION                 |            |

|                                                             |            |

| SECTION 11 JTAG PORT                                        |            |

| 11.1 INTRODUCTION                                           |            |

| 11.2 JTAG PINS                                              |            |

| 11.2.1 Test Clock (TCK)                                     | 11-5       |

| 11.2.2 Test Mode Select (TMS)                               | 11-5       |

| 11.2.3 Test Data Input (TDI)                                | 11-5       |

| 11.2.4 Test Data Output (TDO)                               |            |

| 11.2.5 Test Reset (TRST)                                    | 11-5       |

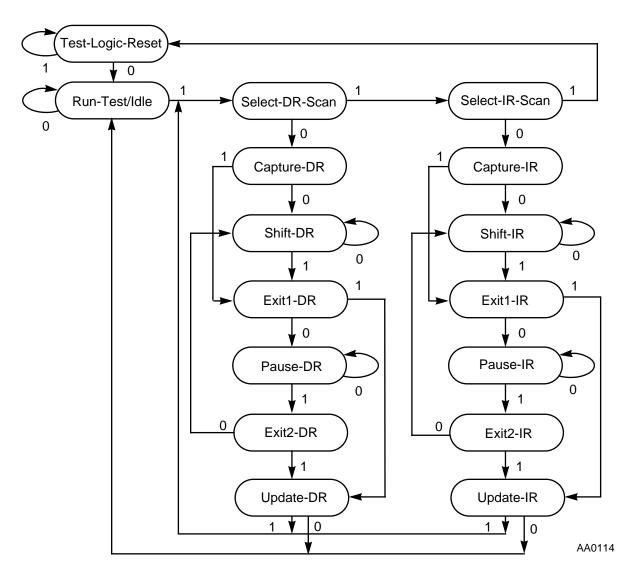

| 11.3 TAP CONTROLLER                                         |            |

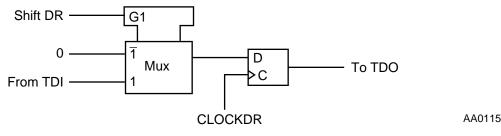

| 11.3.1 Boundary Scan Register                               |            |

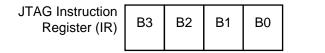

| 11.3.2 Instruction Register                                 |            |

| 11.3.2.1 EXTEST (B[3:0] = 0000)                             |            |

| 11.3.2.2 SAMPLE/PRELOAD (B[3:0] = 0001)                     |            |

| 11.3.2.3 IDCODE (B[3:0] = 0010).                            |            |

| 11.3.2.4 CLAMP (B[3:0] = 0011)                              |            |

| 11.3.2.5 HI-Z (B[3:0] = 0100)                               |            |

| 11.3.2.6 ENABLE_ONCE(B[3:0] = 0110)                         |            |

| 11.3.2.7 DEBUG_REQUEST(B[3:0] = 0111)                       |            |

| 11.3.2.7.1 BYPASS (B[3:0] = 1111)                           |            |

| 11.4 DSP56600 RESTRICTIONS                                  |            |

|                                                             |            |

| APPENDIX A BOOTSTRAP PROGRAM                                | A-1        |

| A.1 DSP56603 BOOTSTRAP LISTING                              | A-3        |

| APPENDIX B X I/O EQUATES                                    | <b>R_1</b> |

| B.1 DSP56603 X I/O EQUATES                                  |            |

|                                                             |            |

| B.2 DSP56603 INTERRUPT EQUATES                              | D-10       |

| APP | ENDIX C | PROGRAMMER'S REFERENCE          | C-1   |

|-----|---------|---------------------------------|-------|

| C.1 | INTRO   |                                 | C-3   |

| C.2 | INSTRU  | ICTION SET SUMMARY              | C-3   |

| C.3 | INTERF  | UPT, VECTOR, AND ADDRESS TABLES | SC-14 |

| C.4 | PROGR   | AMMER'S SHEETS                  | C-23  |

## LIST OF FIGURES

| Figure 1-1 | DSP56603 Block Diagram                                   |

|------------|----------------------------------------------------------|

| Figure 2-1 | DSP56603 Signals Identified by Functional Group 2-4      |

| Figure 3-1 | DSP56603 Memory Map                                      |

| Figure 4-1 | Operating Mode Register (OMR) Programming Model 4-4      |

| Figure 4-2 | Status Register Programming Model                        |

| Figure 4-3 | DSP Device ID (IDR) Register for DSP56603 4-8            |

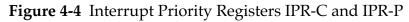

| Figure 4-4 | Interrupt Priority Registers IPR-C and IPR-P 4-14        |

| Figure 4-5 | PLL Control Register 0 (PCTL0) Programming Model 4-17    |

| Figure 4-6 | PLL Control Register 1 (PCTL1) Programming Model 4-18    |

| Figure 5-1 | Static RAM Connection Diagram 5-5                        |

| Figure 5-2 | Bus Operation, One Wait State—SRAM Access 5-6            |

| Figure 5-3 | Bus Control Register Programming Model 5-7               |

| Figure 5-4 | BPMR Register                                            |

| Figure 5-5 | Possible Address Tracing Configuration Diagram 5-12      |

| Figure 6-1 | GPIO Programming Model 6-4                               |

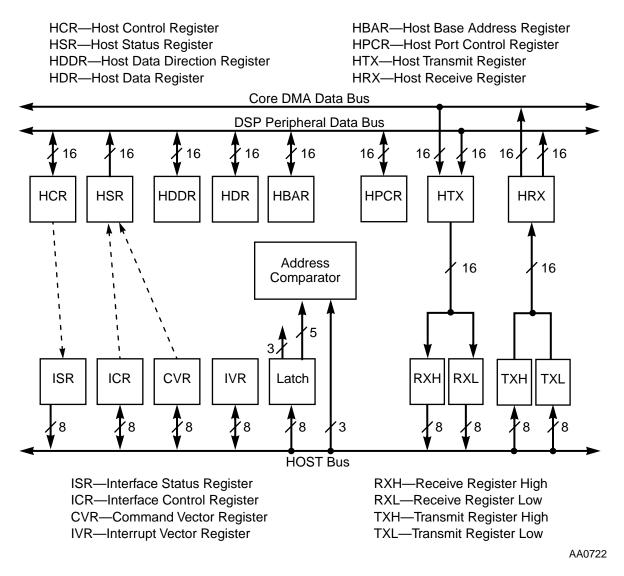

| Figure 7-1 | HI08 Block Diagram                                       |

| Figure 7-2 | Host Control Register Programming Model                  |

| Figure 7-3 | Host Status Register (HSR) Programming Model 7-10        |

| Figure 7-4 | Host Port Control Register (HPCR) Programming Model 7-12 |

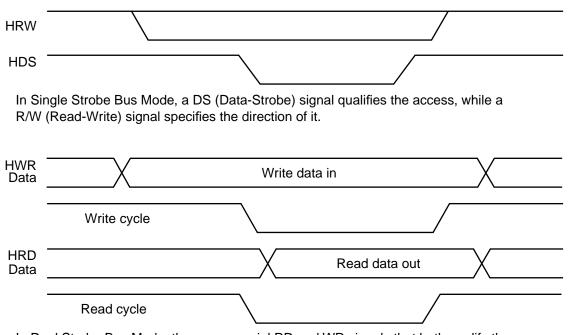

| Figure 7-5 | Single and Dual Strobe Bus Modes                         |

| Figure 7-6  | Host Data Direction Register (HDDR) Programming Model 7-16 |

|-------------|------------------------------------------------------------|

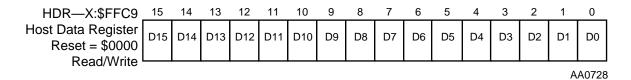

| Figure 7-7  | Host Data Register (HDR) Programming Model                 |

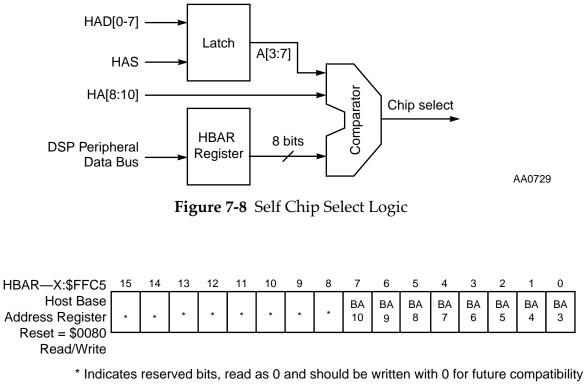

| Figure 7-8  | Self Chip Select Logic                                     |

| Figure 7-9  | Host Base Address Register (HBAR) Programming Model 7-18   |

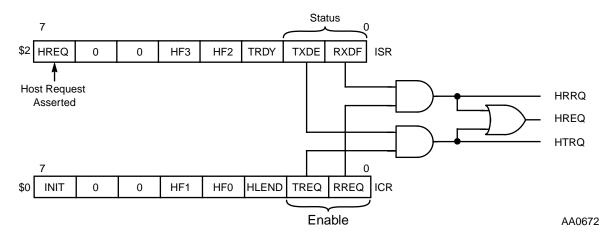

| Figure 7-10 | HSR–HCR Operation                                          |

| Figure 7-11 | Interface Control Register Programming Model               |

| Figure 7-12 | Command Vector Register (CVR)                              |

| Figure 7-13 | Interface Status Register Programming Model                |

| Figure 7-14 | Interrupt Vector Register (IVR)7-28                        |

| Figure 7-15 | HI08 Host Request Structure                                |

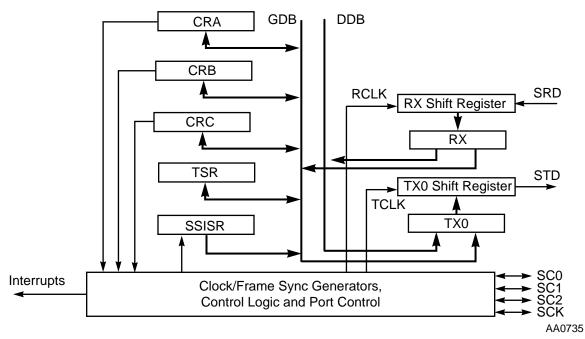

| Figure 8-1  | SSI Block Diagram                                          |

| Figure 8-2  | SSI Control Register A Programming Model                   |

| Figure 8-3  | SSI Control Register B Programming Model                   |

| Figure 8-4  | SSI Control Register C Programming Model 8-14              |

| Figure 8-5  | SSI Status Register Programming Model 8-17                 |

| Figure 8-6  | SSI Port Control Register Programming Model 8-21           |

| Figure 8-7  | SSI GPIO Direction Control Register Programming Model 8-22 |

| Figure 8-8  | SSI GPIO Data Register Programming Model 8-23              |

| Figure 9-1  | Triple Timer Module Block Diagram                          |

| Figure 9-2  | 16-bit Timer Module Block Diagram                          |

| Figure 9-3  | Triple Timers Programming Model                            |

| Figure 10-1 | OnCE Module Block Diagram 10-3                             |

| Figure 10-2  | OnCE Module Multiprocessor Configuration 10-4     |

|--------------|---------------------------------------------------|

| Figure 10-3  | OnCE Controller Block Diagram 10-5                |

| Figure 10-4  | OnCE Command Register                             |

| Figure 10-5  | OnCE Status and Control Register (OSCR) 10-8      |

| Figure 10-6  | OnCE Memory Breakpoint Logic 0 10-11              |

| Figure 10-7  | OnCE Breakpoint Control Register (OBCR) 10-12     |

| Figure 10-8  | OnCE Trace Logic Block Diagram                    |

| Figure 10-9  | OnCE Pipeline Information and GDB Registers 10-20 |

| Figure 10-10 | OnCE Trace Buffer 10-23                           |

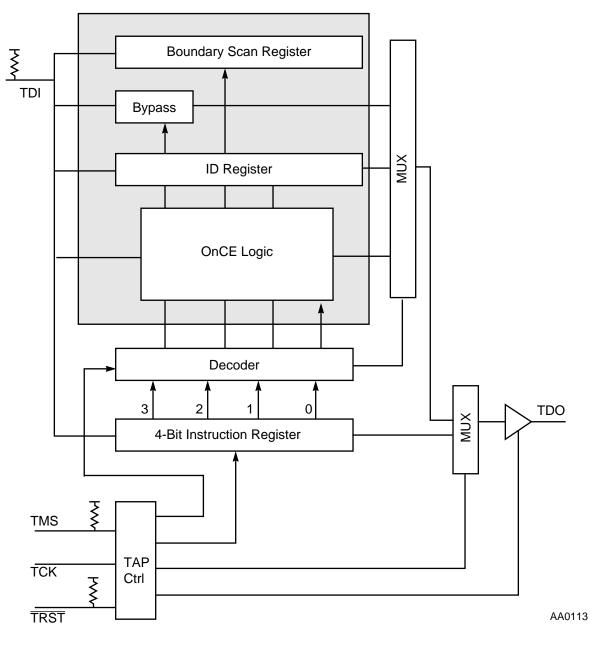

| Figure 11-1  | TAP Block Diagram                                 |

| Figure 11-2  | TAP Controller State Machine 11-6                 |

| Figure 11-3  | JTAG Instruction Register                         |

| Figure 11-4  | JTAG ID Register 11-10                            |

| Figure 11-5  | Bypass Register 11-12                             |

### LIST OF TABLES

| Table 1-1  | High True / Low True Signal Conventions                       |

|------------|---------------------------------------------------------------|

| Table 2-1  | Functional Group Signal Allocations                           |

| Table 2-2  | Power Inputs                                                  |

| Table 2-3  | Grounds                                                       |

| Table 2-4  | Clock and PLL Signals 2-7                                     |

| Table 2-5  | Interrupt and Mode Control Signals                            |

| Table 2-6  | Expansion Port, Port A Signals                                |

| Table 2-7  | Host Port Usage Considerations                                |

| Table 2-8  | Host Interface Signals                                        |

| Table 2-9  | Synchronous Serial Interface 0 (SSI0) 2-18                    |

| Table 2-10 | Synchronous Serial Interface 1 (SSI1) 2-21                    |

| Table 2-11 | General Purpose I/O (GPIO)                                    |

| Table 2-12 | Triple Timer Signals                                          |

| Table 2-13 | JTAG Interface/On-Chip Emulator Interface (OnCE) Signals 2-26 |

| Table 3-1  | Switch Mode Memory Configuration                              |

| Table 3-2  | Internal I/O Memory Map 3-5                                   |

| Table 4-1  | Patch JUMP Targets 4-4                                        |

| Table 4-2  | DSP566603 Reset Addresses                                     |

| Table 4-3  | Interrupt Sources 4-12                                        |

| Table 4-4  | Interrupt Priority Level Bits 4-15                            |

| Table 4-5  | External Interrupt Trigger Mode Bits      |

|------------|-------------------------------------------|

| Table 4-6  | Interrupt Source Priorities within an IPL |

| Table 4-7  | Multiplication Factor Bits MF0–MF114-18   |

| Table 4-8  | Division Factor Bits                      |

| Table 6-1  | PCR and PRR Bits Functionality 6-5        |

| Table 7-1  | Summary of HI08 Pins and Operating Modes  |

| Table 7-2  | Strobe Signals Support Pins               |

| Table 7-3  | Host Request Support Pins                 |

| Table 7-4  | HI08 Interrupt Request Priority Order     |

| Table 7-5  | HDR and HDDR Bits Functionality           |

| Table 7-6  | DSP Side Registers after Reset            |

| Table 7-7  | HI08 Host Side Register Map7-22           |

| Table 7-8  | TREQ and HREQ Modes (HDRQ = 0)7-23        |

| Table 7-9  | TREQ and HREQ Modes (HDRQ = 1)7-23        |

| Table 7-10 | INIT Commands                             |

| Table 7-11 | Host Side Registers After Reset           |

| Table 8-1  | SSI Clock Sources                         |

| Table 8-2  | SSI Word Length Selection8-9              |

| Table 8-3  | Mode and Pin Definition Table             |

| Table 8-4  | FSL1 and FSL0 Encoding8-16                |

| Table 8-5  | PCR and PRR Register Bits Functionality   |

| Table 9-1  | PS Bit Functionality                      |

| Table 9-2   | TC Bit Functionality 9-10                                   |

|-------------|-------------------------------------------------------------|

| Table 9-3   | Timer Mode Summary                                          |

| Table 10-1  | OnCE Register Select Encoding 10-6                          |

| Table 10-2  | EX Bit Definition                                           |

| Table 10-3  | GO Bit Definition 10-7                                      |

| Table 10-4  | R/W Bit Definition 10-8                                     |

| Table 10-5  | Core Status Bits Description 10-10                          |

| Table 10-6  | Memory Breakpoint 0 and 1 Select Table                      |

| Table 10-7  | Breakpoint 0 Read/Write Select Table 10-13                  |

| Table 10-8  | Breakpoint 0 Condition Select Table 10-14                   |

| Table 10-9  | Breakpoint 1 Read/Write Select Table 10-14                  |

| Table 10-10 | Breakpoint 1 Condition Select Table 10-14                   |

| Table 10-11 | Breakpoint 0 and 1 Event Select Table 10-15                 |

| Table 10-12 | TMS Sequencing for DEBUG_REQUEST                            |

| Table 10-13 | TMS Sequencing for ENABLE_ONCE 10-32                        |

| Table 10-14 | TMS Sequencing for Reading Pipeline Registers 10-32         |

| Table 11-1  | JTAG Instructions 11-8                                      |

| Table 11-2  | DSP56603 Boundary Scan Register (BSR) Bit Definitions 11-13 |

| Table C-1   | Program Word and Timing Symbols                             |

| Table C-2   | Condition Code Register (CCR) Symbols                       |

| Table C-3   | Condition Code Register NotationC-4                         |

| Table C-4   | Instruction Set Summary C-4                                 |

| Table C-5 | Interrupt Sources                           | 14 |

|-----------|---------------------------------------------|----|

| Table C-6 | Interrupt Source Priorities within an IPLC- | 16 |

| Table C-7 | Internal I/O Memory MapC-                   | 17 |

| Table C-8 | List of Programmer's SheetsC-               | 23 |

## LIST OF EXAMPLES

| Example 1-1 | Sample Code Listing 1-5                                 |

|-------------|---------------------------------------------------------|

| Example 5-1 | Move from P Source Address to P Destination Address 5-9 |

| Example 5-2 | Bootstrap through External EPROM 5-9                    |

| Example 5-3 | Pass Program Memory Words to the OGDB Register 5-10     |

| Example A-1 | DSP56603 Bootstrap Listing A-3                          |

| Example B-1 | DSP56603 X I/O Equates B-3                              |

| Example B-2 | DSP56603 Interrupt Equates                              |

# SECTION 1 OVERVIEW

| 1.1 | INTRODUCTION                        |

|-----|-------------------------------------|

| 1.2 | MANUAL ORGANIZATION                 |

| 1.3 | MANUAL CONVENTIONS 1-4              |

| 1.4 | DSP56600 CORE DESCRIPTION           |

| 1.5 | DSP56600 CORE FUNCTIONAL BLOCKS 1-6 |

| 1.6 | INTERNAL BUSES                      |

| 1.7 | DSP56603 ARCHITECTURE OVERVIEW      |

#### 1.1 INTRODUCTION

This manual describes the DSP56603 16-bit Digital Signal Processor (DSP), its memory and operating modes, and its peripheral modules. This manual is intended to be used with the *DSP56600 Family Manual (DSP56600FM/AD)*, which describes the Central Processing Unit (CPU), programming models, and instruction set details. *DSP56603 Technical Data (DSP56603/D)* provides electrical specifications, timing, pinout, and packaging descriptions on the DSP56603. These documents, as well as Motorola's DSP development tools, can be obtained through a local Motorola Semiconductor Sales Office or authorized distributor.

To receive the latest information, access the Motorola DSP home page located at the address listed on the back cover of this document.

The DSP56603 is a member of the DSP56600 core-based family of programmable CMOS DSPs. This general purpose DSP combines processing power with configuration flexibility, making it an excellent cost-effective solution for signal processing and control functions.

#### 1.2 MANUAL ORGANIZATION

This manual is arranged in the following sections:

- **Section 1—Overview** provides a brief overview of the DSP56603, describes the structure of this document, and lists other documentation necessary to use this chip.

- Section 2—Signal/Connection Description provides a description of the signals present on the pins of the DSP56603, and how these signals are grouped into the various interfaces.

- Section 3—Memory Maps describes the on-chip memory, structures, registers, and interfaces.

- Section 4—Core Configuration describes the registers that must be programmed to properly configure the DSP56600 core when using the DSP56603.

- Section 5—External Memory Interface (Port A) describes the external memory interface, which is also referred to as Port A.

- **Section 6—GPIO** describes the dedicated GPIO interface, and the alternate GPIO functionality provided on certain on-chip interfaces.

#### **Manual Conventions**

- Section 7— Host Interface (HI08) describes the 8-bit HI08 host interface.

- Section 8—Synchronous Serial Interface describes the 16-bit Synchronous Serial Interface (SSI), which communicates with devices such as codecs, other DSPs, microprocessors, and peripherals, to provide the primary data input path. The SSI is a part of Port C.

- Section 9—Triple Timer Module describes the three internal timer/counter devices.

- Section 10—On-Chip Emulation Module describes the On-Chip Emulation (OnCE<sup>TM</sup>) module, which is accessed through the JTAG port.

- Section 11—JTAG Port describes the specifics of the JTAG port on the DSP56603.

- **Appendix A—Bootstrap Program** provides a listing of the bootstrap code used to start or reset the DSP56603.

- Appendix B—X I/O Equates lists the Input/Output equates for the DSP56603.

- **Appendix C—Programmer's Reference** provides programming references and master programming sheets used to program the DSP56603 registers.

- **Glossary** provides a listing of terms used in this manual.

- **Index** provides a cross-reference to topics in this manual.

#### 1.3 MANUAL CONVENTIONS

The following conventions are used in this manual:

- Bits within registers are always listed from Most Significant Bit (MSB) to Least Significant Bit (LSB).

- **Note:** Other manuals may use the opposite convention, with bits listed from LSB to MSB.

- Bits within a register are indicated AA[n:0] when more than one bit is involved in a description. For purposes of description, the bits are presented as if they are contiguous within a register. However, this is not always the case. Refer to the programming model diagrams or to the programmer's sheets to see the exact location of bits within a register.

- When a bit is described as "set," its value is 1. When a bit is described as "cleared," its value is 0.

- Pins or signals that are asserted low (made active when pulled to ground) have an overbar over their name, for example, the SSO pin is asserted low.

- Hex values are indicated with a dollar sign (\$) preceding the hex value as follows: \$FFFF is the X memory address for the Interrupt Priority Register—Core (IPR-C).

- Code examples are displayed in a monospaced font, as shown in **Example 1-1**.

| BFSET #\$0007,X:PCC; | Configure:                          | line 1 |

|----------------------|-------------------------------------|--------|

|                      | ; MISOO, MOSIO, SCKO for SPI master | line 2 |

|                      | ; ~SSO as PC3 for GPIO              | line 3 |

**Example 1-1** Sample Code Listing

- Pins or signals listed in code examples that are asserted low have a tilde in front of their names. In the previous example, line 3 refers to the  $\overline{SS0}$  pin (shown as ~sso).

- The word "assert" means that a high true (active high) signal is pulled high to V<sub>CC</sub> or that a low true (active low) signal is pulled low to ground. The word "deassert" means that a high true signal is pulled low to ground or that a low true signal is pulled high to V<sub>CC</sub>. See **Table 1-1**.

| Signal/Symbol | Logic State | Signal State | Voltage                      |

|---------------|-------------|--------------|------------------------------|

| PIN           | True        | Asserted     | Ground <sup>1</sup>          |

| PIN           | False       | Deasserted   | V <sub>CC</sub> <sup>2</sup> |

| PIN           | True        | Asserted     | V <sub>CC</sub>              |

| PIN           | False       | Deasserted   | Ground                       |

**Table 1-1** High True / Low True Signal Conventions

- Notes: 1. Ground is an acceptable low voltage level. See the appropriate data sheet for the range of acceptable low voltage levels (typically a TTL logic low).

- 2. V<sub>CC</sub> is an acceptable high voltage level. See the appropriate data sheet for the range of acceptable high voltage levels (typically a TTL logic high).

- The word "reset" is used in three different contexts in this manual. There is a reset pin that is always written as "RESET", a reset instruction that is always written as "RESET", and the word reset that refers to the reset function and is written in lower case with a leading capital letter as grammar dictates. The word "pin" is a generic term for any pin on the chip.

#### DSP56600 Core Description

#### 1.4 DSP56600 CORE DESCRIPTION

The DSP56600 core is based on the DSP56300 core, with a number of power-saving, performance-enhancing, and cost-reducing features implemented. With its seven-stage instruction pipeline, the DSP56600 core is capable of executing an instruction on every clock cycle. A standard interface between the DSP56600 core and the on-chip memory and peripherals supports many memory and peripheral configurations. Complete details of the DSP56600 core are provided in the *DSP56600 Family Manual (DSP56600FM/AD)*.

The following are some of the features of the DSP56600 core:

- 60 Million Instructions Per Second (MIPS) with a 60 MHz clock at 2.7 V

- Fully pipelined 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- 40-bit parallel barrel shifter

- Highly parallel instruction set with unique DSP addressing modes

- Code compatible with the 56300 core

- Position Independent Code (PIC) support

- Nested hardware DO loops

- Fast auto-return interrupts

- On-chip support for software patching and enhancements

- On-chip Phase Lock Loop (PLL)

- Real-time trace capability via External Address Bus

- On-Chip Emulation (OnCE) port

- JTAG port

#### 1.5 DSP56600 CORE FUNCTIONAL BLOCKS

The DSP56600 core provides the following functional blocks:

- Data Arithmetic Logic Unit (Data ALU)

- Address Generation Unit (AGU)

- Program Control Unit (PCU)

- Program Patch Logic

#### **DSP56600 Core Functional Blocks**

- PLL and Clock Oscillator

- Expansion Port (Port A)

- JTAG Test Access Port and On-Chip Emulation (OnCE) module

- Memory

In addition, the DSP56603 provides a set of on-chip peripherals, described in **DSP56603 Architecture Overview** on page 1-13.

#### 1.5.1 Data ALU

The Data ALU performs all the arithmetic and logical operations on data operands in the DSP56600 core. The components of the Data ALU are as follows:

- Four 16-bit input general purpose registers: X1, X0, Y1, and Y0

- A parallel, fully pipelined Multiply-Accumulator unit (MAC)

- Six Data ALU registers (A2, A1, A0, B2, B1, and B0) that are concatenated into two general purpose, 40-bit accumulators, A and B

- An accumulator shifter that is an asynchronous parallel shifter with a 40-bit input and a 40-bit output

- A Bit Field Unit (BFU) with a 40-bit barrel shifter

- Two data bus shifter / limiter circuits

#### 1.5.1.1 Data ALU Registers

The Data ALU registers can be read or written over the X Data Bus (XDB) and the Y Data Bus (YDB) as 16- or 32-bit operands. The source operands for the Data ALU, which can be 16, 32, or 40 bits, always originate from Data ALU registers. The results of all Data ALU operations are stored in an accumulator.

All the Data ALU operations are performed in 2 clock cycles in pipeline fashion so that a new instruction can be initiated in every clock, yielding an effective execution rate of one instruction per clock cycle. The destination of every arithmetic operation can be used as a source operand for the immediate following operation without penalty.

#### 1.5.1.2 Multiply-Accumulator (MAC)

The Multiply-Accumulator (MAC) unit comprises the main arithmetic processing unit of the DSP56600 core and performs all of the calculations on data operands. In the case of arithmetic instructions, the unit accepts as many as three input operands

#### **DSP56600 Core Functional Blocks**

and outputs one 40-bit result of the following form, Extension:Most Significant Product:Least Significant Product (EXT:MSP:LSP).

The multiplier executes 16-bit × 16-bit, parallel, fractional multiplies, between two's-complement signed, unsigned, or mixed operands. The 32-bit product is right-justified and added to the 40-bit contents of either the A or B accumulator. A 40-bit result can be stored as a 16-bit operand. The LSP can either be truncated or rounded into the MSP. Rounding is performed if specified.

#### 1.5.2 Address Generation Unit

The AGU performs the effective address calculations using integer arithmetic necessary to address data operands in memory and contains the registers used to generate the addresses. It implements four types of arithmetic: linear, modulo, multiple wrap-around modulo, and reverse-carry. The AGU operates in parallel with other chip resources to minimize address-generation overhead.

The AGU is divided into two halves, each with its own Address Arithmetic Logic Unit (ALU). Each Address ALU has four sets of register triplets, and each register triplet is composed of an address register, an offset register, and a modifier register. The two Address ALUs are identical. Each contains a 16-bit full adder (called an offset adder).

A second full adder (called a modulo adder) adds the summed result of the first full adder to a modulo value that is stored in its respective modifier register. A third full adder (called a reverse-carry adder) is also provided.

The offset adder and the reverse-carry adder are in parallel and share common inputs. The only difference between them is that the carry propagates in opposite directions. Test logic determines which of the three summed results of the full adders is output.

Each Address ALU can update one address register from its respective address register file during 1 instruction cycle. The contents of the associated modifier register specifies the type of arithmetic to be used in the address register update calculation. The modifier value is decoded in the Address ALU.

#### 1.5.3 **Program Control Unit**

The Program Control Unit (PCU) performs instruction prefetch, instruction decoding, hardware DO loop control, and exception processing. The PCU implements a seven-stage pipeline and controls the different processing states of the DSP56600 core. The PCU consists of three hardware blocks:

- Program Decode Controller (PDC)

- Program Address Generator (PAG)

- Program Interrupt Controller (PIC)

The PDC decodes the 24-bit instruction loaded into the instruction latch and generates all signals necessary for pipeline control. The PAG contains all the hardware needed for program address generation, system stack and loop control. The PIC arbitrates among all interrupt requests (internal interrupts, as well as the five external requests IRQA, IRQB, IRQC, IRQD, and NMI), and generates the appropriate interrupt vector address.

The PCU implements its functions using the following registers:

- PC—Program Counter register

- SR—Status Register

- LA—Loop Address register

- LC—Loop Counter register

- VBA—Vector Base Address register

- SZ—Size register

- SP—Stack Pointer

- OMR—Operating Mode Register

- SC—Stack Counter register

The PCU also includes a hardware System Stack (SS).

#### 1.5.4 **Program Patch Logic**

The Program Patch Logic (PPL) block provides the DSP56600 core user a way to fix the program code in the on-chip ROM without generating a new mask. Implementing the code correction is done by replacing a piece of ROM-based code

#### **DSP56600 Core Functional Blocks**

with a patch program stored in RAM. The PPL consists of four Patch Address Registers (PAR1–PAR4) and four patch address comparators. Each PAR points to a starting location in the ROM code where the program flow is to be changed. The PC register in the PCU is compared to each PAR. When an address of a fetched instruction is identical to an address stored in one of the PARs, the Program Data Bus (PDB) is forced to a corresponding JMP instruction, replacing the instruction that otherwise would have been fetched from the ROM.

#### 1.5.5 PLL and Clock Oscillator

The DSP56600 core features a Phase Lock Loop (PLL) clock oscillator in its central processing module. The PLL allows the processor to operate at a high internal clock frequency using a low frequency clock input, a feature that offers two immediate benefits:

- A lower frequency clock input reduces the overall electromagnetic interference generated by a system.

- The ability to oscillate at different frequencies reduces costs by eliminating the need to add additional oscillators to a system.

The clock generator in the DSP56600 core is composed of two main blocks: the PLL, which performs clock input division, frequency multiplication, and skew elimination; and the Clock Generator (CLKGEN), which performs low power division and clock pulse generation.

#### 1.5.6 Expansion Port (Port A)

Port A is the memory expansion port used for both program and data memory. It provides an easy to use, low part-count connection with fast or slow static memories and with I/O devices. The Port A data bus is 24 bits wide with a separate 16-bit address bus capable of a sustained rate of one memory access per two clock cycles. External memory can be as large as  $64 \text{ K} \times 24$ -bit program memory space, depending on chip configuration. An internal wait state generator can be programmed to insert as many as thirty-one wait states if access to slower memory or I/O device is required. For power-sensitive applications and applications that do not require external memory, Port A can be fully disabled.

#### 1.5.7 JTAG Test Access Port and On-Chip Emulation (OnCE) Module

The DSP56600 core provides a dedicated user-accessible Test Access Port (TAP) that is fully compatible with the *IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture*. Problems associated with testing high density circuit boards have led to development of this standard under the sponsorship of the Test Technology Committee of IEEE and the Joint Test Action Group (JTAG). The DSP56600 core implementation supports circuit-board test strategies based on this standard.

The test logic includes a TAP consisting of four dedicated signal pins, a 16-state controller, and three test data registers. A boundary scan register links all device signal pins into a single shift register. The test logic, implemented utilizing static logic design, is independent of the device system logic. More information on the JTAG port is provided in **Section 11**, **JTAG Port**.

The On-Chip Emulation (OnCE) module provides a means of interacting with the DSP56600 core and its peripherals non-intrusively so that a user can examine registers, memory, or on-chip peripherals. This facilitates hardware and software development on the DSP56600 core processor. OnCE module functions are provided through the JTAG TAP pins. More information on the OnCE module is provided in **Section 10, On-Chip Emulation Module**.

#### 1.5.8 On-Chip Memory

The memory space of the DSP56600 core is partitioned into program memory space, X data memory space, and Y data memory space. The data memory space is divided into X data memory and to Y data memory in order to work with the two Address ALUs and to feed two operands simultaneously to the Data ALU. Memory space includes internal RAM and ROM and can be expanded off-chip under software control. More information on the internal memory is provided in **Section 3**, **Memory Maps**.

#### 1.6 INTERNAL BUSES

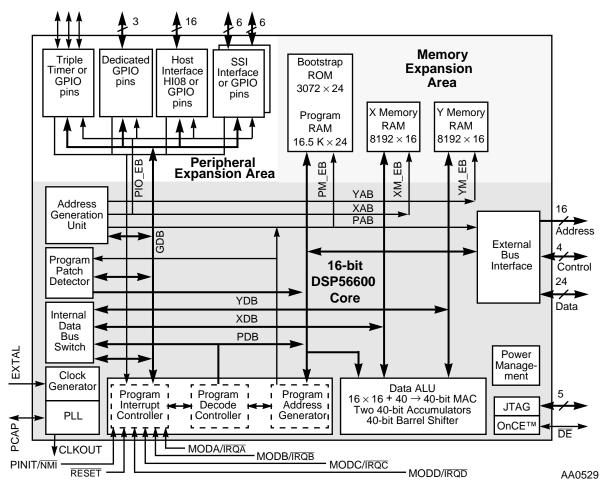

To provide data exchange between these blocks, the following buses are implemented:

• Peripheral I/O Expansion Bus (PIO\_EB) to peripherals

#### Overview

#### **Internal Buses**

- Program Memory Expansion Bus (PM\_EB) to Program ROM

- X Memory Expansion Bus (XM\_EB) to X Memory

- Y Memory Expansion Bus (YM\_EB) to Y Memory

- Global Data Bus (GDB) between Program Control Unit and other core structures

- Program Data Bus (PDB) for carrying program data throughout the core

- X Memory Data Bus (XDB) for carrying X data throughout the core

- Y Memory Data Bus (YDB) for carrying Y data throughout the core

- Program Address Bus (PAB) for carrying program memory addresses throughout the core

- X Memory Address Bus (XAB) for carrying X memory addresses throughout the core

- Y Memory Address Bus (YAB) for carrying Y memory addresses throughout the core

With the exception of the Program Data Bus (PDB), all internal buses on the DSP56600 family members are 16-bit buses. The PDB is a 24-bit bus. **Figure 1-1** provides a block diagram of the DSP56603.

#### **DSP56603** Architecture Overview

Figure 1-1 DSP56603 Block Diagram

### 1.7 DSP56603 ARCHITECTURE OVERVIEW

The DSP56603 is designed to perform a wide variety of fixed-point digital signal processing functions. In addition to the core features previously discussed, the DSP56603 provides the following peripherals:

- Three dedicated General Purpose I/O (GPIO) pins

- As many as thirty-one additional user-configurable GPIO pins

- 8-bit parallel Host Interface (HI08) to external hosts

- Dual Synchronous Serial Interface (SSI)

- Triple timer module

#### **DSP56603** Architecture Overview

- Memory Switch mode

- Four external interrupt/mode control lines

## 1.7.1 GPIO Functionality

The General Purpose I/O (GPIO) port consists of three bidirectional pins, each pin separately controlled. Functionality is controlled by three memory-mapped registers. GPIO functionality is also available on the HI08, SSI, and timer pins when these pins are not otherwise being used by their peripherals. The techniques for register programming for all GPIO functionality is very similar between these interfaces. A maximum of thirty-four GPIO pins can be configured.

## 1.7.2 Host Interface (HI08)

The Host Interface (HI08) is a byte-wide, full-duplex, double-buffered, parallel port that can be connected directly to the data bus of a host processor. The HI08 supports a variety of buses, and provides connection with a number of industry-standard DSPs, microcomputers, and microprocessors without requiring any additional logic.

The DSP core views the HI08 as a memory-mapped peripheral occupying eight 16-bit words in data memory space. The DSP can use the HI08 as a memory-mapped peripheral, using either standard polled or interrupt programming techniques. Separate transmit and receive data registers are double-buffered to allow the DSP and host processor to efficiently transfer data at high speed. Memory mapping allows DSP core communication with the HI08 registers to be accomplished using standard instructions and addressing modes.

## 1.7.3 Synchronous Serial Interface (SSI)

The DSP56603 provides two independent and identical Synchronous Serial Interfaces (SSI). Each SSI provides a full-duplex serial port for communication with a variety of serial devices, including one or more industry-standard codecs, other DSPs, microprocessors, and peripherals that implement the Motorola SPI. The SSI consists of independent transmitter and receiver sections and a common SSI clock generator.

The capabilities of the SSI include:

- Independent (asynchronous) or shared (synchronous) transmit and receive sections with separate or shared internal/external clocks and frame syncs

- Normal mode operation using frame sync

- Network mode operation with as many as 32 time slots

- Programmable word length (8, 12, or 16 bits)

- Program options for frame synchronization and clock generation

### 1.7.4 Triple Timer

The triple timer module is composed of a common 14-bit prescaler and three independent and identical general purpose 16-bit timer/event counters, each one having its own memory-mapped register set.

Each timer can use internal or external clocking and can interrupt the DSP after a specified number of events (clocks) or can signal an external device after counting internal events. Each timer connects to the external world through one bidirectional pin. When this pin is configured as an input, the timer can function as an external event counter or measures external pulse width/signal period. When the pin is used as an output, the timer can function as either a timer, a watchdog, or a Pulse Width Modulator (PWM).

<del>dsp</del>

DSP56603 Architecture Overview

# SECTION 2 SIGNAL/CONNECTION DESCRIPTION

| 2.1  | INTRODUCTION                               |

|------|--------------------------------------------|

| 2.2  | POWER                                      |

| 2.3  | GROUND                                     |

| 2.4  | CLOCK AND PHASE LOCK LOOP                  |

| 2.5  | INTERRUPT AND MODE CONTROL                 |

| 2.6  | EXPANSION PORT (PORT A) 2-11               |

| 2.7  | HOST INTERFACE (HI08) 2-12                 |

| 2.8  | SYNCHRONOUS SERIAL INTERFACE 0 (SSI0) 2-18 |

| 2.9  | SYNCHRONOUS SERIAL INTERFACE 1 (SSI1) 2-21 |

| 2.10 | GENERAL PURPOSE I/O, GPIO 2-24             |

| 2.11 | TRIPLE TIMER 2-25                          |

| 2.12 | JTAG/ONCE INTERFACE 2-26                   |

|      |                                            |

# 2.1 INTRODUCTION

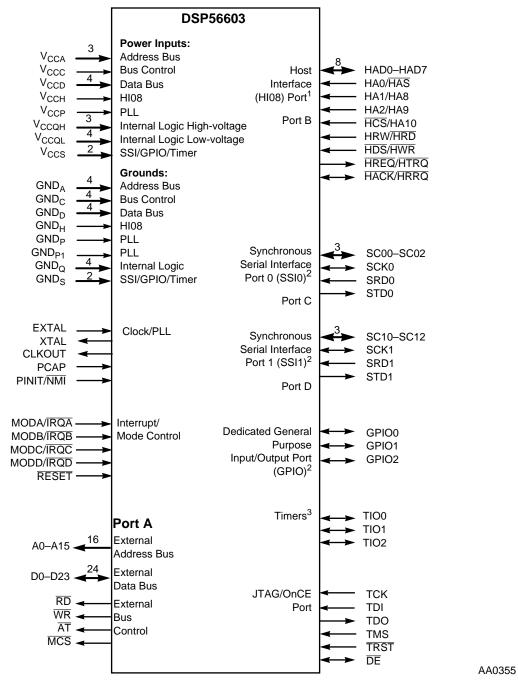

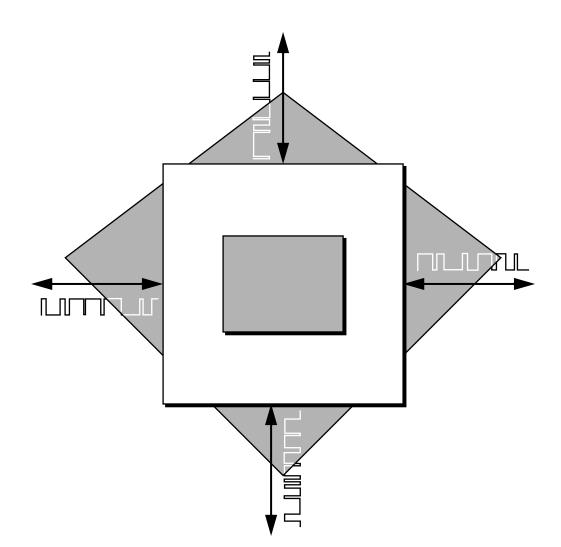

The input and output signals of the DSP56603 are organized into functional groups, as shown in **Table 2-1** and as illustrated in **Figure 2-1**. In **Table 2-2** through **Table 2-13**, each table row describes the signal or signals present on a pin.

The DSP56603 operates from a 3 V supply; however, some of the inputs can tolerate 5 V. A special notice for this feature is added to the signal descriptions of those inputs.

| Functional Group                      | Number of<br>Signals | Detailed<br>Description |            |

|---------------------------------------|----------------------|-------------------------|------------|

| Power (V <sub>CC</sub> )              |                      | 19                      | Table 2-2  |

| Ground (GND)                          |                      | 19                      | Table 2-3  |

| PLL and Clock Signals                 |                      | 5                       | Table 2-4  |

| Interrupt and Mode Control            |                      | 5                       | Table 2-5  |

| External Memory Port                  | Address Bus          | 16                      | Table 2-6  |

| (also referred to as Port A)          | Data Bus             | 24                      |            |

|                                       | Bus Control          | 4                       |            |

| Host Interface (HI08)                 | Port B (GPIO)        | 16                      | Table 2-8  |

| Synchronous Serial Interface 0 (SSI0) | Port C (GPIO)        | 6                       | Table 2-9  |

| Synchronous Serial Interface 1 (SSI1) | 6                    | Table 2-10              |            |

| General Purpose Input/Output (GPI     | 3                    | Table 2-11              |            |

| Triple Timer                          | 3                    | Table 2-12              |            |

| JTAG/On-Chip Emulation (OnCE) Po      | ort                  | 6                       | Table 2-13 |

**Table 2-1** Functional Group Signal Allocations

#### Introduction

- Note: 1. The HI08 port supports a non-multiplexed or a multiplexed bus, single or double Data Strobe (DS), and single or double Host Request (HR) configurations. Since each these modes is configured independently, any combination of these modes is possible. The HI08 signals can also be configured alternately as GPIO signals (PB0–PB15).

- 2. The SSI0 and SSI1 signals can be configured alternatively as Port C GPIO signals (PC0–PC5) and Port D GPIO signals (PD0–PD5), respectively.

- 3. TIO0–TIO2 can be configured alternatively as GPIO signals.

Figure 2-1 DSP56603 Signals Identified by Functional Group

# 2.2 POWER

| Signal Name<br>(number of pins) | Signal Description                                                                                                                                                                                                                                                                           |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCA</sub> (3)            | <b>Address Bus Power</b> — $V_{CCA}$ is an isolated power for sections of address bus I/O drivers, and must be tied externally to all other chip power inputs, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors.                               |

| V <sub>CCC</sub> (1)            | <b>Bus Control Power</b> — $V_{CCC}$ is an isolated power for the bus control I/O drivers, and must be tied to all other chip power inputs externally, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors.                                       |

| V <sub>CCD</sub> (4)            | <b>Data Bus Power</b> — $V_{CCD}$ is an isolated power for sections of data bus I/O drivers, and must be tied to all other chip power inputs externally, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors.                                     |

| V <sub>CCH</sub> (1)            | <b>Host Power</b> — $V_{CCH}$ is an isolated power for the HI08 logic, and must be tied to all other chip power inputs externally, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors.                                                           |

| V <sub>CCP</sub> (1)            | <b>PLL Power</b> — $V_{CCP}$ is $V_{CC}$ dedicated for Phase Lock Loop (PLL) use. The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the $V_{CC}$ power rail.                                                                     |

| V <sub>CCQH</sub> (3)           | <b>Quiet Power High Voltage</b> — $V_{CCQH}$ is an isolated power for the CPU logic, and must be tied to all other chip power inputs externally, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors.                                             |

|                                 | The voltage supplied to these inputs should equal the voltage supplied to I/O power inputs $V_{CCA}$ , $V_{CCC}$ , $V_{CCD}$ , $V_{CCH}$ , and $V_{CCS}$ .                                                                                                                                   |

| V <sub>CCQL</sub> (4)           | <b>Quiet Power Low Voltage</b> —V <sub>CCQL</sub> is an isolated power for the CPU logic, and should not be tied to the other chip power inputs. The user must provide adequate external decoupling capacitors.                                                                              |

|                                 | The voltage supplied to these inputs should be equal to or lower than the voltage supplied to the $V_{CCQH}$ inputs. The user can lower the voltage supplied to $V_{CCQL}$ as long as it meets the MIPS requirements of the application, thus lowering the chip's overall power consumption. |

## Table 2-2Power Inputs

### Ground

| Signal Name<br>(number of pins) | Signal Description                                                                                                                                                                                                                                                   |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V <sub>CCS</sub> (2)            | <b>SSI, GPIO, and Timers Power</b> — $V_{CCS}$ is a isolated power for the SSIs, GPIO, and Timers logic, and must be tied to all other chip power inputs externally, except for the $V_{CCQL}$ input. The user must provide adequate external decoupling capacitors. |  |

# Table 2-2 Power Inputs (Continued)

# 2.3 GROUND

| Signal Name<br>(number of pins) | Signal Description                                                                                                                                                                                                                                                          |  |