# MOTOROLA SEMICONDUCTOR TECHNICAL DATA 24-Bit General Purpose Digital Signal Processor

The DSP56001 is a member of Motorola's family of HCMOS, low-power, general purpose Digital Signal Processors. The DSP56001 features 512 words of full speed, on-chip program RAM (PRAM) memory, two 256 word data RAMs, two preprogrammed data ROMs, and special on-chip bootstrap hardware to permit convenient loading of user programs into the program RAM. It is an off-the-shelf part since the program

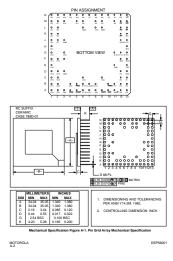

# Pin Grid Array (PGA)

Available in an 88 pin ceramic through-hole package.

**DSP56001**

## **Ceramic Quad Flat Pack (CQFP)** Available in a 132 pin, small footprint,

surface mount package.

# Plastic Quad Flat Pack (PQFP)

Available in a 132 pin, small footprint, surface mount package.

memory is user programmable. The core of the processor consists of three execution units operating in parallel — the data ALU, the address generation unit, and the program controller. The DSP56001 has MCU-style on-chip peripherals, program and data memory, as well as a memory expansion port. The MPU-style programming model and instruction set make writing efficient, compact code, straightforward.

The high throughput of the DSP56001 makes it well-suited for communication, high-speed control, numeric processing, computer and audio applications. The key features which facilitate this throughput are:

| Speed                                 | At 16.5 million instructions per second (MIPS) with a 33 MHz clock, the DSP56001 can execute a 1024 point complex Fast Fourier Transform in1.98 milliseconds (66,240 clock cycles).                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Precision                             | The data paths are 24 bits wide thereby providing 144 dB of dynamic range; intermediate results held in the 56-bit accumulators can range over 336 dB.                                                                                                                                                                                                                                                                                                                                                                                                     |

| Parallelism                           | The data ALU, address arithmetic units, and program controller operate in parallel so that an in-<br>struction prefetch, a 24x24-bit multiplication, a 56-bit addition, two data moves, and two address<br>pointer updates using one of three types of arithmetic (linear, modulo, or reverse carry) can be<br>executed in a single instruction cycle. This parallelism allows a four coefficient Infinite Impulse Re-<br>sponse (IIR) filter section to be executed in only four cycles, the theoretical minimum for a single<br>multiplier architecture. |

| Integration                           | In addition to the three independent execution units, the DSP56001 has six on-chip memories, three on-chip MCU style peripherals (Serial Communication Interface, Synchronous Serial Interface, and Host Interface), a clock generator and seven buses (three address and four data), making the overall system functionally complete and powerful, but also very low cost, low power, and compact.                                                                                                                                                        |

| Invisible Pipeline                    | The three-stage instruction pipeline is essentially invisible to the programmer thus allowing straightforward program development in either assembly language or a high-level language such as ANSI C.                                                                                                                                                                                                                                                                                                                                                     |

| Instruction Set                       | The 62 instruction mnemonics are MCU-like making the transition from programming micropro-<br>cessors to programming the DSP56001 digital signal processor as easy as possible. The orthog-<br>onal syntax supports control of the parallel execution units. This syntax provides 12,808,830 dif-<br>ferent instruction variations using the 62 instruction mnemonics. The no-overhead DO instruction<br>and the REPEAT (REP) instruction make writing straight-line code obsolete.                                                                        |

| DSP56000/DSP56001<br>Compatibility    | The DSP56001 is identical to the DSP56000 except that it has 512x24-bits of on-chip program RAM instead of 3.75K of program ROM; a 32x24-bit bootstrap ROM for loading the program RAM from either a byte-wide memory mapped ROM or via the Host Interface; and the on-chip X and Y Data ROMs have been preprogrammed as positive Mu- and A-Law to linear expansion tables and a full, four quadrant sine wave table, respectively.                                                                                                                        |

| Low Power                             | <ul> <li>As a CMOS part, the DSP56001 is inherently very low power; however, three other features can reduce power consumption to an exceptionally low level.</li> <li>The WAIT instruction shuts off the clock in the central processor portion of the DSP56001.</li> <li>The STOP instruction halts the internal oscillator.</li> <li>Power increases linearly (approximately) with frequency; thus, reducing the clock frequency reduces power consumption.</li> </ul>                                                                                  |

| This document contains information or | a new product. Specifications and information herein are subject to change without notice.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

September 19, 1996

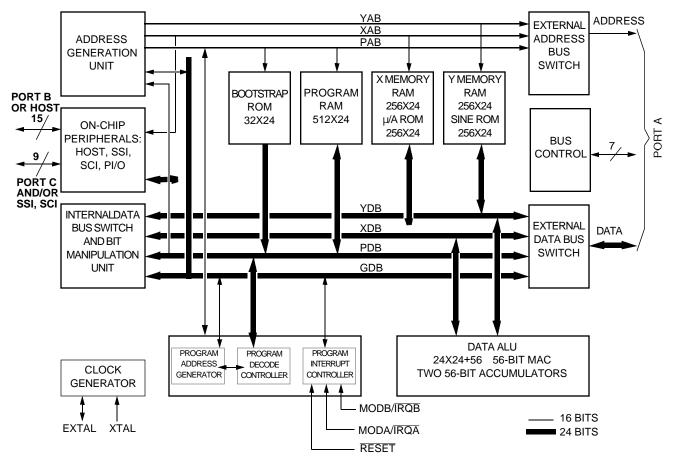

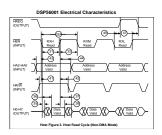

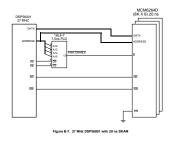

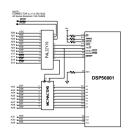

Figure 1. DSP56001 Block Diagram

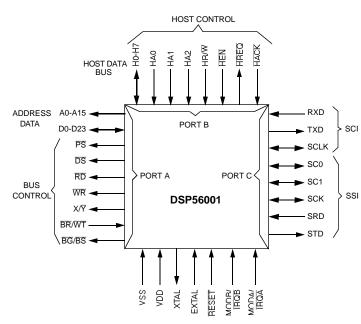

# SIGNAL DESCRIPTION

The DSP56001 is available in 132 pin surface mount (CQFP and PQFP) or an 88-pin pin-grid array packaging. Its input and output signals are organized into seven functional groups which are listed below and shown in Figure 1.

Port A Address and Data Buses Port A Bus Control Interrupt and Mode Control Power and Clock Host Interface or Port B I/O Serial Communications Interface or Port C I/O Synchronous Serial Interface or Port C I/O

# PORT A ADDRESS AND DATA BUS

### Address Bus (A0-A15)

These three-state output pins specify the address for external program and data memory accesses. To minimize power dissipation, A0-A15 do not change state when external memory spaces are not being accessed.

### Data Bus (D0-D23)

These pins provide the bidirectional data bus for external program and data memory accesses. D0-D23 are in the high-impedance state when the bus grant signal is asserted.

# PORT A BUS CONTROL

### Program Memory Select (PS)

This three-state output is asserted only when external program memory is referenced. This pin is three-stated during RESET.

### Data Memory Select (DS)

This three-state output is asserted only when external data memory is referenced. This pin is three-stated during RESET.

### X/Y Select (X/Y)

This three-state output selects which external data memory space (X or Y) is referenced by data memory select ( $\overline{\text{DS}}$ ). This pin is three-stated during  $\overline{\text{RESET}}$ .

### Read Enable (RD)

This three-state output is asserted to read external memory on the data bus D0-D23. This pin is three-stated during RESET.

### Write Enable (WR)

This three-state output is asserted to write external memory on the data bus D0-D23. This pin is three-stated during  $\overline{\mathsf{RESET}}$ .

### Bus Request (BR/WT)

The bus request input BR allows another device such as a processor or DMA controller to become the master of external data bus D0-D23 and external address bus A0-A15. When operating mode register (OMR) bit 7 is clear and BR is asserted, the DSP56001 will always release the external data bus D0-D23, address bus A0-A15, and bus control pins PS, DS, X/Y, RD, and WR (i. e., Port A), by placing these pins in the high-impedance state after execution of the current instruction has been completed. The BR pin should be pulled up when not in use.

If OMR bit 7 is set, this pin is an input that allows an external device to force wait states during an external Port A operation for as long as  $\overline{\text{WT}}$  is asserted.

### Bus Grant (BG/BS)

If OMR bit 7 is clear, this output is asserted to acknowledge an external bus request after Port A has been released. If OMR bit 7 is set, this pin is bus strobe and is asserted when the DSP accesses Port A. This pin is three-stated during RESET.

# INTERRUPT AND MODE CONTROL

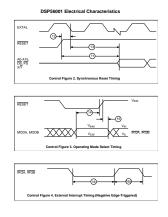

## Mode Select A/External Interrupt Request A (MODA/IRQA), Mode Select B/External Interrupt Request B (MODB/IRQB)

These two inputs have dual functions: 1) to select the initial chip operating mode and 2) to receive an interrupt request from an external source. MODA and MODB are read and internally latched in the DSP when the processor exits the RESET state. Therefore these two pins should be forced into the proper state during reset. After leaving the RESET state, the MODA and MODB pins automatically change to external interrupt requests IRQA and IRQB. After leaving the reset state the chip operating mode can be changed by software. IRQA and IRQB may be programmed to be level sensitive or negative edge triggered. When edge triggered, triggering occurs at a voltage level and is not directly related to the fall time of the interrupt signal, however, the probability of noise on IRQA or IRQB generating multiple interrupts increases with increasing fall time of the interrupt signal. These pins are inputs during RESET.

### Reset (RESET)

This Schmitt trigger input pin is used to reset the DSP56001. When RESET is asserted, the DSP56001 is initialized and placed in the reset state. When the RESET signal is deasserted, the initial chip operating mode is latched from the MODA and MODB pins. When coming out of reset, deassertion occurs at a voltage level and is not directly related to the rise time of the reset signal; however, the probability of noise on RESET generating multiple resets increases with increasing rise time of the reset signal.

## **POWER AND CLOCK**

### Power (Vcc), Ground (GND)

There are five sets of power and ground pins used for the four groups of logic on the chip, two pairs for internal logic, one power and two ground for Port A address and control pins, one power and two ground for Port A data pins, and one pair for peripherals. Refer to the pin assignments in the **LAYOUT PRACTICES** section.

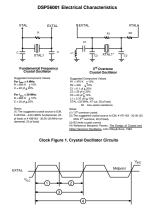

### External Clock/Crystal Input (EXTAL)

EXTAL may be used to interface the crystal oscillator input to an external crystal or an external clock.

# Crystal Output (XTAL)

This output connects the internal crystal oscillator output to an external crystal. If an external clock is used, XTAL should not be connected.

# HOST INTERFACE

# Host Data Bus (H0-H7)

This bidirectional data bus is used to transfer data between the host processor and the DSP56001. This bus is an input unless enabled by a host processor read. H0-H7 may be programmed as general purpose parallel I/O pins called PB0-PB7 when the Host Interface is not being used. These pins are configured as a GPIO input pins during hardware reset.

## Host Address (HA0-HA2)

These inputs provide the address selection for each Host Interface register. HA0-HA2 may be programmed as general purpose parallel I/O pins called PB8-PB10 when the Host Interface is not being used. These pins are configured as a GPIO input pins during hardware reset.

# Host Read/Write (HR/W)

This input selects the direction of data transfer for each host processor access. HR/ $\overline{W}$  may be programmed as a general purpose I/O pin called PB11 when the Host Interface is not being used. This pin is configured as a GPIO input pins during hardware reset.

### Host Enable (HEN)

This input enables a data transfer on the host data bus. When HEN is asserted and HR/ $\overline{W}$  is high, H0-H7 become outputs, and DSP56001 data may be read by the host processor, When HEN is asserted and HR/ $\overline{W}$  is low, H0-H7 become inputs and host data is latched inside the DSP when HEN is deasserted. Normally a chip select signal, derived from host address decoding and an enable clock, is used to generate HEN. HEN may be programmed as a general purpose I/O pin called PB12 when the Host Interface is not being used. This pin is configured as a GPIO input pins during hardware reset.

### Host Request (HREQ)

This open-drain output signal is used by the DSP56001 Host Interface to request service from the host processor, DMA controller, or simple external controller. HREQ may be programmed as a general purpose I/O pin (not open-drain) called PB13 when the Host interface is not being used. HREQ should be pulled high when not in use. This pin is configured as a GPIO input pins during hardware reset.

### Host Acknowledge (HACK)

This input has two functions: 1) to receive a Host Acknowledge handshake signal for DMA transfers and, 2) to receive a Host Interrupt Acknowledge compatible with MC68000 Family processors. HACK may be programmed as a general purpose I/O pin called PB14 when the Host Interface is not being used. This pin is configured as a GPIO input pins during hardware reset. **HACK should be pulled high when not in use.**

# SERIAL COMMUNICATIONS INTERFACE (SCI)

### Receive Data (RXD)

This input receives byte-oriented data into the SCI Receive Shift Register. Input data is sampled on the positive edge of the Receive Clock. RXD may be programmed as a general purpose I/O pin called PC0 when the SCI is not being used. This pin is configured as a GPIO input pins during hardware reset.

### Transmit Data (TXD)

This output transmits serial data from the SCI Transmit Shift Register. Data changes on the negative edge of the transmit clock. This output is stable on the positive edge of the transmit clock. TXD may be programmed as a general purpose I/O pin called PC1 when the SCI is not being used. This pin is configured as a GPIO input pins during hardware reset.

### SCI Serial Clock (SCLK)

This bidirectional pin provides an input or output clock from which the transmit and/or receive baud rate is derived in the asynchronous mode and from which data is transferred in the synchronous mode. SCLK may be programmed as a general purpose I/O pin called PC2 when the SCI is not being used. This pin is configured as a GPIO input pins during hardware reset.

## SYNCHRONOUS SERIAL INTERFACE (SSI)

### Serial Control Zero (SC0)

This bidirectional pin is used for control by the SSI. SC0 may be programmed as a general purpose I/O pin called PC3 when the SSI is not being used. This pin is configured as a GPIO input pins during hardware reset.

### Serial Control One (SC1)

This bidirectional pin is used for control by the SSI. SC1 may be programmed as a general purpose I/O pin called PC4 when the SSI is not being used. This pin is configured as a GPIO input pins during hardware reset.

### Serial Control Two (SC2)

This bidirectional pin is used for control by the SSI. SC2 may be programmed as a general purpose I/O pin called PC5 when the SSI is not being used. This pin is configured as a GPIO input pins during hardware reset.

### SSI Serial Clock (SCK)

This bidirectional pin provides the serial bit rate clock for the SSI when only one clock is used. SCK may be programmed as a general purpose I/O pin called PC6 when the SSI is not being used. This pin is configured as a GPIO input pins during hardware reset.

### SSI Receive Data (SRD)

This input pin receives serial data into the SSI Receive Shift Register. SRD may be programmed as a general purpose I/O pin called PC7 when the SSI is not being used. This pin is configured as a GPIO input pins during hardware reset.

### SSI Transmit Data (STD)

This output pin transmits serial data from the SSI Transmit Shift Register. STD may be programmed as a general purpose I/O pin called PC8 when the SSI is not being used. This pin is configured as a GPIO input pins during hardware reset.

# <text><text><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header>

This device contains circuity protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-reladi voltages to this high-impedance circuit. Reliability of operation is enhanced i suused inputs are lised to an appropriate logic voltage level (e.g., either Ged or Voc).

DSP56001

<section-header><section-header><section-header><section-header><section-header><text><text><text><text><text><text><text><text><text><text>

| Vcc            | GND                       | Function                                 |  |

|----------------|---------------------------|------------------------------------------|--|

| G12,C6         | G11,07                    | Internal Logic supply pins               |  |

| 1.0            | 16,1.9                    | Address bus output buffer supply pins    |  |

| G3             | 03,13                     | Data bus output buffer supply pins       |  |

| C9             | E11                       | Port B and C output buffer supply pins   |  |

|                |                           |                                          |  |

|                | Power and                 | d Ground Connections for PGA             |  |

| Vec            | Power and<br>GND          | d Ground Connections for PGA<br>Function |  |

|                |                           |                                          |  |

|                | GND                       | Function                                 |  |

| 35, 36, 128, 1 | GND<br>2983, 34, 130, 131 | Function<br>Internal Logic supply pins   |  |

DSP56001

<section-header><section-header><section-header><section-header><section-header><text>

DSP56001 MOTOROLA 7

| Characteristic                                                                                                                  | Symbol                        | Min       | Тур                            | Max                             | Uni                  |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------|--------------------------------|---------------------------------|----------------------|

| Supply Voltage 20, 27 MHz<br>33 MHz                                                                                             | Vec                           | 45<br>475 | 50                             | 5.5<br>5.25                     | v                    |

| Input High Voltage<br>Except EXTAL, RESET, MODA/ROR, MODE/ROB                                                                   | VH                            | 2.0       | -                              | Vec                             | v                    |

| Input Low Voltage<br>Except EXTAL, MODATROP, MODE/PROB                                                                          | V <sub>L</sub>                | -0.5      | -                              | 0.8                             | v                    |

| Input High Voltage EXTAL                                                                                                        | V <sub>HC</sub>               | 4.0       | -                              | Vec                             | v                    |

| Input Low Voltage EXTAL                                                                                                         | Vac                           | -0.5      | -                              | 0.6                             | v                    |

| Input High Voltage RESET                                                                                                        | Vee                           | 2.5       | -                              | Vec                             | v                    |

| Input High Voltage MODA/IRCR and MODB/IRCR                                                                                      | Vent                          | 3.5       | -                              | Vec                             | v                    |

| Input Low Voltage MODA/INDRAIN MODE/INDE                                                                                        | Vam                           | -0.5      | -                              | 2.0                             | v                    |

| Input Leakage Current<br>EXTAL, RESET, MODA/ROX, MODB/ROB, BR                                                                   | 5                             | -1        | -                              | 1                               | ωA                   |

| Three-State (Off-State) Input Current<br>(8/2.4 V/0.4 V)                                                                        | ina .                         | -10       | -                              | 10                              | ωA                   |

| Output High Voltage (I <sub>OH</sub> = -0.4 mA)                                                                                 | V <sub>DH</sub>               | 2.4       | -                              | -                               | v                    |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                            | V <sub>DL</sub>               | -         | -                              | 0.4                             | v                    |

| Total Supply Current 5.25 V, 33 MHz<br>5.5 V, 27 MHz<br>5.5 V, 20 MHz<br>in WAIT Mode (see Note 1)<br>in STOP Mode (see Note 1) | leess<br>lees<br>lees<br>lees | -         | 160<br>130<br>100<br>10<br>100 | 185<br>155<br>115<br>25<br>2000 | mA<br>mA<br>mA<br>Au |

|                                                                                                                                 |                               |           |                                |                                 |                      |

Notes: 1. Is order to obtain these results all inputs must be terminated (i.e., not allowed to float). 2. Periodically sampled and not 100% tested.

DSP56001 Electrical Characteristics A Cenceristical Characteristics The provide the second Vog-memorie area and u a V and u a V menodowy. AC Electrical Characteristics - Clock Operation the D552001 speed code on the en-chop cypal excitator as shown in Clock Figure 1, or 1 may be estemally supplied. An estimally applied against wine visible access tool bit commended to DTML being TML phycolary contracted and clock Figure 1 in the address radius. The shown wine visible access the address the the manament.

DSP56001 MOTOROLA 9

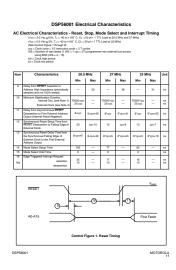

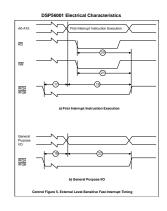

### DSP56001 Electrical Characteristics AC Electrical Characteristics - Reset, Stop, Mode Select, and Interrupt Timing (continue) **DET** When any terminal characteristics - Reset and the selectric of the selectric of the selectric of the selectric selectric of the s

| Num | Characteristics                                                                                                                                                 | 20.5                   | MHz                                      | 27 1                   | MHz                                      | 33                     | MHz                                      | Unit     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------|------------------------|------------------------------------------|------------------------|------------------------------------------|----------|

|     |                                                                                                                                                                 | Min                    | Max                                      | Min                    | Max                                      | Min                    | Max                                      |          |

| 17  | Delay from IRCIA, IRCIE Assertion to<br>External Memory Access Address Out<br>Valid Caused by Fint Interrupt<br>Instruction Facth<br>Instruction Execution      | 5-cyc+ich<br>9-cyc+ich | -                                        | 5-cyc+lch<br>9-cyc+lch | -                                        | 5-cyc+lch<br>9-cyc+lch | -                                        | ns<br>ns |

| 10  | Delay from IRCA, IRCEI Assertion to<br>General Purpose Transfer Output Valid<br>Caused by First Interrupt Instruction<br>Execution                              | 11+cyc<br>+ich         | -                                        | 11-cyc<br>+tch         | -                                        | 11-cyc<br>+tch         | -                                        | ns       |

| 19  | Delay hom Address Output Valid<br>Caused by First Interrupt Instruction<br>Execution to Interrupt Request<br>Deassertion for Level Sensitive Fast<br>Interrupts | -                      | 2-cyc+td+<br>(cyc-W5)<br>-44             | -                      | 2-cyc+td+<br>(cyc-W5)<br>-34             | -                      | 2-cyc+td+<br>(cyc-W5)<br>-27             | ns       |

| 20  | Delay from RD Assertion to Interrupt<br>Request Deassertion for Level<br>Sensitive Fast Interrupts                                                              | -                      | 2×cyc+<br>(cyc>WS)<br>-40                | -                      | 2×cjic+<br>(cjic>WS)<br>-31              | -                      | 2×cjic+<br>(cjic>WS)<br>-25              | ns       |

| 21  | Delay from WR Assertion to WS+0<br>Interrupt Request Deassertion for<br>WS>0 Level Sensitive Fast Interrupts                                                    | =                      | 2+cyc-40<br>cjic+td+<br>(cjic-W5)<br>-40 | =                      | 2-cyc-31<br>cjic+td+<br>(cjic-WS)<br>-31 | =                      | 2-cyc-25<br>cjic+td+<br>(cjic-W5)<br>-25 | ns<br>ns |

| 22  | Delay hom General-Purpose Output<br>Valid to Interrupt Request Dessertion<br>for Level Senable Fast Internation In:<br>Single Cycle<br>Two Cycle                | =                      | 101-60<br>(2-ctyst)+tcl<br>-60           | =                      | 101-46<br>(2-ct)(2)+1cl<br>-46           | =                      | 121-37<br>(2-cyc)+tcl<br>-37             |          |

MOTOROLA 12 DS

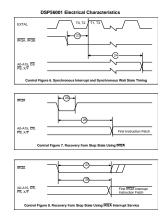

# DSP56001 Electrical Characteristics AC Electrical Characteristics - Reset, Stop, Mode Select, and Interrupt Timing (Continued)

MOTOROLA 16

DSP56001

DSP55001 Electrical Characterization HOST PORT USAGE CONSIDERATIONS Order proferrational services and the service and the first port the service devices the proper portion and accumate inter-

- A set of the set of th

- (1.24), man the instal at guaranteed to be instal. A potential problem exists when reading status bits MP3 and MP2 as an encoded part. If the CSP changes MP3 and MP2 from 00 to 11, free it is an analyzability that the fullow could read the bits during the transition and receive 01 or 10 instead of 11. If the combination of MP3 and MP2 has significance, the Host could read the wrong combination.

- combinence of the area we are a second secon

- Constaining the Heat Vactor

Constaining the Heat Vactor

The Vactor powerser should change the Heat Vactor register only when the Vactor

Constant bit (HC) is clear. This change will

guarantee that BCEP Interrupt control logic will receive a stable vector.

- c concept and the difference to many end of the second set of t

DSP56001

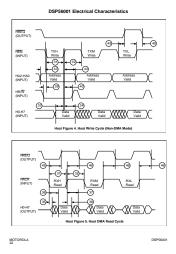

|            | DSP56001 Electrical Characteristics                                                          |

|------------|----------------------------------------------------------------------------------------------|

|            | AC Electrical Characteristics - Host VO Timing                                               |

| (Vcc = 5.) | 0 Vdc ± 10%, T <sub>J</sub> = -40 to +105° C, CL = 50 pl + 1 TTL Load at 20.5 MHz and 27 MHz |

|            | 3 Vdc ± 5%, T <sub>J</sub> = -40 to +105° C, CL = 50 pf + 1 TTL Load at 33 MHz)              |

|            | (Figures 1 through 6)                                                                        |

| cyc = Clo  | ck cycle = 1/2 instruction cycle = 2 T cycles                                                |

|            | Host Synchronization Delay Time                                                              |

| Active low | v lines should be "pulled up" in a manner consistent with the AC and DC specification        |

| Num | Characteristics                                                                                         | 20.5               | MHz    | 27 1               | //Hz   | 331                | //Hz   | Ur |

|-----|---------------------------------------------------------------------------------------------------------|--------------------|--------|--------------------|--------|--------------------|--------|----|

|     |                                                                                                         | Min                | Max    | Min                | Max    | Min                | Max    |    |

| 30  | Host Synchronous Delay (see Note 1)                                                                     | 10                 | cyc+td | 1d                 | cyc+td | 1d                 | cyc+td |    |

| 31  | RENTRACK Assertion Width<br>(see Note 2)<br>a.CVR, ICR, ISR Read (see Note 4)<br>b.Read<br>c.Write      | 070+60<br>50<br>25 | Ξ      | 070+46<br>29<br>19 | Ξ      | 0)0+37<br>31<br>16 | Ξ      |    |

| 32  | INTRACK Deassertion Width<br>(see Note 2 and 5)                                                         | 25                 | -      | 19                 | -      | 16                 | -      | ľ  |

| 223 | Minimum Cycle Time Between Two<br>REN Assertion for Consecutive CVR,<br>ICR, and ISR Reads (see Note 2) | 2°cyc+60           | -      | 2°cyc+46           | -      | 2ºcyc+37           | -      | 1  |

|     | Host Data Input Setup Time Before<br>RENTRACK Deassertion                                               | 5                  | -      | 4                  | -      | 4                  | -      | Г  |

| 34  | Host Data Input Hold Time After PERV<br>PACK Descention                                                 | 5                  | -      | 4                  | -      | 4                  | -      | ľ  |

| 35  | RENTRACK Assertion to Output Data<br>Active from High Impedance                                         | 0                  | -      | 0                  | -      | 0                  | -      | ľ  |

| 36  | Valid (periodically sampled, and not<br>100% tested)                                                    | -                  | 50     | -                  | 39     | -                  | 31     | ľ  |

| 37  | NEN RACK Deassertion to Output<br>Data High Impedance                                                   | -                  | 25     | -                  | 27     | -                  | 22     | Г  |

| 38  | Output Data Hold Time After FER/<br>FROM Deasention                                                     | 5                  | -      | 4                  | -      | 4                  | -      | ľ  |

| 29  | HR/W Low Setup Time Before REN<br>Assertion                                                             | 0                  | -      | 0                  | -      | 0                  | -      | T  |

| 40  | HR/W Low Hold Time After FIEN<br>Deassertion                                                            | 5                  | -      | 4                  | -      | 4                  | -      | ľ  |

| 41  | HR/W High Setup Time to FIEN<br>Assertion                                                               | 0                  | -      | 0                  | -      | 0                  | -      | ľ  |

|     | HR/W High Hold Time After FIERV<br>FACK Deassertion                                                     | 5                  | -      | 4                  | -      | 4                  | -      | ħ  |

| 43  | HAO-HA2 Setup Time Before PEN<br>Assertion                                                              | 0                  | -      | 0                  | -      | 0                  | -      | ľ  |

| 44  | NAO-HA2 Hold Time After FIEN<br>Deassertion                                                             | 5                  | -      | 4                  | -      | 4                  | -      | ľ  |

| 45  | DMA TRACK Assertion to FIRED<br>Deassertion (see Note 3)                                                | 5                  | 60     | 4                  | 46     | 4                  | 49     | ħ  |

MOTOROLA 18 DSP560

|                                    | DSP56001 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HREQ<br>(OUTPUT)                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| HACK<br>(INPUT)<br>HR/W<br>(INPUT) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| H0-H7<br>(OUTPUT)                  | Control Contro |

DSP56001 Electrical Characteristics

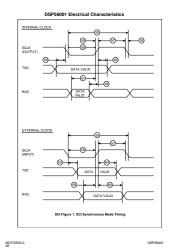

AC Betrical Characteristics - SCI Time

(1) - SCI - SC

| Num | Characteristics                                                     | 20.5              | MHz             | 271              | //Hz            | 33              | MHz             | Unit |

|-----|---------------------------------------------------------------------|-------------------|-----------------|------------------|-----------------|-----------------|-----------------|------|

|     |                                                                     | Min               | Max             | Min              | Max             | Min             | Max             |      |

| 55  | Synchronous Clock Cycle tSCC                                        | 8-cyc             | -               | 8-cyc            | -               | 8-cyc           | -               | ns   |

| 56  | Clock Low Period                                                    | 4+cyc-20          | -               | 4-cyc-15         | -               | 4-cyc-13        | -               | ns   |

| 57  | Clock High Period                                                   | 4-cyc-20          | -               | 4-cyc-15         | -               | 4+cyc-13        | -               | 15   |

| 50  | Output Data Setup to Clock Failing<br>Edge (Internal Clock)         | 2+cyc<br>+td-50   | -               | 2-cyc<br>+td-39  | -               | 2.cyc<br>+td-31 | -               | ns   |

| 60  | Output Data Hold After Clock Rising<br>Edge (Internal Clock)        | 2.cyc<br>-td-15   | -               | 2.cyc<br>-tzl-11 | -               | 2.cyc<br>-td-9  | -               | - 15 |

| 61  | Input Data Setup Time Before Clock<br>Rising Edge (Internal Clock)  | 2+cyc<br>+1::1+45 | -               | 2+cyc<br>+tcl+35 | -               | 2+cyc<br>+td+28 | -               | - 15 |

| 62  | Input Data Not Valid Before Clock Ris-<br>ing Edge (Internal Clock) | -                 | 2-cyc<br>+td-10 | -                | 2.cyc<br>+tcl-8 | -               | 2.cyc<br>+tcl-6 | -15  |

| 63  | Clock Falling Edge to Output Data<br>Valid (External Clock)         | -                 | 63              | -                | 40              | -               | 29              | ^5   |

| ы   | Output Data Hold After Clock Rising<br>Edge (External Clock)        | cyc+12            | -               | cyc+9            | -               | cyc+8           | -               | ns   |

|     | Input Data Setup Time Before Clock<br>Rising Edge (External Clock)  | 30                | -               | 23               | -               | 19              | -               | -15  |

| 66  | Input Data Hold Time After Clock Ris-<br>ing Edge (External Clock)  | 40                | -               | 31               | -               | 25              | -               | - 15 |

MOTOROLA 24

DSP56001

| D | SP56001     | Electrical  | Charae      | cteristics |

|---|-------------|-------------|-------------|------------|

| A | C Electrica | I Character | ristics - S | SCI Timing |

|   |             |             |             |            |

DESCROT DEACHTOR CAPACITERISES AC REACTERISES - SCATTERISE CAPACITY - SCATTERISES CAPACITY ier and loyc)

| Num | Characteristics                                              | 20.5            | MHz | 27 1          | //Hz | 33 N          | IHz | Unit |

|-----|--------------------------------------------------------------|-----------------|-----|---------------|------|---------------|-----|------|

|     |                                                              | Min             | Max | Min           | Max  | Min           | Max |      |

| 67  | Asynchronous Clock Cycle                                     | 64 cyc          | -   | 64-cyc        | -    | 64-cyc        | -   | ns   |

| 68  | Clock Low Period                                             | 32-cyc-20       | -   | 32-cyc-15     | -    | 32-cyc-13     | -   | 115  |

| 60  | Clock High Period                                            | 32-cjo-20       | -   | 32-cyc-15     | -    | 32-cyc-13     | -   | 115  |

| 71  | Output Data Setup to Clock Rising<br>Edge (Internal Clock)   | 32) cyc<br>-100 | -   | 32.cpc<br>-77 | -    | 32.cpc<br>-61 | -   | - 15 |

| 72  | Output Data Hold After Clock Rising<br>Edge (Internal Clock) | 32-cyc<br>-100  | -   | 32-cyc<br>-77 | -    | 32.cjc<br>-61 | -   | - 15 |

DSP56001

| DSP56001 Electrical Characteristics                   |

|-------------------------------------------------------|

| Note: In the wire CR note, TXD can be public up by 15 |

| SCI Figure 2. SCI Asynchronous Mode Timing            |

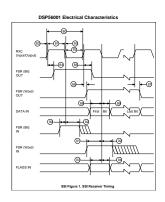

|   | AC Electrical Characteristics - SSI Timing                                                                   |

|---|--------------------------------------------------------------------------------------------------------------|

|   | Voc = 5.0 Vdc ± 10%, T <sub>J</sub> = -40 to +105° C, CL = 50 pl + 1 TTL Load at 20.5 MHz and 27 MH          |

|   | Vcc = 5.0 Vdc ± 5%, T <sub>2</sub> = -40 to +105° C, CL = 50 pl + 1 TTL Load at 33 MHz,                      |

|   | see SSI Figures 1 and 2)                                                                                     |

|   | cyc = Clock cycle = 1/2 instruction cycle = 2 T cycles                                                       |

|   | SSICC = SSI clock cycle time                                                                                 |

|   | TXC (SCK Pin) = Transmit Clock                                                                               |

|   | RXC (SCD or SCK Pin) = Receive Clock                                                                         |

|   | FST (SC2 Pin) = Tranamit Frame Sync                                                                          |

|   | FSR (SC1 or SC2 Pin) = Receive Frame Sync                                                                    |

|   | ck = Internal Clock                                                                                          |

|   | k ok = External Clock                                                                                        |

|   | g ck = Gated Clock                                                                                           |

|   | ck a = Internal Clock, Asynchronous Mode (Asynchronous implies that TXC and<br>RXC are two different clocks) |

| ł | ck s = Internal Clock, Synchronous Mode (Synchronous implies that TXC and<br>PXC are the same clock)         |

| ł | al = bit length                                                                                              |

|   | el = word length                                                                                             |

| Num | Characteristics                                                                                     | 20.5 MHz |          | 27 MHz         |          | 33 MHz         |          | Unz            |  |

|-----|-----------------------------------------------------------------------------------------------------|----------|----------|----------------|----------|----------------|----------|----------------|--|

|     |                                                                                                     | Min      | Max      | Min            | Max      | Min            | Max      |                |  |

| 80  | Clock Cycle (see Note 1)                                                                            | 4 cyc    | -        | 4 cyc          | -        | 4 cyc          | -        | ns             |  |

| 81  | Clock High Period                                                                                   | 2×cyc-20 | -        | 2-cyc-15       | -        | 2-cyc-13       | -        | ns             |  |

|     | Clock High Period                                                                                   | 2×cyc-20 | -        | 2-cyc-15       | -        | 2-cyc-13       | -        | - 15           |  |

|     | RXC Rising Edge to FSR Out (bi) High<br>x ck<br>i ck a                                              | =        | 80<br>50 | =              | 61<br>38 | =              | 48<br>21 | ns<br>ns       |  |

| 85  | RXC Rising Edge to FSR Out (bi) Low<br>x ck<br>i ck a                                               | Ξ        | 70<br>40 | -              | 54<br>31 | -              | 8 B      | .ns<br>.ns     |  |

|     | RXC Raing Edge to FSR Out (wi) High<br>x ck<br>i ck a                                               | Ξ        | 70<br>40 | =              | 54<br>31 | =              | 42<br>25 | .ns<br>.ns     |  |

| 67  | RXC Rising Edge to FSR Out (w) Low<br>x ck<br>i ck a                                                | Ξ        | 70<br>40 | =              | 54<br>31 | =              | 43<br>25 | ns<br>ns       |  |

| 60  | Data in Setup Time Before RXC (SCK<br>in Synchronous Mode) Falling Edge<br>x ck<br>i ck a<br>i ck a | N K G    | Ξ        | 12<br>27<br>19 | Ξ        | 10<br>22<br>16 | Ξ        | ns<br>ns<br>ns |  |

|     | Data in Hold Time After RXC Falling<br>Edge x ck<br>i ck a                                          | 25<br>5  | =        | 27<br>4        | Ξ        | 22<br>4        | Ξ.       | ns<br>ns       |  |

| 90  | FSR input (bl) High Before RXC Falling<br>Edge x ck<br>i ck a                                       | 15<br>35 | Ξ        | 12<br>27       | Ξ        | 10<br>23       | Ξ        | ns<br>ns       |  |

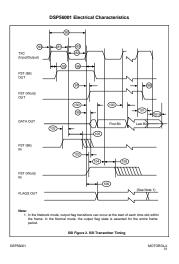

### DSP56001 Electrical Characteristics AC Electrical Characteristics - SSI Timing (Continued)

| Num   | Characteristics                                                                                             | 20.5     | MHz      | 271      | MHz      | 33       | MHz      | Un       |

|-------|-------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|

|       |                                                                                                             | Min      | Max      | Min      | Max      | Min      | Max      |          |

| 93    | Flags input Setup Before RXC Failing<br>Edge x ck<br>i ck a                                                 | 30<br>50 | =        | 23<br>39 | =        | 19<br>31 | Ξ        | ns<br>na |

| 94    | Flags Input Hold Time After RXC<br>Falling Edge x.ck<br>i.ck a                                              | 35<br>5  | =        | 27<br>4  | =        | 22<br>4  | Ξ        | ns<br>ns |

| 22    | TXC Rising Edge to FST Out (bi) High<br>x dk<br>i ck a                                                      | =        | 70<br>30 | =        | 54<br>23 | =        | 43<br>19 | 15       |

| 96    | TXC Rising Edge to FST Out (b) Low<br>x dk<br>i ck a                                                        | Ξ        | 65<br>35 | Ξ        | 50<br>27 | Ξ        | 40<br>22 | ns<br>ns |

|       | TXC Rising Edge to FST Out (W) High<br>x ck<br>i ck a                                                       | Ξ        | 65<br>25 | =        | 50<br>27 | =        | 40<br>22 | ns<br>ns |

| 58    | TXC Rising Edge to FST Out (W) Low<br>x ck<br>i ck a                                                        | Ξ        | 65<br>35 | =        | 50<br>27 | =        | 40<br>22 | ns<br>ns |

| 99    | TXC Rising Edge to Data Out Enable<br>from High Impedance x ck<br>i ck a                                    | =        | 65<br>40 | Ξ        | 50<br>31 | Ξ        | 49<br>22 | ns<br>ns |

|       | TXC Rising Edge to Data Out Valid<br>x ck<br>i ck a                                                         | Ξ        | 65<br>40 | =        | 50<br>31 | =        | 49<br>22 | ns<br>ns |

|       | TXC Rising Edge to Data Out High<br>Impedance (periodically sampled, and<br>not 100% tested) x ck<br>i ck a | =        | 70<br>40 | =        | 54<br>31 | =        | 47 22    | .ns      |

| 101a1 | XC Falling Edge to Data Out High<br>Impedance for Gated Clock Mode Only<br>g ck                             | cyc+tch  | -        | cyc+tch  | -        | cyc+tch  | -        | - 15     |

| 102   | FST input (bi) Setup Time Belore TXC<br>Falling Edge x ck<br>i ck a                                         | 15<br>35 | =        | 12<br>27 | =        | 10<br>23 | Ξ        | ns<br>ns |

| 103   | FST input (w) to Data Out Enable from<br>High impedance                                                     | -        | 60       | -        | 46       | -        | 37       | - 15     |

| 104   | FST input (w) Setup Time Before TXC<br>Falling Edge x ck<br>i ck a                                          | 20<br>55 | =        | 15<br>42 | =        | 13<br>34 | =        | ns<br>ns |

| 105   | FST input Hold Time After TXC Falling<br>Edge x ck<br>i ck a                                                | 25<br>5  | =        | 27<br>4  | =        | 22<br>4  | =        | ns<br>ns |

| 106   | Flag Output Valid After TXC Rising<br>Edge x ck<br>i ck a                                                   | =        | 70<br>40 | =        | 54<br>31 | =        | 41       | ns<br>ns |

Note: 1. For internal clock, External Clock Cycle is defined by Icyc and SSI control register.

DSP56001

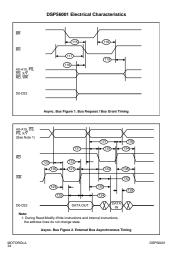

<section-header><section-header><section-header><text><text><text><text><text>

| Num | Characteristics                                                                                                             | 20.5 MHz                   |                               | 27 MHz                     |                               | 33                           | Un                            |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------|----------------------------|-------------------------------|------------------------------|-------------------------------|----|

|     |                                                                                                                             | Min                        | Max                           | Min                        | Max                           | Min                          | Max                           |    |

| 115 | Delay from BR Assertion to BG                                                                                               | _                          |                               | _                          |                               | _                            |                               | t  |

|     |                                                                                                                             | 2-cyc+tch                  | 20                            |                            | 4°cyc+tch+<br>15              |                              | 4°cyc+tch+<br>13              | 1  |

|     | (see Note 2)                                                                                                                | cyc+tch                    | 4°cyc+tch+<br>cyc'W5+20       | cyc+tch                    | 4"cyc+tch+<br>cyc'W5+15       | cyc+tch                      | 4°cyc+tch+<br>cyc'W5+13       | 1  |

|     | (see Note 3)                                                                                                                | cyc+tch                    | 6°cyc+tch+<br>2°cyc*WS+<br>20 | cyc+tch                    | 6°cyc+tch+<br>2°cyc*WS+<br>15 | cyc+tch                      | 6°cyc+tch+<br>2°cyc*WS+<br>13 | ľ  |

|     | (nee Note 4)                                                                                                                | Infinity                   | -                             | Infinity                   |                               | Infinity                     |                               |    |

|     | (see Note 5)                                                                                                                | 1ch+4                      | cyc+tch+30                    | tch+3                      | cyc+tch+23                    | tch+3                        | cyc+tch+19                    |    |

|     | Flags Input Hold Time After RXC<br>Falling Edge Deassertion                                                                 | 2°cyc                      | 4°cyc+20                      | 2°cyc                      | 4°cyc+15                      | 2°cyc                        | 4'cyc+13                      | ľ  |

|     | BG Deassertion Duration                                                                                                     | 2*cyc-10                   | -                             | 2"cyc-8                    | -                             | 2"cyc-6                      | -                             | 1  |

|     | Delay from Address, Data, and Control<br>Bus High Impedance to BG Assertion                                                 | 0                          | -                             | 0                          | -                             | 0                            | -                             | Г  |

| 119 | Delay from BG Deassertion to<br>Address, Data, and Control Bus<br>Enabled                                                   | -                          | sch-10                        | -                          | sch-ē                         | -                            | sch-6                         | ľ  |

| 120 | Address Valid to WR Assertion WS+0<br>WS+0                                                                                  | 10-9<br>cyc-9              | 15+5<br>cyc+5                 | 10-7<br>cyc-7              | 15+5<br>cyc+5                 | 10-5.5<br>cjo-5.5            | 15+5<br>cyc+5                 | 1  |

|     | WR Assertion Width WS+0<br>WS>0                                                                                             | W5*cyc<br>+tcl-9           | Ξ                             | cyc-7<br>W5*cpc<br>+td-7   | Ξ                             | cje-5.0<br>W5*cje<br>+kd-5.0 | Ξ                             | 1  |

| 122 | WR Deassertion to Address Not Valid                                                                                         | 12h-12                     | -                             | tch-9                      | -                             | tch-7.5                      | -                             | 1  |

|     | WR Assertion to Data Out Valid WS+0<br>WS>0                                                                                 | 1ch-9<br>0                 | \$ch+10<br>10                 | 1ch-7<br>0                 | 1ch+8<br>8                    | 10h-5.5<br>0                 | 1ch+6.5<br>6.5                | 1  |

| 124 | Data Out Hold Time from WR<br>Deassertion (The maximum specifica-<br>tion is periodically sampled, and not<br>100% tested.) | sch-9                      | tch+7                         | sch-7                      | tch+6                         | 10-55                        | Ich+4.5                       | ľ  |

| 125 | Data Out Setup Time to WK<br>Deassertion (see Note 6) WS+0<br>WS>0                                                          | 151-5<br>W51'cyc<br>+151-5 | Ξ                             | 151-5<br>W51'cyc<br>+151-5 | Ξ                             | 151-5<br>W51'cyc<br>+151-5   | Ξ                             | ;  |

| 126 | RD Deassertion to Address Not Valid                                                                                         | tch-9                      | -                             | tch-7                      | -                             | 1ch-5.5                      | -                             | ۰. |

DSP56001

| Num  | Characteristics                           |                  | 20.5 MHz                            |                                     | 27 MHz                              |                                     | 33 MHz                              |                                     | Uni        |

|------|-------------------------------------------|------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|------------|

|      |                                           |                  | Min                                 | Max                                 | Min                                 | Max                                 | Min                                 | Max                                 | L .        |

| 127  | Address Valid to W<br>RD deassertion W    | 5=0<br>5>0       | cyc+tcl-8<br>((WS+1)-<br>cyc)+tcl-8 | Ξ                                   | cyc+tcl-6<br>((WS+1)+<br>cyc)+tcl-6 | Ξ                                   | cyc+tcl-6<br>((WS+1)+<br>cyc)+tcl-6 | Ξ                                   | ns<br>ns   |

|      | Input Data Hold Time to RD<br>Deassertion |                  | 0                                   | -                                   | 0                                   | -                                   | 0                                   | -                                   | -15        |

| 129  | RD Assertion Width W<br>W                 | 5×0<br>5×0       | cyc-9<br>((WS+1)*<br>cyc)-9         | Ξ                                   | cyc-7<br>((WS+1)*<br>cyc)-7         | =                                   | cyc-6.5<br>((WS+1)*<br>cyc)-6.5     | =                                   | ns<br>ns   |

| 130  | Address Valid to V<br>Input Data Valid V  | VS = 0<br>VS > 0 | Ξ                                   | cyc+td-18<br>((WS+1)-<br>cyc)+td-18 | =                                   | cyc+td-14<br>((WS+1)+<br>cyc)+td-14 | =                                   | cyc+td-11<br>((WS+1)+<br>cyc)+td-11 | ns<br>ns   |

| 131  | Address Valid to RD Assertion             | _                | 12-9                                | 121+5                               | 10-7                                | 121+5                               | 10-5.5                              | 121+5                               | 115        |

| 1.32 | RD Assertion to<br>Input Data Valid       | W\$=0<br>W\$>0   | Ξ                                   | cyc-14<br>((NIS+1)*<br>cyc)-14      | Ξ                                   | cyc-11<br>((WS+1)*<br>cyc)-11       | Ξ                                   | 0/0-9<br>((WS+1)*<br>0/0-9          | ns<br>ns   |

| 123  | WR Deassertion to RD Assertion            |                  | cyc-15                              | -                                   | cyc-12                              | -                                   | cyc-10                              | -                                   | 0.5        |

| 134  | RD Deassertion to RD Assertion            | _                | cyc-10                              | -                                   | cyc-8                               | -                                   | cyc-6.5                             | -                                   | 115        |

| 135  | WR Deassertion to<br>WR Assertion         | W5+0<br>W5+0     | cyc-15<br>cyc+tch-15                | Ξ                                   | cyc-12<br>cyc+tch-12                | -                                   | cyc-10<br>cyc+tch-10                | -                                   | 15<br>15   |

| 136  |                                           | NS-0<br>WS-0     | cyc-10<br>cyc+tch-10                | Ξ                                   | cyc+8<br>cyc+1ch+8                  | =                                   | cyc-6.5<br>cyc+tch-<br>6.5          | =                                   | 715<br>715 |

a the Biology Chickan Hann Science, Janeszi 20,53M/sz and WS-ol, Min = td-4 at 20,53M/sz and WS-ol, Min = td-3 at 22 Minz and WS-ol, Min = td-3 at 22 Minz and WS-ol, Min = td-3 at 23 Minz and WS-ol, Min = td-2,5 at 23 Minz and WS-ol, Min = td-2,5 at 23 Minz and WS-ol, Min = td-2,5

DSP56001

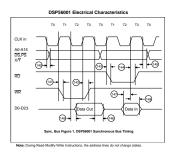

# DSP56001 Electrical Characteristics AC Electrical Characteristics - External Bus Synchronous Timing Vec.s6Verg.9W, T<sub>1</sub>-+0 W C C #35.5Me 27 Me Vec.s6Verg.9W, T<sub>1</sub>-+0 W C C #35.5Me 27 Me

| Num | Characteristics                                                   | 20.5 MHz |              | 27 MHz |              | 33 MHz |              | Unit     |

|-----|-------------------------------------------------------------------|----------|--------------|--------|--------------|--------|--------------|----------|

|     |                                                                   | Min      | Max          | Min    | Max          | Min    | Max          | I        |

| 140 | Cik Low Transition To Address Valid                               | -        | 24           | -      | 19           | -      | 19           | 115      |

| 141 | Clk High Transition To WK WS = 0<br>Assertion (see Note 2) WS > 0 | ő        | 19<br>tch+19 | °.     | 15<br>1ch+15 | °.     | 17<br>1ch+17 | ns<br>ns |

| 142 | Cik High Transition To WR<br>Deassertion                          | 5        | 21           | 5      | 16           | 5      | 13           | - 15     |

| 143 | Cik High Transition To RD Assertion                               | 0        | 19           | 0      | 15           | 0      | 16           | 15       |

| 544 | Cik High Transition To RD Deassertion                             | 5        | 17           | 5      | 13           | 45     | 10.5         | 115      |

| 145 | Cik Low Transition To Data-Out Valid                              | -        | 25           | -      | 19           | -      | 19           | 115      |

| 146 | Cik Low Transition To Data-Out Invalid<br>(see Note 3)            | 5        | -            | 4      | -            | 25     | -            | ns       |

|     | Data-In Valid To Clk High Transition<br>(Setup)                   | 0        | -            | 0      | -            | 0      | -            | ns       |

| 148 | Cik High Transition To Data-In Invalid<br>(Hold)                  | 12       | -            | 12     | -            | 13     | -            | ns<br>ns |

| 149 | Cik Low To Address Invalid<br>(new Note 1)                        | 3        | -            | з      | -            | з      | -            | -15      |

Note: 1.4. Cheng operations which are when ------1.4. Cheng operations and the second seco

DSP56001

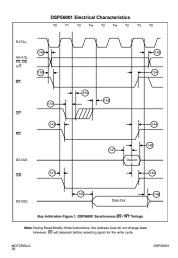

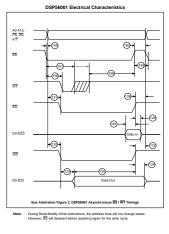

## DSP56001 Electrical Characteristics AC Electrical Characteristics - Bus Strobe / Wait Timing

| Num | Characteristics                                                            | 20.5                  | MHz                        | 27 1                     | MHz                       | 33                        | MHz                        | Unit      |

|-----|----------------------------------------------------------------------------|-----------------------|----------------------------|--------------------------|---------------------------|---------------------------|----------------------------|-----------|

|     |                                                                            | Min                   | Max                        | Min                      | Max                       | Min                       | Max                        |           |

| 150 | Cik Low Transition To IIS Assertion                                        | 4                     | 24                         | 3                        | 19                        | 2.5                       | 19                         | ns        |

|     | WT Assertion To Cik Low Transition<br>(setup time)                         | 4                     | -                          | 3                        | -                         | 2.5                       | -                          | ns<br>ns  |

| 152 | Cik Low Transition To WT Deassertion<br>For Minimum Timing                 | 14                    | cyc-8                      | 11                       | 906                       | 12                        | 905                        | <b>ns</b> |

| 153 | WT Deassertion To Clk Low Transition<br>For Maximum Timing (2 wait states  | 0                     | -                          | 6                        | -                         | 5                         | -                          | 75        |

| 154 | Cik High Transition To B5 Deassertion                                      | 5                     | 26                         | 4                        | 20                        | 35                        | 19                         | ns        |

| 155 | 55 Assertion To Address Valid                                              | -2                    | 10                         | -2                       | - 0                       | -2                        | 6.5                        | ns        |

| 156 | ISS Assertion To WT Assertion<br>(see Note 2)                              | 0                     | cyo-15                     | 0                        | cyc-11                    | 0                         | cyo-10                     | 75        |

|     | ISS Assertion To WT Dessertion<br>(See Note 2 and Note 4) WS ≤ 2<br>WS ≥ 2 | cyc<br>(WS-1)<br>-cyc | 2*cyc-15<br>W\$*cyc<br>-15 | CJIC<br>(WIS-1)<br>-CJIC | 2"cyc-11<br>W5"cyc<br>-11 | cyc+4<br>(WS-1)<br>+cyc+4 | 2*cyc-10<br>W\$*cyc<br>-10 | ns<br>ns  |

| 158 | WT Deassertion To BS Deassertion                                           | cyc+td                | 2-cyc+td<br>+23            | eye+td                   | 2-cyc+td<br>+17           | eye+td                    | 2-cyc+td<br>+15            | <b>ns</b> |

| 159 | Minimum IDS Deasaertion Width For<br>Consecutive External Accesses         | sch-7                 | -                          | sch-6                    | -                         | sch-4.5                   | -                          | 75        |

|     | 05 Dessertion To Address Invalid<br>(see Note 3)                           | tch-10                |                            | sch-8                    |                           | tch-6.5                   |                            |           |

| 161 | Data-In Valid to RD Deassertion<br>(Set Up)                                | 16                    | -                          | 12                       | -                         | 10                        | -                          | ns        |

and cases which are referenced to a device topol signal are researced to production with 400 particle of the respective topol signal to the text. Set to provide the respective topol signal topol si

AC timing specification mapped to the 50% pp 2. If wait status are also specification number 3. BS2 deassertion to ad to be valid.

The minimum numbe 5. For read-modify-write write cycle. However, sited for each of the second of the

DSP56001

MOTOROLA 37

DSP56001 MOTOROLA 39 DSP56001 Electrical Characteristics

MOTOROLA DSP56001 40

| A | PE | ΞÞ | łD | A |  |

|---|----|----|----|---|--|

|   |    |    |    |   |  |

|                      |                               | ORDERI                            | NG INFORMATION                                     |                                                                                                       |

|----------------------|-------------------------------|-----------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| D                    | SP56001FE 33                  | Pi<br>20<br>27                    | requency<br>= 20.5 MHz<br>= 27 MHz<br>= 23 MHz     | Pack age Type                                                                                         |

|                      |                               |                                   | ISP Type<br>2001 = RAM Part                        | RC = Pin Grid Array<br>FE = Cenamic Quad<br>Flat Pack (CQFP)<br>FC = Plastic Quad<br>Flat Pack (PQFP) |

|                      |                               | DSP56001 S                        | OCKET INFORMATION<br>PGA                           |                                                                                                       |

| Supplier             | Telephone                     | Socket Type                       | Part Number                                        | Comment                                                                                               |

| Advanced Interc      | (401) 823-5200                | Standard 88 Pin                   | 4C5088-01TG <sup>2</sup>                           | Includes Cutout in Center                                                                             |

|                      | (717) 564-0100                | Standard 88 Pin                   | 5-916223-3<br>5-55283-9<br>5-55283-4               | Low Insertion Force<br>ZIF Production                                                                 |

| Robinson Nuger       | (012) 945-0211                | Standard 128 Pin<br>Custom Pinout | 1-55383-4<br>PGA-080CM3P-5-TG <sup>2</sup>         | ZIF Burn-In and Test                                                                                  |

| Santec               | (012) 944-6733                | Standard 120 Pin                  | PGA-080CHP3-SL-TG<br>MVAS-120-ZSTT-13 <sup>1</sup> | <sup>3</sup> High Temp, Longer Leads<br>Includes Output in Center                                     |

| NOTES:               |                               | Custom 88 Pin                     | CPAS-88-ZSTT-138F                                  | No Cutout                                                                                             |

| and tin<br>2. Please | shell.<br>specify wirewtap an |                                   | part number shown specifies or                     | profile solder tail pins having a tin contact<br>ald contact and tin shell.                           |

|                      |                               |                                   | CQFP                                               |                                                                                                       |

| Suppler              | Telephone                     | Socket Type                       | Part Number                                        | Comment                                                                                               |

|                      | (717)584-0100                 | -                                 | 822054-21                                          | Converts CQFP to fit AMP's<br>132 position PQFP "Micro-Pitch<br>Socket".                              |