ETV/AN89004

Author: R.C.J. Brink, Eindhoven

#### INTRODUCTION

# 1.1. Purpose

This document is a user manual for the I<sup>2</sup>C software module IIC51. It is intended for Intel PLM51 users who need to control an I<sup>2</sup>C bus. This document assumes some basic knowledge about I<sup>2</sup>C and Intel PLM51.

### 1.2. Scope

IIC51 is a software module to provide an Intel PLM51 user with a set of procedures to control a bi-directional I<sup>2</sup>C bus. These procedures have been coded in Intel ASM51 and have been optimized for speed. IIC51 supports all common used I2C master transmitter and master receiver protocols. Each different protocol corresponds to one of the procedures in IIC51. IIC51 is available in two different versions:

#### IIC51S:

IIC51S is a module for singlemaster I2C to be used on microcontrollers of the 8XC51 family. It directly controls the microcontroller I/O pins by software without the need of any specific hardware. No other I<sup>2</sup>C masters are allowed on the bus. Note that the electrical characteristics of this microcontroller family are not conform the I<sup>2</sup>C specifications.

#### IIC51M:

IIC51M is a module for multimaster I<sup>2</sup>C to be used on microcontrollers of the PCB8XC552/C652 family. It makes use of the built-in I<sup>2</sup>C interface hardware (SIO1) of these microcontrollers. Since this hardware is a multimaster interface, other I<sup>2</sup>C masters are allowed on the

All I<sup>2</sup>C transfer procedures in IIC51S are fully software interface compatible with IIC51M. This allows a single PLM51 program using I<sup>2</sup>C to be written for both mentioned microcontroller families.

| <b>1.3. Defi</b> i                      | nitions, Acronyms and Abbreviations Inter-IC bus                                                                                                                                                                                                                                                   |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLM51<br>ASM51<br>RL51                  | High level Program Language for 8051 family Microcontrollers<br>Assembly Language for 8051 family Microcontrollers<br>Relocating Linker for 8051 family Microcontrollers                                                                                                                           |

| S<br>P<br>A<br>N<br>SIvW<br>SIvR<br>Sub | I <sup>2</sup> C Message Start Condition I <sup>2</sup> C Message Stop Condition I <sup>2</sup> C Message Acknowledge I <sup>2</sup> C Message Negative Acknowledge I <sup>2</sup> C Message Slave Address + Write I <sup>2</sup> C Message Slave Address + Read I <sup>2</sup> C Slave Subaddress |

| NV-Memory                               | I <sup>2</sup> C Controlled Non Volatile Memory (F <sup>2</sup> PROM)                                                                                                                                                                                                                              |

|    | 4. References  I <sup>2</sup> C Specification  I <sup>2</sup> C-bus compatible ICs  Philips Components Data Handbook IC12a                           | 1989       |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2. | PL/M-51 User's Guide for DOS Systems Intel Corporation                                                                                               | 1986       |

| 3. | MSC-51 Macro Assembler User's Guide for DOS Systems<br>Intel Corporation                                                                             | 1986       |

| 4. | MSC-51 Utilities User's Guide for DOS Systems<br>Intel Corporation                                                                                   | 1986       |

| 5. | Single-chip 8-bit microcontrollers PCB83C552/PCB80C552, PCB83C652/PCB80C652 et $\rm I^2C$ -bus compatible ICs Philips Components Data Handbook IC12a | c.<br>1989 |

| 6. | Single-chip 8-bit microcontroller PCB80C51 Integrated circuits Book IC14                                                                             | 1987       |

May 1989 1

ETV/AN89004

#### 2. GENERAL DESCRIPTION

# 2.1. Perspective

IIC51 is designed for use in stand-alone microcontroller I<sup>2</sup>C systems. It is mainly written to provide a standard set of procedures for computer controlled television/teletext concepts based on 8051 family microcontrollers.

#### 2.2. Functions

IIC51 contains the following functions:

- Initialisation of the I<sup>2</sup>C interface (software and hardware)

- Transfer of I<sup>2</sup>C messages to and from an I<sup>2</sup>C slave device

- Error detection

- Automatic retrying if an error occurs during a transfer (up to 5 attempts)

- Error recovery if the bus is held by a slave device that is out of bit-sync

- Optional slave receiver/transmitter function (IIC51M only)

#### 2.3. User Characteristics

IIC51 is designed to be an easy to use package. All needed code and data is defined in a single object module (IIC51M.OBJ or IIC51S.OBJ). The PLM51 user needs only to link this module to his own application object modules, using Intel's RL51. Procedures and data of concern to the user can be declared EXTERNAL by including the file IIC51.DCL.

#### 2.4. General Constraints

IIC51 is coded for and translated by the Intel MSC-51 Macro Assembler. It is tested together with Intel PLM51 modules. Intel utilities used for testing:

- MSC-51 Macro Assembler, ASM51.EXE, Version V2.3

- PL/M-51 Compiler, PLM51.EXE, Version V1.2 and V1.3

- MSC-51 Relocator and Linker, RL51.EXE, Version V3.1

Development is done on an IBM-PC/AT running DOS.

#### IIC51S needs:

- 350 Bytes CODE (approx.)

- 6 Bytes DATA

- 1 Byte Bit-Addressable DATA

- 1 Bit

#### IIC5MS needs:

- 400 Bytes CODE (approx.)

- 6 Bytes DATA

- 1 Byte Bit-Addressable DATA

- 1 Bit

- Exclusive use of Register Bank 1

ETV/AN89004

#### 3. FUNCTIONAL DESCRIPTION

### 3.1. Master Mode Functions

This section describes the available functions in IIC51 on a procedure by procedure basis.

Each procedure must be declared EXTERNAL by the PLM51 user. In this declaration the user can specify the type returned by each procedure. All procedures (except Init\_IIC) can return a BIT or a BYTE (depending on the chosen EXTERNAL declaration). The BIT or BYTE returned is 0 if the I<sup>2</sup>C transmission was successful. If the user decides to declare a procedure untyped, the result of the previous I<sup>2</sup>C transmission can always be checked by examining the static BIT variable IIC\_Error. Note that typed procedures must be called using an expression. If the result of an I<sup>2</sup>C procedure is to be ignored, a dummy assignment must be done for a typed procedure. An untyped procedure can be called by the PLM51 CALL statement, without any additional overhead. The examples in the following section assume the procedures to be declared untyped.

Note that the least significant bit of all slaveaddresses passed to the I<sup>2</sup>C procedures must be 0.

### 3.1.1. Init\_IIC

#### **Declaration:**

```

Init_IIC:

PROCEDURE ( Own_Slave_Address ) EXTERNAL ;

DECLARE ( Own_Slave_Address ) BYTE ;

END ;

```

#### Description:

Init\_IIC must be called once after reset, before any other procedure is used. It initialises all I<sup>2</sup>C internal static data and hardware. The Own\_Slave\_Address is passed to Init\_IIC for the optional slave function in a multimaster I<sup>2</sup>C system (IIC51M). In a singlemaster I<sup>2</sup>C system (IIC51S), the Own\_Slave\_Address is ignored. Note that Init\_IIC does not effect the global interrupt enable flag (EA). IIC51M requires the user to enable interrupts afterwards (see example).

#### Example:

```

CALL Init_IIC ( 54h ) ;

ENABLE ; /*Enable Interrupts; EA = 1 */

```

## 3.1.2. IIC\_Test\_Device

### **Declaration:**

```

IIC_Test_Device:

PROCEDURE ( Slave_Address ) [ BIT | BYTE ] EXTERNAL ;

```

#### <u>Description</u>

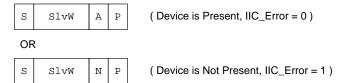

IIC\_Test\_Device just sends the slaveaddress on the I<sup>2</sup>C bus. It can be used to check the presence of a device on the I<sup>2</sup>C bus.

#### I2C Protocol:

## Example:

```

DECLARE IIC_Error BIT EXTERNAL ;

......

CALL IIC_Test_Device ( 8Ch ) ;

IF (IIC_Error ) THEN

"Device is Not Present Handling"

ELSE

"Device is Present Handling"

```

ETV/AN89004

#### 3.1.3. IIC\_Write

#### **Declaration:**

```

IIC_Write:

PROCEDURE ( Slave_Address, Count, Source_Ptr ) [ BIT | BYTE ] EXTERNAL ;

DECLARE ( Slave_Address, Count, Source_Ptr ) BYTE ;

END ;

```

#### **Description:**

IIC\_Write is the most basic procedure to write a message to a slave device.

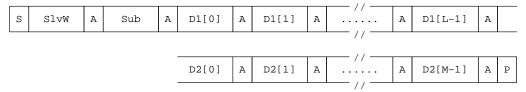

#### I<sup>2</sup>C Protocol:

```

L = Count

D1[0..L-1] BASED by Source_Ptr

```

| S SlvW A D1[0] A D1[1] A | //<br>A | D1[L-1] | A P |

|--------------------------|---------|---------|-----|

|--------------------------|---------|---------|-----|

#### Example:

```

DECLARE Data_Buffer ( 4 ) BYTE ;

.....

CALL IIC_Write ( 0C2h, LENGTH ( Data_Buffer ), .Date_Buffer ) ;

```

#### 3.1.4. IIC\_Write\_Sub

#### Declaration:

```

IIC_Write_Sub:

PROCEDURE ( Slave_Address, Count, Source_Ptr, Sub_Address ) [ BIT | BYTE ] EXTERNAL;

DECLARE ( Slave_Address, Count, Source_Ptr, Sub_Address ) BYTE;

END :

```

#### Description:

IIC\_Write\_Sub writes a message preceded by a subaddress to a slave device.

# I<sup>2</sup>C Protocol:

```

L = Count

Sub = Sub_Address

D1[0..L-1] BASED by Source_Ptr

```

| S SlvW A Sub A D1[0] A D1[1] A |  | A | D1[L-1] | А | Р |  |

|--------------------------------|--|---|---------|---|---|--|

|--------------------------------|--|---|---------|---|---|--|

#### Example:

```

DECLARE Data_Buffer ( 8 ) BYTE ;

.....

CALL IIC_Write_Sub ( 48h, LENGTH ( Data_Buffer ), .Date_Buffer, 2 ) ;

```

### 3.1.5. IIC\_Write\_Sub\_SWInc

# Declaration:

```

IIC_Write_Sub_SWInc:

PROCEDURE ( Slave_Address, Count, Source_Ptr, Sub_Address) [ BIT | BYTE ] EXTERNAL ;

DECLARE ( Slave_Address, Count, Source_Ptr, Sub_Address ) BYTE ;

END ;

```

## Description:

Some I<sup>2</sup>C devices addressed with a subaddress do not automatically increment the subaddress after reception of each byte. IIC\_Write\_Sub\_SWInc can be used for such devices the same way IIC\_Write\_Sub is used. IIC\_Write\_Sub\_SWInc splits up the message in smaller messages and increments the subaddress itself.

ETV/AN89004

#### I<sup>2</sup>C Protocol:

```

Τ.

= Count

Sub

= Sub Address

D1[0..L-1] BASED by Source_Ptr

S

SlvW

Α

Sub

D1[0]

Ρ

S

SlvW

Α

Sub+1

D1[1]

Ρ

S

SlvW

Sub+L-1

Α

D1[L-1]

Ρ

```

#### Example:

```

DECLARE Data_Buffer ( 6 ) BYTE ;

.....

CALL IIC_Write_Sub_SWInc ( 80h, LENGTH ( Data_Buffer ), .Date_Buffer, 0 ) ;

```

#### 3.1.6. IIC\_Write\_Memory

### **Declaration:**

```

IIC_Write_Memory:

PROCEDURE ( Slave_Address, Count, Source_Ptr, Sub_Address) [ BIT | BYTE ] EXTERNAL;

DECLARE ( Slave_Address, Count, Source_Ptr, Sub_Address ) BYTE;

END;

```

#### **Description:**

I<sup>2</sup>C Non-Volatile Memory devices (such as PCF8582) need an additional delay after writing a byte to it. IIC\_Write\_Memory can be used to write to such devices the same way IIC\_Write\_Sub is used. IIC\_Write\_Memory splits up the message in smaller messages and increments the subaddress itself. After transmission of each small message a delay of 40 milliseconds is inserted.

#### I<sup>2</sup>C Protocol:

```

L

= Count

Sub

= Sub_Address

D1[0..L-1] BASED by Source_Ptr

S

< Delay 40 ms >

D1[0]

Ρ

SlvW

Sub

Α

S

D1[1]

Ρ

< Delay 40 ms >

SlvW

Α

Sub+1

S

Ρ

< Delay 40 ms >

SlvW

Sub+L-1

Α

D1[L-1]

Α

```

### Example:

```

DECLARE Data_Buffer ( 10 ) BYTE ;

.....

CALL IIC_Memory ( 0A0h, LENGTH ( Data_Buffer ), .Date_Buffer, 0F0h ) ;

```

ETV/AN89004

#### 3.1.7. IIC\_Write\_Sub\_Write

```

Declaration:

```

#### **Description:**

IIC\_Write\_Sub\_Write write 2 data blocks preceded by a subaddress in one message to a slave device. This procedure can be used for devices that need an extended addressing method, without the need to put all data into one large buffer. Such a device is the ECCT (I<sup>2</sup>C controlled teletext device; see example).

# I<sup>2</sup>C Protocol:

```

L = Count1

M = Count2

Sub = Sub_Address

D1[0..L-1] BASED by Source_Ptr1

D2[0..M-1] BASED by Source_Ptr2

```

#### Example:

```

PROCEDURE Write_CCT_Memory ( Chapter, Row, Column, Data_Buf, Data_Count );

DECLARE ( Chapter, Row, Column, Data_Buf, Data_Count ) BYTE;

/*

The extended address (CCT-Cursor) is formed by Chapter, Row and Column. These three bytes are written after the subaddress (8) followed by the actual data which will be stored relative to the extended address.

*/

CALL IIC_Write_Sub_Write ( 22h, 3, .Chapter, 8, Data_Buf, Data_Count );

END Write_CCT_Memory;

```

# 3.1.8. IIC\_Read

# Declaration:

```

IIC_Read:

PROCEDURE ( Slave_Address, Count, Dest_Ptr ) [ BIT | BYTE ] EXTERNAL ;

DECLARE ( Slave_Address, Count, Dest_Ptr ) BYTE ;

END ;

```

#### **Description:**

ICC\_Read is the most basic procedure to read a message from a slave device.

## I<sup>2</sup>C Protocol:

```

M = Count

D2[0..M-1] BASED by Dest_Ptr

S SlvR A D2[0] A D2[1] A ..... A D2[M-1] N P

```

## Example:

```

DECLARE Data_Buffer ( 4 ) BYTE ;

.....

CALL IIC_Read ( 0B4h, LENGTH ( Data_Buffer ), .Data_Buffer ) ;

```

ETV/AN89004

#### 3.1.9. IIC\_Read\_Status

#### **Declaration:**

```

IIC_Read_Status:

PROCEDURE ( Slave_Address, Dest_Ptr ) [ BIT | BYTE ] EXTERNAL ;

DECLARE ( Slave_Address, Dest_Ptr ) BYTE ;

END ;

```

#### Description:

A lot of I<sup>2</sup>C devices have only a one status byte that can be read via I<sup>2</sup>C. IIC\_Read\_Status can be used for this purpose. IIC\_Read\_Status works the same as IIC\_Read but the user does not have to pass a count parameter.

#### I<sup>2</sup>C Protocol:

## Example:

```

DECLARE Status_Byte BYTE ;

.....

CALL IIC_Read_Status ( 84h, .Status_Byte ) ;

```

#### 3.1.10. IIC\_Read\_Sub

#### **Declaration:**

```

IIC_Read_Sub:

PROCEDURE ( Slave_Address, Count, Dest_Ptr, Sub_Address ) [ BIT | BYTE ] EXTERNAL;

DECLARE ( Slave_Address, Count, Dest_Ptr, Sub_Address ) BYTE;

END;

```

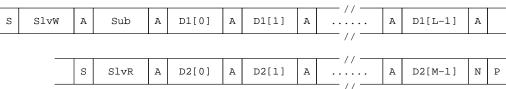

#### **Description:**

IIC\_Read\_Sub reads a message from a slave device preceded by a write of the subaddress. Between writing the subaddress and reading the message, an I<sup>2</sup>C restart condition is generated without surrendering the bus. This prevents other masters from accessing the slave device in between and overwriting the subaddress.

#### I<sup>2</sup>C Protocol:

```

M = Count

Sub = Sub_Address

D2[0..M-1] BASED by Dest_Ptr

```

|  | S | SlvW | A | Sub | А | S | SlvR | А | D2[0] | А | D2[1] | A |  | А | D2[M-1] | N | P |

|--|---|------|---|-----|---|---|------|---|-------|---|-------|---|--|---|---------|---|---|

|--|---|------|---|-----|---|---|------|---|-------|---|-------|---|--|---|---------|---|---|

#### Example:

```

DECLARE Data_Buffer ( 5 ) BYTE ;

.....

CALL IIC_Write_Sub ( 0A2h, LENGTH ( Data_Buffer ), .Data_Buffer, 2 ) ;

```

### 3.1.11. IIC\_Write\_Sub\_Read

#### Declaration:

# Description:

IIC\_Write\_Sub\_Read writes a data block preceded by a subaddress, generates an  $I^2C$  restart condition, and reads a data block. This procedure can be used for devices that need an extended addressing method. Such a device is the ECCT ( $I^2C$  controlled teletext device; see example).

ETV/AN89004

#### I<sup>2</sup>C Protocol:

```

L = Count1

M = Count2

Sub = Sub_Address

D1[0..L-1] BASED by Source_Ptr1

D2[0..M-1] BASED by Dest_Ptr2

```

#### Example:

```

PROCEDURE Read_CCT_Memory ( Chapter,Row, Column, Data_Buf, Data_Count );

DECLARE ( Chapter, Row, Column, Data_Buf, Data_Count ) BYTE ;

/*

The extended address (CCT-Cursor) is formed by Chapter, Row and Column. These three bytes are written after the subaddress (8). After that the actual data will be read relative to the extended address.

*/

CALL IIC_Write_Sub_Read ( 22h, 3, .Chapter, 8, Data_Buf, Data_Count );

END Read_CCT_Memory;

```

#### 3.2. Slave Mode Functions

I<sup>2</sup>C slave mode is provided by IIC51M only. All slave mode actions (except initialisation) take place in the SIO1 interrupt procedure. Slave mode I<sup>2</sup>C protocol is very application dependent. If a specific slave mode is required, the user have to modify three procedures in IIC51M at source level. The following sections describe these procedures. The program examples of the procedures implement an I<sup>2</sup>C slave protocol to read and write the microcontroller's on chip RAM via I<sup>2</sup>C. This can be a useful feature during program development and debugging.

#### 3.2.1. Init\_Slave

This procedure is called from IIC\_Init. In this procedure the user can initialise all static data concerning slave mode functions (if any).

#### Example:

```

Slave_Sub_Address: db 1

....

Init_Slave: mov Slave_Sub_Address,#0 ; Initialise Sub Address

ret

```

#### 3.2.2. Receive Slave

Receive\_Slave is a procedure called from the SIO1 interrupt procedure each time a byte is received from another I<sup>2</sup>C master. The procedure can make use of the bit "IICntrl.BYTE1EXPECTED", as defined in IIC51M. This bit is set to logic 1, every time the first data byte of an I<sup>2</sup>C message is about to be received. Receive\_Slave can use this bit to detect the start of a new message.

Normally all bytes received from the other master will be acknowledged (i.e., SIO1 control bit Assert Acknowledge is set, AA = 1). If AA is cleared by Receive\_Slave subsequent bytes in the message will be ignored and a negative acknowledge will be transmitted after reception of each byte. Note that the example does not make use of this feature.

# Constraints:

- Receive\_Slave <u>must</u> read the S1DAT register.

- Receive\_Slave may clear the SIO1 control bit AA, to stop acknowledging data.

- Receive\_Slave may not effect any other SIO1 hardware registers/bits.

- Receive\_Slave is only allowed to use the accumulator and register R0 in the current registerbank.

#### Example:

```

Receive_Slave: mov a,S1DAT ; Pick up data

mov r0,#Slave_Sub_Address ; Prepare for 1st byte

jbc IICCntrl.BYTE1EXPECTED,Save_Byte ; Jump if 1st byte

mov r0,Slave_Sub_Address ; Else data byte

inc Slave_Sub_Address ; Postincrement Sub.

Save_Byte: mov @r0,a ; Save_Data

ret ; Exit

```

ETV/AN89004

#### 3.2.3. Send\_Slave

Send\_Slave is a procedure called during the SIO1 interrupt procedure each time a byte has to be transmitted to another I<sup>2</sup>C master. This occurs after reception of I<sup>2</sup>C startcondition followed by the microcontroller's own slaveaddress (as passed to Init\_IIC) with read-bit. Send\_Slave will be called again after transmission of each subsequent byte, until a negative acknowledge is received from the reading I<sup>2</sup>C master.

#### Constraints:

- Send\_Slave must write to the S1DAT register.

- Send\_Slave may not effect any other SIO1 hardware registers/bits.

- Send\_Slave is only allowed to use the accumulator and register R0 in the current registerbank.

## Example:

Send\_Slave: mov r0,Slave\_Sub\_Address ; Pick up Sub Address

mov S1DAT,@r0 ; Send Data

inc Slave\_Sub\_Address ; Postincrement Sub.

ret