# INTEGRATED CIRCUITS

# APPLICATION NOTE

## ABSTRACT

Starts with an overview of I<sup>2</sup>C basics including functions of master & slave, data transfers, addressing and transfer formats and use of sub-addresses. Next, the I<sup>2</sup>C hardware features of the 87LPC76X are described including control, data and configuration registers and Timer I. Finally, a single-master ASM programming example is presented which includes send and receive routines with error recovery.

# **AN464** Using the 87LPC76X microcontroller as an I<sup>2</sup>C bus master

2000 Jan 11

# AN464

#### DESCRIPTION

The 87LPC76X Microcontroller offers the advantages of the 80C51 architecture in a small package and at a low cost. It combines the benefits of a high-performance microcontroller with on-board hardware supporting the Inter-Integrated Circuit (I<sup>2</sup>C) bus interface.

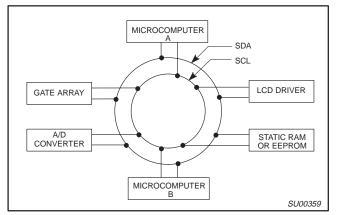

The I<sup>2</sup>C bus, developed and patented by Philips, allows integrated circuits to communicate directly with each other via a simple bidirectional 2-wire bus. The comprehensive family of CMOS and bipolar ICs incorporating the on-chip I<sup>2</sup>C interface offers many advantages to designers of digital control for industrial, consumer and telecommunications equipment. A typical system configuration is shown in Figure 1.

Figure 1. Typical I<sup>2</sup>C Bus Configuration

Interfacing the devices in an I<sup>2</sup>C based system is very simple because they connect directly to the two bus lines: a serial data line (SDA) and a serial clock line (SCL). System design can rapidly progress from block diagram to final schematic, as there is no need to design bus interfaces, and functional blocks on a block diagram correspond to actual ICs. A prototype system or a final product version can easily be modified or upgraded by 'clipping' or 'unclipping' ICs to or from the bus. The simplicity of designing with the I<sup>2</sup>C bus does not reduce its effectiveness; it is a reliable, multimaster bus with integrated addressing and data-transfer protocols (see Figure 2). In addition, the I<sup>2</sup>C-bus compatible ICs provide cost reduction benefits to equipment manufacturers, some of which are smaller IC packages and a minimization of PCB traces and glue logic.

The availability of microcontrollers like the 87LPC76X, with on-board I<sup>2</sup>C interface, is a very powerful tool for system designers. The integrated protocols allow systems to be completely software defined. Software development time of different products can be reduced by assembling a library of reusable software modules. In addition, the multimaster capability allows rapid testing and alignment of end-products via external connections to an assembly-line computer.

The mask programmable 87LPC76X and its EPROM version, the 87LPC76X, can operate as a master or a slave device on the  $I^2C$  small area network. In addition to the efficient interface to the dedicated function ICs in the  $I^2C$  family, the on-board interface facilities I/O and RAM expansion, access to EEPROM and processor-to-processor communications.

The multimaster capability of the I<sup>2</sup>C is very important but many designs do not require it. For many systems, it is sufficient that all communications between devices are initiated by a single, master processor. In this application note, use of the 87LPC76X as an I<sup>2</sup>C bus master is described. Some of the technical features of the bus and the 87LPC76X's special hardware associated with the I<sup>2</sup>C are discussed. Also included is a software example demonstrating I<sup>2</sup>C single master communications. Note that the sample routines are quite general, and therefore may be transferred easily to many applications.

The discussion of the  $I^2C$  bus characteristics in this application note is by no means complete. Additional information for the  $I^2C$  bus and the 87LPC76X Microcontroller can be found in the 80C51 Microcontroller databook.

## THE I<sup>2</sup>C BUS

The two lines of the I<sup>2</sup>C-bus are a serial data line (SDA) and a serial clock line (SCL). Both lines are connected to a positive supply via a pull-up resistor, and remain HIGH when the bus is not busy. Each device is recognized by a unique address—whether it is a microcomputer, LCD driver, memory or keyboard interface—and can operate as either a transmitter or receiver, depending on the function of the device. A device generating a message or data is a transmitter, and a device receiving the message or data is a receiver. Obviously, a passive function like an LCD driver could only be a receiver, while a microcontroller or a memory can both transmit and receive data.

## **Masters and Slaves**

When a data transfer takes place on the bus, a device can either be a master or a slave. The device which initiates the transfer, and generates the clock signals for this transfer, is the master. At that time any device addressed is considered a slave. It is important to note that a master could either be a transmitter or a receiver; a master microcontroller may send data to a RAM acting as a transmitter, and then interrogate the RAM for its contents acting as a receiver—in both cases performing as the master initiating the transfer. In the same manner, a slave could be both a receiver and a transmitter.

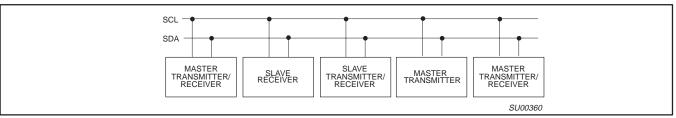

The  $l^2C$  is a multimaster bus. It is possible to have, in one system, more than one device capable of initiating transfers and controlling the bus (Figure 2). A microcontroller may act as a master for one transfer, and then be the slave for another transfer, initiated by another processor on the network. The master/slave relationships on the bus are not permanent, and may change on each transfer.

Figure 2. I<sup>2</sup>C Bus Connection

# AN464

As more than one master may be connected to the bus, it is possible that two devices will try to initiate a transfer at the same time. Obviously, in order to eliminate bus collisions and communications chaos, an arbitration procedure is necessary. The I<sup>2</sup>C design has an inherent arbitration and clock synchronization procedure relying on the wired-AND connection of the devices on the bus. In a typical multimaster system, a microcontroller program should allow it to gracefully switch between master and slave modes and preserve data integrity upon loss of arbitration. In this note, a simple case is presented describing the 87LPC76X operating as a single master on the bus.

#### **Data Transfers**

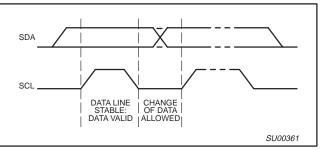

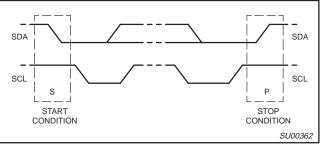

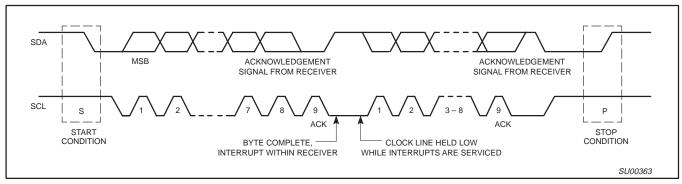

One data bit is transferred during each clock pulse (see Figure 3). The data on the SDA line must remain stable during the HIGH period of the clock pulse in order to be valid. Changes in the data line at this time will be interpreted as control signals. A HIGH-to-LOW transition of the data line (SDA) while the clock signal (SCL) is HIGH indicates a Start condition, and a LOW-to-HIGH transition of the SDA while SCL is HIGH defines a Stop condition (see Figure 4). The bus is considered to be busy after the Start condition and free again at a certain time interval after the Stop condition. The Start and Stop conditions are always generated by the master.

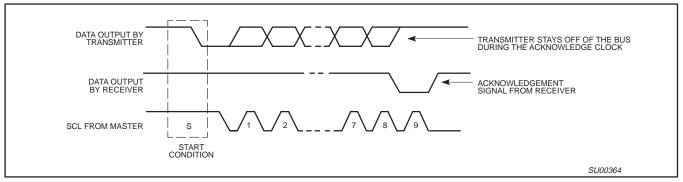

The number of data bytes transferred between the Start and Stop condition from transmitter to receiver is not limited. Each byte, which must be eight bits long, is transferred serially with the most significant bit first, and is followed by an acknowledge bit. (see Figure 5). The clock pulse related to the acknowledge bit is generated by the master. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, while the transmitting device releases the SDA line (HIGH) during this pulse (see Figure 6).

Figure 3. Bit Transfer on the I<sup>2</sup>C Bus

Figure 4. Start and Stop Conditions

Figure 5. Data Transfer on the I<sup>2</sup>C Bus

Figure 6. Acknowledge on the I<sup>2</sup>C Bus

A slave receiver must generate an acknowledge after the reception of each byte, and a master must generate one after the reception of each byte clocked out of the slave transmitter. If a receiving device cannot receive the data byte immediately, it can force the transmitter into a wait state by holding the clock line (SCL) LOW. When designing a system, it is necessary to take into account cases when acknowledge is not received. This happens, for example, when the addressed device is busy in a real time operation. In such a case the master, after an appropriate "time-out", should abort the transfer by generating a Stop condition, allowing other transfers to take place. These "other transfers" could be initiated by other masters in a multimaster system, or by this same master.

There are two exceptions to the "acknowledge after every byte" rule. The first occurs when a master is a receiver: it must signal an end of data to the transmitter by NOT signalling an acknowledge on the last byte that has been clocked out of the slave. The acknowledge related clock, generated by the master should still take place, but the SDA line will not be pulled down. In order to indicate that this is an active and intentional lack of acknowledgement, we shall term this special condition as a "negative acknowledge".

The second exception is that a slave will send a negative acknowledge when it can no longer accept additional data bytes. This occurs after an attempted transfer that cannot be accepted.

The bus design includes special provisions for interfacing to microprocessors which implement all of the  $I^2C$  communications in software only—it is called "Slow Mode". When all of the devices on the network have built-in  $I^2C$  hardware support, the Slow Mode is irrelevant.

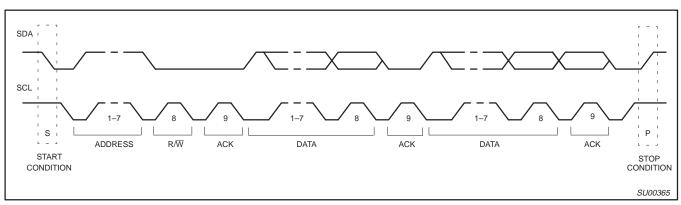

#### Addressing and Transfer Formats

Each device on the bus has its own unique address. Before any data is transmitted on the bus, the master transmits on the bus the address of the slave to be accessed for this transaction. A well-behaved slave with a matching address, if it exists on the network, should of course acknowledge the master's addressing. The addressing is done by the first byte transmitted by the master after the Start condition.

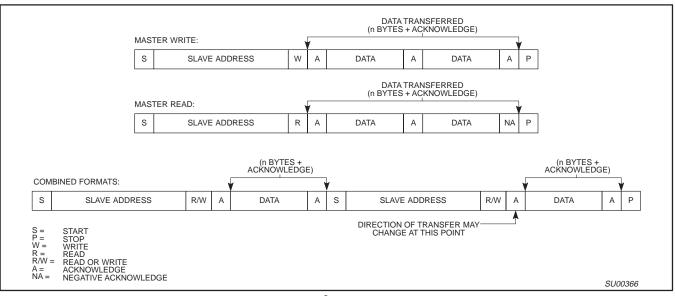

An address on the network is seven bits long, appearing as the most significant bits of the address byte. The last bit is a direction (R/W) bit. A zero indicates that the master is transmitting (WRITE) and a one indicates that the master requests data (READ). A complete data

transfer, comprised of an address byte indicating a WRITE and two data bytes is shown in Figure 7.

When an address is sent, each device in the system compares the first seven bits after the Start with its own address. If there is a match, the device will consider itself addressed by the master, and will send an acknowledge. The device could also determine if in this transaction it is assigned the role of a slave receiver or slave transmitter, depending on the R/W bit.

Each node of the I<sup>2</sup>C network has a unique seven bit address. The address of a microcontroller is of course fully programmable, while peripheral devices usually have fixed and programmable address portions. In addition to the "standard" addressing discussed here, the I<sup>2</sup>C bus protocol allows for "general call" addressing and interfacing to CBUS devices.

When the master is communicating with one device only, data transfers follow the format of Figure 7, where the R/W bit could indicate either direction. After completing the transfer and issuing a Stop condition, if a master would like to address some other device on the network, it could of course start another transaction, issuing a new Start.

Another way for a master to communicate with several different devices would be by using a "repeated start". After the last byte of the transaction was transferred, including its acknowledge (or negative acknowledge), the master issues another Start, followed by address byte and data—without effecting a Stop. The master may communicate with a number of different devices, combining READS and WRITES. After the last transfer takes place, the master issues a Stop and releases the bus. Possible data formats are demonstrated in Figure 8. Note that the repeated start allows for both change of a slave and a change of direction, without releasing the bus. We shall see later on that the change of direction feature can come in handy even when dealing with a single device.

In a single master system, the repeated start mechanism may be more efficient than terminating each transfer with a Stop and starting again. In a multimaster environment, the determination of which format is more efficient could be more complicated, as when a master is using repeated starts it occupies the bus for a long time and thus preventing other devices from initiating transfers.

Figure 7. A Complete Data Transfer on the I<sup>2</sup>C-Bus

Figure 8. I<sup>2</sup>C Data Formats

Figure 9. I<sup>2</sup>C Sub-Address Usage

#### Use of Sub-Addresses

For some ICs on the I<sup>2</sup>C bus, the device address alone is not sufficient for effective communications, and a mechanism for addressing the internals of the device is necessary. A typical example when we want to access a specific word inside the device is addressing memories, or a sequence of memory locations starting at a specific internal address.

A typical I<sup>2</sup>C memory device like the PCF8570 RAM contains a built-in word address register that is incremented automatically after each data byte which is a read or written data byte. When a master communicates with the PCF8570 it must send a sub-address in the byte following the slave address byte. This sub-address is the internal address of the word the master wants to access for a single byte transfer, or the beginning of a sequence of locations for a multi-byte transfer. A sub-address is an 8-bit byte, unlike the device address, it does not contain a direction (R/W) bit, and like any byte transferred on the bus it must be followed by an acknowledge.

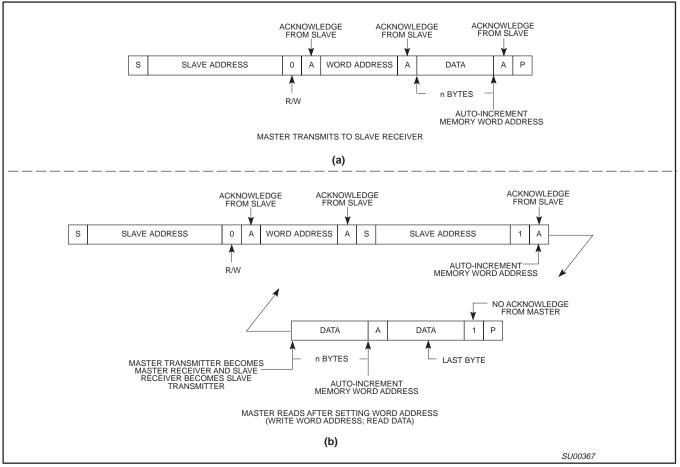

A memory write cycle is shown in Figure 9(a). The Start is followed by a slave byte with the direction bit set to WRITE, a sub-address byte, a number of data bytes and a Stop signal. The sub-address is loaded into the word address memory, and the data bytes which follow will be written one after the other starting with the sub-address location, as the register is incremented automatically.

The memory read cycle (see Figure 9(b)) commences in a similar manner, with the master sending a slave address with the direction bit set to WRITE with a following sub-address. Then, in order to reverse the direction of the transfer, the master issues a repeated Start followed again by the memory device address, but this time with the direction bit set to READ. The data bytes starting at the internal sub-address will be clocked out of the device, each followed by a master-generated acknowledge. The last byte of the read cycle will be followed by a negative acknowledge, signalling the end of transfer. The cycle is terminated by a Stop signal.

## 87LPC76X I<sup>2</sup>C HARDWARE

The on-chip I<sup>2</sup>C bus hardware support of the 87LPC76X allows operation on the bus at full speed, and simplifies the software needed for effective communications on the network. The hardware activates and monitors the SDA and SCL lines, performs the necessary arbitration and framing errors checks, and takes care of clock stretching and synchronization. The hardware support includes a bus time-out timer, called Timer I. The hardware is synchronized to the software either through polled loops or interrupts.

Two of the port 0 pins are multi-functional. When the  $I^2C$  is active, the pin associated with P0.0 functions as SCL, and the pin associated with P0.1 functions as SDA. These pins have an open drain output.

Two of the five 87LPC76X interrupt sources may be used for  $I^2C$  support. The  $I^2C$  interrupt is enabled by the El2 flag of the interrupt enable register, and its service routine should start at address 023h. An  $I^2C$  interrupt is usually requested (if enabled) when a rising edge of SCL indicates a new data bit on the bus, or a special condition occurs: Start, Stop or arbitration loss. The interrupt is induced by the ATN flag—see below for the conditions for setting this flag. The Timer I overflow interrupt is enabled by the ETI flag, and the service routine starts at 01Bh.

The I<sup>2</sup>C port is controlled through three special function registers: I<sup>2</sup>C Control (I2CON), I<sup>2</sup>C Configuration (I2CFG), and I<sup>2</sup>C Data (I2DAT). The register addresses are shown in Table 1.

Although the following discussion of the hardware and register details is not complete, it should give a better understanding of the programming examples.

#### Timer I

In I<sup>2</sup>C applications, Timer I is dedicated to the port timing generation and bus monitoring. In non-I<sup>2</sup>C applications, it is available for use as a fixed time base.

In its port timing generation function, Timer I is used to generate SCL, the I<sup>2</sup>C clock. Timer I is clocked once per machine cycle (osc/12), so that the toggle rate of SCL will be some multiple of that rate. Because the 87LPC76X can be run over a wide range of oscillator frequencies, it is necessary to adjust SCL for the part's oscillator frequency. This allows the I<sup>2</sup>C bus to be used at its highest transfer rates independent of the oscillator frequency. SCL is adjusted by writing to two bits (CT0 and CT1) in the I2CFG special function register (see Table 2). The inverse of the values in CT0 and CT1 are loaded into the least significant two bit locations of Timer I every time the fourth bit of the timer is toggled. (A value is actually loaded into the least significant three bits, the third bit being 0 unless both CT0 and CT1 are programmed high and in that case the third bit is 1). SCL is then toggled every time the fourth bit of Timer I is toggled. For example: if CT1 = 0 and CT0 = 1 then the least significant three bits of Timer I would be preloaded with 2 (010 binary). Timer I would then count 3, 4, 5, 6, 7, 8 (6 counts or machine cycles). On 8, the fourth bit of Timer I will toggle, SCL will toggle and the 3 least significant bits will again be preloaded with the value 2 (010).

Table 1. I<sup>2</sup>C Special Function Register Addresses

| R                              | BIT ADDRESS |         |     |    |    |    |    |    |    |     |

|--------------------------------|-------------|---------|-----|----|----|----|----|----|----|-----|

| Name                           | Symbol      | Address | MSB |    |    |    |    |    |    | LSB |

| I <sup>2</sup> C Control       | I2CON       | D8      | DF  | DE | DD | DC | DB | DA | D9 | D8  |

| I <sup>2</sup> C Data          | I2DAT       | D9      | -   | -  | -  | -  | -  | -  | -  | -   |

| I <sup>2</sup> C Configuration | I2CFG       | C8      | CF  | CE | CD | CC | СВ | CA | C9 | C8  |

## Table 2. CT1, CT0 Values

| СТ1, СТ0 | Min Time Count<br>(Machine Cycles) | CPU Clock Max<br>(for 100 kHz I <sup>2</sup> C) | Timeout Period<br>(Machine Cycles) |

|----------|------------------------------------|-------------------------------------------------|------------------------------------|

| 1 0      | 7                                  | 8.4 MHz                                         | 1023                               |

| 0 1      | 6                                  | 7.2 MHz                                         | 1022                               |

| 0 0      | 5                                  | 6.0 MHz                                         | 1021                               |

| 1 1      | 4                                  | 4.8 MHz                                         | 1020                               |

AN464

For the bus monitoring function, Timer I is used as a "watchdog timer" for bus hang-ups. It creates an interrupt when the SCL line stays in one state for an extended period of time while the bus is active (between a Start condition and a following Stop condition). SCL "stuck low" indicates a faulty master or slave. SCL "stuck high" may mean a faulty device, or that noise induced unto the I<sup>2</sup>C caused all masters to withdraw from the I<sup>2</sup>C arbitration.

The time-out interval of Timer I is fixed (cannot be set): it carries out and interrupts (if enabled) when about 1024 machine cycles have elapsed since a change on SCL within a frame. In other words, whenever I<sup>2</sup>C is active and Timer I is enabled, the falling edge of SCL will reset Timer I. If SCL is not toggled low for 1024 machine cycles, Timer I will overflow and cause an interrupt. (Note: we wrote "about 1024 machine cycles" although for the sake of accuracy-this number is affected by the setting of the CT0 and CT1 bits mentioned above and may vary by up to three machine cycles) The exact number of cycles for a time-out is not critical; what is important is that it indicates SCL is stuck.

In addition to the interrupt, upon Timer I overflow the I<sup>2</sup>C port hardware is reset. This is useful for multiple master systems in situations where a bus fault might cause the bus to hang-up due to a lack of software response. When this happens, SCL will be released, and I<sup>2</sup>C operation between other devices can continue.

## **I2CON Register**

The I<sup>2</sup>C control register (I2CON) can be written to (see Figure 10). When writing to the I2CON register, one should use bit masks as demonstrated in the example program. Trying to clear or set the bits in the register using the bit addressing capabilities of the 87LPC76X may lead to undesirable results. The reason is that a command like CLR reads the register, sets the bit and writes it back, and the write-back may affect other bits.

## **I2CFG Register**

The configuration register (I2CFG) is a read/write register (see Figure 11).

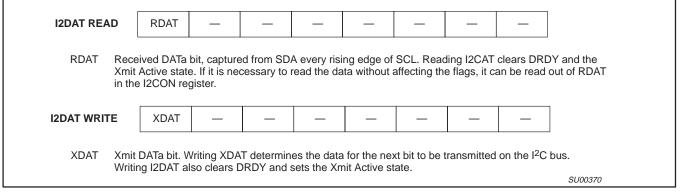

## **I2DAT Register**

The I<sup>2</sup>C data register (I2DAT) is a read/write register, where the MSB represents the data received or data to be sent. The other seven bits are read as 0 (see Figure 12).

## **Transmit Active State**

The transmit active state—Xmit Active—is an internal state in the I<sup>2</sup>C interface that is affected by the I<sup>2</sup>C registers as explained above. The I<sup>2</sup>C interface will only drive the SDA line low when Xmit Active is set. Xmit Active is set by writing the I2DAT register, or by writing I2CON with XSTR = 1 or XSTP = 1. The ARL bit will be set to 1 only when Xmit Active is set-in such a case Xmit Active will be automatically reset upon arbitration loss. Xmit Active is cleared by writing 1 to CXA at I2CON register or by reading the I2DAT register.

| I2CON REA  | D                                | RDAT                                                                                                                                                                                                                                                            | ATN         | DRDY         | ARL          | STR            | STP           | MASTER      |              |                                           |

|------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|--------------|----------------|---------------|-------------|--------------|-------------------------------------------|

| RDAT       |                                  |                                                                                                                                                                                                                                                                 |             |              |              |                |               |             |              | cal to RDAT in the eleasing SCL.          |

| ATN        |                                  | An "ATteNtion" flag, set when any one of DRDY, ARL, STR or STP is set. This flag allows a single bit testing for terminating "wait loops", indicating a meaningful event on the bus. This flag also activates the I <sup>2</sup> C interrupt request.           |             |              |              |                |               |             |              |                                           |

| DRDY       |                                  |                                                                                                                                                                                                                                                                 |             |              |              |                |               |             |              | is flag is cleared by<br>CON is written). |

| ARL        | ARbi                             | tration Loss                                                                                                                                                                                                                                                    | flag. Indic | ates that th | is device lo | ost arbitratio | on while try  | ing to take | control of t | he bus.                                   |

| STR        | STaR                             | t flag. Set v                                                                                                                                                                                                                                                   | when a Sta  | rt condition | is detected  | d, except a    | t an idle sla | ave.        |              |                                           |

| STP        | SToP                             | flag. Set w                                                                                                                                                                                                                                                     | hen a Stop  | o condition  | is detected  | , except at    | an idle sla   | ve.         |              |                                           |

| MASTER     | This f                           | This flag is set when the controller is a bus master (or a potential master, prior to arbitration).                                                                                                                                                             |             |              |              |                |               |             |              |                                           |

| I2CON WRIT | ΓE                               | СХА                                                                                                                                                                                                                                                             | IDLE        | CDR          | CARL         | CSTR           | CSTP          | XSTR        | XSTP         | ]                                         |

|            |                                  | _                                                                                                                                                                                                                                                               |             | _            |              |                |               | _           | _            |                                           |

| CXA        | "Clea                            | "Clear Xmit Active". Writing a 1 to CXA clears the internal transmit-active state.                                                                                                                                                                              |             |              |              |                |               |             |              |                                           |

| IDLE       |                                  | Setting this bit will cause a slave to enter idle mode and ignore the I <sup>2</sup> C bus until the next Start is detected. If the software sets the MASTRQ flag, the device may stop idling by turning into a master.                                         |             |              |              |                |               |             |              |                                           |

| CDR        | Clear                            | Clear Data Ready. Clears the DRDY flag.                                                                                                                                                                                                                         |             |              |              |                |               |             |              |                                           |

| CARL       | Clear                            | r Arbitration                                                                                                                                                                                                                                                   | Lost. Clea  | irs the ARL  | flag.        |                |               |             |              |                                           |

| CSTR       | Clear                            | STaRt. Cle                                                                                                                                                                                                                                                      | ears the ST | R flag.      |              |                |               |             |              |                                           |

| CSTP       | Clear STop. Clears the STP flag. |                                                                                                                                                                                                                                                                 |             |              |              |                |               |             |              |                                           |

| 0319       | Cieai                            | Clear STop. Clears the STP flag.<br>"Xmit repeated STaRt". Writing a 1 to this bit causes the hardware to issue a Repeated Start signal. A side effect<br>will be setting the internal Xmit Active state. This should be used only when the device is a master. |             |              |              |                |               |             |              |                                           |

| XSTR       | "Xmit                            | repeated S                                                                                                                                                                                                                                                      |             |              |              |                |               |             |              |                                           |

Figure 10. I2CON Register

# AN464

|          | SLAVEN                                                                                                                                                                                                                                  | MASTRQ                                                          | CLRTI       | TIRUN     | —                         | —          | CT1 | СТ0 |    |       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------|-----------|---------------------------|------------|-----|-----|----|-------|

| SLAVEN   | Writing a 1 to this                                                                                                                                                                                                                     | s flag enables                                                  | s the slave | functions | of the I <sup>2</sup> C i | interface. |     |     |    |       |

| MASTRQ   | Request control                                                                                                                                                                                                                         | of the bus as                                                   | a master.   |           |                           |            |     |     |    |       |

| CLRTI    | Clear the Timer I                                                                                                                                                                                                                       | Clear the Timer I interrupt flag. This bit is always read as 0. |             |           |                           |            |     |     |    |       |

| TIRUN    | Writing a 1 will let Timer I run. When I <sup>2</sup> C is active, it will run only inside frames, and will be cleared by SCL transitions, Start and Stop. Writing a 0 will stop and clear the timer.                                   |                                                                 |             |           |                           |            |     |     |    |       |

| CT1, CT0 | These bits should be programmed according to the frequency of the crystal oscillator used in the hardware. They determine the minimum high and low times for SCL, and are used to optimized performance at different oscillator speeds. |                                                                 |             |           |                           |            |     |     |    |       |

|          |                                                                                                                                                                                                                                         |                                                                 |             |           |                           |            |     |     | SL | 10036 |

#### Figure 12. I2DAT Register

#### **PROGRAMMING EXAMPLE**

The listing demonstrates communications routines for the 87LPC76X as an I<sup>2</sup>C bus master in a single-master system.

The single-master system is less complicated than a multimaster environment. The programmer does not have to worry about switching between master and slave roles, or the consequences of an arbitration loss.

The I<sup>2</sup>C interrupt is not used, and therefore disabled. There is no need for frame Start interrupts, as this processor is the only bus master and all data transfers are initiated by it when the appropriate routines are called by the application. No one else generates frame Starts which could be an interrupt source in a multimaster system. Within the frames we monitor bus activity with a wait-loop which polls the ATN flag. As we expect the bus to operate in its full-speed mode, we can assume that only a small amount of time will be wasted in those loops, and the use of interrupts would be less efficient.

The 87LPC76X has single-bit I<sup>2</sup>C hardware interface, where the registers may directly affect the levels on the bus and the software interacting with the register takes part in the protocol implementation. The hardware and the low-level routines dealing with the registers are tightly coupled. Therefore, one should take extra care if trying to modify these lower level routines.

The beginning of the program, at address 0, contains the reset vector, where the microcontroller begins executing code after a hardware reset. In this case, the code simply jumps to the main part of the program, which begins at the label 'Reset' near the end of the listing.

The main program is a simple demonstration of the I<sup>2</sup>C routines which comprise the balance of the listing. It first enables the Timer I interrupt,

and sets up parameters in order to read data from a slave device. In this example, the slave device is a PCF8574A 8-bit I/O port that has pushbuttons connected to bits 3:0, and LEDs connected to bits 7:4. The program causes the I/O port data to be read by calling the "RcvData" routine. Once the data byte from the PCF8574A has been read, the pushbutton data is saved and copied to the LED bit position and the switch data set high. The program then prepares to write this new value to the PCF8574A I/O port, and performs the write operation by calling the "SendData" routine. The SendData and RcvData routines can send or receive multiple bytes of data, the number of which is determined by the variable 'ByteCnt'.

Upon return from both SendData and RcvData, the program checks the system flag named 'Retry' to see if the transfer was completed correctly. If not, it loops back and attempts the same transfer again.

This entire process is repeated indefinitely by jumping back to MainLoop.

Back at the beginning of the program, the next location after the reset vector is the Timer I interrupt service routine. The microcontroller will go to address 73 hexadecimal if Timer I overflows. This routine stops the timer, clears the timer interrupt, clears the pending interrupt so that other interrupts will be enabled, restores the stack pointer, and jumps to the 'Recover' routine to try to correct whatever stopped the I<sup>2</sup>C bus and allowed Timer I to overflow.

Next in the listing come the main  $l^2C$  service routines. These are the routines SendData, RcvData, SendSub, and RcvSub that were called from the main program. Both of the send routines use the data area labeled 'XmtDat' as the transmit data buffer. In this sample program, four bytes were reserved for this area, but it could be larger or

smaller depending on the application. The two receive routines use another four byte buffer labeled 'RcvDat' to store received data. All of these routines use the variables 'SlvAdr' and 'ByteCnt' to determine the slave address and the number of bytes to be sent or received, respectively. The SendSub and RcvSub routines use the variable 'SubAdr' as the sub-address to send to the slave device.

Following the main  $l^2C$  service routines in the listing are the subroutines that are called by the main routines to deal intimately with the  $l^2C$  hardware.

The 'SendAddr' subroutine requests mastership of the  $I^2C$  bus and calls the routine 'XmitAddr' to complete sending the slave address. The bulk of the XmitAddr routine is shared with the 'XmitByte' subroutine which sends data bytes on the  $I^2C$  bus. XmitByte is also used to send  $I^2C$  sub-addresses. Both subroutines check for an acknowledge from the slave device after every byte is sent on the  $I^2C$  bus.

The next subroutine 'RDAck' calls the 'RcvByte' routine to read in a byte of data. It then sends an acknowledge to the slave device. RDAck is used to receive all data except for the last byte of a receive data frame, where the acknowledge is omitted by the bus master. The RcvByte subroutine is called directly for the last byte of a frame.

The 'SendStop' subroutine causes a stop condition on the  $I^2C$ , thus ending a frame. The 'RepStart' subroutine sends a repeated start condition on the  $I^2C$  bus, to allow the master to start a new frame without first having to send an intervening stop.

The lower level subroutines deal directly with the hardware. The tight coupling between hardware and software is best demonstrated by the following explanations, relating to two cases in which the code is not self evident.

## Sending the Address

When sending the address byte in the Send Addr subroutine, the first bit is written to I2DAT prior to the loop where the other seven bits are

sent (SendAd2). The reason is that we need to clear the Start condition in order to release the SCL line, and this is done explicitly by the subsequent command. When SCL is released, the correct bit (MSB of address) must already be in I2DAT.

### **Capturing the Received Data**

Typically, a program receiving data waits in a loop for ATN, and when detected, checks DRDY. If DRDY = 1 then there was a rising SCL, and the new data can be read from RDAT in I2CON or I2DAT. Reading or writing I2DAT clears DRDY, thus releasing SCL.

When reading the last bit in a byte, it should be read from I2CON, and not I2DAT (see the end of the RcvByte routine). This way the Data Ready (DRDY) flag is not cleared, and the low period on SCL is stretched. The reason for doing so is that upon reception of the last bit of a received byte the master must react with an acknowledge. In order to ensure that we "wait" with the acknowledge clock (release of SCL) until the acknowledge level is issued on SDA, the last bit is read out of I2CON and not I2DAT. SCL is stretched low until the acknowledge level is written into I2DAT by the software.

#### **Bus Faults and Other Exceptions**

Bus exceptions are detected either by Timer I time-out, or "illegal" logic states tested for and detected by the software. Upon Timer I time-out, a bus recovery is attempted by the Recover routine. The final section of the listing is this 'Recover' routine. Its job is to try to restore control of the I<sup>2</sup>C bus to the main program. First, the subroutine 'FixBus' is called. It checks to see if only the SDA line is 'stuck', and if so, tries to correct it by sending some extra clocks on the SCL line, and forcing a stop condition on the bus. If this does not work, another subroutine 'BusReset' is called. This generally happens when a severe bus error occurs, such as a shorted clock line. The philosophy used in this code is that the only chance of recovering from a severe error is to cause a reset of the I<sup>1</sup>C hardware by deliberately forcing Timer I to time out. This method allows recovery from a temporary short or other serious condition on the I<sup>2</sup>C bus.

## AN464

```

I2C Single Master Routines for the 87LPC764

; Modified from code published for the 8xC751/752 in AN422. This program

; reads an I2C slave device using subaddressing, alters the data, and

; returns it to the same slave.

; Notes on 87LPC764 I2C differences:

- I2C interrupt vector address.

;

- Timer I interrupt vector address.

;

- IEN0 SFR name (IE on 751) and addition of IEN1.

- I2C interrupt enable location (now in IEN1 and a different bit).

- Timer I interrupt enable location (now in IEN1 and a different bit).

;

;

- I2C SFR addresses (altered by inclusion of the MOD764 file).

SDEBUG

$MOD764

; I2C Demo Board I2C Addresses

LCD

74h

; PCF8577 LCD display.

equ

LED7

76h

; SAA1064 LED display.

equ

RTCLK

0A2h

; PCF8583 clock calendar.

equ

RAM

0AEh

; PCF8570 256 byte RAM.

equ

0A6h

EEPROM equ

; PCF8582 256 byte EEPROM.

; PCD3312 DTMF generator.

DTMF

4Ah

equ

PIO

4Eh

; PCF8574 8-bit I/O port.

equ

KEYLED

7Eh

; PCF8574A that runs the discrete LEDs & keypad.

equ

09Eh

; PCF8591 A/D and DAC.

ADDAC

equ

; Value definitions.

CTVAL

02h

; CT1, CT0 bit values for I2C.

equ

; Masks for I2CFG bits.

BTIR

10h

; mask for TIRUN bit.

equ

BMRQ

equ

40h

; mask for MASTRQ bit.

; Masks for I2CON bits.

BCXA

equ

80h

; mask for CXA bit.

40h

; mask for IDLE bit.

BIDLE

equ

BCDR

20h

; mask for CDR bit.

equ

BCARL

equ

10h

; mask for CARL bit.

BCSTR

08h

; mask for CSTR bit.

equ

BCSTP

equ

04h

; mask for CSTP bit.

; mask for XSTR bit.

BXSTR

02h

equ

BXSTP

01h

; mask for XSTP bit.

equ

; RAM locations used by I2C routines.

bitCnt data 21h

; I2C bit counter.

ByteCnt data

2.2h

SlvAdr data

23h

; address of active slave.

SubAdr data 24h

; I2C receive data buffer (4 bytes).

RcvDat

data 25h

addresses 25h through 28h.

```

;

| XmtDat                                                                      | data                                                                                                                                                     | 29h ;<br>;                                                                                                                                                                                                                                                             | I2C transmit data buffer (4 bytes).<br>addresses 29h through 2Ch.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| StackSave                                                                   | data                                                                                                                                                     | 2Dh ;                                                                                                                                                                                                                                                                  | saves stack address for bus recovery.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Flags<br>NoAck<br>Fault<br>retry                                            |                                                                                                                                                          | Flags.0 ;<br>Flags.1 ;                                                                                                                                                                                                                                                 | I2C software status flags.<br>indicates missing acknowledge.<br>indicates a bus fault of some kind.<br>indicates that last I2C transmission<br>failed and should be repeated.                                                                                                                                                                                                                                                                                                            |

| ; * * * * * * * * *                                                         | * * * * * * *                                                                                                                                            | * * * * * * * * * * * * * * * * * * * *                                                                                                                                                                                                                                | *****                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ;<br>; * * * * * * * * *                                                    | * * * * * * *                                                                                                                                            | * * * * * * * * * * * * * * * *                                                                                                                                                                                                                                        | Begin Code<br>************************************                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ; Reset ar                                                                  | nd inter                                                                                                                                                 | crupt vectors                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | org                                                                                                                                                      | 0000h                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | ajmp                                                                                                                                                     | Reset                                                                                                                                                                                                                                                                  | ; reset vector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | orq                                                                                                                                                      | 0073h                                                                                                                                                                                                                                                                  | ; Timer I interrupt address.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TimerI:                                                                     | setb                                                                                                                                                     | CLRTI                                                                                                                                                                                                                                                                  | ; Clear timer I interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                             | clr                                                                                                                                                      | TIRUN                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | acall                                                                                                                                                    | ClrInt                                                                                                                                                                                                                                                                 | ; Clear interrupt pending.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                             | mov                                                                                                                                                      |                                                                                                                                                                                                                                                                        | ; Restore stack for return to main.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                             | ajmp                                                                                                                                                     | Recover                                                                                                                                                                                                                                                                | ; Attempt bus recovery.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ClrInt:                                                                     | reti                                                                                                                                                     |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             |                                                                                                                                                          |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | org                                                                                                                                                      | 0100h                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | org                                                                                                                                                      | 010011                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             |                                                                                                                                                          |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             |                                                                                                                                                          |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ; * * * * * * * * *                                                         | * * * * * * *                                                                                                                                            | *****                                                                                                                                                                                                                                                                  | ***************                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ;                                                                           |                                                                                                                                                          | Main Trans                                                                                                                                                                                                                                                             | mit and Receive Routines                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ;                                                                           |                                                                                                                                                          | Main Trans                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ;<br>;<br>;*******                                                          | * * * * * * *                                                                                                                                            | Main Trans                                                                                                                                                                                                                                                             | mit and Receive Routines                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ;<br>;<br>; *********<br>; Send dat                                         | *******<br>a byte                                                                                                                                        | Main Trans                                                                                                                                                                                                                                                             | mit and Receive Routines<br>************************************                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ;<br>;**********<br>; Send dat<br>; Enter                                   | a byte<br>with s                                                                                                                                         | Main Trans<br>******************<br>(s) to slave.<br>lave address in                                                                                                                                                                                                   | mit and Receive Routines                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ;<br>;**********<br>; Send dat<br>; Enter                                   | a byte<br>with s                                                                                                                                         | Main Trans                                                                                                                                                                                                                                                             | mit and Receive Routines<br>************************************                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ;<br>;**********<br>; Send dat<br>; Enter                                   | a byte<br>with s                                                                                                                                         | Main Trans<br>******************<br>(s) to slave.<br>lave address in                                                                                                                                                                                                   | mit and Receive Routines<br>************************************                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ;<br>;*********<br>; Send dat<br>; Enter<br>; bytes                         | a byte<br>with si                                                                                                                                        | Main Trans<br>******************<br>(s) to slave.<br>lave address in                                                                                                                                                                                                   | mit and Receive Routines<br>************************************                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ;<br>;*********<br>; Send dat<br>; Enter<br>; bytes                         | a byte<br>with s<br>to send                                                                                                                              | Main Trans<br>************************************                                                                                                                                                                                                                     | mit and Receive Routines<br>************************************                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ;<br>;*********<br>; Send dat<br>; Enter<br>; bytes                         | a byte<br>with site send<br>clr                                                                                                                          | Main Trans<br>************************************                                                                                                                                                                                                                     | mit and Receive Routines<br>************************************                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ;<br>;*********<br>; Send dat<br>; Enter<br>; bytes                         | clr<br>clr                                                                                                                                               | Main Trans<br>(s) to slave.<br>lave address in<br>d in ByteCnt.<br>NoAck<br>Fault                                                                                                                                                                                      | mit and Receive Routines<br>************************************                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ;<br>;*********<br>; Send dat<br>; Enter<br>; bytes                         | clr<br>clr                                                                                                                                               | Main Trans<br>************************************                                                                                                                                                                                                                     | mit and Receive Routines<br>************************************                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ;<br>;*********<br>; Send dat<br>; Enter<br>; bytes                         | a byte<br>with si<br>to send<br>clr<br>clr<br>clr<br>mov                                                                                                 | Main Trans<br>(s) to slave.<br>lave address in<br>d in ByteCnt.<br>NoAck<br>Fault<br>retry<br>StackSave,SP<br>A,SlvAdr<br>SendAddr                                                                                                                                     | <pre>mit and Receive Routines ************************************</pre>                                                                                                                                                                                                                                                                                                                                                                                                                 |