AN430

#### INTRODUCTION

The Philips Semiconductors 83C751/87C751 offers the advantages of the 80C51 architecture in a small package and at a low cost. It combines the benefits of a high performance microcontroller with on-board hardware supporting the Inter Integrated Circuit (I<sup>2</sup>C) bus interface.

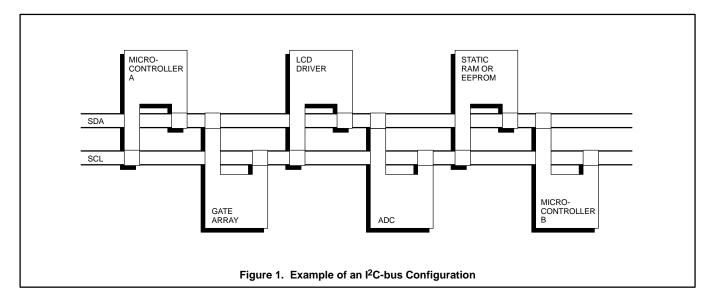

The Inter IC ( $I^2C$ ) bus developed by Philips allows integrated circuits to communicate directly with each other via a simple bidirectional 2-wire bus. The comprehensive family of CMOS and bipolar ICs incorporating the on-chip  $I^2C$  interface offers many advantages to designers of digital control for industrial, consumer and telecommunications equipment.

Interfacing the devices in an I<sup>2</sup>C based system is very simple as they connect directly to the two bus lines: a serial data line (SDA) and a serial clock line (SCL). System design can rapidly progress from block diagram to final schematics, as there is no need to design bus interfaces. In addition, functional blocks on the block diagram correspond to actual ICs. A prototype system or a final product version can be easily modified or upgraded by 'clipping' or 'unclipping' ICs to or from the bus. The simplicity of designing with the I<sup>2</sup>C bus does not reduce its effectiveness: it is a reliable, multimaster bus with integrated addressing and data-transfer protocols. The I<sup>2</sup>C-bus compatible ICs give cost reduction benefits through smaller IC packages and a minimization of PCB traces and glue logic.

The availability of microcontrollers, like the 83C751, with on-board I<sup>2</sup>C interface is a very powerful tool for system designers. The integrated protocols allow systems to be completely software defined. Software development time of different products can be reduced by assembling a library of re-usable software modules. In addition, the multimaster capability allows rapid testing and alignment of end-products via external connections to an assembly-line computer.

The mask programmable 83C751 and its EPROM version, 87C751, can operate as a master or a slave device on the  $l^2$ C small area network. In addition to the efficient interface to the dedicated function ICs in the  $l^2$ C family the on-board interface facilitates I/O and RAM expansion, access to EEPROM, and processor-to-processor communications.

The 83C752 and its EPROM version, 87C752, are essentially the 83C751/87C751 with the addition of a five channel multiplexed 8-bit A/D converter and an 8-bit PWM output. As the I<sup>2</sup>C bus interface is identical, the programming example and the discussion relates to both processors. The multimaster capability of the I<sup>2</sup>C bus allows easy integration and expansion of relatively complex systems, in which different devices can independently initiate data transfers. Integration of a multimaster system is easy as a Master on the bus does not have to coordinate its data transfer with other potential Master devices-arbitration and synchronization are taken care of by the

hardware and bus protocols. Expanding a system with a new device is trivial—it is "clipped" onto the two serial bus lines, and the new device may act as a Master without any modification to the other devices (see Figure 1). Microcontrollers like the S8XC751/752 on the I<sup>2</sup>C bus are extremely powerful, as they can be programmed to be both Masters and Slaves in the same system. This way the microcontroller may initiate communication on the bus, and when requested, will respond to a data transfer request by another device.

In this Application Note we shall discuss the most important technical features of the I<sup>2</sup>C bus and describe the special I<sup>2</sup>C hardware interface of the 8XC751/752. We shall demonstrate with an example how the microcontroller can be programmed for a multimaster environment. The communications routines of the example are quite general, and can be ported to many applications—so we shall discuss in detail the software interface to these routines.

The description of the 8XC751  $I^2C$  interface hardware and part of the general discussion of the  $I^2C$  bus is similar to Application Note AN422 which dealt with the microcontroller in a single-master environment. Most of the added discussions relate to the multimaster aspects of the bus. Additional information for the  $I^2C$  bus and the 83C751/752 Microcontroller can be found in the Philips Semiconductors Microcontroller Data Handbook (IC20).

AN430

### Using the 8XC751/752 in multimaster I<sup>2</sup>C applications

#### THE I<sup>2</sup>C BUS

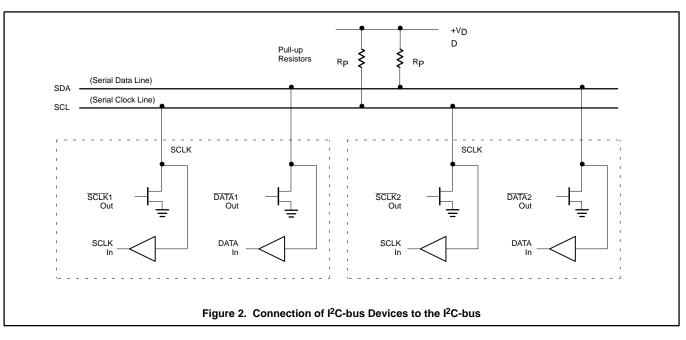

The two lines of the I<sup>2</sup>C bus are a serial data line (SDA) and a serial clock line (SCL). A typical system configuration is shown in Figure 2. Each device is recognized by a unique address—whether it is a microcomputer, LCD driver, memory or keyboard interface—and can operate as either a transmitter or a receiver, depending on the function of the device. A device generating a message or data is a transmitter, and a device receiving the message or data is a receiver. Obviously, a passive function like an LCD driver could only be a receiver, while a microcontroller or a memory can both transmit and receive data.

Every device connected to the bus must have an open-drain or an open-collector output for both the data (SDA) and the clock (SCL) lines. Each one of the lines is connected to the positive supply via a common pull-up resistor (see Figure 2). This implements a wired-AND function, and each of the bus lines which will have the HIGH level only if all the output transistors tied to it are switched off.

Data on the I<sup>2</sup>C bus can be transferred at a rate up to 100kbit/s. The number of devices connected to the bus is limited only by the maximum bus capacitance of 400pF. As different technology devices can be connected to the I<sup>2</sup>C bus, the levels of the logical 0 (Low) and logical 1 (High) are not fixed and depend on the appropriate level of V<sub>DD</sub>.

#### MASTERS AND SLAVES

When a data transfer takes place on the bus, a device can be either a master or a slave. The device which initiates the transfer, and generates the clock signals for this transfer is the master. At that time any device addressed is considered a slave. It is important to note that a master could be either a transmitter or a receiver: a master microcontroller may send data to a RAM acting as a transmitter, and then interrogate the RAM for its contents acting as a receiver—in both cases being the master initiating the transfer. In the same manner, a slave could be both a receiver and a transmitter.

The I<sup>2</sup>C is a multimaster bus. It is possible to have in one system more than one device capable of initiating transfers and controlling the bus. A microcontroller may act as a master for one transfer, and then be the slave for another transfer, initiated by another processor on the network. The master/slave relationships on the bus are not permanent, and exist per transfer.

As more than one master may be connected to the bus it is possible that two devices will try to initiate transfer at the same time. Obviously, in order to eliminate bus collisions and communications chaos, an arbitration procedure is necessary. The  $I^2C$  design has an inherent arbitration and clock synchronization procedure relying on the wired-AND connection of the devices on the bus. In a typical multimaster system, a microcontroller program should allow it to gracefully switch between master and slave modes and preserve data integrity upon loss of arbitration.

#### DATA TRANSFERS

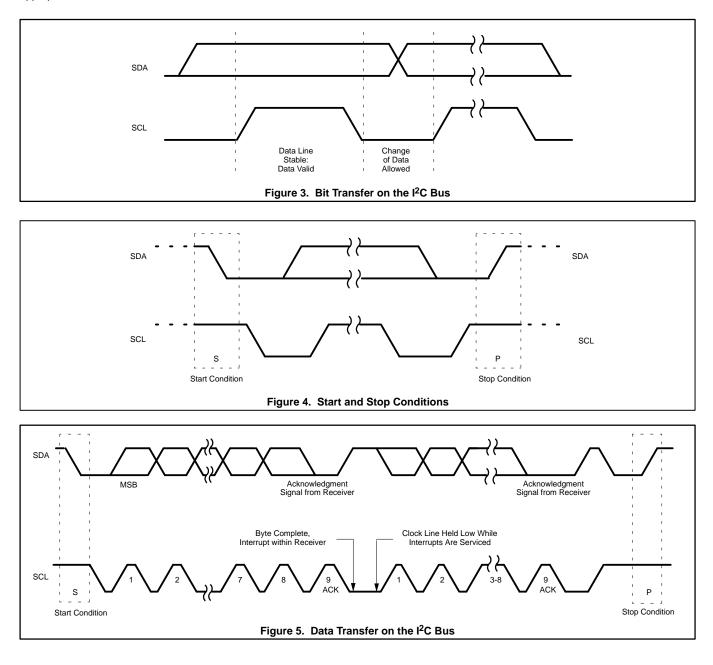

One data bit is transferred during each clock pulse (Figure 3). The data on the SDA line must remain stable during the HIGH period of the clock pulse in order to be valid. Changes in the data line at this time will be interpreted as control signals. A HIGH-to-LOW transition of the data line (SDA) while the clock signal (SCL) is HIGH indicates a Start condition, and a LOW-to-HIGH transition of the SDA while SCL is HIGH defines a Stop condition (Figure 4). The bus is considered to be busy after the Start condition and free again a certain time after the Stop condition. The Start and Stop conditions are always generated by the master.

The number of data bytes transferred between the Start and Stop condition from transmitter to receiver is not limited. Each byte, which must be eight bits long, is transferred serially with the most significant bit first, and is followed by an acknowledge bit (Figure 5). The clock pulse related to the acknowledge bit is generated by the master. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, while the transmitting device releases the SDA line (HIGH) during this pulse (Figure 6).

AN430

A slave receiver must generate an acknowledge after the reception of each byte, and a master must generate one after the reception of each byte clocked out of the slave transmitter. If a receiving device cannot receive the data byte immediately, it can force the transmitter into a wait state by holding the clock line (SCL) LOW. When designing a system it is necessary to take into account cases when acknowledge is not received. This happens, for example, when the addressed device is busy in a real time operation. In such a case the master, after an appropriate "time-out", should abort the transfer by generating a Stop condition, allowing other transfers to take place. These "other transfers" could be initiated by other masters in a multimaster system or by this same master.

An exception to the "acknowledge after every byte" rule occurs when a master is a receiver: it must signal an end of data to the transmitter by NOT signalling an acknowledge on the last byte that has been clocked out of the slave. The acknowledge related clock, generated by the master, should still take place but the SDA line will not be pulled down. In order to indicate that this is an active and intentional lack of acknowledgement, we shall term this special condition as a "Negative ACK".

The bus design includes special provisions for interfacing to microprocessors which implement all the I<sup>2</sup>C communications in software only—it is called "Slow Mode". When all the devices on the network have built-in I<sup>2</sup>C hardware support the Slow Mode is irrelevant.

June 26, 1992

## Using the 8XC751/752 in multimaster I<sup>2</sup>C applications

#### ADDRESSING AND TRANSFER FORMATS

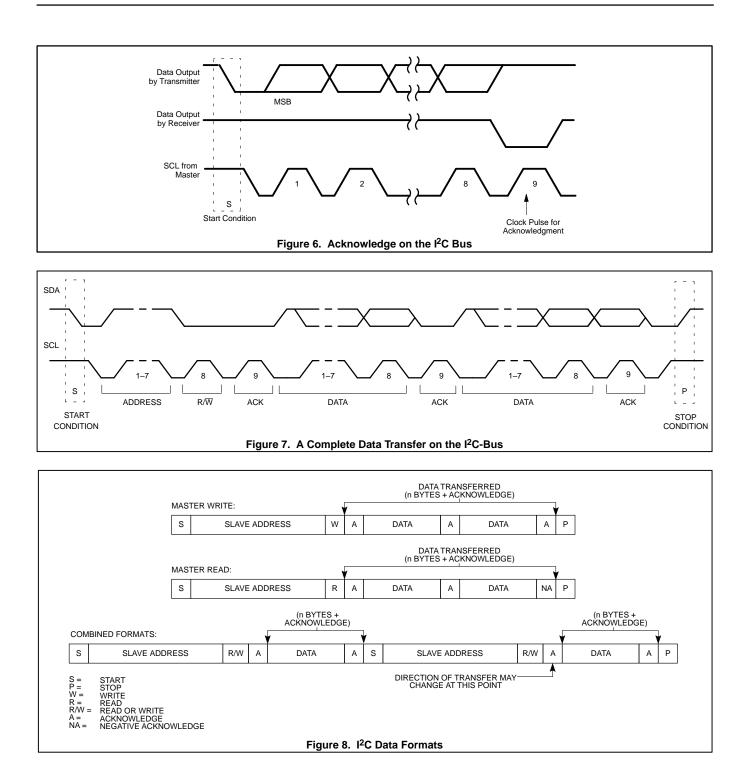

Each device on the bus has its own unique address. Before any data is transmitted on the bus, the master transmits on the bus the address of the slave of this transaction. A well-behaved slave, if it exists on the network, should of course acknowledge the master's addressing. The addressing is done with the first byte transmitted by the master after the Start condition.

An address on the network is seven bits long, appearing as the most significant bits of the address byte. The last bit is a direction (R/W) bit. A zero indicates that the master is transmitting (WRITE) and a one indicates that the master requests data (READ). A complete data transfer, comprised of an address byte indicating a WRITE and two data bytes is shown in Figure 7.

When an address is sent, each device in the system compares the first seven bits after the Start with its own address. If there is a match, the device will consider itself addressed by the master and will send an acknowledge. The device could also determine if in this transaction it is assigned the role of a slave receiver or slave transmitter, depending on the R/W bit.

Each node of the I<sup>2</sup>C network has a unique seven bit address. The address of a microcontroller is, of course, fully programmable, while peripheral devices usually have fixed and programmable address portions. In addition to the "standard" addressing discussed here, the I<sup>2</sup>C bus protocol allows for "general call" addressing and interfacing to CBUS devices.

When the master is communicating with one device only, data transfers follow the format of Figure 8 where the R/W bit could indicate either direction. After completing the transfer

and issuing a Stop condition, if a master would like to address some other device on the network, it could start another transaction by issuing a new Start.

Another way for a master to communicate with several different devices would be by using a "repeated start". After the last byte of the transaction was transferred, including its acknowledge (or Negative ACK), the master issues again a Start, followed by address byte and data, without effecting a Stop. The master may communicate with a number of different devices, combining READS and WRITES. Only after the transfer with the last slave took place, the master issues a Stop and releases the bus. Possible data formats are demonstrated in Figure 8. Note that the repeated start allows for both change of a slave and a change of direction, without releasing the bus. We shall see later on that the change of direction feature can come in handy even when dealing with a single device.

In a single master system the repeated start mechanism is more efficient than terminating each transfer with a Stop and starting again. In a multimaster environment the determination of which format is more efficient could be more complicated, as when a master is using repeated starts it occupies the bus for a long time and prevents other devices from initiating transfers.

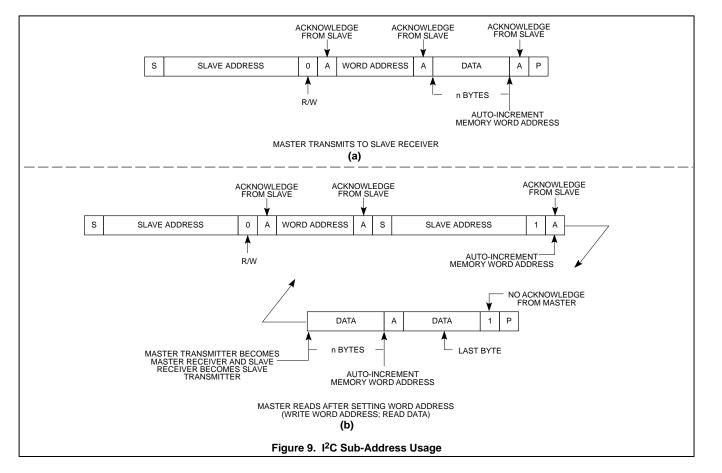

#### **USE OF SUB-ADDRESSES**

For some ICs on the  $l^2C$  bus the device address alone is not sufficient for effective communications and a mechanism for addressing the internals of the device is necessary. A typical example is addressing memories, when we want to access a specific word inside the device or a sequence of memory locations starting at a specific internal address.

A typical I<sup>2</sup>C memory device like the PCF8570 RAM contains a built-in word address register that is incremented automatically after each read or written data byte. When a master communicates with the PCF8570 it must send a sub-address in the byte following the slave address byte. This sub-address is the internal address of the word the master wants to access for a single byte transfer or the beginning of a sequence of locations for a multi-byte transfer. A sub-address is an eight bit byte, unlike the device address it does not contain a direction (R/W) bit, and like any byte transferred on the bus it must be followed by an acknowledge.

A memory write cycle is shown in Figure 9(a). The Start is followed by a slave byte with the direction bit set to WRITE, a sub-address byte, a number of data bytes and a Stop signal. The sub-address is loaded into the word address memory. The data bytes which follow will be written one after the other starting with the sub-address location and the register is incremented automatically.

The memory read cycle (Figure 9(b)) commences in a similar manner with the master sending a slave address with the direction bit set to WRITE with a following sub-address. Then, in order to reverse the direction of the transfer, the master issues a repeated Start followed again by the memory device address, but this time with the direction bit set to READ. The data bytes starting at the internal sub-address will be clocked out of the device with each followed by a master-generated acknowledge. The last byte of the read cycle will be followed by a Negative ACK, signalling the end of transfer. The cycle is terminated by a Stop signal.

AN430

### Using the 8XC751/752 in multimaster I<sup>2</sup>C applications

#### ARBITRATION IN A MULTIMASTER SYSTEM

The decision about which master has control over the I<sup>2</sup>C bus is based solely on the address and data sent by competing masters, and there is no central master or any order of device priority on the bus. Any device connected to the I<sup>2</sup>C bus is allowed to become a master, but devices are not supposed to "steal" the bus from other devices when a transfer is in process. If a device wishing to be a Master is aware that a transaction (initiated by another master) is taking place, it will wait until the transfer is concluded with a Stop condition on the bus-and only then try to seize it by sending its own Start. It is possible, however, that two or more masters may want to start a transfer at exactly the same moment. A scenario that may happen quite frequently in a loaded system: two devices are waiting for a long transaction to be completed, and simultaneously try to get the bus when detecting the Stop condition. An arbitration procedure synchronizes the different clocks, ensuring that the data is not corrupted, and causes all masters except one to withdraw from the bus, so only one master will control the transfer. This procedure applies only when masters initiate transfers simultaneously.

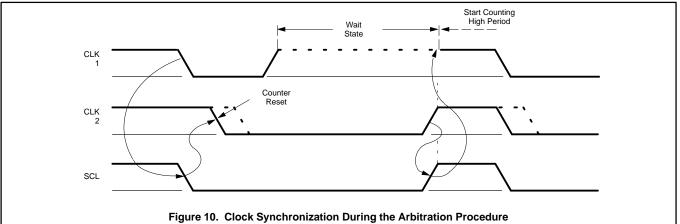

The clock synchronization, illustrated in Figure 10, ensures that only one defined clock is generated on the bus. It occurs naturally, as a result of the wired-AND property of the SCL line. Suppose two masters want to initiate a transfer on the bus. Clk1 and Clk2 in Figure 10 illustrate the desired clock outputs of each device, which would actually occur on the bus if each were the only master. The SCL waveform is the resulting wired-AND of the two clocks. The device that pulls the SCL down first will succeed. The other masters continuously monitor the clock line, and reset their internal clock counter to start counting their own Low clock period. This way, the first falling edge will synchronize all clock generators to the beginning of the Low time.

Once a device clock has gone Low it will hold the SCL line in this state until its internal clock High state is reached, and then will release the line. The Low to High change in this device will not change the state of the SCL line if another device, which is still within its Low period, is pulling down the line. This way, SCL will be held Low by the device with the longest Low period. A master that has finished its Low time earlier will enter a wait state until SCL is released by the slowest master and goes high. Upon the rising edge of SCL all masters start counting their High period, the first device to complete its High period will pull the SCL Low. In this way a single, synchronized clock is generated on the bus where the rising edge is being defined by the slowest master and the falling edge by the fastest master.

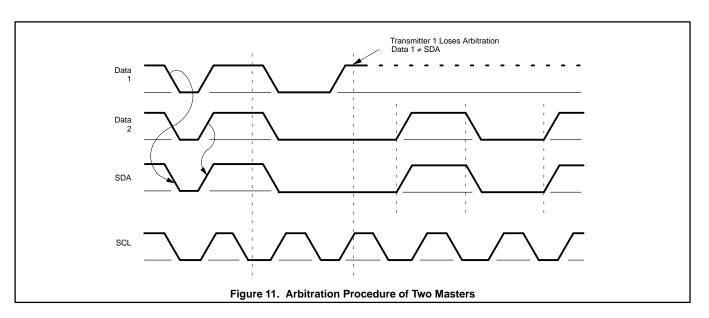

Arbitration between masters takes place on the SDA line. A master which tries to transmit a High while another device transmits a Low will withdraw, shutting off its data output stage and not interfering with the transfer until a Stop condition is detected. Due to the wired-AND property of the SDA line, a device "knows" that it lost arbitration by the fact that the Low SDA is different than its desired High output. Arbitration starts by comparing the address bits. When masters transmit different addresses the one transmitting the address with the lowest binary value wins. If all masters in arbitration transmit to the same address, arbitration continues into the comparison of data. Figure 11 illustrates the arbitration process between two masters.

By definition, the transfer that forces the wired-AND result is the one that wins the arbitration, so the address and data of a winning device are not corrupted and no information is lost in the arbitration process. A master losing arbitration may generate clock pulses until the end of the byte. Thus it may affect the clock speed, but not the data on the bus.

If a master loses arbitration during the addressing stage it is possible that the winning master is trying to address it. In an efficient design, the losing master should switch immediately to its slave receiver mode, receive the data transmitted and acknowledge it-otherwise the message will have to be re-transmitted or is lost. A well designed master will take into account "illegal" protocol situations and will determine that it lost arbitration when it detects a Stop or a Start which are not synchronized with its own transmission. Electrical interference or a malfunctioning device may cause such a situation which actually corrupts the message transfer.

AN430

#### HANDSHAKE BY CLOCK SYNCHRONIZATION

The clock synchronization mechanism as described above actually implements a handshake mechanism, enabling receiving devices to "slow down" fast transfers when necessary.

On the bit level, a slow slave device like a microcontroller that does not have hardware I<sup>2</sup>C interface port, can extend each clock period and slow down the bus clock. The speed of any master is adapted to the operating rate of this device as long as it is active on the bus.

On the byte level the synchronization mechanism takes effect as a "handshake" mechanism when a slave device that was fast enough to receive or transmit a byte still needs extra time to store the received byte or prepare the next byte for transmission. The slave can hold the SCL line low after the reception and acknowledge of a byte, thus forcing the Master into a wait state—until the slave is ready for the next transfer.

#### 8XC751 I<sup>2</sup>C HARDWARE

The on-chip I<sup>2</sup>C bus hardware support of the 8XC751 allows operation on the bus at full speed and simplifies the software needed for effective communications on the network. The hardware activates and monitors the SDA and SCL lines, performs the necessary arbitration and framing error checks, and takes care of clock stretching and synchronization. The hardware support includes a bus timeout timer, called Timer I. The hardware is synchronized to the software either through polled loops or interrupts.

Two of the port 0 pins are multi-functional. When the  $I^2C$  is active, the pin associated with P0.0 functions as SCL, and the pin associated with P0.1 functions as SDA. These pins have an open drain output.

Two of the five interrupt sources may be used for I<sup>2</sup>C support. The I<sup>2</sup>C interrupt is enabled by the EI2 flag of the interrupt enable register, and its service routine should start at address 023h. An I<sup>2</sup>C interrupt is usually requested (if enabled) when a rising edge of SCL indicates new data on the bus or a special condition occurs: Start, Stop or arbitration loss. The interrupt is induced by the ATN flag, (see below for the conditions for setting this flag). The Timer I overflow interrupt is enabled by the ETI flag, and the service routine starts at 01Bh.

The I<sup>2</sup>C port is controlled through four special function registers: I<sup>2</sup>C Control (I2CON), I<sup>2</sup>C Configuration (I2CFG), I<sup>2</sup>C Data (I2DAT) and I<sup>2</sup>C Status (I2STA). The register addresses are shown in the 8XC751 section of the Philips Semiconductors Microcontroller Data Handbook (IC20). Although the following discussion of the hardware and register details is not complete, it should give a better understanding of the programming examples.

#### Timer I

In  $I^2C$  applications, Timer I is dedicated to the port timing generation and bus monitoring. In non- $I^2C$  applications, it is available for use as a fixed rate timer.

For the bus monitoring function, Timer I is being used as a "watchdog timer" for bus hang-ups. It creates an interrupt when the SCL line stays in one state for an extended period of time between a Start condition and a following Stop condition. SCL "stuck low" indicates a faulty master or slave. SCL "stuck high" may mean a faulty device or that noise induced into the I<sup>2</sup>C caused all masters to withdraw from the I<sup>2</sup>C arbitration.

The time-out interval of Timer I is fixed: it carries out and interrupts (if enabled) when about 1024 machine cycles have elapsed since a change on SCL within a frame. In other words, whenever I<sup>2</sup>C is active we let Timer I run, but clear it whenever a frame is not in progress (reset or Stop occurred more recently than the last Start condition) or SCL changes within a frame. (Note: we wrote "about 1024 machine cycles" for the sake of accuracy—this number may slightly change according to the setting of the CT0 and CT1 bits mentioned below. In any case, the exact number of cycles for a time out does not have any practical significance).

In addition to the interrupt upon Timer I overflow, the I<sup>2</sup>C port hardware is reset. This is useful for multiple master systems in situations where this same 8XC751 caused the bus hang-up due to a lack of software response. SCL will be released and I<sup>2</sup>C operation between other devices could continue.

#### **I2CON Register**

The  $I^2C$  Control register can be read or written to (see Figure 12).

When writing to the I2CON register one should use bit masks as demonstrated in the examples. Trying to clear or set the bits in the register using the bit addressing capabilities of the 8XC751 may lead to undesirable results. The reason is that a command like CLRB reads the register, sets the bit and writes it back—and the write-back may affect other bits.

#### **I2CFG Register**

The configuration register is a read/write register (see Figure 13).

#### **I2DAT Register**

The  $I^2C$  data register is a read/write register, where the msb represents the data received or data to be sent. The other seven bits are read as 0 (see Figure 14).

#### **I2CSTA Register**

The  $I^2C$  STAtus Register is a read-only register reflecting the internal status of the  $I^2C$  interface hardware (see Figure 15).

#### **Transmit Active State**

The transmit active state—Xmit Active—is an internal state in the  $I^2C$  interface that is affected by the  $I^2C$  registers as explained above. The  $I^2C$  interface will only drive the SDA line low when Xmit Active is set. Xmit Active is set by writing the I2DAT register or by writing I2CON with XSTR = 1 or XSTP = 1. The ARL bit will be set to 1 only when Xmit Active is set—in such a case Xmit Active will be automatically reset upon ARL. Xmit Active is cleared by writing 1 to CXA at I2CON register or by reading the I2DAT register.

| I2CON READ  | RDAT        | ATN                                                                                                                                                                                                                                                                  | DRDY           | ARL             | STR                                         | STP             | MASTER           | —               |  |  |  |  |

|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|---------------------------------------------|-----------------|------------------|-----------------|--|--|--|--|

| RDAT        | RDAT in     | Received DATa bit. The value of SDA latched by the rising edge of SCL. Its contents is identical to RDAT in I2DAT register. Reading the received data here allows doing so without clearing DRDY and releasing SCL.                                                  |                |                 |                                             |                 |                  |                 |  |  |  |  |

| ATN         | testing for | An "ATteNsion" flag, set when any one of DRDY, ARL, STR or STP is set. This flag allows a single bit<br>testing for terminating "wait loops", indicating a meaningful event on the bus. This same flag actually<br>activates the I <sup>2</sup> C interrupt request. |                |                 |                                             |                 |                  |                 |  |  |  |  |

| DRDY        |             | bata ReaDY flag, set by a rising edge of SCL when I <sup>2</sup> C is active, except at an idle slave. This flag is leared by reading or writing the I2DAT register, or by writing a 1 to CDR (same address, I2CON write).                                           |                |                 |                                             |                 |                  |                 |  |  |  |  |

| ARL         | ARbitrat    | Rbitration Loss flag. Indicates that this device lost the arbitraion while trying to take control of the bus.                                                                                                                                                        |                |                 |                                             |                 |                  |                 |  |  |  |  |

| STR         | STaRt fla   | ag is set whe                                                                                                                                                                                                                                                        | n a Start con  | dition is detec | ted, except a                               | t an idle slave | e.               |                 |  |  |  |  |

| STP         | SToP fla    | g is set when                                                                                                                                                                                                                                                        | a Stop cond    | ition is detect | ed, except at                               | an idle slave   |                  |                 |  |  |  |  |

| MASTER      | This flag   | is set when                                                                                                                                                                                                                                                          | the controller | is a bus mas    | ter (or a pote                              | ntial master, j | prior to arbitra | ation).         |  |  |  |  |

| I2CON WRITE | CXA         | CXA IDLE CDR CARL CSTR CSTP XSTR XSTP                                                                                                                                                                                                                                |                |                 |                                             |                 |                  |                 |  |  |  |  |

| CXA         | "Clear X    | mit Active". V                                                                                                                                                                                                                                                       | Vriting a 1 to | CXA clears th   | ne internal tra                             | nsmit-active s  | state.           |                 |  |  |  |  |

| IDLE        |             |                                                                                                                                                                                                                                                                      |                |                 | the I <sup>2</sup> C until<br>ng by turning |                 |                  | If the software |  |  |  |  |

| CDR         | Clear Da    | ata Ready—c                                                                                                                                                                                                                                                          | lears the DRI  | DY flag.        |                                             |                 |                  |                 |  |  |  |  |

| CARL        | Clear Ar    | bitration Loss                                                                                                                                                                                                                                                       | -clears ARI    | flag.           |                                             |                 |                  |                 |  |  |  |  |

| CSTR        | Clear ST    | āRt—clear S                                                                                                                                                                                                                                                          | TR flag        |                 |                                             |                 |                  |                 |  |  |  |  |

| CSTP        | Clear ST    | op-clear ST                                                                                                                                                                                                                                                          | P flag.        |                 |                                             |                 |                  |                 |  |  |  |  |

| XSTR        |             | "Xmit repeated STaRt". writing a 1 to this bit causes the hardware to issue a Repeated Start signal. A<br>side effect will be setting the internal Xmit Active state. This should be used only when the device is a<br>master.                                       |                |                 |                                             |                 |                  |                 |  |  |  |  |

| XSTP        | "Xmit ST    | oP". Issue a                                                                                                                                                                                                                                                         | Stop conditio  | n. The Xmit A   | Active state is                             | being set.      |                  |                 |  |  |  |  |

|             |             |                                                                                                                                                                                                                                                                      | Figu           | re 12. I2C      | ON Regis                                    | ster            |                  |                 |  |  |  |  |

|          | SLAVEN  | MASTREQ                                        | CLRTI         | TIRUN         | _                          | _         | CT1           | CT0           |

|----------|---------|------------------------------------------------|---------------|---------------|----------------------------|-----------|---------------|---------------|

| SLAVEN   | 0       | a 1 to this flag                               |               |               | ns of the I <sup>2</sup> C | nterface. |               |               |

| MASTREC  |         | control of the                                 |               |               | s read as 0.               |           |               |               |

| TIRUN    |         | a 1 will let Tim<br>nsitions, Start            |               |               |                            |           | mes, and will | be cleared by |

| CT1, CT0 | hardwar | its should be<br>e. They contro<br>performance | ol a frequenc | y devider whi | ch determine               |           |               |               |

|          |         |                                                | Figu          | re 13. I2C    | FG Regis                   | ster      |               |               |

| I2DAT READ  | RDAT                                                                                                                                                                                   | _ | _ | _ | _ | _            | _ | _ | 1 |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|--------------|---|---|---|--|--|

| RDAT        | Xmit Ac                                                                                                                                                                                |   |   |   |   | SCL. Reading |   |   |   |  |  |

| I2DAT WRITE | I2DAT WRITE XDAT — — — — — — — — —                                                                                                                                                     |   |   |   |   |              |   |   |   |  |  |

| XDAT        | XDAT Xmit DATa bit. Writing XDAT determines the data for the next bit to be transmitted on the I <sup>2</sup> C bus.<br>Writing I2DAT also clears DRDY and sets the Xmit Active state. |   |   |   |   |              |   |   |   |  |  |

|             | Figure 14. I2DAT Register                                                                                                                                                              |   |   |   |   |              |   |   |   |  |  |

٦

| I2CSTA READ                | IDLE                            | XDATA                                                           | XACTV         | MAKSTR          | MAKSTP | XSTR | XSTP | — |  |  |

|----------------------------|---------------------------------|-----------------------------------------------------------------|---------------|-----------------|--------|------|------|---|--|--|

| IDLE                       | Indicate                        | s when the I <sup>2</sup>                                       | C hardware i  | s in the Idle m | node   | -    | -    |   |  |  |

| XDATA                      |                                 | flects the contents of the I <sup>2</sup> C transmitter buffer. |               |                 |        |      |      |   |  |  |

| XACTV                      | Indicate                        | licates that the I <sup>2</sup> C transmitter is active.        |               |                 |        |      |      |   |  |  |

| MAKSTR                     | Indicate                        | dicates that the hardware is effecting a Start.                 |               |                 |        |      |      |   |  |  |

| MAKSTP                     | Indicate                        | s that the har                                                  | dware is effe | cting a Stop.   |        |      |      |   |  |  |

| XSTR                       | Hardwa                          | re effecting a                                                  | Repeated St   | art.            |        |      |      |   |  |  |

| XSTP                       | XSTP Hardware effecting a Stop. |                                                                 |               |                 |        |      |      |   |  |  |

| Figure 15. I2CSTA Register |                                 |                                                                 |               |                 |        |      |      |   |  |  |

#### I<sup>2</sup>C COMMUNICATIONS SOFTWARE

The software listing demonstrates programming the 8XC751/752 for a multimaster I<sup>2</sup>C environment where the device can be both a Master or a Slave responding to other Masters on the I<sup>2</sup>C network. The bulk of the software is communications routines which are not only for demonstration but could be ported to other user programs with minimal or no modifications. The routines are guite general and could be useful in most applications. We have tried to design a well-defined software interface, enabling most users to copy the routines as they are, modifying only the pre-defined interface elements to fit the specific applications. We encourage users to use the routines without modifications whenever possible, as the lower levels of the hardware-software integration could be guite involved.

The rest of this application note will relate to the programming example. We shall discuss the general operation of the routines and how they are integrated into an application. Then we shall describe in detail all the software interface elements and how to use them.

#### I<sup>2</sup>C COMMUNICATIONS ROUTINES—OVERVIEW

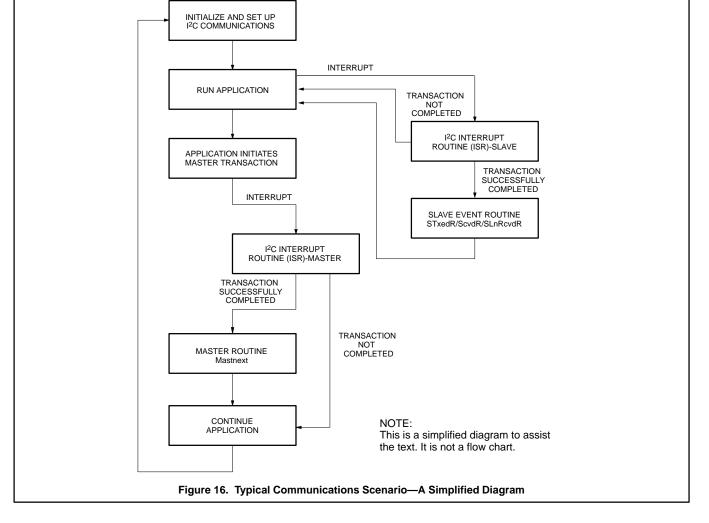

In order to function well in a multimaster environment the microcontroller must be able to take control of the I<sup>2</sup>C bus as a Master, "tolerate" message transactions between other Masters and other devices, and respond efficiently as a Slave to other bus Masters. The communications routines should allow a Master "graceful" recovery from an arbitration loss and other situations when a message transaction is not completed, allowing for communication re-tries.

For Slave operation the microcontroller must be interrupt driven relative to an  $I^2C$  frame

Start, as any Master on the bus could request a transaction at any moment, not synchronized to the application program executing on the controller. An interrupt service routine monitors the address transmitted on the bus. When the microcontroller is addressed it takes care to either read the data from the bus into a buffer or write buffer data onto the bus. When such a transaction is successfully completed, one of several "Slave Event Routines" is called prior to returning to the main application program. Such an "Event Routine" is a part of the application, allowing an immediate response to the data received, or the fact that data was transmitted to a requesting Master. This allows "synchronization" of the application to a "slave" bus transaction. Typical uses of the Event Routine mechanism will be a computation based on new data, or re-loading the transmit buffer with new data getting ready for the next random request. The actual Event Routines will be programmed differently for different applications, but the names and the calls will remain the same as long as the communications routines are left unmodified.

A transaction as a Master is initiated by the application program. Our implementation uses the interrupt mechanism for the Master communications as well. The application issues a request for the bus by setting the MASTRQ bit of the I<sup>2</sup>C port control, and when the bus is available an interrupt occurs. This way, if the bus is free there will be an immediate response. If the bus is busy, the application may go on executing (if so programmed) until this controller can get control of the bus. When the microcontroller gets mastership of the bus it initiates a bus transaction according to "directives" set by the application program. The most important directives are the address (and subaddress if relevant) of the slave device addressed, and the length of the message to be transmitted or received.

10

When a Master transaction is concluded, a Master Event Routine (called MastNext) is called to perform whatever task the application demands. As with the Slave Event Routines it will typically respond to a successful transmission or reception of data. In addition, it could handle situations where a slave does not respond at all, or does not acknowledge a data byte (thus causing data transfer to terminate). A program might react to the fact that a slave does not respond by re-trying to communicate at a later time, by issuing a message to another peripheral device or just ignoring it. The handling of such cases is application dependent, and should be programmed into the routine called "MastNext". The MastNext routine is invoked when the Master terminates the transaction "willingly", but not upon arbitration loss.

The microcontroller operating as a bus Master may lose arbitration to another Master which happens when two Masters transmit in synchronization, commencing with the same Start signal. If arbitration is lost while transmitting or receiving data, our processor withdraws from the bus and turns itself into a slave-an active Slave upon a Start, or returning to the calling program as an idle slave. When the arbitration loss occurs while transmitting an address, our processor turns itself immediately into an active slave, "listening" to the rest of the address transmitted by the new Master. If our processor reads its own address from the bus (as transmitted by the new Master) our processor responds as a willful slave. If this mechanism would not have been implemented, there could be potential inefficiency when a device that happened to be synchronized to another Master loses arbitration, but is not able to respond to the winning device.

Another situation for arbitration loss could be a bus exception resulting from a device operating not according to the bus protocol or

be interrupted again for the next frame (next Start, received as a slave or induced as a Master). A status flag and a counter report on the watchdog interrupt, so the application program can be made to inhibit the  $l^2C$  port if

"regular" arbitration loss detected with the ARL hardware flag, such a situation may occur with detecting a Start or a Stop in the middle of transmitting an address or data byte. In such a situation the microcontroller

noise, temporary bus line shorts, "hot plug in" of devices or even erroneously programmed devices—and a "fail safe" controller program should be able to detect bus problems and possibly assist in resolving them. The RECOVER routine resets the I<sup>2</sup>C interface of the microcontroller, and attempts to release some other devices on the bus by toggling the clock line. The I<sup>2</sup>C interface of the 8XC751 is reset by letting TimerI run and expire, since this circuitry does not feature a software controlled reset. This "extreme" measure is needed in some cases of bus protocol violation.

there are too many occurrences of a

The bus and interface circuit recovery routine can be automatically invoked whenever Timerl detects a timeout. In addition, for systems where potential bus failures are a concern and reliability is an issue, one may implement mechanisms to invoke bus and interface recovery from the application code. This may help in cases where the bus gets "stuck" when there is no I<sup>2</sup>C frame in progress. In such an instance the watchdog timer will not give any timeout indications, as it has not been activated. Another case emanates from a design peculiarity of the interface circuitry on the 8XC751: if the SCL line is externally grounded when there is a Start condition, this Start might be ignored, and the watchdog may not be activated. Our programming example deals with potential failures by testing for transaction completion and retrying transmissions when necessary (these are explicit retries, in addition to an "automatic" retry after a Master's arbitration loss, invoked by the MASTRQ bit). Too many transmission failures activate the RECOVER routine.

#### I<sup>2</sup>C COMMUNICATIONS ROUTINES—INTERFACE

The I<sup>2</sup>C service routine deals with the transmission and reception of messages, without any concern for the contents of the message. In order to provide a general interface for different applications the data is transferred via buffers. The service routine does not have to "know" where the data goes to or comes from—as long as the application program specifies the required pointers for these buffers. The interface to the actual application (which "cares" about message contents, timing, addressing and so forth) is done in a well defined manner, allowing usage of the same service routine with different application programs.

The interface is carried out with the use of buffers, pre-defined names for Application Event Routines, interface RAM locations for transferring parameters, pointers and flags, and constants. A more detailed discussion of the interface follows.

#### Buffers

There are three buffers for data transfers between the  $I^2C$  bus and the application program.

MasBuf is used for Master transmission and reception. The number of data bytes for each Master message—reception or transmission, is specified by the memory location MASTCNT. The value in MASTCNT should be less than the length of MasBuf. For Master transmission the message is placed in MasBuf before the transmission is initiated. In Master reception, the received message will be contained in the same buffer. There is only one Master message transaction occurring at the same time, so we may use the same buffer both for transmission and reception.

For Slave operation we must accommodate data transfers which may come randomly, asynchronous to each other or to possible operation of the same device as a Master. Therefore it is necessary to allocate additional RAM area as buffers dedicated to Slave operation: SRcvBuf for receiving data, STxBuf for transmission.

The length of the Slave receive buffer is defined by the symbol RBufLen. It is used by the code for protection, avoiding overwriting RAM beyond the allocated buffer size in case a Master sends a message which is too long. There is no need for RAM protection for transmission, but the Master should not request more data than STxBuf can supply.

#### Interface RAM Locations

RAM location MyAddr contains the address of this processor.

Status flag MSGSTAT is used for reporting to the application on I<sup>2</sup>C communications status-mainly on the successful, or unsuccessful, completion of a message transaction. The contents of MSGSTAT may be used by the mainline application code or by the Event Routines. The different codes that could be placed by the I<sup>2</sup>C service routine are described later in the text. When the message processing commences, a code indicating Slave or Master processing is inserted to MSGSTAT, and is updated as we go along. There could be many applications that will not need to use MSGSTAT contents, as the very fact of calling a certain event routine implies completion of a processing stage.

## Using the 8XC751/752 in multimaster I<sup>2</sup>C applications

Philips Semiconductors Microcontroller Products

interference on the bus lines. In addition to

withdraws from the bus as well-active Slave

upon a Start detection, or returning as an idle

When a Master transaction is terminated by

an arbitration loss, the Master Request flag (MASTRQ) of the hardware I<sup>2</sup>C port remains

in effect. As a result when the bus gets free,

the transaction that was cut will start again.

any application involvement (unlike

our device will take control, issue a Start, and

This restart will happen automatically, without

non-acknowledgement, where the MastNext

routine determines what shall be done).

structured as an interrupt service routine

responding to an I<sup>2</sup>C port interrupt upon a

processing is continuous, where the I<sup>2</sup>C port

is polled for hardware response, and the I2C

program are minimal, and interfacing is done

via RAM buffers and some pre defined RAM

locations. The lower level interface with the

hardware is done inside the service routine,

**BUS WATCHDOG AND ERROR**

A malfunctioning device (in hardware or

software) may hold the SCL line low, thus

(due to hardware interference, such as a

the bus. Since within a frame the bus is

software-polled, a "stuck" bus might cause

the application software to "hang forever".

Here the TIMERI watchdog comes to the

rescue, interrupting when there is no bus

the watchdog timer, the processing of the

When the I<sup>2</sup>C service routine is interrupted by

current frame is not completed and the event

routines are not called. The software returns

activity for a long period of time.

causing the bus to be "stuck". It might even

be possible that a transient protocol violation

device turning on) may cause some devices (non programmable, or even microcontrollers

which were not carefully programmed) to hold

interrupts are disabled. Other interrupts are

enabled during the service routine. The

set-up requirements from the mainline

and can typically be ignored by the

application programmer.

RECOVERY

The I<sup>2</sup>C communications routines are

frame Start. Within a frame the I<sup>2</sup>C

slave in other cases.

Application note

### AN430

For Master transactions, in addition to the data buffer MasBuf, there are several RAM locations into which the application inserts Master message "directives". These directives provide the service routine with the information necessary to carry out the next Master transaction. The one byte RAM locations used for directives are DESTADRW, DESSUBAD, MASTCNT and MASCMD.

DESTADRW contains the destination slave address in bits 7-1, while bit 0 is the R/W bit. Bit 0 contains 0 for a Write operation (the message is to be transmitted to the salve) and 1 for a Read operation (message is being read from the slave and received by this Master).

DESSUBAD contains the 8 bit sub-address of the slave, if necessary. For transactions without a sub-address, the contents of DESSUBAD is ignored.

MASTCNT contains the number of data bytes in the message to be sent from or received into MasBuf. This number should not be bigger than the length of MasBuf.

MASCMD byte contains the bit flags SUBADD, RPSTRT and SETMRQ. SUBADD is 0 (cleared) for a message with a regular address, and 1 (set) when a subaddress is required. When SUBADD is set, the service routine takes care of all the protocol required for sub-addressing, which includes a Repeated Start for Read operations. A message with a subaddress is considered to be a single message, even if it includes a Repeated Start.

The RPSTRT and SETMRQ are kept cleared in regular applications, and will be used only for "tailoring" the bus transfers in special cases. When RPSTRT is cleared the message will terminate, as usually required, with a Stop. When RPSTRT is set a Repeated Start will be sent on the bus, and Master operation will resume. The RPSTRT directive relates to terminating the message after all the data was transferred, and not to the mandatory Repeated Start in the middle of sub-addressed Read operation. A single message with a subaddress will typically have RPSTRT cleared. SETMRQ indicates what will be loaded into the MASTRQ flag of the hardware when Stop is transmitted. Typically it will be cleared. When SETMRQ is 1, MASTRQ will be set, thus trying to issue a new Start immediately following the Stop. In such a case the service routine will not return upon Stop, but will continue as a Master.

TITOCNT is used to count time-outs of the watchdog timer. Whenever such a timeout invokes the TIMER I interrupt service routine the contents of the location TITOCNT are

incremented, and the timeout is reported in MSGSTAT. The count is saturated at 0FFh. This mechanism may be used in an application that is very much "concerned" with potential bus failures, allowing some type of "failure monitoring" by the application even for Slave transactions.

#### APPLICATION EVENT ROUTINES

The service routine calls Event Routines with pre-defined names (Figure 16), and these routines must be provided by the application program. The actual code of the routines will differ from application to application, but the routine names are being kept the same.

These routines are being called when successful processing of a message (send or receive) is completed. The routines may perform whatever action the application was designed for, which is not necessarily related to the  $l^2C$  communications mechanism. In addition, the routines may perform the data interface tasks for the  $l^2C$  port, like emptying buffers from received data or preparing the next message by setting up the buffers.

The mechanism of calling the event routines out of the service routine allows an immediate reaction to the event of message processing completion, before any new activity happens on the bus. In some simple applications this may not be necessary. For example, one may have a main program for a slave which is just a wait loop monitoring a flag set by the service routine when a message transfer, initiated by some master, is completed. In such a case the application could react to the message completion after the interrupt service routine returns. However, in the general case this will not be sufficient. An example could be a slave with an application which is constantly busy doing another task, in an environment where the communication requests on the I<sup>2</sup>C bus are frequent. If there is a new message request shortly after the current message is completed, having to wait for the application until it "has time" may result in not reacting, or sending the same data again, or overwriting the received data in the buffer. Another obvious case demanding event routine calls is a Master sending different messages with a Repeated Start-the new data for the following message must be prepared in the interrupt service routine as the current message is completed (there is no return from interrupt prior to the new data transmission).

The programmer has the flexibility to decide where to prepare the next message according to the requirements of the application. This can be done after return from the event routine, in the application code after the return from interrupt, or a combination of both, where the time critical events are performed in the event routines. The application may monitor the MSGSTAT flag for message processing completion. If the event routines are not used, it is recommended to simply code them as a "RET" instruction, thus turning them into dummy routines (this an easier and better practice than changing the service routine itself, eliminating the calls).

#### **Master Event Routine:**

#### MastNext

This routine is called by the service routine when the processing of the current Master message is completed. For an indication on the type of message processing completion, MastNext may inspect the contents of MSGSTAT RAM location.

When MastNext is called, MSGSTAT will contain one of the following codes for message processing completion:

MRCVED (= 21h)—a complete message (with number of data bytes indicated by MASTCNT) was received from the slave.

MTXED (= 22h)—the number of data bytes indicated by MASTCNT were successfully sent and acknowledged by the slave.

MTXNAK ( = 23h)—the slave did not acknowledge a data byte of the message, even though it had acknowledged its address. The message transmission was terminated upon the NAK.

MTXNOSLV (= 24h)—no slave acknowledged the address indicated by memory location DESTADDR.

The MastNext routine may perform any task(s) necessary for the application. Data handling tasks will typically be dependent on the MSGSTAT indication. One possible task could be setting the directives for the next message. The necessity for executing this task here (versus the main-line code initiating the transfer) is of course application dependent.

#### **Slave Event Routines:**

These routines are called when a message transaction as a slave has been completed. In many cases it could be important to utilize the calls to such routines as the requests for message transactions as a slave can come randomly, asynchronous to the application program. The application may demand that new data coming in should immediately

initiate some tasks (e.g. control an output port)—and the event routine can be used to process the result of the slave interrupt.

In most cases it will be necessary for a slave to react immediately to a message received simply in order not to lose the data. As a new message may come randomly, it may overwrite the reception buffer before the data has been transferred out of it or acted upon.

For applications in which the reaction for slave events is performed after the return from the service routine, the event is reported by placing an appropriate code in the MSGSTAT flag. The programmer may use event routines, other mainline routines inspecting MSGSTAT, or both. If the event routines are not used, it is recommended to code them as a "RET" instruction.

#### SRcvdR:

Called by the service routine when a new, complete message has been received into SRcvBuf. When SRcvdR is called, R1 points to the address of the last byte received into the buffer. In a typical application SRcvdR will transfer the new data out of SRcvBuf, so it will not be written over by a subsequent slave reception.

The equivalent MSGSTAT indication for this event is SRCVD (= 11h).

#### SLnRcvdR:

Called when a slave message has been received into SRcvBuf, but the message was longer than the SRcvBuf buffer (as specified by RbufLen).

The equivalent MSGSTAT indication for this event is SRLNG (= 12h).

If the program is supposed to react to a too long a message the same way as to a message that can be contained in the buffer, one may code SLnRcvdR simply as a call to SRcvdR.

#### STXedR:

Called by the service routine when data has been transmitted out of the slave STxBuf buffer according to a master's request. This routine may insert new data into the buffer, preparing it for the next slave transmission.

The equivalent MSGSTAT indication for this event is STXED ( = 13h).

Note that we do not have a separate routine for the case that the master requested too many bytes—more than STxBuf length—and we sent out meaningless bytes. It is the master's responsibility to specify the message length, and it should be able to request messages with the appropriate length from each slave on the bus.

#### SRErrR:

This routine relates more to bus communications than to the application itself.

# Application note

It can be called when we positively detect a bus error upon reception as a slave, in case the application is supposed to know about it. In most cases this call will not be used, as dealing with bus communications difficulties is usually left to the Master.

Just prior to calling SRErrR, the code SRERR (= 14h) is placed in MSGSTAT.

## 0Completion Routine: I2CDONE

This routine is called every time, before returning from the I<sup>2</sup>C interrupt service routine, whether the transaction was successful or not. It can be used to "safely" monitor MSGSTAT without any risk of a new interrupt modifying the current indication. Simple application programs will not make use of this routine. A more sophisticated application implementing a fail-safe communications protocol may use it to count errors of a certain type in order to determine a recovery scheme. In our programming example, I2CDONE inhibits I2C interrupts when it is evident that as a result of protocol errors interrupts are not caused by legitimate Starts.

#### CONSTANTS

RBufLen—the length of SRcvBuf, the slave receive buffer. This constant may be used both by the I<sup>2</sup>C routines and the application program, and it is the responsibility of the application programmer to define the correct buffer length.

MYNUM—This ROM constant is dependent on the application environment. It is a small integer defining a "serial number" of the node, out of all the processors running the same code. This constant is used only when recovering from a timeout, in order to "de-synchronize" masters from each other when trying to recover the bus.

CTVAL1 is a constant defined in ROM. It is used by the application code portion which

initializes the  $l^2$ C, for loading CT0 and CT1 with a value appropriate for the crystal being used.

MYADDR1 is a ROM constant containing the address of the processor's  $I^2C$  node. This value is used by the application demo to load the RAM location MyAddr.

#### USING THE COMMUNICATIONS SUBROUTINES

In order to use the I<sup>2</sup>C Communications Routines an application program should take care of the following:

- Upon initialization, load bits CT1, CT0 of I2CFG register according to the clock crystal used (refer to the table of CT1, CT0 values in the 8XC751 section of the Philips Semiconductors Microcontroller Data Handbook (IC20)).

- Load MyAddr RAM location with the address of this node.

- For Slave operation, load STxBuf with the initial data to be transmitted.

- For slave operation, set the SLAVEN bit in the I2CFG register.

- Enable I<sup>2</sup>C and watchdog interrupts by setting the ETI, EI2 and EA bits of the interrupt enable register.

- For Master operation, set up the next transaction by loading the appropriate directives into MASCMD, DESTADRW, DESSUBAD (if applicable) and MASTCNT, and load MasBuf with the appropriate data if it is a Write message.

- For Master operation, initiate the next transaction by setting MASTRQ bit in I2CFG.

- For both Master and Slave operation, handle data transmission and reception via the buffers in main-line code or the Event Routines.

#### **PROGRAMMING EXAMPLE**

The assembler listing includes the I<sup>2</sup>C Communications Routines and a demo application exercising these routines. In most real-life applications the code of the routines could be used without modifications. For those who follow the coding of the routines. one should note that in many instances code speed and program space have been slightly compromised in order to improve readability. The almost "general purpose" interface to the routines affects efficiency as well, and it is possible to write more compact and somewhat faster code for specific applications. The reader is encouraged, though, to use the code "as is" whenever possible.

The "application" demo is simple—two microcontrollers exchange messages in a "ping-pong" game. In addition to trivial message exchange, the code demonstrates recovery mechanisms from communications errors and bus "hangups". We tried this code with two pairs of controllers exchanging messages on the same bus. The message exchange could repeatedly recover and restart when the SCL and SDA lines were temporarily shorted to ground or between themselves. Simpler versions, without the "protection" mechanisms, could "hang up" under such conditions.

#### Source Code Available On BBS

The source code file for this program is available for download from the Philips computer bulletin board system. This system is open to all callers, operates 24 hours a day, and can be accessed with modems at 2400, 1200, and 300 baud. The telephone numbers for the BBS are: (800) 451-6644 (in the U.S. only) or (408) 991-2406.

| PPCODE1 | 83C751   | Multimaster I2C                        | Routines      |            |                                                              | 4/14/1992    | PAGE 1 |  |  |  |

|---------|----------|----------------------------------------|---------------|------------|--------------------------------------------------------------|--------------|--------|--|--|--|

|         | 1        | ;                                      |               |            |                                                              |              |        |  |  |  |

|         | 2        |                                        |               |            |                                                              |              |        |  |  |  |

|         | 3        | •************<br>'                     | *******       | ******     | ******                                                       | *****        | *****  |  |  |  |

|         | 4        | ;                                      | Multimas      | ter Code f | for 83C751/83C752                                            |              |        |  |  |  |

|         | 5        | ;                                      | 4/14/1992     |            |                                                              |              |        |  |  |  |

|         | 6        | ,                                      |               |            | ***************************************                      |              | *****  |  |  |  |

|         | 7        |                                        |               |            | y an application note. The I2C                               | routines     |        |  |  |  |

|         | 8        |                                        |               |            | d transportable into different                               |              |        |  |  |  |

|         | 9<br>10  |                                        | enarios, and  | were NO    | T optimized for speed and/or r                               | nemory       |        |  |  |  |

|         | 10       | ; utilization.                         |               |            |                                                              |              |        |  |  |  |

|         | 11       | ,<br>; Yoram Arbel                     |               |            |                                                              |              |        |  |  |  |

|         | 12       | , ioium moei                           |               |            |                                                              |              |        |  |  |  |

|         | 13       | \$TITLE(83C75                          | 1 Multi Mas   | ster I2C R | outines)                                                     |              |        |  |  |  |

|         | 15       | \$DATE(4/14/19                         |               |            |                                                              |              |        |  |  |  |

|         | 16       | \$MOD751                               | ,             |            |                                                              |              |        |  |  |  |

|         | 17       | \$DEBUG                                |               |            |                                                              |              |        |  |  |  |

|         | 18       |                                        |               |            |                                                              |              |        |  |  |  |

|         | 19       | ·************************************* | *******       | ******     | ******                                                       | *****        | *****  |  |  |  |

|         | 20       | ;                                      | 8XC751 I      | MULTIM     | ASTER I2C COMMUNICATI                                        | ONS ROUTINES |        |  |  |  |

|         | 21       | ;                                      | 2             |            | definitions                                                  |              |        |  |  |  |

|         | 22       | ·************************************* | *******       | ******     | *****                                                        | ******       | ****** |  |  |  |

|         | 23       |                                        |               |            |                                                              |              |        |  |  |  |

|         | 24       | ; Symbols (masks) for I2CFG bits.      |               |            |                                                              |              |        |  |  |  |

| 0010    | 25       |                                        |               | 4.01       |                                                              |              |        |  |  |  |

| 0010    | 26       | BTIR                                   | EQU           | 10h        | ; TIRUN bit.                                                 |              |        |  |  |  |

| 0040    | 27       | BMRQ                                   | EQU           | 40h        | ; MASTRQ bit.                                                |              |        |  |  |  |

|         | 28<br>29 |                                        |               |            |                                                              |              |        |  |  |  |

|         | 30       | ; Symbols (mas                         | ks) for I2CC  | )N hits    |                                                              |              |        |  |  |  |

|         | 31       | , Bymbols (mas                         | K3) 101 12CC  | n ons.     |                                                              |              |        |  |  |  |

| 0080    | 32       | BCXA                                   | EQU           | 80h        | ; CXA bit.                                                   |              |        |  |  |  |

| 0040    | 33       | BIDLE                                  | EQU           | 40h        | ; IDLE bit.                                                  |              |        |  |  |  |

| 0020    | 34       | BCDR                                   | EQU           | 20h        | ; CDR bit.                                                   |              |        |  |  |  |

| 0010    | 35       | BCARL                                  | EQU           | 10h        | ; CARL bit.                                                  |              |        |  |  |  |

| 0008    | 36       | BCSTR                                  | EQU           | 08h        | ; CSTR bit.                                                  |              |        |  |  |  |

| 0004    | 37       | BCSTP                                  | EQU           | 04h        | ; CSTP bit.                                                  |              |        |  |  |  |

| 0002    | 38       | BXSTR                                  | EQU           | 02h        | ; XSTR bit.                                                  |              |        |  |  |  |

| 0001    | 39       | BXSTP                                  | EQU           | 01h        | ; XSTP bit.                                                  |              |        |  |  |  |

|         | 40       |                                        |               |            |                                                              |              |        |  |  |  |

|         | 41       | ; Note:                                |               |            |                                                              |              |        |  |  |  |

|         | 42       | ;                                      |               |            |                                                              |              |        |  |  |  |

|         | 43       | -                                      |               | -          | are set by writing into this regi                            |              |        |  |  |  |

|         | 44<br>45 |                                        |               |            | bove using the MOV comman-<br>used with I2CON, as it is impl |              |        |  |  |  |

|         | 45<br>46 |                                        |               |            | setting the appropriate bit and                              | lemented by  |        |  |  |  |

|         | 40<br>47 | -                                      |               | -          | the functionality of the Read a                              | nd           |        |  |  |  |

|         | 48       |                                        |               |            | r is different, using SETB may                               |              |        |  |  |  |

|         | 40<br>49 | ; unwanted resu                        |               |            | . is anterent, using DETE IIIay                              | Judoo        |        |  |  |  |

|         | 50       | ,                                      |               |            |                                                              |              |        |  |  |  |

|         | 51       | ; Message trans                        | action status | indicatio  | ns in MSGSTAT:                                               |              |        |  |  |  |

|         | 52       | C                                      |               |            |                                                              |              |        |  |  |  |

| 0010    | 53       | SGO                                    | EQU           | 10h        | ; Started Slave message pro                                  | cessing.     |        |  |  |  |

| PPCODE1 | 83C751 | Multimaster I2C | Routines |       | 4/14/1992 PAGE 2                                        |

|---------|--------|-----------------|----------|-------|---------------------------------------------------------|

| 0011    | 54     | SRCVD           | EQU      | 11h   | ; as a slave, received a new message                    |

| 0012    | 55     | SRLNG           | EQU      | 12h   | ; received as slave a message which is too              |

|         | 56     |                 |          |       | ; long for the buffer                                   |

| 0013    | 57     | STXED           | EQU      | 13h   | ; as slave, completed message transmission.             |

| 0014    | 58     | SRERR           | EQU      | 14h   | ; bus error detected when operating as a slave.         |

|         | 59     |                 |          |       |                                                         |

| 0020    | 60     | MGO             | EQU      | 20h   | ; Started Master message processing.                    |

| 0021    | 61     | MRCVED          | EQU      | 21h   | ; As Master, received complete message from             |

|         | 62     |                 |          |       | ; slave.                                                |

| 0022    | 63     | MTXED           | EQU      | 22h   | ; As Master, completed successful message               |

|         | 64     |                 |          |       | ; transmission (slave acknowledged all data             |

|         | 65     |                 |          |       | ; bytes).                                               |

| 0023    | 66     | MTXNAK          | EQU      | 23h   | ; As Master, truncated message since slave did          |

|         | 67     |                 |          |       | ; not acknowledge a data byte.                          |

| 0024    | 68     | MTXNOSLV        | EQU      | 24h   | ; AS Master, did not receive an acknowledgement         |