# AN1265

# **Configuring the MPC2604GA Integrated** L2 Cache with the MPC106 For a 256Kbyte L2 Cache

Prepared by: Kevin Lew, Jim Lewis, and Richard Wheelus

L2 cache is fast becoming a requirement for all computers, especially for RISC architectures such as the PowerPC<sup>™</sup> family of microprocessors. Adding L2 cache to the system is one of the easiest ways to significantly increase the performance of the processor. Several factors contribute to the need for L2 cache: faster processor speeds that are multiples of the system bus frequencies so that an L1 miss results in several processor wait cycles while data are retrieved from main memory; larger applications with code or data that does not fit in the L1 cache; and larger penalties for going to main memory due to greater speed differences between DRAM main memory and SRAM L2 cache.

So, what is the best L2 cache design? Optimally, it would be one that never misses a processor read request, and one that can provide data as fast as the processor can handle it. This is not possible, realistically (at a reasonable cost, at least). However, a close approximation is possible with a good design. The MPC2604GA is an integrated secondary cache for PowerPC microprocessor based designs and has all the features that an optimally designed L2 cache should have. The MPC2604GA is the fastest L2 cache available for the PowerPC 60X bus. Due to its integration of logic, tag, and data on the same silicon, it can respond to a read hit with a 2-1-1-1 burst at 66MHz. This alone is a 17% read hit performance improvement over a 3-1-1-1 L2 cache. The MPC2604GA can also provide subsequent bursts as fast as 1-1-1-1. It is also a copy-back (write-back) design meaning that it will shorten a processor write to the speed of the L2 instead of the speed of main memory. Additionally, it is four way set associative which significantly increases the odds of a read hit over an equivalent sized direct mapped cache. The set associativity also decreases the odds of thrashing, a scenario in which the cache is constantly being rewritten from main memory because different main memory addresses are mapped to the same cache address.

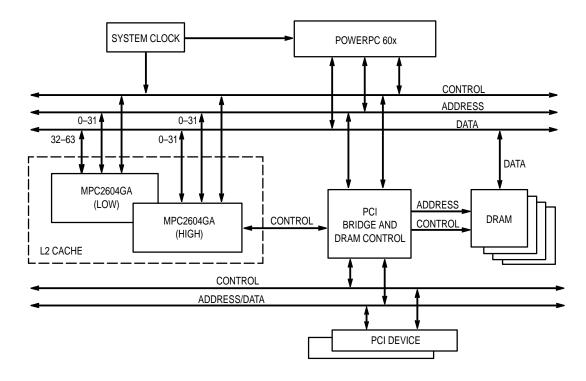

#### SYSTEM BLOCK DIAGRAM

PowerPC is a trademark of IBM Corp.

10/20/95

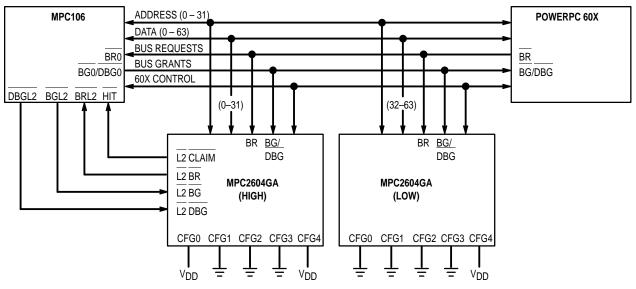

# CONNECTING THE MPC2604GA TO THE MPC106

The MPC2604GA is designed to work in conjunction with the Motorola MPC106 PCI Bridge/Memory controller. The following describes a two-chip MPC2604GA solution (256K bytes) in conjunction with a MPC106 chip and a single PowerPC processor. The MPC2604GA is configured for 2-1-1-1 mode.

Since the data bus on the MPC2604GA is 36 bits wide, the processor data bus is split into two for a 72 bit bus. The chip that receives the upper half is called the high chip, and the chip that receives the lower half is called the low chip. To configure this correctly, the CFG0 on the high chip must be tied high and tied low on the low chip. The CFG4 pin must be tied high on both chips. All other CFG pins on both chips are tied low.

For the address lines, all 32 bits must be tied to both chips. For the data lines, the upper 32 bits are tied to the high chip. The lower 32 bits go to the low chip in a similar way. For example, D63 on the processor bus is tied to D31 on the MPC2604GA.

Certain control lines are <u>tied</u> between the MPC106 and the <u>high MPC</u>2604GA chip. HIT, on <u>the MPC106</u>, is <u>tied</u> to <u>L2 CL</u>AIM <u>on the MPC2604G</u>A; BRL2 to L2 BR; BGL2 to L2 BG; and DBGL2 to L2 DBG.

The 60x control lines that must go to the MPC2604GA chips include: TS, TT0-4, TSIZ0-2, TBST, CI, WT, GBL, AACK, TA, XATS, ARTRY, SHD, and HRESET. All other input control lines may be tied high, unless other chips in the system use them.

#### SYSTEM BLOCK DIAGRAM FOR A 256KB MPC2604GA SOLUTION IN 2–1–1–1 MODE

### SPECIAL CASES

1. If there is ROM present on the processor bus, then the parity bits should not be connected. The MPC106 uses the parity bits to address the ROM, therefore, they are not used as parity. They can be left open on the MPC2604GA.

2. If the system is using a 603 processor that is running in 1:1 bus mode, then the MPC2604GA must be forced to insert a lead–off wait state. This can be accomplished by tying the CFG3 pin high. CFG3 should otherwise be set low for optimum performance.

# **CONFIGURATION REGISTER BITS**

Certain bits in the processor interface configuration register in the MPC106 have to be set to work with the MPC2604GA:

- 1. The bit named CF\_APHASE\_WS must be set low. The bit named CF\_LOOP\_SNOOP must be set high.

- 2. If CFG3 is low on the MPC2604GA, then the L2 hit delay bits on the MPC106 must be set to 1. If CFG3 is high, then the L2 hit delay bits must be set to 2.

- 3. If the system is in Fast L2 mode and CFG3 = 0, then the CF\_DPARK must be set to 0.

- 4. The setting of CF\_FAST\_L2\_MODE should be set to match the processor aft<u>er a reset</u>. To get into Fast L2 mode <u>on the MPC2604GA</u>, DRTRY must be asserted when HRESET goes high. This is the same procedure used to <u>configure</u> the processor into Fast L2 mode. Note that DBB on the MPC2604GA must be tied high to be in Fast L2 mode.

- If the system is configured in normal bus mode, and the MPC2604GA is configured for 2–1–1–1 operation, the best performance is achieved by having the MPC106 park the data bus. This can be done by setting CF\_APARK and CF\_DPARK to 1 and setting CF\_BREAD\_WS to 0.

- 6. Since the MPC2604GA has its own cache controller, the controller on the MPC106 must be disabled. This is accom-

plished by setting bit CF\_EXTERNAL\_L2 = 1. For a uniprocessor situation, bits CF\_L2\_MP (1..0) = 10 to indicate a write back cache is being used. Bits CF\_L2\_SIZE (1..0) should also be set accordingly, 00 for 256K (2 MPC2604GA chips), or 01 for 512K (4 MPC2604GA chips).

The registers L2\_CACHE\_MISS\_INHIBIT, L2\_UP-DATE\_INHIBIT, and CF\_FLUSH\_L2 in the MPC106 have no effect on the MPC2604GA. To obtain this functionality on the MPC2604GA, they must be generated by some other device.

#### **REFERENCES TO PCI SPACE**

System software must insure that cache coherency is maintained for accesses to PCI. Because the MPC2604GA does not distinguish between accesses to PCI and main memory, the processor's WIMG status bits must either (1) inhibit the cache or (2) set the W and M bits to write through mode and coherency is maintained, respectively.

# INITIALIZATION

<u>To properly initialize</u> the MPC2604GA, begin clocking with HRESET and TRST low for 16 clock cycles immediately upon power up. The MPC2604GA device will then begin an internal configuration which requires approximately 4096 clock cycles, and is idle during that time. If this is not done, improper device operation may occur.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and Motorola, Inc. Motorola, Inc. So an Equal Opportunity/Affirmative Action Employer.

How to reach us: USA / EUROPE: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447

MFAX: RMFAX0@email.sps.mot.com - TOUCHTONE (602) 244-6609 INTERNET: http://Design-NET.com

JAPAN: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, Toshikatsu Otsuki, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–3521–8315

HONG KONG: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298