# **CMOS SINGLE CHIP** 8-BIT MICROCONTROLLER

**PRELIMINARY JUNE 1997**

### **FEATURES**

- 4K x 8 ROM (IS80C51 only)

- 128 x 8 RAM

- Two 16-bit timers/counters

- Full duplex serial channel

- · Boolean processor

- Four 8-bit I/O ports, 32 I/O lines

- External memory expandable to 128K

- CMOS and TTL compatible

- Maximum speed range: 40 MHz @ Vcc = 5V

- Packages available:

- 40-pin DIP

- 44-pin PLCC

- 44-pin PQFP

#### GENERAL DESCRIPTION

The ISSI IS80C51/31 is a high-performance microcontroller fabricated using high-density CMOS technology. The CMOS IS80C51/31 is functionally compatible with the NMOS Intel 8051/31 microcontroller.

The IS80C51 is designed with 4K x 8 ROM; 128 x 8 RAM: 32 I/O lines for either multiprocessor communications, I/O expansion, or full duplex UART; two 16-bit timers/counters: a five-source, two-prioritylevel, nested interrupt structure; and an on-chip oscillator and clock circuit. The IS80C51 can be expanded using standard TTL compatible memory.

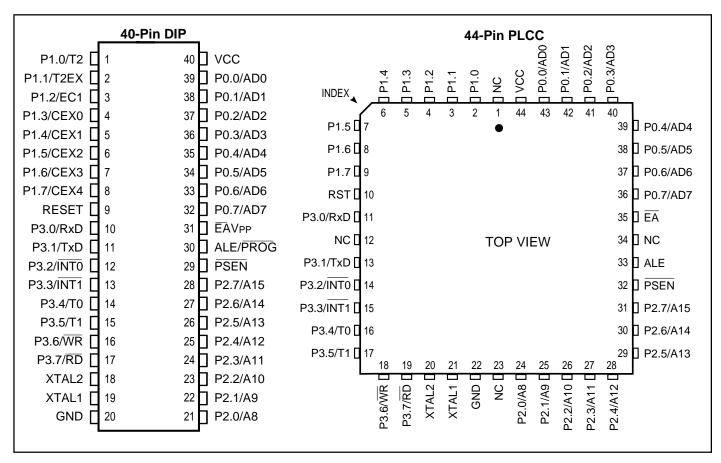

Figure 1. IS80C51/31 Pin Configurations

This document contains PRELIMINARY data. ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 1997, Integrated Silicon Solution, Inc.

Figure 1. IS80C51/31 Pin Configurations (continued)

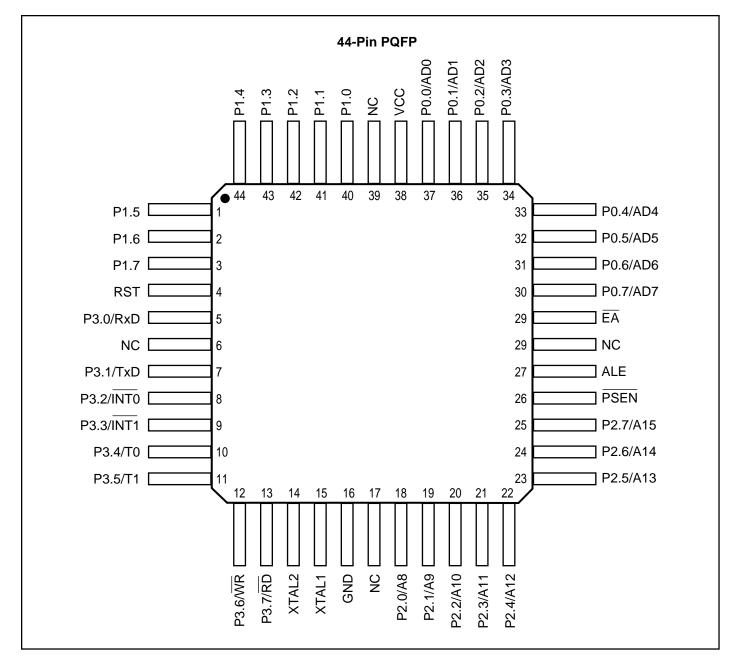

Figure 2. IS80C51 Block Diagram

## **PIN DESCRIPTION**

| Symbol    | DIP      | PLCC      | QFP     | I/O | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|----------|-----------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1.0-P1.7 | 1-8      | 2-9       | 40-44   | I/O | Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pullups. Port 1 pins that have 1s written to them are pulled high by the internal pullups and can be used as inputs. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pullups.                                                                                                                                                                                                                                                                                                                                                                       |

| RST       | 9        | 10        | 4       | I   | Reset: A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to GND permits a power-on reset using only an external capacitor. A small internal resistor permits power-on reset using only a capacitor connected to VCC.                                                                                                                                                                                                                                                                                                                                                                        |

| P3.0-P3.7 | 10-17    | 11, 13-19 | 5, 7-13 | I/O | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pullups. Port 3 pins that have 1s written to them are pulled high by the internal pullups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pullups.                                                                                                                                                                                                                                                                                                                                                                |

|           | 10       | 11        | 5       | I   | Port 3 also serves the special features of the IS80C51, as listed below:  RxD (P3.0): Serial input port  TxD (P3.4): Serial systems and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | 11<br>12 | 13<br>14  | 7<br>8  | 0   | TxD (P3.1): Serial output port INTO (P3.2): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           | 13       | 15        | 9       | i   | INT1 (P3.3): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 14       | 16        | 10      | İ   | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | 15       | 17        | 11      | I   | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | 16       | 18        | 12      | Ο   | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|           | 17       | 19        | 13      | 0   | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| XTAL 2    | 18       | 20        | 14      | 0   | <b>Crystal 2:</b> Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTAL 1    | 19       | 21        | 15      | I   | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GND       | 20       | 22        | 16      | I   | Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P2.0-P2.7 | 21-28    | 24-31     | 18-25   | I/O | Port 2: Port 2 is an 8-bit bi-directional I/O port with internal pullups. Port 2 pins that have 1s written to them are pulled high by the internal pullups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pullups. Port 2 emits the high order address byte during fetches from external program memory and during accesses to external data memory that used 16-bit addresses. In this application, it uses strong internal pullups when emitting 1s. During accesses to external data memory that use 8-bit addresses, Port 2 emits the contents of the P2 special function register. |

(continued)

## PIN DESCRIPTION (continued)

| Pin Symbol | DIP   | PLCC  | QFP   | I/O | Name and Function                                                                                                                                                                                                                                                                                                                                  |

|------------|-------|-------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSEN       | 29    | 32    | 26    | O   | Program Store Enable: The read strobe to external program memory. When the device is executing code from the external program memory, PSEN is activated twice each machine cycle except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.       |

| ALE        | 30    | 33    | 27    | I/O | Address Latch Enable: Output pulse for latching the low byte of the address during an address to the external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and be used for external timing or clocking. Note that one ALE pulse is skipped during each access external data memory.             |

| ĒĀ         | 31    | 35    | 29    | I   | <b>External Access enable:</b> $\overline{EA}$ must be externally held low to enable the device to fetch code from external program memory locations 0000H to 0FFFH. If $\overline{EA}$ is held high, the device executes from internal program memory unless the program counter contains an address greater than 0FFFH.                          |

| P0.0-P0.7  | 39-32 | 43-36 | 30-37 | I/O | <b>Port 0:</b> Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pullups when emitting 1s. |

| Vcc        | 40    | 44    | 38    | I   | <b>Power Supply:</b> This is the power supply voltage for operation.                                                                                                                                                                                                                                                                               |

### **OPERATING DESCRIPTION**

The detail description of the IS80C51 included in this description are:

- · Memory map and registers

- Timers/counters

- Serial interface

- Interrupt system

- Instruction

- Other information

## **Memory Map and Registers**

#### Memory

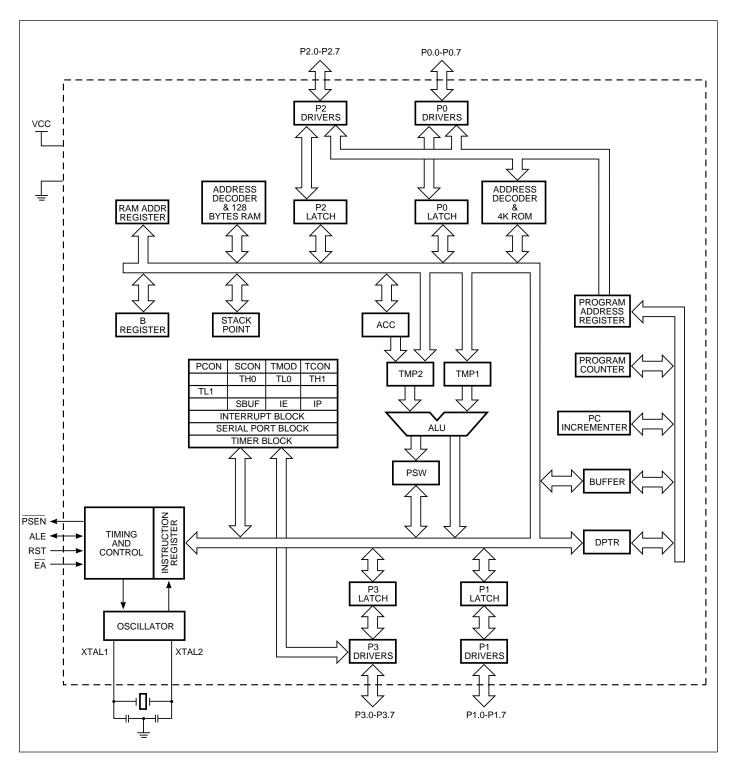

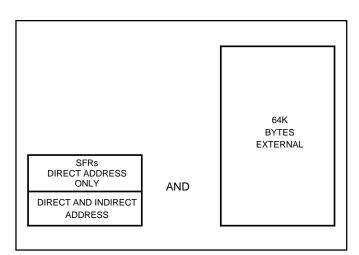

The IS80C51 has separate address spaces for program and data memory. The program memory can be up 64K bytes long. The lower 4K can reside on-chip. Figure 3 shows a map of the IS80C51 program memory.

The IS80C51 has 128 bytes of on-chip RAM, plus a number of special function registers. The lower 128 bytes can be accessed either by direct addressing or by indirect addressing. Figure 4 shows data memory origination.

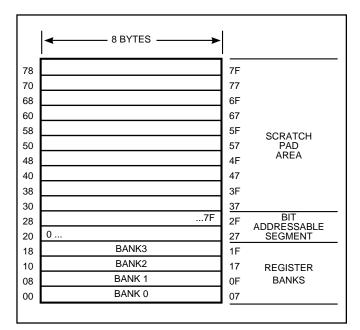

The 128 bytes of RAM which can be accessed by both direct and indirect addressing can be divided into three segments as listed below and shown in Figure 5.

Register Banks 0-3: locations 0 through 1FH (32 bytes). The device after reset defaults to register bank 0. To use the other register banks, the user must select them in software. Each register bank contains eight 1-byte registers 0-7. Reset initializes the stack point to location 07H, and is incremented once to start from 08H, which is the first register of the second bank.

Figure 3. Program Memory Access Range

Figure 4. Data Memory Access Range

- 2. Bit Addressable Area: 16 bytes have been assigned for this segment 20H-2FH. Each one of the 128 bits of this segment can be directly addressed (0-7FH). The bits can be referred to in two ways, both of which are acceptable by most assemblers. One way is referencing to bytes 20H-2FH. Thus, bits 0-7 can also be referred to as bits 20.0-20.7, and bits 8-FH are the same as 21.0-21.7, and so on. Each of the 16 bytes in this segment can also be addressed as a byte.

- 3. Scratch Pad Area: 30-7FH are available to the user as data RAM. However, if the data pointer has been initialized to this area, enough bytes should be left aside to prevent SP data destruction.

Figure 5. 128 Bytes of RAM Direct and Indirect Addressable

## **SPECIAL FUNCTION REGISTER**

| Symbol              | Description         | Direct<br>Address |                   |                   |                   | dress<br>tive f   |                   | -                 |                   |                   | Reset<br>Value |

|---------------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------|

| ACC <sup>(1)</sup>  | Accumulator         | E0H               | E7                | E6                | E5                | E4                | E3                | E2                | E1                | E0                | 00H            |

| B <sup>(1)</sup>    | B register          | F0H               | F7                | F6                | F5                | F4                | F3                | F2                | F1                | F0                | 00H            |

| DPH                 | Data pointer high   | 83H               |                   |                   |                   |                   |                   |                   |                   |                   | 00H            |

| DPL                 | Data pointer low    | 82H               |                   |                   |                   |                   |                   |                   |                   |                   | 00H            |

| IE <sup>(1)</sup>   | Interrupt enable    | А8Н               | <b>AF</b><br>EA   | AE<br>—           | AD<br>—           | AC<br>ES          | AB<br>ET1         | AA<br>EX1         | <b>A9</b><br>ET0  | <b>A8</b><br>EX0  | 0X000000B      |

| IP <sup>(1)</sup>   | Interrupt priority  | В8Н               | BF<br>—           | BE<br>—           | BD<br>—           | BC<br>PS          | BB<br>PT1         | <b>BA</b><br>PX1  | <b>B9</b><br>PT0  | <b>B8</b> PX0     | XXX00000B      |

| P0 <sup>(1)</sup>   | Port 0              | 80H               | <b>87</b><br>P0.7 | <b>86</b><br>P0.6 | <b>85</b><br>P0.5 | <b>84</b><br>P0.4 | <b>83</b><br>P0.3 | <b>82</b><br>P0.2 | <b>81</b><br>P0.1 | <b>80</b><br>P0.0 | FFH            |

| P1 <sup>(1)</sup>   | Port 1              | 90H               | <b>97</b><br>P1.7 | <b>96</b><br>P1.6 | <b>95</b><br>P1.5 | <b>94</b><br>P1.4 | <b>93</b><br>P1.3 | <b>92</b><br>P1.2 | <b>91</b><br>P1.1 | <b>90</b><br>P1.0 | FFH            |

| P2 <sup>(1)</sup>   | Port 2              | АОН               | <b>A7</b><br>P2.7 | <b>A6</b> P2.6    | <b>A5</b><br>P2.5 | <b>A4</b><br>P2.4 | <b>A3</b> P2.3    | <b>A2</b><br>P2.2 | <b>A1</b><br>P2.1 | <b>A0</b> P2.0    | FFH            |

| P3 <sup>(1)</sup>   | Port 3              | вон               | <b>B7</b><br>P3.7 | <b>B6</b><br>P3.6 | <b>B5</b><br>P3.5 | <b>B4</b><br>P3.4 | <b>B3</b><br>P3.3 | <b>B2</b><br>P3.2 | <b>B1</b><br>P3.1 | <b>B0</b><br>P3.0 | FFH            |

| PCON                | Power control       | 87H               | SMO               | ) —               | _                 | _                 | GF1               | GF0               | PD                | IDL               | 0XXX0000B      |

| PSW <sup>(1)</sup>  | Program status word | D0H               | <b>D7</b><br>CY   | <b>D6</b><br>AC   | <b>D5</b><br>F0   | <b>D4</b><br>RS1  | <b>D3</b><br>RS0  | <b>D2</b><br>OV   | D1<br>—           | <b>D0</b><br>P    | 00H            |

| SBUF                | Serial data buffer  | 99H               |                   |                   |                   |                   |                   |                   |                   |                   | XXXXXXXXB      |

| SCON <sup>(1)</sup> | Serial controller   | 98H               | <b>9F</b><br>SM0  | <b>9E</b><br>SM1  | <b>9D</b><br>SM2  | 9C<br>REN         | <b>9B</b><br>TB8  | <b>9A</b><br>RB8  | <b>99</b><br>TI   | <b>98</b><br>RI   | 00H            |

| SP                  | Stack pointer       | 81H               |                   |                   |                   |                   |                   |                   |                   |                   | 07H            |

| TCON <sup>(1)</sup> | Timer control       | 88H               | <b>8F</b><br>TF1  | <b>8E</b><br>TR1  | <b>8D</b><br>TF0  | 8C<br>TR0         | <b>8B</b><br>IE1  | <b>8A</b><br>IT1  | <b>89</b><br>IE0  | <b>88</b><br>IT0  |                |

| TH0                 | Timer high 0        | 8CH               |                   |                   |                   |                   |                   |                   |                   |                   | 00H            |

| TH1                 | Timer high 1        | 8DH               |                   |                   |                   |                   |                   |                   |                   |                   | 00H            |

| TL0                 | Timer low 0         | 8AH               |                   |                   |                   |                   |                   |                   |                   |                   | 00H            |

| TL1                 | Timer low 1         | 8BH               |                   |                   |                   |                   |                   |                   |                   |                   | 00H            |

| TMOD                | Timer mode          | 89H               | GATE              | C/T               | M1                | MO                | GATE              | C/T               | M1                | M0                | 00H            |

## Note:

1. Denotes bit addressable.

The detail description of each bit is as follows:

# **PSW**

| CY  | AC F0 | RS1 RS0 OV — P                                                                                                         |

|-----|-------|------------------------------------------------------------------------------------------------------------------------|

| CY  | PSW.7 | Carry flag                                                                                                             |

| AC  | PSW.6 | Auxiliary carry flag                                                                                                   |

| F0  | PSW.5 | Flag 0 available to the user for general purpose                                                                       |

| RS1 | PSW.4 | Register bank selector bit 1                                                                                           |

| RS0 | PSW.3 | Register bank selector bit 0 <sup>(1)</sup>                                                                            |

| OV  | PSW.2 | Overflow flag                                                                                                          |

| _   | PSW.1 | Usable as a general purpose flag                                                                                       |

| Р   | PSW.0 | Parity flag. Set/clear by hardware each instruction cycle to indicate an odd/even number of "1" bus in the accumulator |

### Note:

1. The value presented by RS0 and RS1 selects the corresponding register bank.

| _ |     |     |               |         |  |

|---|-----|-----|---------------|---------|--|

|   | RS1 | RS0 | Register Bank | Address |  |

|   | 0   | 0   | 0             | 00H-07H |  |

|   | 0   | 1   | 1             | 08H-0FH |  |

|   | 1   | 0   | 2             | 10H-17H |  |

|   | 1   | 1   | 3             | 18H-1FH |  |

# **PCON**

| 1 001 | . ■                                                                                                                                                   |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMOD  | — — GF1 GF0 PD IDL                                                                                                                                    |

| SMOD  | Double baud rate bit. If Timer 1 is used to generate baud rate and SMOD=1, the baud rate is doubled when the serial port is used in modes 1, 2, or 3. |

|       | Not implemented, reserve for future use.                                                                                                              |

|       | Not implemented, reserve for future use.                                                                                                              |

|       | Not implemented, reserve for future use.                                                                                                              |

| GF1   | General purpose flag bit.                                                                                                                             |

| GF0   | General purpose flag bit.                                                                                                                             |

| PD    | Power-down bit. Setting this bit activates power-down operation in the IS80C51.                                                                       |

| IDL   | Idle mode bit. Setting this bit activates idle mode operation in the IS80C51. If 1s are written to PD and IDL at the same time, PD takes precedence.  |

# ΙE

| EA  | _    | — ES ET1 EX1 ET0 EX0                                                                                                                                                          |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EA  | IE.7 | Disable all interrupts. If EA=0, no interrupt will be acknowledged. If EA=1, each interrupt source is individually enabled or disabled by setting or clearing its enable bit. |

|     | IE.6 | Not implemented, reserve for future use.                                                                                                                                      |

|     | IE.5 | Not implemented, reserve for future use.                                                                                                                                      |

| ES  | IE.4 | Enable or disable the serial port interrupt.                                                                                                                                  |

| ET1 | IE.3 | Enable or disable the timer 1 overflow interrupt.                                                                                                                             |

| EX1 | IE.2 | Enable or disable external interrupt 1.                                                                                                                                       |

| ET0 | IE.1 | Enable or disable the timer 0 overflow interrupt.                                                                                                                             |

| EX0 | IE.0 | Enable or disable external interrupt 0.                                                                                                                                       |

# **IP**

| _   | _    | — PS PT1 PX1 PT0 PX0                              |

|-----|------|---------------------------------------------------|

| _   | IP.7 | Not implemented, reserve for future use.          |

|     | IP.6 | Not implemented, reserve for future use.          |

| _   | IP.5 | Not implemented, reserve for future use.          |

| PS  | IP.4 | Defines the serial port interrupt priority level. |

| PT1 | IP.3 | Defines the timer 1 interrupt priority level.     |

| PX1 | IP.2 | Defines the external interrupt 1 priority level   |

| PT0 | IP.1 | Defines the timer 0 interrupt priority level.     |

| PX0 | IP.0 | Defines the external interrupt 0 priority level   |

# **TCON**

| TF1 | TR1 TF0   | TR0                                                    | IE1                           | IT1                         | IE0              | IT0               |

|-----|-----------|--------------------------------------------------------|-------------------------------|-----------------------------|------------------|-------------------|

| TF1 | TCON.7    | Timer 1 hardware overflows processor service r         | e when<br>s. Clea<br>or vecto | the tim<br>red by<br>ors to | ner/cou<br>hardw | unter 1<br>are as |

| TR1 | TCON.6    | Timer 1 r<br>by softwa<br>ON/OFF                       | are to t                      |                             |                  |                   |

| TF0 | TCON.5    | Timer 0 hardware overflows processor service r         | e when<br>s. Clea<br>or vecto | the tim<br>red by<br>ors to | ner/cou<br>hardw | unter 0<br>are as |

| TR0 | TCON.4    | Timer 0 r<br>by softwa<br>ON/OFF                       | are to t                      |                             |                  |                   |

| IE1 | TCON.3    | External<br>by softwaredge is<br>hardware<br>processes | are whe<br>detec<br>re wh     | en exte<br>cted.            | rnal in<br>Clear | terrupt<br>ed by  |

| IT1 | TCON.2    | Interrupt<br>cleared to<br>edge/low<br>interrupt.      | oy softv<br>/ level           | ware s                      | pecify           | falling           |

| IE0 | TCON.1    | External<br>by softwaredge is<br>hardware<br>processe  | are whe<br>detec<br>re wh     | n exte                      | rnal in<br>Clear | terrupt<br>ed by  |

| IT0 | TCON.0 Ir | nterrupt 0 t<br>by softw<br>low lev<br>interrupt.      | are sp                        | ecify 1                     | falling          |                   |

# **TMOD**

Timer 1

| GAII | = C/I | M1 M0     | GAIL       | C/I    | M1      | MO     |

|------|-------|-----------|------------|--------|---------|--------|

| GATE | When  | TRx (in 1 | CON) is    | set a  | nd GA   | TE=1,  |

|      | TIME  | R/COUNT   | FRx will r | ันท ดท | v while | e INTx |

Timer 0

TIMER/COUNTERx will run only while INTx pin is high (hardware control). When GATE=0, TIMER/COUNTERx will run only while TRx=1 (software control).

C/T Timer or counter selector. Cleared for timer operation (input from internal system clock). Set for counter operation (input from Tx input pin).

Mode selector bit.(2) M1 M0 Mode selector bit.(2)

### Note 2:

| M | 1 M0 | Operating mode                                                                                                                                               |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 0    | Mode 0. (13-bit timer)                                                                                                                                       |

| 0 | 1    | Mode 1. (16-bit timer/counter)                                                                                                                               |

| 1 | 0    | Mode 2. (8-bit auto-load timer/counter)                                                                                                                      |

| 1 | 1    | Mode 3. (TL0 is an 8-bit timer/counter controller by the standard timer 0 control bits. TH0 is an 8-bit timer and is controlled by timer 1 controller bits.) |

| 1 | 1    | Mode 3. (Timer/counter 1 stopped).                                                                                                                           |

SM0 SM1 SM2

REN

TB8

RB8

ΤI

RI

## **SCON**

| SM0 | SCON.7 | Serial port mode specifier. (3)                                                                                                                                                                                                                                                             |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SM1 | SCON.6 | Serial port mode specifier.(3)                                                                                                                                                                                                                                                              |

| SM2 | SCON.5 | Enable the multiprocessor communication feature in mode 2 and 3. In mode 2 or 3, if SM2 is set to 1 then RI will not be activated if the received 9th data bit (RB8) is 0. In mode 1, if SM2=1 then RI will not be activated if valid stop bit was not receive. In mode 0, SM2 should be 0. |

| REN | SCON.4 | Set/cleared by software to enable/disable reception.                                                                                                                                                                                                                                        |

| TB8 | SCON.3 | The 9th bit that will be transmitted in mode 2 and 3. Set/cleared by software.                                                                                                                                                                                                              |

| RB8 | SCON.2 | In modes 2 and 3, RB8 is the 9th data bit that was received. In mode 1, if SM2=0, RB8 is the stop bit that was received. In mode 0, RB8 is not used.                                                                                                                                        |

| TI  | SCON.1 | Transmit interrupt flag. Set by hardware at the end of the 8th bit time in mode 0, or at the beginning of the stop bit in the other modes. Must be cleared by software.                                                                                                                     |

| RI  | SCON.0 | Receive interrupt flag. Set by hardware at the end of the 8th bit time in mode 0, or halfway through the stop bit time in the other modes (except see SM2). Must be cleared                                                                                                                 |

#### Note 3:

| SM0 | SM1 | MODE | Description    | Baud rate          |

|-----|-----|------|----------------|--------------------|

| 0   | 0   | 0    | Shift register | Fosc/12            |

| 0   | 1   | 1    | 8-bit UART     | Variable           |

| 1   | 0   | 2    | 9-bit UART     | Fosc/64 or Fosc/32 |

| 1   | 1   | 3    | 9-bit UART     | Variable           |

by software.

## **Timers/counters**

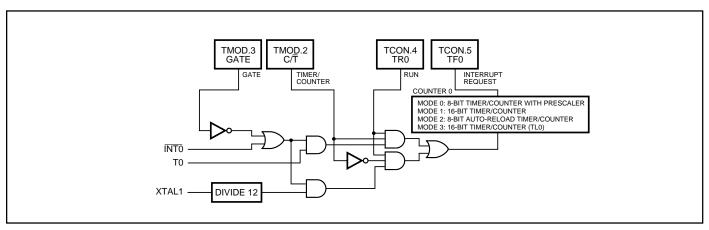

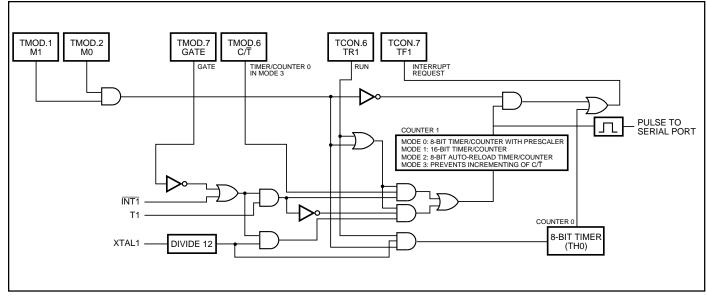

The IS80C51 contains two 16-bit counters for measuring time intervals, measuring pulse widths, counting events and generating precise, periodic interrupt request.

The operating mode is listed below.

#### Timer 1/Counter 1:

Timer 1/Counter 1 can be configured in one of four modes:

- Mode 0: Provides an 8-bit counter with a divide-by-32 prescaler or an 8-bit timer with a divide-by-32 prescaler. A read/write of TH1 accesses counter 1's bits 12-5. A read/write of TL1 accesses counter 1's bits 7-0. TL1 bits 4-0 are the prescaler (counter 1's 4-0) while bits 7-5 are indeterminate and should be ignored. The programmer should clear the prescaler (counter 1's bits 4-0) before setting the run flag.

- Mode 1: Configures counter 1 as a 16-bit timer/counter.

- Mode 2: Configures counter 1 as an 8-bit autoreload value. TH1 holds the reload value. TL1 is incremented. The value in TH1 is reload onto TL1 when TL1 overflows from all ones.

- Mode 3: When counter 1's mode is repro-grammed to mode 3 (from mode 0, 1 or 2), it disables the incrementing of the counter. This mode is provided as an alternative to use TR1 bit (TCON.6) to start and stop counter 1.

The serial port receives a pulse each time that counter 1 overflows. The standard UART mode divides this pulse rate to generate the transmission rate.

### Counter 0/ Timer 0:

Counter 0 can also be configured in one of four modes:

Mode 0-2: Mode 0-2 are the same as for counter 1.

Mode 3: In mode 3, the configure of TH0 is not affected by the bits in TMOD or TCON. It is configured solely as an 8-bit timer that is enabled for incrementing by TCON's TR1 bit. Upon TH0's overflow the TF1 flag gets set. Thus, neither TR1 nor TF1 is available to counter 1 when counter 0 is in mode 3. The function of

TR1 can be done by placing counter 1 in mode 3, so only the function of TF1 is actually given up by counter 1. In mode 3, TL0 is configured as an 8-bit timer/counter and is controlled, as usual, by the GATE (TMOD. 3), C/ (TMOD.2), TR0 (TCON.4) and TF0 (TCON.5) control bits.

The use of the timers/counters is determined by two 8-bit registers, TMOD and TCON is shown in SFR. The counter input circuit is shown in Figures 6 and 7.

Figure 6. Timer/event Counter 0 Control and Status Flag Circiut

Figure 7. Timer/event Counter 1 Control and Status Flag Circiut

### **Serial Interface**

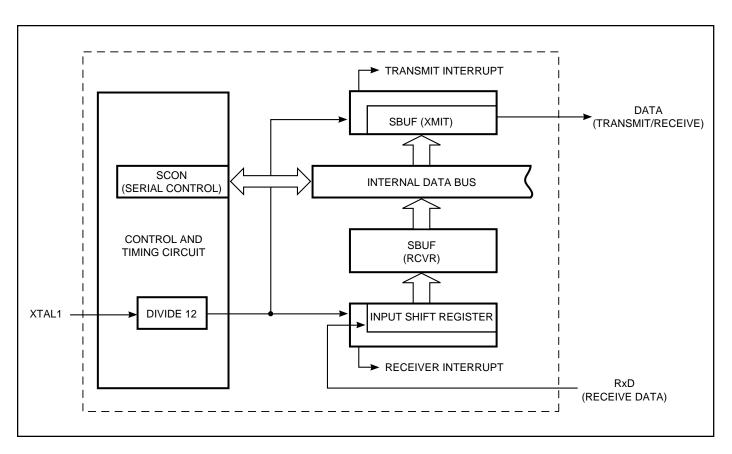

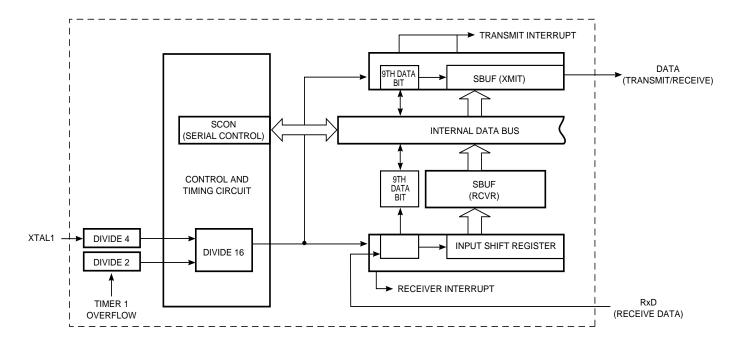

The IS80C51 has a serial I/O port that is useful for serial linking peripheral devices as well as multiple IS80C51s through standard asynchronous protocol with full-duplex operations. The data for transmission to and from reception reside in the serial port buffer register (SBUF). The serial port control and the monitoring of its status is provided by the serial port control register (SCON). The contents of the 8-bit SCON register are shown in SFR.

The IS80C51 has a serial channel useful for serially linking UART (universal asynchronous receiver/transmitter) devices and for expanding I/O. The full-

duplex serial I/O port can be programmed to function in one of four operating modes:

Mode 0: Synchronous I/O expansion using TTL

or CMOS shift registers.

Mode 1: UART interface with 10-bit frame and variable transmission rate.

Mode 2: UART interface with 11-bit frame and fixed transmission rate.

Mode 3: UART interface with 11-bit frame and variable transmission rate.

The serial interface circuit is shown in Figures 8 and 9. The use of the serial interface is determined by TCON and PCON registers is shown in SFR.

Figure 8. Serial Port: Synchronous Mode 0

Figure 9. Serial Port: UART Mode 1, 2, and 3

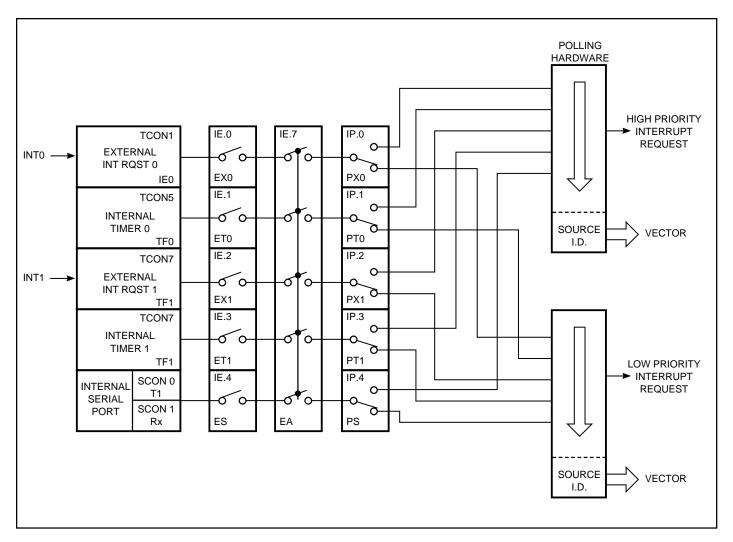

## **Interrupt System**

External events and the real-time driven on-chip peripherals require service by the CPU asynchronous to the execution of any particular section code. To tie the asynchronous activities of these functions to normal program execution, a sophisticated multiple-

source, two-priority-level, nested interrupt system is provided. The interrupt system is shown in Figure 10. The interrupt request flag and program memory location of interrupt service program is shown in the table below:

| Interrupt Source            | Request Flag | Bit Location | Start Address |

|-----------------------------|--------------|--------------|---------------|

| External Request 0          | IE0          | TCON.1       | 3 (0003H)     |

| Internal Timer 0/Counter 0  | TF0          | TCON.5       | 11 (000BH)    |

| External Request 1          | IE1          | TCON.3       | 19 (0013H)    |

| Internal Timer 1/Counter 1  | TF1          | TCON.7       | 27 (001BH)    |

| Internal Serial Port (XMIT) | TI           | SCON.1       | 35 (0023H)    |

| Internal Serial Port (RCVR) | RI           | SCON.0       | 35 (0023H)    |

Figure 10. Interrupt System

#### ADDITIONAL INFORMATION

#### Idle mode

In idle mode, the CPU puts itself to sleep while all the on-chip perpherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the Special Function Register remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.

It should be noted that when idle is terminated by a hardware reset, the device normally resumes program exection, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when idle is terminated by reset, the instruction following the one that invokes idle should not be one that writes to a port pin or to external memory. The status of external pins is shown in the following table.

#### Power-down mode

In the power-down mode the oscillator is stopped, and the instruction that invokes power down is the last instruction executed. The on-chip RAM and special function register retain their values until the power down mode is terminated.

The only exit from power-down mode is a hardware reset. Reset redefines the SFR but does not change the on-chip RAM. The reset should not be activated before VCC is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize. The status of the external pins during idle and power-down mode is shown in the following table.

## Status of the External Pins during Idle and Power-down modes.

| Mode       | Memory   | ALE | PSEN | PORT 0 | PORT 1 | PORT 2  | PORT 3 |

|------------|----------|-----|------|--------|--------|---------|--------|

| Idle       | Internal | 1   | 1    | Data   | Data   | Data    | Data   |

| Idle       | External | 1   | 1    | Float  | Data   | Address | Data   |

| Power-down | Internal | 0   | 0    | Data   | Data   | Data    | Data   |

| Power-down | External | 0   | 0    | Float  | Data   | Data    | Data   |

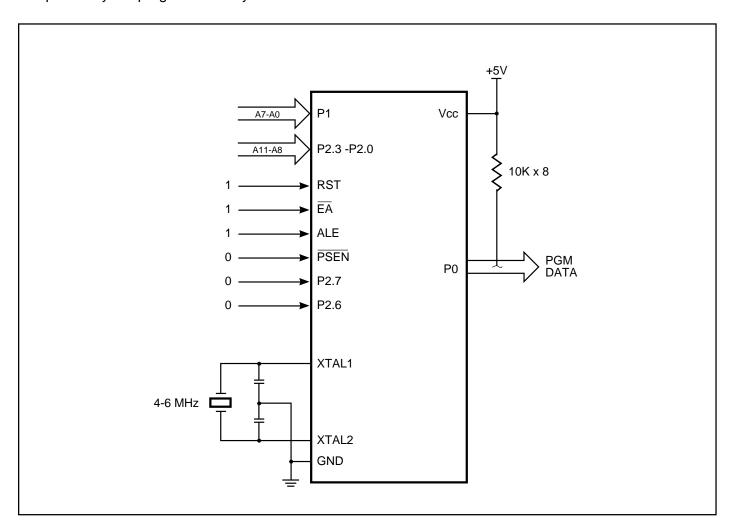

## **ROM Verification**

The address of the program memory location to be read is applied to Port 1 and pins P2.3-P2.0. The other pins should be held at the "Verify" level are indicated in Figure 11. The contents of the addressed locations exits on Port 0. External pullups are required on Port 0 for this operation. Figure 11 shows the setup to verify the program memory.

Figure 11. ROM Verification

## ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Parameter                               | Value        | Unit |

|--------|-----------------------------------------|--------------|------|

| VTERM  | Terminal Voltage with Respect to GND(2) | -2.0 to +7.0 | V    |

| TBIAS  | Temperature Under Bias <sup>(3)</sup>   | 0 to +70     | °C   |

| Тѕтс   | Storage Temperature                     | -65 to +125  | °C   |

| Рт     | Power Dissipation                       | 1.5          | W    |

#### Note:

- Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to -2.0V for periods less than 20 ns. Maximum DC voltage on output pins is Vcc + 0.5V which may overshoot to Vcc + 2.0V for periods less than 20 ns.

- 3. Operating temperature is for commercial products only defined by this specification.

### OPERATING RANGE(1)

| Range      | Ambient Temperature | Vcc      | Oscillator Frequency |  |

|------------|---------------------|----------|----------------------|--|

| Commercial | 0°C to +70°C        | 5V ± 10% | 3.5 to 40 MHz        |  |

#### Note:

1. Operating ranges define those limits between which the functionality of the device is guaranteed.

## **DC CHARACTERISTICS**

$(T_A = 0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5V \pm 10\%; GND = 0V)$

| Symbol             | Parameter                                        | Test conditions                              | Min          | Max             | Unit |

|--------------------|--------------------------------------------------|----------------------------------------------|--------------|-----------------|------|

| VIL                | Input low voltage                                |                                              | -0.5         | 0.2Vcc - 0.1    | V    |

| VIL1               | Input low voltage                                |                                              | -0.5         | 0.2Vcc - 0.3    | V    |

| VIH                | Input high voltage<br>(All except XTAL1, RST)    |                                              | 0.3Vcc + 0.9 | Vcc + 0.5       | V    |

| VIH1               | Input high voltage (XTAL1, EA)                   |                                              | 0.6Vcc       | Vcc + 0.5       | V    |

| Vsc++              | RST positive schmitt-trigger threshold voltage   |                                              | 0.7Vcc       | Vcc + 0.5       | V    |

| Vsch-              | RST negative schmitt-trigger threshold voltage   |                                              | 0            | 0.2Vcc          | V    |

| VoL <sup>(1)</sup> | Output low voltage                               | IoL = 100 μA                                 | _            | 0.3             | V    |

|                    | (Ports 1, 2, and 3)                              | IoL = 1.6 mA                                 | _            | 0.45            | V    |

|                    | ·                                                | IoL = 3.5 mA                                 | _            | 1.0             | V    |

| Vol1(1)            | Output low voltage                               | IoL = 200 μA                                 | _            | 0.3             | V    |

|                    | (Port 0, ALE, PSEN)                              | loL = 3.2 mA                                 | _            | 0.45            | V    |

|                    | ·                                                | IoL = 7.0 mA                                 | _            | 1.0             | V    |

| Vон                | Output high voltage<br>(Port 1, 2, 3, ALE, PSEN) | $I_{OH} = -10 \mu A$<br>$V_{CC} = 4.5V-5.5V$ | 0.9Vcc       | <del>_</del>    | V    |

|                    |                                                  | IoL = -25 μA                                 | 0.75Vcc      | _               | V    |

|                    |                                                  | $IoL = -60 \mu A$                            | 2.4          | _               | V    |

| Voн1               | Output high voltage<br>(Port 0, ALE, PSEN)       | $IOH = -80 \mu A$<br>VCC = 4.5V-5.5V         | 0.9Vcc       | _               | V    |

|                    |                                                  | Іон = –300 μА                                | 0.75Vcc      |                 | V    |

|                    |                                                  | Іон = –800 μА                                | 2.4          | <del>_</del>    | V    |

| lıL                | Logical 0 input current (Port 1, 2, 3)           | VIN = 0.45V                                  | _            | <b>-</b> 50     | μΑ   |

| lы                 | Input leakage current (Port 0)                   | 0.45V < VIN < VCC                            | -10          | +10             | μΑ   |

| lτι                | Logical 1-to-0 transition current (Port 1, 2, 3) | VIN = 2.0V                                   | <del>_</del> | <del></del> 650 | μΑ   |

| RRST               | RST pulldown resister                            |                                              | 50           | 300             | Kohm |

#### Note:

1. Under steady state (non-transient) conditions, lol must be externally limited as follows:

Maximum Io∟ per port pin: ..... 10 mA

Maximum IoL per 8-bit port

Port 0: ..... 26 mA

Port 1, 2, 3:........... 15 mA Maximum total lo<sub>L</sub> for all output pins:.... 71 mA

If lole exceeds the test condition, Vole may exceed the related specification. Pins are not guaranteed to sink greater than the listed test conditions.

## POWER SUPPLY CHARACTERISTICS

| Symbol | Parameter               | Test conditions | Min          | Max | Unit |

|--------|-------------------------|-----------------|--------------|-----|------|

| Icc    | Power supply current(1) |                 |              |     |      |

|        | Active mode             | 12 MHz          |              | 20  | mA   |

|        |                         | 20 MHz          | _            | 32  | mA   |

|        |                         | 24 MHz          | _            | 38  | mA   |

|        |                         | 40 MHz          | _            | 62  | mA   |

|        | Idle mode               | 12 MHz          |              | 5   | mΑ   |

|        |                         | 20 MHz          | <del>_</del> | 7.6 | mΑ   |

|        |                         | 24 MHz          | _            | 9   | mA   |

|        |                         | 40 MHz          | <del></del>  | 15  | mΑ   |

|        | Power-down mode         |                 | _            | 100 | μΑ   |

#### Note:

1. See Figures 12, 13, 14, and 15 for Icc test conditiions.

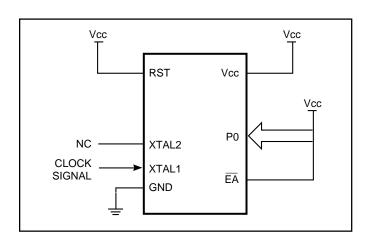

Figure 12. Active Mode

## IS80C51/31 Active Current

| Clock  | Vcc = 4.5V | Vcc = 5.0V | Vcc = 5.5V |

|--------|------------|------------|------------|

| 2 MHz  | 0.71 mA    | 0.81 mA    | 0.94 mA    |

| 4 MHz  | 1.38 mA    | 1.59 mA    | 1.83 mA    |

| 6 MHz  | 2.05 mA    | 2.37 mA    | 2.71 mA    |

| 8 MHz  | 2.65 mA    | 3.08 mA    | 3.49 mA    |

| 10 MHz | 3.69 mA    | 4.23 mA    | 4.81 mA    |

| 12 MHz | 4.00 mA    | 4.62 mA    | 5.24 mA    |

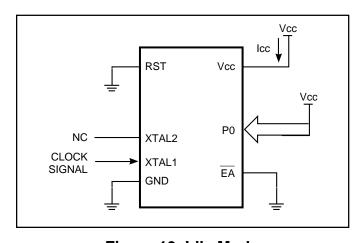

Figure 13. Idle Mode

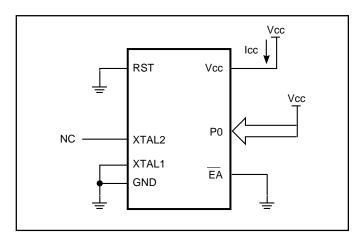

Figure 14. Power-down Mode

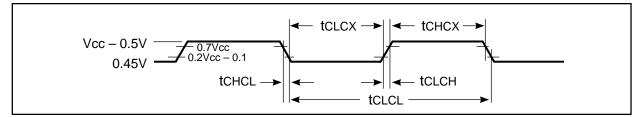

**Figure 15. Icc Test Conditions**

Clock signal waveform for lcc tests in active and idle mode (tclch = tchcl = 5 ns)

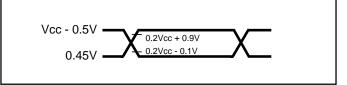

## **AC CHARACTERISTICS**

(TA = 0°C to 70°C; Vcc = 5V  $\pm$  10%; GND = 0V; CL for Port 0, ALE and  $\overline{\text{PSEN}}$ ;

Outputs = 100 pF; C<sub>L</sub> for other outputs = 80 pF)

## **External Memory Characteristics**

|               |                              | 24 N | 1Hz | 40 MHz         |             |            |      |

|---------------|------------------------------|------|-----|----------------|-------------|------------|------|

|               |                              | Clo  | ck  | Clock          | Variable (  | Oscillator |      |

| Symbol        | Parameter                    | Min  | Max | Min Max        | Min         | Max        | Unit |

| 1/tclcl       | Oscillator frequency         |      | _   |                | 3.5         | 40         | MHz  |

| tlhll         | ALE pulse width              | 43   |     | 10 —           | 2tclcl-40   |            | ns   |

| tavll         | Address valid to ALE low     | 2    |     | -15 <b>—</b>   | tclcl-40    |            | ns   |

| tLLAX         | Address hold after ALE low   | 7    |     | -10 <b>—</b>   | tclcl-35    |            | ns   |

| tlliv         | ALE low to valid instr in    | _    | 105 | <del> 55</del> | <del></del> | 3tclcl-20  | ns   |

| tllpl         | ALE low to PSEN low          | 2    |     | -15 <b>—</b>   | tclcl-40    |            | ns   |

| tPLPH         | PSEN pulse width             | 80   |     | 30 —           | 3tclcl-45   |            | ns   |

| tpliv         | PSEN low to valid instr in   | _    | 73  | — 40           | <del></del> | 2tclcl-10  | ns   |

| tpxix         | Input instr hold after PSEN  | 0    |     | 0— —           | 0           |            | ns   |

| tPXIZ         | Input instr float after PSEN | _    | 73  | — 40           | <del></del> | 2tclcl-10  | ns   |

| taviv         | Address to valid instr in    | _    | 147 | — 80           | <del></del> | 4tclcl-20  | ns   |

| <b>t</b> PLAZ | PSEN low to address float    | _    | 10  | — 10           | <del></del> | 10         | ns   |

| trlrh         | RD pulse width               | 150  |     | 50 —           | 6tclcl-100  |            | ns   |

| twlwh         | WR pulse width               | 150  |     | 50 —           | 6tclcl-100  |            | ns   |

| trldv         | RD low to valid data in      | _    | 114 | — 30           | <del></del> | 5tclcl-95  | ns   |

| trhdx         | Data hold after RD           | 0    |     | 0 —            | 0           |            | ns   |

| tRHDZ         | Data float after RD          | _    | 63  | — 30           | <del></del> | 2tclcl-70  | ns   |

| tlldv         | ALE low to valid data in     | _    | 244 | — 110          | <del></del> | 8tclcl-90  | ns   |

| tavdv         | Address to valid data in     | _    | 285 | — 135          | <del></del> | 9tclcl-90  | ns   |

| tllwl         | ALE low to RD or WR low      | 75   | 175 | 25 125         | 3tclcl-50   | 3tclcl+50  | ns   |

| tavwl         | Address to RD or WR low      | 77   |     | 10 —           | 4tclcl-90   |            | ns   |

| tqvwx         | Data valid to WR transition  | 2    |     | -1.5 <b>—</b>  | tclcl-40    |            | ns   |

| twhqx         | Data hold after WR           | 2    | _   | -1.5 <b>—</b>  | tclcl-40    |            | ns   |

| tqvwh         | Data valid to WR high        | 219  | _   | 105 —          | 7tclcl-70   |            | ns   |

| tRLAZ         | RD low to address float      | _    | 63  | — 30           | _           | 2tclcl-20  | ns   |

| twhlh         | RD or WR high to ALE high    | 2    | 82  | <b>-15</b> 65  | tclcl-40    | tclcl+40   | ns   |

## **Serial Port Timing: Shift Register Mode**

|        |                                          | 24 MHz<br>Clock |     | 40 MHz<br>Clock |      | Variable Oscillator |              |      |

|--------|------------------------------------------|-----------------|-----|-----------------|------|---------------------|--------------|------|

| Symbol | Parameter                                | Min             | Max | Min N           | Vlax | Min                 | Max          | Unit |

| txlxl  | Serial port clock cycle time             | 500             | _   | _               | _    | 12tclcl             | <del>_</del> | ns   |

| tqvxh  | Output data setup to clock rising edge   | 284             | _   | 117             | _    | 10tclcL-133         | _            | ns   |

| txhqx  | Output data hold after clock rising edge | 33              | _   | 0               | _    | 2tclcl-50           | _            | ns   |

| txhdx  | Input data hold after clock rising edge  | 0               | _   | 0               | _    | 0                   | _            | ns   |

| txhdv  | Clock rising edge to input data valid    | _               | 284 | _ ′             | 117  | <del>_</del>        | 10tclcL-133  | ns   |

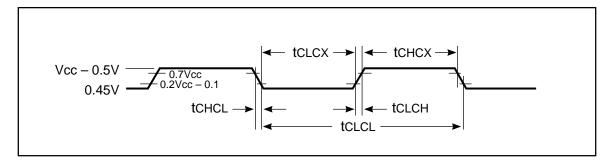

## **External Clock Drive**

| Symbol  | Parameter            | Min | Max      | Unit |

|---------|----------------------|-----|----------|------|

| 1/tclcl | Oscillator Frequency | 3.5 | 40       | MHz  |

| tchcx   | High time            | 10  | <u> </u> | ns   |

| tclcx   | Low time             | 10  | _        | ns   |

| tclch   | Rise time            | _   | 10       | ns   |

| tchcl   | Fall time            | _   | 10       | ns   |

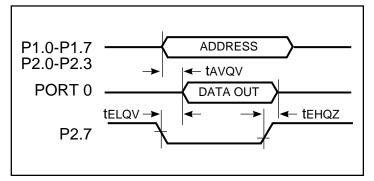

## **ROM Verification Characteristics**

| Symbol        | Parameter                | Min | Max     | Unit |

|---------------|--------------------------|-----|---------|------|

| 1/tclcl       | Oscillator Frequency     | 2.5 | 40      | MHz  |

| tavqv         | Address to data valid    |     | 48tclcl |      |

| telqv         | ENABLE low to data valid |     | 48tclcl |      |

| <b>t</b> EHQZ | Data float after ENABLE  | 0   | 48tclcl |      |

## **TIMING WAVEFORMS**

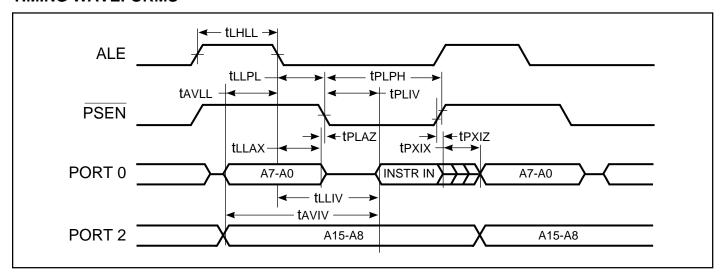

Figure 16. External Program Memory Read Cycle

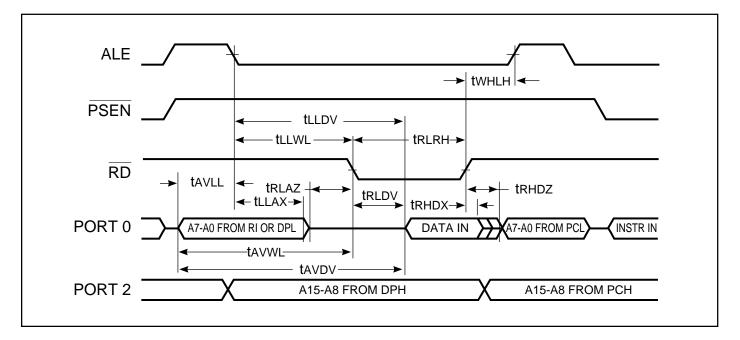

Figure 17. External Data Memory Read Cycle

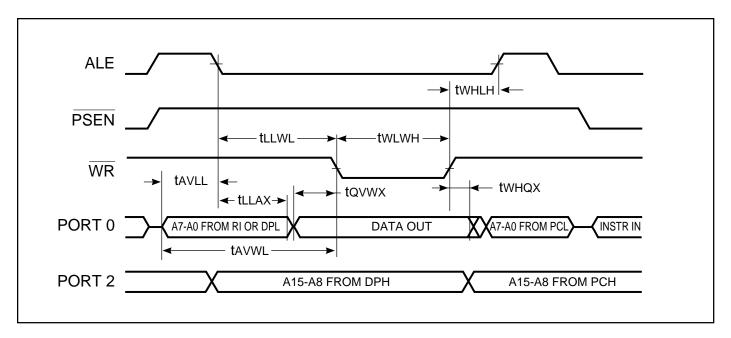

Figure 18. External Data Memory Write Cycle

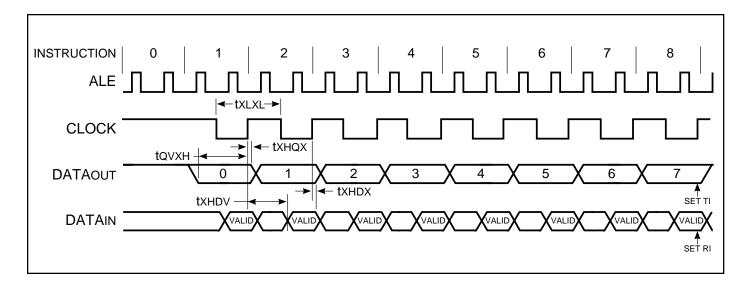

Figure 19. Shift Register Mode Timing Waveforms

Figure 20. External Clock Drive Waveform

Figure 21. ROM Verification Waveforms

Figure 22. AC Test Point

## Note:

1. AC inputs during testing are driven at VCC – 0.5V for logic "1" and 0.45V for logic "0". Timing measurements are made at VIH min for logic "1" and max for logic "0".

## **ORDERING INFORMATION**

| Speed  | Order Part Number                           | Package                                                                                    |

|--------|---------------------------------------------|--------------------------------------------------------------------------------------------|

| 12 MHz | IS80C51-12PL<br>IS80C51-12PQ<br>IS80C51-12W | PLCC – Plastic Leaded Chip Carrier<br>PQFP - Plastic Qual Flat Pack<br>600-mil Plastic DIP |

| 20 MHz | IS80C51-20PL<br>IS80C51-20PQ<br>IS80C51-20W | PLCC – Plastic Leaded Chip Carrier<br>PQFP - Plastic Qual Flat Pack<br>600-mil Plastic DIP |

| 24 MHz | IS80C51-24PL<br>IS80C51-24PQ<br>IS80C51-24W | PLCC – Plastic Leaded Chip Carrier<br>PQFP - Plastic Qual Flat Pack<br>600-mil Plastic DIP |

| 40 MHz | IS80C51-40PL<br>IS80C51-40PQ<br>IS80C51-40W | PLCC – Plastic Leaded Chip Carrier<br>PQFP - Plastic Qual Flat Pack<br>600-mil Plastic DIP |

| 12 MHz | IS80C31-12PL<br>IS80C31-12PQ<br>IS80C31-12W | PLCC – Plastic Leaded Chip Carrier<br>PQFP - Plastic Qual Flat Pack<br>600-mil Plastic DIP |

| 20 MHz | IS80C31-20PL<br>IS80C31-20PQ<br>IS80C31-20W | PLCC – Plastic Leaded Chip Carrier<br>PQFP - Plastic Qual Flat Pack<br>600-mil Plastic DIP |

| 24 MHz | IS80C31-24PL<br>IS80C31-24PQ<br>IS80C31-24W | PLCC – Plastic Leaded Chip Carrier<br>PQFP - Plastic Qual Flat Pack<br>600-mil Plastic DIP |

| 40 MHz | IS80C31-40PL<br>IS80C31-40PQ<br>IS80C31-40W | PLCC – Plastic Leaded Chip Carrier<br>PQFP - Plastic Qual Flat Pack<br>600-mil Plastic DIP |

## Integrated Silicon Solution, Inc.

2231 Lawson Lane Santa Clara, CA 95054 Fax: (408) 588-0806

Toll Free: 1-800-379-4774 http://www.issiusa.com