# CAT64LC10/20/40

# 1K/2K/4K-Bit Serial E2PROM

# **FEATURES**

- SPI Bus Compatible

- **Low Power CMOS Technology**

- 2.5V to 6.0V Operation

- Self-Timed Write Cycle with Auto-Clear

- **■** Hardware Reset Pin

- Hardware and Software Write Protection

- **■** Commercial and Industrial Temperature Ranges

- **Power-Up Inadvertant Write Protection**

- RDY/BUSY Pin for End-of-Write Indication

- 1,000,000 Program/Erase Cycles

- 100 Year Data Retention

## **DESCRIPTION**

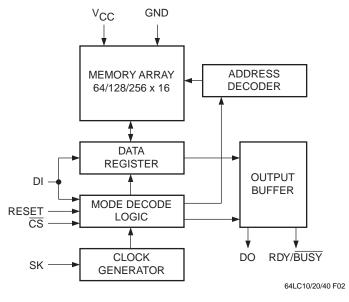

The CAT64LC10/20/40 is a 1K/2K/4K-bit Serial E<sup>2</sup>PROM which is configured as 64/128/256 registers by 16 bits. Each register can be written (or read) serially by using the DI (or DO) pin. The CAT64LC10/20/40 is manufactured using Catalyst's advanced CMOS E<sup>2</sup>PROM float-

ing gate technology. It is designed to endure 1,000,000 program/erase cycles and has a data retention of 100 years. The device is available in 8-pin DIP or SOIC packages.

### **PIN CONFIGURATION**

#### DIP Package (P) SOIC Package (J) SOIC Package (S) <u>cs</u> □•1 RDY/BUSY -1 CS C RESET □ Vcc □ Vcc 2 7 Vcc ⊏ 2 7 7 SK □ ☐ RDY/BUSY ☐ GND SK [ RDY/BUSY 3 6 3 6 3 6 ☐ RESET cs 🖂 DO 🗀 DI 🖂 🗀 RESET 5 5 DO 🗆 ☐ GND SK 🖂 DO [ ☐ GND 5064 FHD F01

# **PIN FUNCTIONS**

| Pin Name | Function                    |

|----------|-----------------------------|

| CS       | Chip Select                 |

| SK       | Clock Input                 |

| DI       | Serial Data Input           |

| DO       | Serial Data Output          |

| Vcc      | +2.5V to +6.0V Power Supply |

| GND      | Ground                      |

| RESET    | Reset                       |

| RDY/BUSY | Ready/BUSY Status           |

# **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias –55°C to +125°C                                                  |

|-----------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                       |

| Voltage on any Pin with Respect to Ground <sup>(1)</sup> 2.0V to +V <sub>CC</sub> +2.0V |

| $V_{CC}$ with Respect to Ground –2.0V to +7.0V                                          |

| Package Power Dissipation Capability (Ta = 25°C)                                        |

| Lead Soldering Temperature (10 secs) 300°C                                              |

| Output Short Circuit Current <sup>(2)</sup> 100 mA                                      |

# \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

#### **RELIABILITY CHARACTERISTICS**

| Symbol                         | Parameter          | Min.      | Max. | Units       | Reference Test Method         |

|--------------------------------|--------------------|-----------|------|-------------|-------------------------------|

| N <sub>END</sub> (3)           | Endurance          | 1,000,000 |      | Cycles/Byte | MIL-STD-883, Test Method 1033 |

| T <sub>DR</sub> <sup>(3)</sup> | Data Retention     | 100       |      | Years       | MIL-STD-883, Test Method 1008 |

| V <sub>ZAP</sub> (3)           | ESD Susceptibility | 2000      |      | Volts       | MIL-STD-883, Test Method 3015 |

| I <sub>LTH</sub> (3)(4)        | Latch-Up           | 100       |      | mA          | JEDEC Standard 17             |

# **CAPACITANCE** ( $T_A = 25^{\circ}C$ , f= 1.0 MHz, $V_{CC} = 6.0 \text{V}$ )

| Symbol               | Test                                    | Max. | Units | Conditions           |

|----------------------|-----------------------------------------|------|-------|----------------------|

| C <sub>I/O</sub> (3) | Input/Output Capacitance (DO, RDY/BUSY) | 8    | pF    | $V_{I/O} = 0V$       |

| C <sub>IN</sub> (3)  | Input Capacitance (CS, SK, DI, RESET)   | 6    | pF    | V <sub>IN</sub> = 0V |

#### Note

- (1) The minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to -2.0V for periods of less than 20 ns. Maximum DC voltage on output pins is  $V_{CC}$  +0.5V, which may overshoot to  $V_{CC}$  +2.0V for periods of less than 20 ns.

- (2) Output shorted for no more than one second. No more than one output shorted at a time.

- (3) This parameter is tested initially and after a design or process change that affects the parameter.

- (4) Latch-up protection is provided for stresses up to 100 mA on address and data pins from -1V to V<sub>CC</sub> +1V.

# D.C. OPERATING CHARACTERISTICS

$V_{CC}$  = +2.5V to +6.0V, unless otherwise specified.

|                                |                                         |          | Limits                |      |                       |       |                                              |

|--------------------------------|-----------------------------------------|----------|-----------------------|------|-----------------------|-------|----------------------------------------------|

| Sym.                           | Parameter                               |          | Min.                  | Тур. | Max.                  | Units | <b>Test Conditions</b>                       |

| Icc                            | Operating Current                       | 2.5V     |                       |      | 0.4                   | mA    | f <sub>SK</sub> = 250 kHz                    |

|                                | EWEN, EWDS, READ                        | 6.0V     |                       |      | 1                     | mA    | f <sub>SK</sub> = 1 MHz                      |

| ICCP                           | Program Current                         | 2.5V     |                       |      | 2                     | mA    |                                              |

|                                |                                         | 6.0V     |                       |      | 3                     | mA    |                                              |

| I <sub>SB</sub> <sup>(1)</sup> | Standby Current                         |          |                       |      | 0                     | μΑ    | $\frac{V_{IN}}{CS} = GND \text{ or } V_{CC}$ |

| ILI                            | Input Leakage Current                   |          |                       |      | 2                     | μА    | $V_{IN} = GND \text{ to } V_{CC}$            |

| ILO                            | Output Leakage Current                  |          |                       |      | 10                    | μА    | $V_{OUT} = GND$ to $V_{CC}$                  |

| VIL                            | Low Level Input Voltage, DI             |          | -0.1                  |      | V <sub>CC</sub> x 0.3 | V     |                                              |

| V <sub>IH</sub>                | High Level Input Voltag                 | ge, DI   | V <sub>CC</sub> x 0.7 |      | V <sub>CC</sub> + 0.5 | V     |                                              |

| VIL                            | Low Level Input Voltag<br>CS, SK, RESET | e,       | -0.1                  |      | V <sub>CC</sub> x 0.2 | V     |                                              |

| V <sub>IH</sub>                | High Level Input Voltag                 | ge,      | V <sub>CC</sub> x 0.8 |      | V <sub>CC</sub> + 0.5 | V     |                                              |

| V <sub>OH</sub> <sup>(2)</sup> | High Level Output Volt                  | age 2.5V | V <sub>CC</sub> - 0.3 |      |                       | V     | I <sub>OH</sub> = -10μA                      |

|                                | 6.0V                                    |          | V <sub>CC</sub> - 0.3 |      |                       |       | I <sub>OH</sub> = -10μA                      |

|                                |                                         |          | 2.4                   |      |                       |       | I <sub>OH</sub> = -400μA                     |

| V <sub>OL</sub> <sup>(2)</sup> | Low Level Output Volta                  | age 2.5V |                       |      | 0.4                   | V     | I <sub>OL</sub> = 10μA                       |

|                                |                                         | 6.0V     |                       |      | 0.4                   | V     | I <sub>OL</sub> = 2.1mA                      |

Note: (1) Standby Current ( $I_{SB}$ ) =  $0\mu A$  (<900nA) \_\_\_\_ (2)  $V_{OH}$  and  $V_{OL}$  spec applies to READY/BUSY pin also

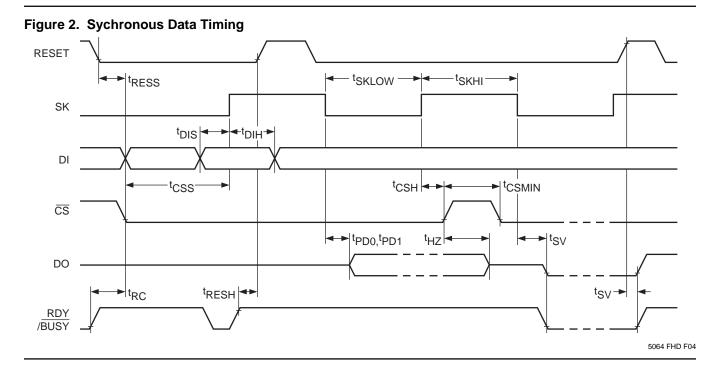

### **A.C. OPERATING CHARACTERISTICS**

$V_{CC}$  = +2.5V to +6.0V, unless otherwise specified.

|                     |                                 |           |      | Limits |      |       |

|---------------------|---------------------------------|-----------|------|--------|------|-------|

| Symbol              | Parameter                       |           | Min. | Тур.   | Max. | Units |

| tcss                | CS Setup Time                   |           | 100  |        |      | ns    |

| tcsh                | CS Hold Time                    |           | 100  |        |      | ns    |

| t <sub>DIS</sub>    | DI Setup Time                   |           | 200  |        |      | ns    |

| tDIH                | DI Hold Time                    |           | 200  |        |      | ns    |

| t <sub>PD1</sub>    | Output Delay to 1               |           |      |        | 300  | ns    |

| t <sub>PD0</sub>    | Output Delay to 0               |           |      |        | 300  | ns    |

| t <sub>HZ</sub> (2) | Output Delay to High Impendance | •         |      |        | 500  | ns    |

| tcsmin              | Minimum CS High Time            |           | 250  |        |      | ns    |

| tskhi               | Minimum SK High Time            | 2.5V      | 1000 |        |      | ns    |

|                     |                                 | 4.5V-6.0V | 400  |        |      |       |

| tsklow              | Minimum SK Low Time             | 2.5V      | 1000 |        |      | ns    |

|                     |                                 | 4.5V-6.0V | 400  |        |      |       |

| tsv                 | Output Delay to Status Valid    | '         |      |        | 500  | ns    |

| fsĸ                 | Maximum Clock Frequency         | 2.5V      | 250  |        |      | kHz   |

|                     |                                 |           | 1000 |        |      |       |

| t <sub>RESS</sub>   | Reset to CS Setup Time          |           | 0    |        |      | ns    |

| t <sub>RESMIN</sub> | Minimum RESET High Time         |           | 250  |        |      | ns    |

| t <sub>RESH</sub>   | RESET to READY Hold Time        |           | 0    |        |      | ns    |

| t <sub>RC</sub>     | Write Recovery                  |           | 100  |        |      | ns    |

# POWER-UP TIMING(1)(3)

| Symbol           | Parameter                     | Min. | Max. | Units |

|------------------|-------------------------------|------|------|-------|

| t <sub>PUR</sub> | Power-Up to Read Operation    |      | 10   | μs    |

| t <sub>PUW</sub> | Power-Up to Program Operation |      | 1    | ms    |

# WRITE CYCLE LIMITS

| Symbol          | Parameter          |           | Min. | Max. | Units |

|-----------------|--------------------|-----------|------|------|-------|

| t <sub>WR</sub> | Program Cycle Time | 2.5V      |      | 10   | ms    |

|                 |                    | 4.5V-6.0V |      | 5    |       |

- This parameter is tested initially and after a design or process change that affects the parameter.

This parameter is sampled but not 100% tested.

t<sub>PUR</sub> and t<sub>PUW</sub> are the delays required from the time V<sub>CC</sub> is stable until the specified operation can be initiated.

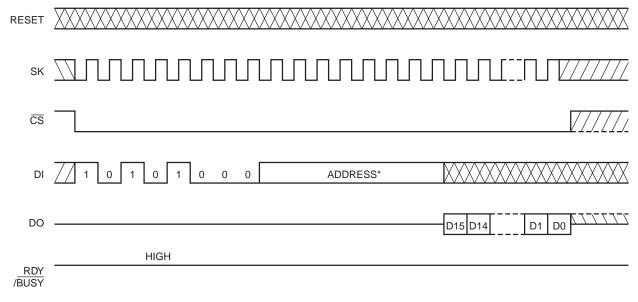

### **INSTRUCTION SET**

| Instru                 | ıction       | Opcode   | Address                 | Data     |

|------------------------|--------------|----------|-------------------------|----------|

| Read                   | 64LC10       | 10101000 | A5 A4 A3 A2 A1 A0 0 0   | D15 - D0 |

|                        | 64LC20       | 10101000 | A6 A5 A4 A3 A2 A1 A0 0  | D15 - D0 |

|                        | 64LC40       | 10101000 | A7 A6 A5 A4 A3 A2 A1 A0 | D15 - D0 |

| Write                  | 64LC10       | 10100100 | A5 A4 A3 A2 A1 A0 0 0   | D15 - D0 |

|                        | 64LC20       | 10100100 | A6 A5 A4 A3 A2 A1 A0 0  | D15 - D0 |

|                        | 64LC40       | 10100100 | A7 A6 A5 A4 A3 A2 A1 A0 | D15 - D0 |

| Write Enab             | ole          | 10100011 | XXXXXXX                 |          |

| Write Disable 10100000 |              | 10100000 | XXXXXXX                 |          |

| [Write All L           | ocations](1) | 10100001 | XXXXXXX                 | D15-D0   |

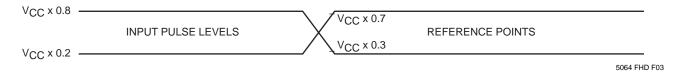

Figure 1. A.C. Testing Input/Output Waveform (2)(3(4) ( $C_L = 100 \text{ pF}$ )

#### Note:

- (Write All Locations) is a test mode operation and is therefore not included in the A.C./D.C. Operations specifications.

- Input Rise and Fall Times (10% to 90%) < 10 ns.

- (3) Input Pulse Levels = V<sub>CC</sub> x 0.2 and V<sub>CC</sub> x 0.8.

(4) Input and Output Timing Reference = V<sub>CC</sub> x 0.3 and V<sub>CC</sub> x 0.7.

### **DEVICE OPERATION**

The CAT64LC10/20/40 is a 1K/2K/4K-bit nonvolatile memory intended for use with all standard controllers. The CAT64LC10/20/40 is organized in a 64/128/256 x 16 format. All instructions are based on an 8-bit format. There are four 16-bit instructions: READ, WRITE, EWEN, and EWDS. The CAT64LC10/20/40 operates on a single power supply ranging from 2.5V to 6.0V and it has an onchip voltage generator to provide the high voltage needed during a programming operation. Instructions, addresses

and data to be written are clocked into the DI pin on the rising edge of the SK clock. The DO pin is normally in a high impedance state except when outputting data in a READ operation or outputting RDY/BUSY status when polled during a WRITE operation.

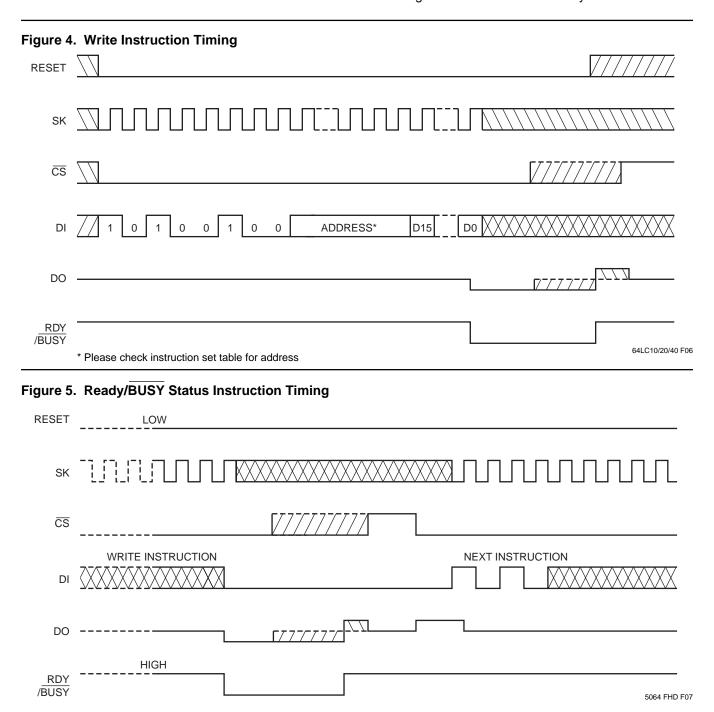

The format for all instructions sent to this device includes a 4-bit start sequence, 1010, a 4-bit op code and an 8-bit address field or dummy bits. For a WRITE operation,

Figure 3. Read Instruction Timing

<sup>\*</sup> Please check the instruction set table for address

a 16-bit data field is also required following the 8-bit address field.

The CAT64LC10/20/40 requires an active LOW  $\overline{CS}$  in order to be selected. Each instruction must be preceded by a HIGH-to-LOW transition of  $\overline{CS}$  before the input of the 4-bit start sequence. Prior to the 4-bit start sequence (1010), the device will ignore inputs of all other logical sequence.

#### Read

Upon receiving a READ command and address (clocked into the DI pin), the DO pin will output data one  $t_{PD}$  after the falling edge of the 16th clock (the last bit of the address field). The READ operation is not affected by the RESET input.

#### Write

After receiving a WRITE op code, address and data, the device goes into the AUTO-Clear cycle and then the

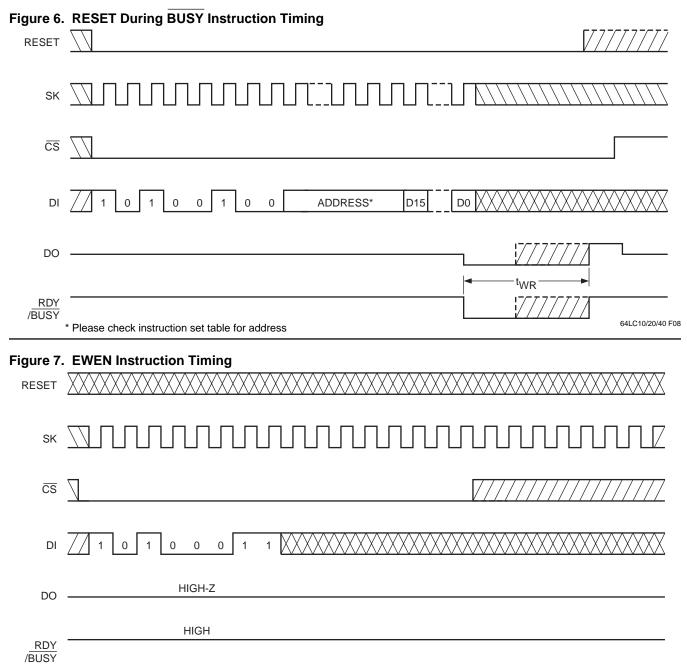

WRITE cycle. The RDY/ $\overline{\text{BUSY}}$  pin will output the BUSY status (LOW) one  $t_{\text{SV}}$  after the rising edge of the 32nd clock (the last data bit) and will stay LOW until the write cycle is complete. Then it will output a logical "1" until the next WRITE cycle. The RDY/ $\overline{\text{BUSY}}$  output is not affected by the input of  $\overline{\text{CS}}$ .

An alternative to get RDY/BUSY status is from the DO pin. During a write cycle, asserting a LOW input to the CS pin will cause the DO pin to output the RDY/BUSY status. Bringing CS HIGH will bring the DO pin back to a high impedance state again. After the device has completed a WRITE cycle, the DO pin will output a

logical "1" when the device is deselected. The rising edge of the first "1" input on the DI pin will reset DO back to the high impedance state again.

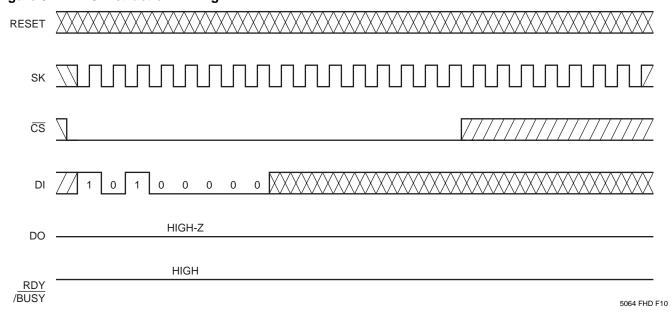

The WRITE operation can be halted anywhere in the operation by the RESET input. If a RESET pulse occurs during a WRITE operation, the device will abort the operation and output a READY status.

NOTE: Data <u>may be</u> corrupted if a RESET occurs <u>while</u> the device is <u>BUSY</u>. If the reset occurs before the <u>BUSY</u> period, no writing <u>will</u> be initiated. However, if RESET occurs after the <u>BUSY</u> period, new data will have been written over the old data.

#### RESET

The RESET pin, when set to HIGH, will reset or abort a WRITE operation. When RESET is set to HIGH while the WRITE instruction is being entered, the device will not execute the WRITE instruction and will keep DO in High-Z condition.

When RESET is set to HIGH, while the device is in a clear/write cycle, the device will abort the operation and will display READY status on the RDY/BUSY pin and on the DO pin if CS is low.

The RESET input affects only the WRITE and WRITE ALL operations. It does not reset any other operations

such as READ, EWEN and EWDS.

#### **ERASE/WRITE ENABLE and DISABLE**

The CAT64LC10/20/40 powers up in the erase/write disabled state. After power-up or while the device is in an erase/write disabled state, any write operation must be preceded by an execution of the EWEN instruction. Once enabled, the device will stay enabled until an EWDS has been executed or a power-down has occured. The EWDS is used to prevent any inadvertent overwriting of the data. The EWEN and EWDS instructions have no affect on the READ operation and are not affected by the RESET input.

# Figure 8. EWDS Instruction Timing

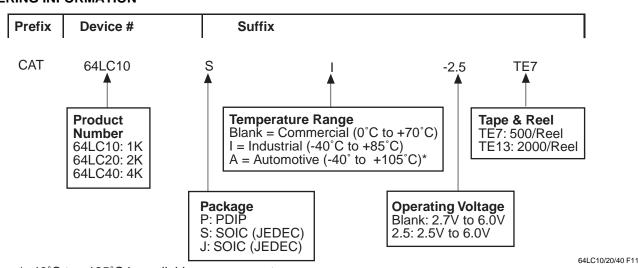

# **ORDERING INFORMATION**

\* -40°C to +125°C is available upon request

Notes:

(1) The device used in the above example is a 64LC10SI-2.5TE7 (SOIC, Industrial Temperature, 2.5 Volt to 6 Volt Operating Voltage, Tape & Reel)

# Sales Offices

# Corporate Headquarters

Catalyst Semiconductor, Inc. 1250 Borregas Avenue Sunnyvale, CA 94089 Phone: 408-542-1000 FAX: 408-542-1200 http://www.catsemi.com

# International Sales Offices

# Europe Area

Catalyst Semiconductor, Inc. The Quorum, Bldg. 7200 Oxford Business Park Oxford OX4 2JZ **ENGLAND**

Phone: 44.1865.481.411 FAX: 44.1865.481.511

#### Japan Area

Nippon Catalyst K.K. 6th Fl, Kurihara Bldg. 4-48-13 Honcho Nakano-ku, Tokyo 164 **JAPAN**

Phone: 81.3.5340.3781 FAX: 81.3.5340.3780

#### Far East Offices

Catalyst Semiconductor, Inc. 9F, No 400, Sec 1 Kee-Lung Road Taipei, TAIWAN Phone: 886.2.345.6192

FAX: 886.2.729.9388

Catalyst Semiconductor, Inc. Blk 446, #B1-1635 Hougang Ave 8 Singapore 530446 Republic of Singapore Phone: 65.385.8568

Fax: 65.385.8569

#### U.S. Sales Offices

#### Western and Central U.S.

Catalyst Semiconductor, Inc. 1250 Borregas Avenue Sunnyvale, CA 94089 Phone: 408-542-1000 FAX: 408-542-1200

Catalyst Semiconductor, Inc. Los Gatos Eureka Building Suite 105 236N. Santa Cruz Ave. Los Gatos, CA 95030 Phone: 408-395-1921 FAX: 408-395-4941

Catalyst Semiconductor, Inc. 1201 S. Alma School Road Suite 14000 Mesa, Arizona 85210 Phone: 602-844-3800 FAX: 602-844-3600

Catalyst Semiconductor, Inc. 3303 FM 1960 West Suite 300-T Houston, Texas 77068 Phone: 281-397-8809 FAX: 281-397-0433

#### Eastern U.S.

Catalyst Semiconductor, Inc. 2200 Winter Springs Blvd. Suite 106-310 Oviedo, FL 32765 Phone: 407-977-1973 FAX: 407-977-1975

Catalyst Semiconductor, Inc. 1000 Mansell Exchange West Suite 250 Alpharetta, GA 30022 Phone: 770-645-7541

FAX: 770-645-7551

Catalyst Semiconductor, Inc. 5669 Whitesburg Court Norcross, GA 30092 Phone 770-613-2999 FAX: 770-613-0024