# **INSTRUCTION MANUAL**

# MODEL 802 50 MHz PULSE GENERATOR

9045 BALBOA AVENUE, SAN DIEGO, CALIFORNIA

# **INSTRUCTION MANUAL**

# MODEL 802 50 MHz PULSE GENERATOR

THIS DOCUMENT CONTAINS INFORMATION PROPRIETARY TO WAVETEK. THE INFORMATION IN THIS DOCUMENT IS NOT TOBE USED OR DUPLICATED IN ANY MANNER WITHOUT THE PRIOR APPROVAL IN WRITING OF WAVETEK.

9045 Balboa Ave., San Diego, Calif. 92123 P. O. Box 651, San Diego, California 92112 Tel 714/279-2200 TWX 910-335-2007

# **WARRANTY**

All Wavetek instruments are warranteed against defects in material and workmanship for a period of one year after date of manufacture. Wavetek agrees to repair or replace any assembly or component (except batteries) found to be defective, under normal use, during this period. Wavetek's obligation under this warranty is limited solely to repairing any such instrument which in Wavetek's sole opinion proves to be defective within the scope of the warranty when returned to the factory or to an authorized service center. Transportation to the factory or service center is to be prepaid by purchaser. Shipment should not be made without prior authorization by Wavetek.

This warranty does not apply to any products repaired or altered by persons not authorized by Wavetek, or not in accordance with instructions furnished by Wavetek. If the instrument is defective as a result of misuse, improper repair, or abnormal conditions or operations, repairs will be billed at cost.

Wavetek assumes no responsibility for its product being used in a hazardous or dangerous manner either alone or in conjunction with other equipment. High voltage used in some instruments may be dangerous if misused. Special disclaimers apply to these instruments. Wavetek assumes no liability for secondary charges or consequential damages and, in any event, Wavetek's liability for breach of warranty under any contract or otherwise, shall not exceed the purchase price of the specific instrument shipped and against which a claim is made.

Any recommendations made by Wavetek for use of its products are based upon tests believed to be reliable, but Wavetek makes no warranty of the results to be obtained. This warranty is in lieu of all other warranties, expressed or implied, and no representative or person is authorized to represent or assume for Wavetek any liability in connection with the sale of our products other than set forth herein.

# **CONTENTS**

| SECTION 1 | GENERA  | L DESCRIPTION                           |

|-----------|---------|-----------------------------------------|

|           | 1.1 TH  | E MODEL 802                             |

|           |         | ECIFICATIONS 1-                         |

|           |         | Versatility                             |

|           |         | Pulse Outputs                           |

|           |         | Time Domain                             |

|           |         | Input Characteristics                   |

|           |         | General                                 |

| SECTION 2 | INSTALL | ATION                                   |

|           | 2.1 ME  | CHANICAL INSTALLATION                   |

|           |         | ECTRICAL INSTALLATION                   |

|           |         | Power Connection                        |

|           |         | Signal Connections                      |

|           |         | ECTRICAL ACCEPTANCE CHECK2-             |

| SECTION 3 | OPERAT  | ION                                     |

|           | 3.1 CO  | NTROLS AND CONNECTORS 3-                |

|           |         | TES ON OPERATION 3-3                    |

|           |         | Modes                                   |

|           | 3.2.2   | Nhite Marks                             |

|           |         | Pulse Width and Delay                   |

|           |         | Output Terminations                     |

|           |         | Outy Cycle 3.4                          |

|           |         | Output Mixing                           |

|           |         | Precise Output Levels                   |

|           |         | Fixed Delay                             |

|           |         | Two Phase Clocking                      |

|           |         | Rise Time Measurements                  |

|           |         | ERATION                                 |

|           |         | Continuous Pulses                       |

|           |         | Vide Duty Cycle Pulses                  |

|           |         | Externally Triggered Pulses             |

|           |         | Manually Triggered Pulses               |

|           |         | Gated Pulses 3-7                        |

|           |         | Pulses With Width Controlled Externally |

|           |         | Oouble Pulses                           |

# Contents (Continued)

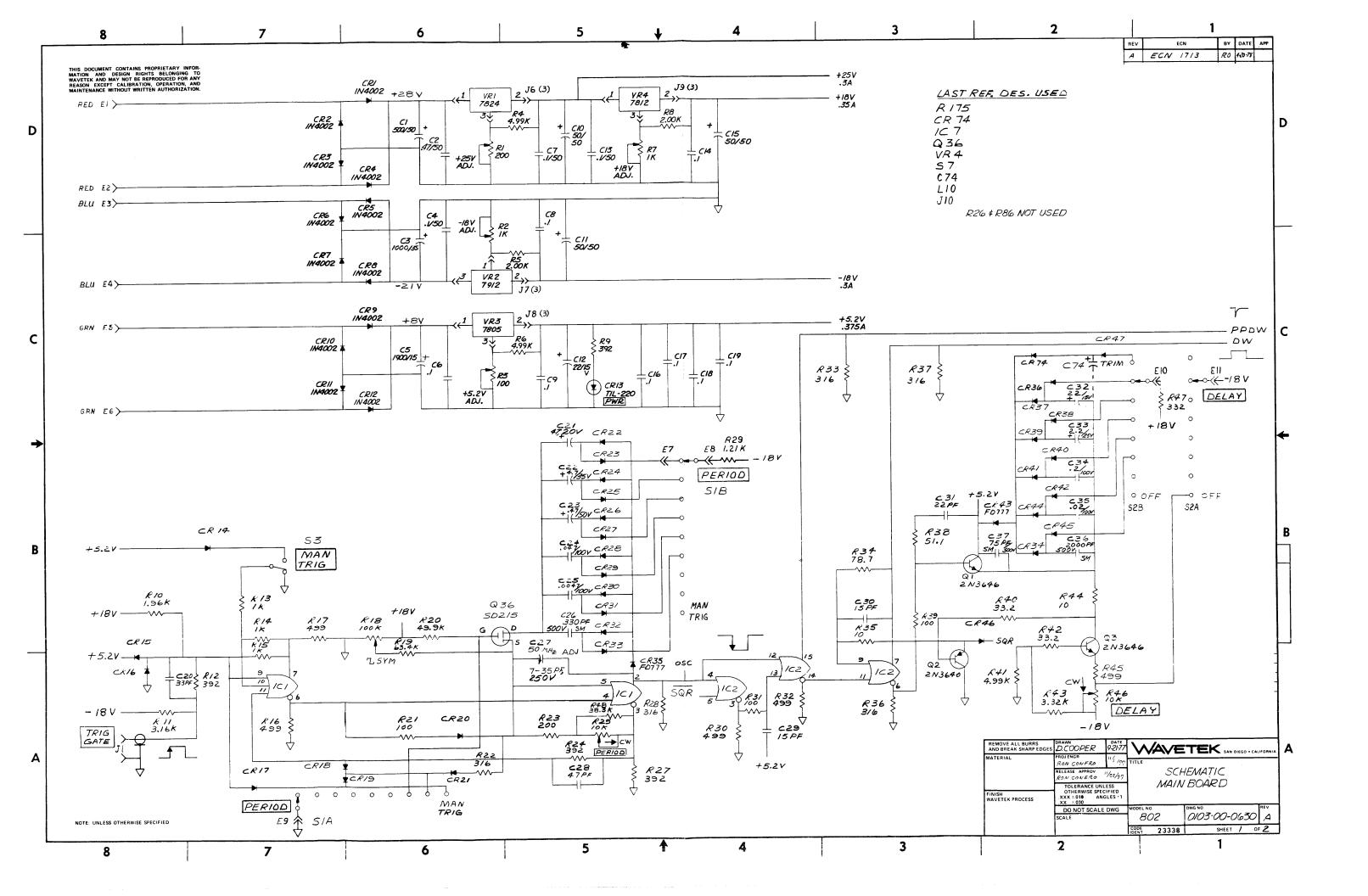

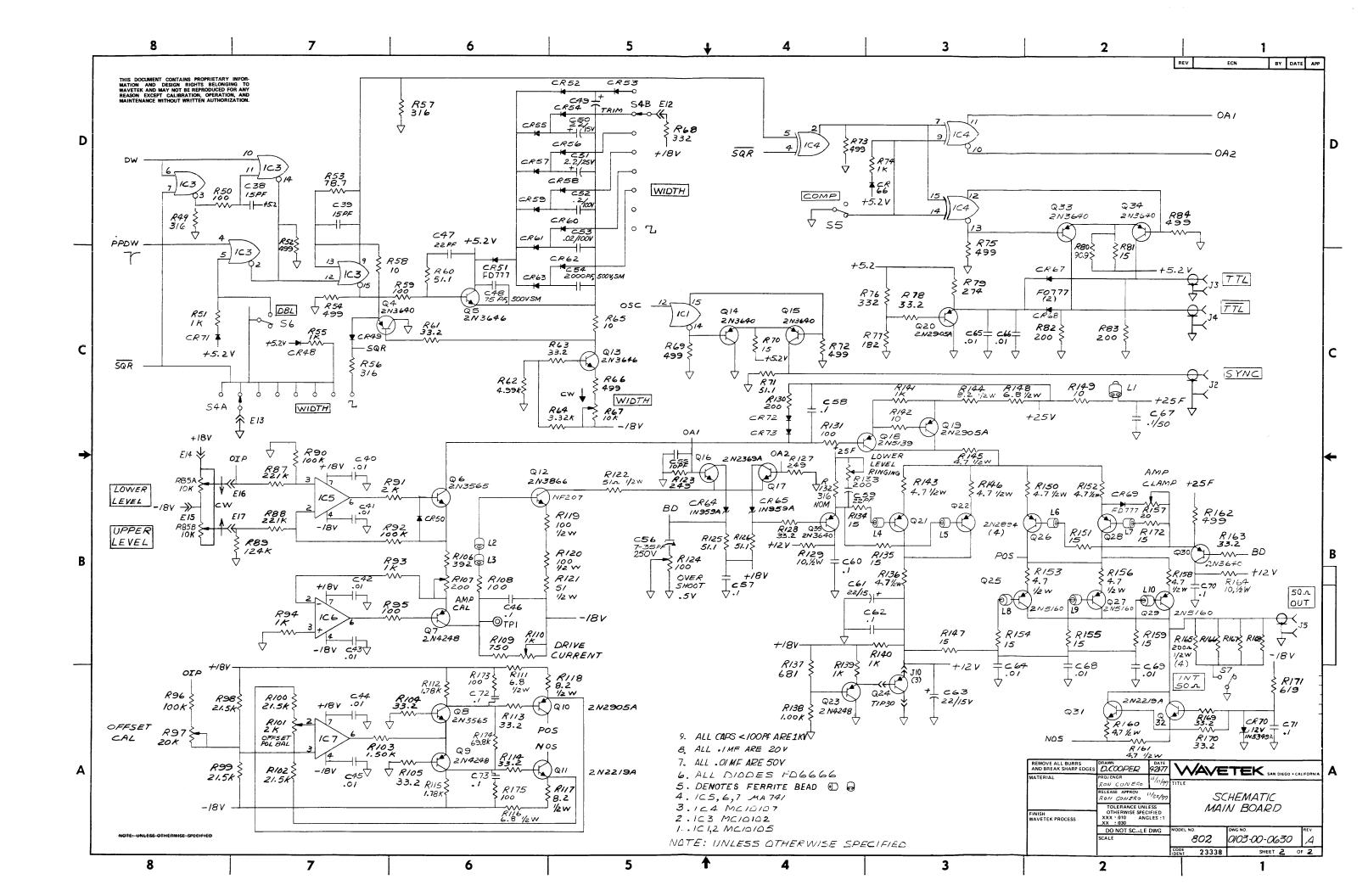

| SECTION 4 | CIRCUIT DESCRIPTION                           |  |  |  |  |

|-----------|-----------------------------------------------|--|--|--|--|

|           | 4.1 OVERALL BLOCK DIAGRAM 4-1                 |  |  |  |  |

|           | <b>4.2 PERIOD OSCILLATOR</b> 4-1              |  |  |  |  |

|           | 4.3 TRIGGER/GATE CIRCUIT 4-1                  |  |  |  |  |

|           | 4.4 SYNC CIRCUIT                              |  |  |  |  |

|           | 4.5 DELAY CIRCUIT 4-1                         |  |  |  |  |

|           | 4.6 WIDTH CIRCUIT                             |  |  |  |  |

|           | 4.7 TTL BUFFER AMPLIFIER 4-2                  |  |  |  |  |

|           | 4.8 OUTPUT AMPLIFIER 4-2                      |  |  |  |  |

|           | 4.9 POWER SUPPLY 4-2                          |  |  |  |  |

|           | 4.10 MODES OF OPERATION                       |  |  |  |  |

| SECTION 5 | CALIBRATION                                   |  |  |  |  |

|           | <b>5.1 FACTORY REPAIR</b>                     |  |  |  |  |

|           | 5.2 REQUIRED TEST EQUIPMENT                   |  |  |  |  |

|           | 5.3 REMOVING GENERATOR COVERS 5-1             |  |  |  |  |

|           | <b>5.4 CALIBRATION</b>                        |  |  |  |  |

| SECTION 6 | TROUBLESHOOTING 6-1                           |  |  |  |  |

|           | <b>6.1 INTRODUCTION</b>                       |  |  |  |  |

|           | <b>6.2 SAFETY</b> 6-1                         |  |  |  |  |

|           | <b>6.2.1 Precautions</b>                      |  |  |  |  |

|           | <b>6.2.2 Safety Check</b>                     |  |  |  |  |

|           | 6.3 CIRCUIT BOARD ACCESS 6-1                  |  |  |  |  |

|           | 6.4 BASIC TECHNIQUES 6-1                      |  |  |  |  |

|           | 6.5 TROUBLESHOOTING INDIVIDUAL COMPONENTS 6-2 |  |  |  |  |

|           | <b>6.5.1 Transistor</b>                       |  |  |  |  |

|           | <b>6.5.2</b> Diode                            |  |  |  |  |

|           | 6.5.3 Operational Amplifier                   |  |  |  |  |

|           | <b>6.5.4 FET Transistor</b>                   |  |  |  |  |

|           | <b>6.5.5 MOSFET Transistor</b>                |  |  |  |  |

|           | 6.5.6 Capacitor                               |  |  |  |  |

|           | 6.5.7 ECL Gate                                |  |  |  |  |

|           | 6.6 FLOW CHARTS                               |  |  |  |  |

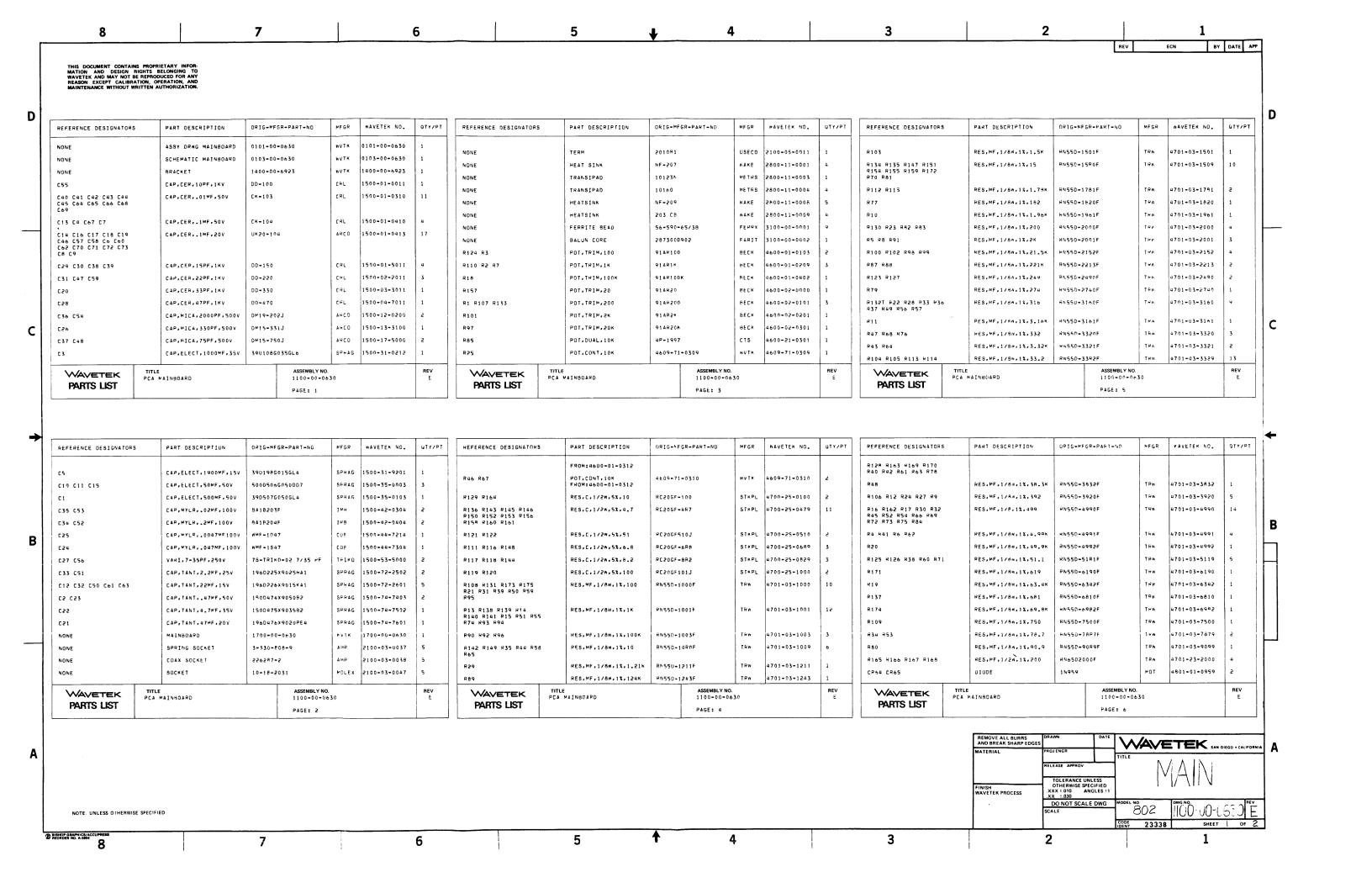

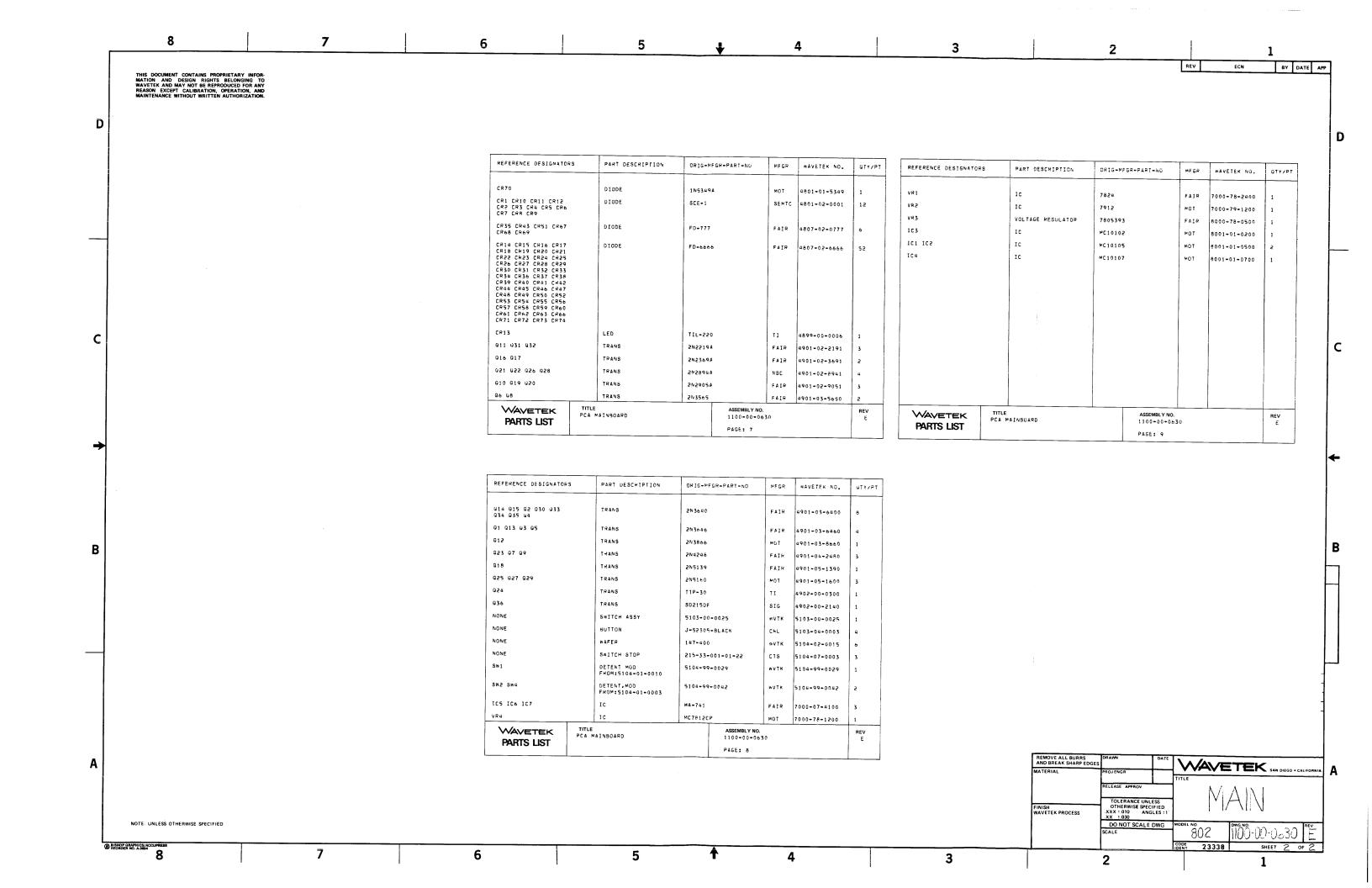

| SECTION 7 | PARTS AND SCHEMATICS                          |  |  |  |  |

|           | <b>7.1 DRAWINGS</b>                           |  |  |  |  |

|           | <b>7.2 ORDERING PARTS</b>                     |  |  |  |  |

|           | 7.3 ADDENDA                                   |  |  |  |  |

# **SAFETY**

This instrument is wired for earth grounding via the facility power wiring. Do not bypass earth grounding with two wire extension cords, plug adapters, etc.

BEFORE PLUGGING IN the instrument, comply with installation instructions.

MAINTENANCE may require power on with the instrument covers removed. This should be done only by qualified personnel aware of the electrical hazards.

WARNING notes call attention to possible injury or death hazards in subsequent operations.

CAUTION notes call attention to possible equipment damage in subsequent operations.

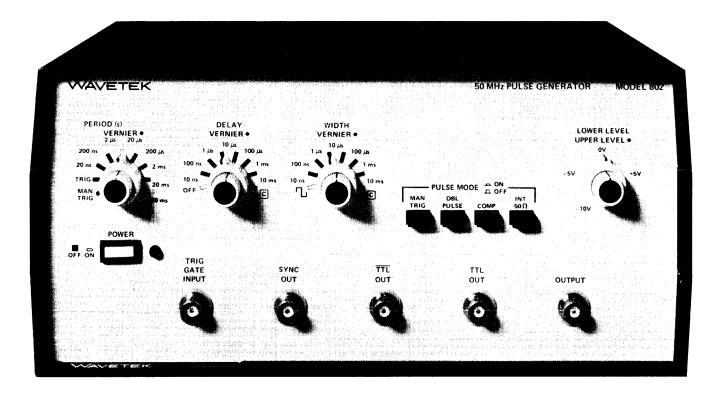

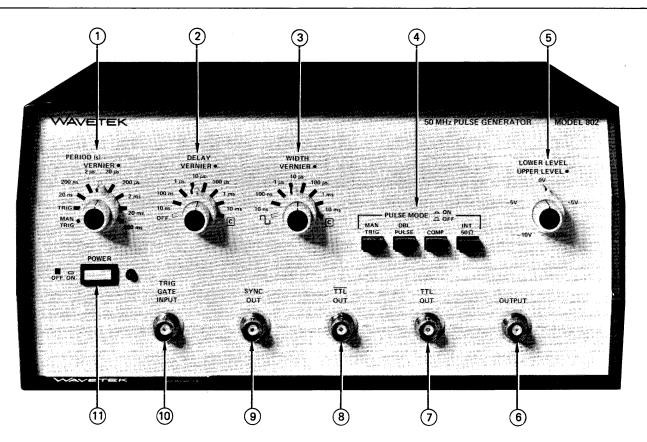

Figure i. Model 802 50 MHz Pulse Generator

# SECTION SECTION GENERAL DESCRIPTION

#### 1.1 THE MODEL 802

The Model 802 is a 50 MHz general purpose laboratory pulse generator. The instrument gives you full control in primary pulse triggering and shaping plus simultaneous TTL, TTL and sync pulses. The primary pulse output has controllability in rate, width, delay, upper level, lower level and a choice of positive, negative or complementary outputs. The TTL and TTL are of fixed levels and rise times that are standard for use with compatible devices. The primary pulse has rise and fall times of 5 ns or less.

The output is  $\pm 10$  volts with a  $50\Omega$  termination. Upper and lower pulse levels are fully adjustable through  $\pm 10$  volts, a 20 volt window. Termination may be internal, at the load or both.

Single pulses or pulse pairs may be triggered; pulse width may be trigger controlled; continuous pulses may be gated for a 'burst' output.

# 1.2 SPECIFICATIONS

# 1.2.1 Versatility

# Four Simultaneous Pulse Outputs

Fixed TTL level sync, TTL and TTL outputs, and variable amplitude output pulses are available over a 5 Hz (200 ms) to 50 MHz (20 ns) frequency range.

For optimum pulse characteristics from the variable amplitude pulse output, an internal  $50\Omega$  load can be selected via a front panel control.

# **Operational Modes**

Continuous: Generator oscillates continuously at selected frequency.

Triggered: Generator quiescent until triggered by external TTL pulse or front panel control, then generates one pulse.

Gated: Generator oscillates at the period rate selected by the front panel control when gate input is high. Generator quiescent when input is low. First cycle is synchronous with rising edge of gating signal. Double Pulse: Same as continuous, triggered and gated, except two pulses for each period. Time to second pulse is controlled by delay control. Double pulse at all outputs except sync.

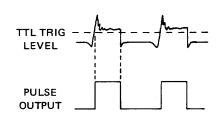

External Width: External signal at trigger input determines output pulse width and period as shown.

# 1.2.2 Pulse Outputs

#### Variable Amplitude Pulse

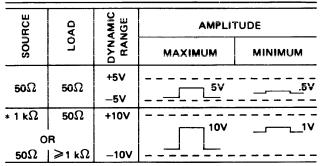

|   | SOURCE | LOAD  | DYNAMIC<br>RANGE | AMPLITUDE       |

|---|--------|-------|------------------|-----------------|

|   | son    | LO    | DYN,<br>RAÎ      | MAXIMUM MINIMUM |

| • | 50Ω    | 50Ω   | +5V<br>-5V       | 5V5v            |

| • | 1 kΩ   | 50Ω   | +10V             | 10V1V           |

|   | o      | R     |                  | 1001            |

|   | 50Ω    | ≥1 kΩ | -10V             |                 |

Upper and lower pulse levels are independently adjustable. Pulse dynamic range is  $\pm 10V$  when load is  $50\Omega$  terminated and source is not (internal  $50\Omega$  off) or vice versa. Maximum pulse amplitude is 10V; minimum is 1V. Dynamic range and pulse amplitude are decreased by a factor of 2 when source and load are  $50\Omega$  terminated. Overshoot and ringing are less than  $\pm (5\%$  of amplitude setting  $\pm 100$  mV) when terminated into  $50\Omega$  at both load and source. Transition times are less than 5 ns.

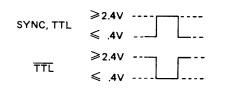

# Sync, TTL and TTL Pulses

Sync pulse levels from 50 $\Omega$ ; TTL and  $\overline{\text{TTL}}$  pulse levels into 50 $\Omega$  termination.

Transition times less than 7 ns into  $50\Omega$  termination.

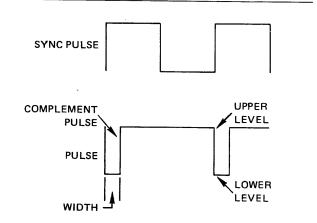

# Normal/Complement Control

Normal pulse or its complement is selected. The normally quiescent and active levels are reversed in complement format. This control affects all outputs except sync pulse.

#### 1.2.3 Time Domain

#### Period

Period range is from less than 20 ns to greater than 200 ms in 7 overlapping ranges. Period jitter is less than  $\pm 0.1\%$  plus 50 picoseconds.

#### Width

Width range is from less than 10 ns to 10 ms in 6 overlapping ranges. Maximum duty cycle is 70% for periods to 200 ns, decreasing to 50% for 20 ns periods. Width selector switch also has a square wave detent and a customer-specified detent.\*  $\Box$  duty cycle is 50 ±4% to 2  $\mu$ s period, changing to 50 ±15% at 20 ns period. Width jitter is less than ±0.1% plus 50 picoseconds. Sync pulse duty cycle is 50 ±4% of pulse period to 2  $\mu$ s period, changing to 50 ±15% at 20 ns period except in trigger and external width modes, in which case it is determined by the trigger signal.

#### Delay

Pulse occurence can be delayed from less than 10 ns to 10 ms with respect to the sync pulse (not including fixed delay). Delay selector switch also has a customer-specified detent.\* Maximum delay duty cycle is 70% for periods to 200 ns, decreasing to 30% for 20 ns periods.

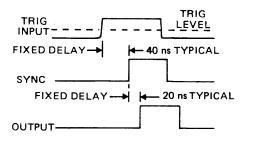

Delay jitter is less than  $\pm 0.1\%$  plus 50 picoseconds. Fixed delay is as shown.

#### 1.2.4 Input Characteristics

# **External Trigger**

The circuit receiving the external trigger is TTL compatible. Triggering level is fixed at approximately 1:4V. Input impedance is greater than  $500\Omega$  shunted by approximately 33 pF. Triggering and gating occurs on the rising edge of the input signal.

# 1.2.5 General

#### **Environmental**

Specifications apply at 25°C ±5°C after 30 minutes warmup. Instrument will operate from 0°C to 50°C,

# **Dimensions**

28.8 cm (11.4 in.) wide; 10.2 cm (4 in.) high; 29 cm (11.4 in.) deep.

#### Weigh<sup>\*</sup>

4.0 kg (8.9 lb) net; 5.4 kg (12 lb) shipping.

# Power

108 to 132V or 216 to 250V; 50 to 400 Hz; 40 watts nominal.

<sup>\*</sup>Customer-installed capacitor determines detent range.

# SECTION 2 INSTALLATION

# 2.1 MECHANICAL INSTALLATION

After unpacking the instrument, visually inspect all external parts for possible damage to connectors, surface areas, etc. If damage is discovered, file a claim with the carrier who transported the unit. The shipping container and packing material should be saved in case reshipment is required.

# 2.2 ELECTRICAL INSTALLATION

# 2.2.1 Power Connection

#### WARNING

To preclude injury or death due to shock, the third wire earth ground must be continuous to the facility power outlet. Before connecting to the facility power outlet, examine extension cords, autotransformers, etc., between the instrument and the facility power outlet for a continuous earth ground path. The earth ground path can be identified at the plug on the instrument power cord; of the three terminals, the earth ground terminal is the nonmatching shape, usually cylindrical.

# **CAUTION**

To prevent damage to the instrument, check for proper match of line and instrument voltage and proper fuse type and rating.

# NOTE

Unless otherwise specified at the time of purchase, this instrument was shipped from the factory with the power transformer connected for operation on a 108 to 126 Vac line supply and with a 0.5 amp fuse.

Conversion to other input voltages requires a change in rear panel fuse-holder voltage card position and fuse according to the following table and procedure.

| Card Position | Input Vac  | Fuse<br>(Slow Blow, 3 AG) |

|---------------|------------|---------------------------|

| 100           | 90 to 105  | 0.5 amp                   |

| 120           | 108 to 126 | 0.5 amp                   |

| 220           | 198 to 231 | 0.25 amp                  |

| 240           | 216 to 250 | 0.25 amp                  |

- Open fuse holder cover door and rotate FUSE PULL to left to remove the fuse.

- 2. Select operating voltage by orienting the printed circuit board to position the desired voltage on the top left side. Push the board firmly into its module slot.

- Rotate the FUSE PULL back into the normal position and insert the correct fuse into the fuse holder. Close the cover door.

- 4. Connect the ac line cord to the mating connector at the rear of the unit and the power source.

# 2.2.2 Signal Connections

Use 3 foot RG58U  $50\Omega$  shielded cables equipped with female BNC connectors to distribute input and output signals when connecting this instrument to associated equipment.

# 2.3 ELECTRICAL ACCEPTANCE CHECK

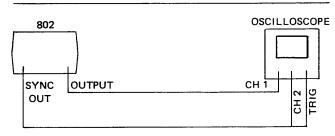

This checkout procedure verifies the generator operation. If a malfunction is found, refer to the Warranty in the front of this manual. A 2 channel oscilloscope and  $50\Omega$  coax cable are needed for this procedure (see figure 2-1).

Figure 2-1. Initial Setup

Preset the pulse generator controls by setting the following switches to their white mark:

PERIOD/RATE DELAY WIDTH

Set the PULSE MODE switches OFF except set INT  $50\Omega$  ON.

Set the following controls to 12 o'clock:

PERIOD/RATE VERNIER

DELAY VERNIER

WIDTH VERNIER

LOWER LEVEL

UPPER LEVEL

Perform the steps in table 2-1. Only approximate values are required to verify operation.

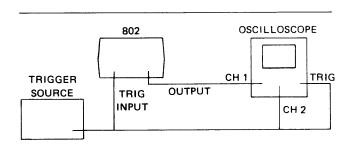

Figure 2-2. Second Setup

Table 2-1. Performance Checkout

| Step | Control                | Position/Operation                                            | Observation                                                                                                     |

|------|------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1    | POWER                  | ON <sup>-</sup>                                               | CH 1: A near 0 volt dc level. (LEVEL control is not calibrated.) CH 2: Approximately 2.5 volt pulses.           |

| 2    | LOWER LEVEL            | Rotate ccw                                                    | Pulse base drops 10V.                                                                                           |

| 3    | UPPER LEVEL            | Rotate ccw                                                    | Pulse upper level drops 10V.                                                                                    |

| 4    | UPPER LEVEL            | Rotate cw. Make observation; then reposition for good display | Pulse rises 10V, then rises 10V more while pulling the base up 10V. Base rises to 0V.                           |

| 5    | СОМР                   | ON then OFF                                                   | Set scope for one or two cycles. Observe the switching of duty time from first half cycle to second half cycle. |

| 6    | WIDTH                  | Rotate ccw, then to 10 μs 100 μs                              | Pulse width changes. (Use scope X 10 magnification to see narrow widths.)                                       |

| 7    | WIDTH VERNIER          | Rotate ccw, then to 12 o'clock                                | Pulse width decreases, then increases.                                                                          |

| 8    | DELAY                  | Rotate cw to 10 μs I 100 μs                                   | Pulse delay changes within cycle time.                                                                          |

| 9    | DELAY VERNIER          | Rotate ccw, then cw                                           | Pulse delay moves to left, then right.                                                                          |

| 10   | PERIOD/RATE<br>VERNIER | Rotate cw, then to 12 o'clock                                 | Period increases, then decreases.                                                                               |

| 11   | DBL PULSE              | ON                                                            | Two pulses instead of one.                                                                                      |

| 12   | DELAY VERNIER          | Rotate ccw, then cw, but main-<br>tain double pulse           | Pulse pairs move closer, then further apart.                                                                    |

| 13   | WIDTH VERNIER          | Rotate ccw, then to 12 o'clock, but maintain double pulse     | Pulse width of each pulse of pulse pair decreases, then increases.                                              |

| 14   | ОИТРИТ                 | Remove cable; place on TTL connector                          | TTL double pulse output.                                                                                        |

| 15   | TTL OUT                | Remove cable; place on TTL connector                          | TTL double pulse output complement of previous output.                                                          |

Table 2-1. Performance Checkout (Continued)

| Step | Control  | Position/Operation                                                                               | Observation                                     |

|------|----------|--------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 16   |          | Change to setup in figure 2-2;<br>trigger with a 10 kHz signal;<br>adjust scope for best display | One pulse on CH 2; set of pulses on CH 1.       |

| 17   | WIDTH    | Rotate to $\square$                                                                              | One pulse on CH 1; one pulse on CH 2.           |

| 18   | MAN TRIG | ON                                                                                               | Repeated operation makes pulse pair observable. |

# SECTION OPERATION

# 3.1 CONTROLS AND CONNECTORS

The generator controls and connections are shown in figure 3-1 and keyed to the following descriptions.

of pulse period calibrated in seconds and hertz. The TRIG detent holds the output at the inactive level until a TTL level trigger signal is applied at the TRIG GATE INPUT BNC. On the input rising edge, one pulse, or one double pulse, is output. The MAN TRIG detent is as the TRIG detent, except pressing the MAN TRIG switch generates the output.

# NOTE

For continuous mode operation, low input or  $50\Omega$  termination to the TRIG GATE INPUT BNC must be removed.

**VERNIER Control** — Varies the pulse period within the range selected by the outer knob. Clockwise increases the pulse period and decreases frequency.

DELAY Switch — Selects one of seven ranges of pulse delay or time-to-second-pulse of double pulses, depending on DBL PULSE switch setting. OFF position of DELAY switch ensures minimum delay. The detent marked "C" is for customer selected range.

**VERNIER Control** — Varies the delay time within the range selected by the outer knob. Clockwise increases the delay.

WIDTH Switch — Selects one of seven ranges of pulse width or an approximate 50% duty cycle. The detent marked "C" is for customer selected range.

Figure 3-1. Controls and Connections

**VERNIER Control** — Varies the pulse width within the range selected by the outer knob except in  $\square$ .

MAN TRIG Switch — Triggers the generator one time when pressed. Output depends on the mode selected.

**DBL PULSE Switch** — When ON, a double pulse occurs in each period. Time to leading edge of second pulse is controlled by the DELAY setting. When OFF, one pulse occurs in each period.

**COMP Switch** — Selects a normal pulse when OFF or its complement when ON, which swaps the active and quiescent levels. Affects all outputs, except SYNC.

INT 50 $\Omega$  Switch — When ON, the output current source is  $50\Omega$  terminated internally. When OFF, the current source has greater than 1 k $\Omega$  impedance.

5 LOWER LEVEL Control — Outer knob sets the lower level of the OUTPUT pulse, which may be varied from -10 to +10 volts into a single  $50\Omega$  termination or -5 to +5 volts into a double  $50\Omega$  termination. Maximum pulse heights are 10 and 5 volts, respectively.

**UPPER LEVEL Control** – Inner knob sets the upper level of the OUTPUT pulse. Upper level range is identical to that stated for the lower level.

- 6 OUTPUT Connector The main output of the generator. Pulses from this output may be controlled in level as well as frequency and width.

- (7) TTL OUT Connector An output with a transistor-transistor-logic level pulse whose occurrence and duration are controllable. Normal pulse level is <0.4V quiescent, > 2.4V active into a  $50\Omega$  termination. Levels are reversed for the complement pulse.

- (8) TTL OUT Connector An output like the TTL output (7) except active and quiescent levels are reversed.

- 9 SYNC OUT Connector A TTL level output from a  $50\Omega$  source. Square wave in all modes except external width and external trigger modes, in which pulse width is determined by trigger pulse width.

- TRIG GATE INPUT Connector Accepts an external TTL level signal to trigger or gate the generator. Triggers on rising edge of input. Gates off when level is at a TTL low level.

**POWER Switch** – Pulse generator on/off switch features red power-on indicator light and black/white changing switch surface for off/on indication.

# 3.2 NOTES ON OPERATION

# 3.2.1 Modes

The following modes of operation are available and selectable as described herein.

**Continuous** — For a continuous stream of pulses, the PERIOD switch must be in any position except TRIG or MAN TRIG and the TRIG GATE INPUT BNC must be free of input signals and  $50\Omega$  terminations.

Triggered — For a pulse, or pulse pair, triggered by an external signal, the PERIOD switch must be set to TRIG and a TTL level square pulse must be present at the TRIG GATE INPUT. Triggering occurs on the trigger pulse rising edge.

Manually Triggered — For a pulse, or pulse pair, triggered by the MAN TRIG switch, the PERIOD switch must be set to MAN TRIG.

**Gated** — For continuous pulses for the duration of a gate signal, the PERIOD switch must be in any position except TRIG or MAN TRIG and a TTL level square pulse must be input to the TRIG GATE INPUT BNC. For manual gating, place a  $50\Omega$  termination on the TRIG GATE INPUT BNC to disable the generator output. Push the MAN TRIG switch to gate an output.

**External Width** — For pulses whose widths are determined by an external signal, the PERIOD switch must be set to TRIG and the WIDTH switch must be set to  $\Box$ .

# 3.2.2 White Marks

When first becoming familiar with the 802, the white mark settings are handy. The white mark settings for the front panel switches will always give a 50 to 500 kHz sync signal when power is on. The same settings will give 50% duty cycle TTL, TTL and output pulses; the LOWER LEVEL/ UPPER LEVEL control may need adjusting to observe the output on an oscilloscope. Once the output is observed, each control can be adjusted and observed until the desired result is obtained.

# 3.2.3 Pulse Width and Delay

Narrow duty cycle pulses require a normal output (COMP OFF) while greater than 70% duty cycle pulses require the COMP ON setting to allow the width circuitry sufficient recovery time. When using DELAY time, ensure that delay ≤ 70% of PERIOD and width ≤ 70% of PERIOD.

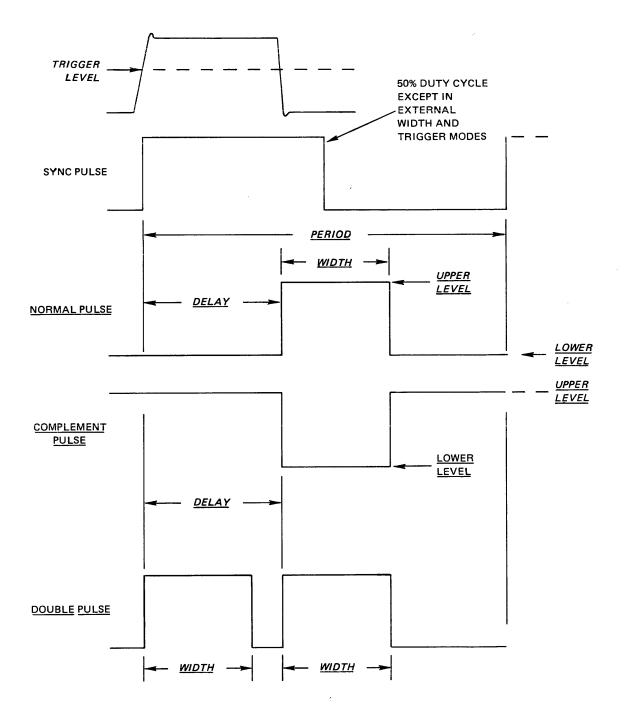

NOTE: Underline indicates a front panel controlled parameter.

Figure 3-2. Pulse Parameters

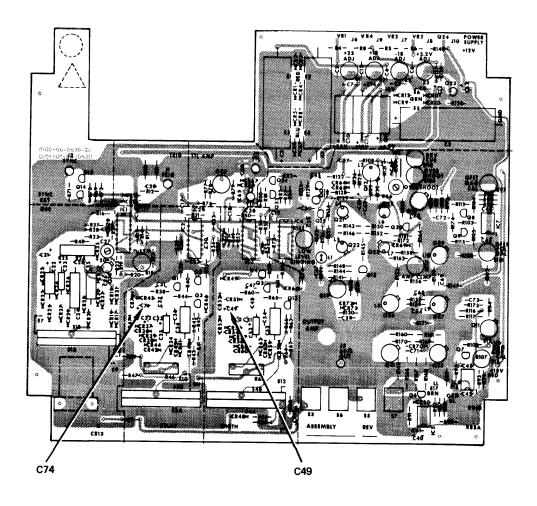

Figure 3-3. Placement of Customer Option Capacitors

The unidth setting gives a 50% duty cycle in continuous mode, when TRIG or MAN TRIG is selected on the PERIOD switch, the pulse width is determined by the trigger signal width. This is external width mode of operation.

Table 3-1. Capacitance and Range

| Table 11 Supusitance and Italige |             |  |

|----------------------------------|-------------|--|

| Delay or Width Range             | Capacitance |  |

| 10 ns - 100 ns                   | None        |  |

| 100 ns - 1 μs                    | 2000 pF     |  |

| 1 μs - 10 μs                     | 0.02 μF     |  |

| 10 μs - 100 μs                   | 0.2 μF      |  |

| 0.1 ms - 1 ms                    | 2.0 μF      |  |

| 1 ms - 10 ms                     | 20 μF       |  |

| 10 ms - 100 ms                   | 200 μF      |  |

| 0.1s - 1s                        | 2000 μF     |  |

The unmarked detent on the DELAY switch and WIDTH switch can be any desired range by placing appropriate capacitors on the circuit board, as shown in figure 3-3. Refer to table 3-1 for typical capacitance and range.

# 3.2.4 Output Terminations

Only  $50\Omega$  RG58U cables should be used to connect the 802 to the circuit under test. Either the INT  $50\Omega$  should be ON or a  $50\Omega$  2W load should be used at the circuit end of the cable. For best pulse fidelity, a  $50\Omega$  load at both the source and the load is required.

As shown in figure 3-4, the combinations of load and source impedances determine the output pulse amplitude range

\*1 k $\Omega$  is the unterminated source impedance of the OUTPUT.

Figure 3-4. Load and Source Terminations

and the dynamic range. As shown, when a greater than 5V pulse is desired, only one  $50\Omega$  termination can be used, and the placement of the termination can optimize the pulse purity. In this case, the capacitance of the circuit being driven must be considered. For capacitive loads greater than  $20~\rm pF$ , reflections on the line are most effectively absorbed by the  $50\Omega$  termination at the  $802~\rm (INT~50\Omega$  switch ON). For capacitive loads less than  $20~\rm pF$ , the  $50\Omega$  termination should be placed at the load side of the line. When a less than  $5V~\rm pulse$  is required, a  $50\Omega$  termination at each end of the line is recommended for optimum pulse purity.

The  $50\Omega$  terminations should always be used on the SYNC, TTL and  $\overline{\text{TTL}}$  outputs.

# 3.2.5 Duty Cycle

Always use the lowest range possible for both delay and width functions. This will reduce the recovery time of the circuit one-shots and extend the maximum duty cycle of the 802 to its fullest capability.

# 3.2.6 Output Mixing

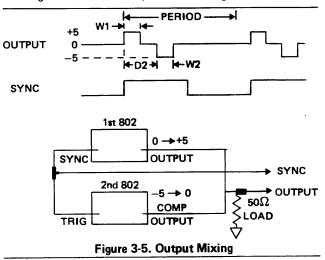

By triggering a second 802 from the sync output of the first 802 and then mixing their outputs in a common load, three level signals can be created, as shown in figure 3-5.

# 3.2.7 Precise Output Levels

Many times when testing a circuit, it is desirable to lock the output of the generator at either the high or low level. A precise measurement of this level may then be obtained using a DVM.

To lock the output at high or low level, select EXT TRIG and  $\square$  with no TRIG GATE INPUT. Use the COMP ON/OFF switch to select high and low level outputs.

# 3.2.8 Fixed Delay

A fixed delay of 20 ns has been incorporated within the 802 to ensure that the leading edge is visible on the scope. If this delay is not desired, simply increase the length of the sync cable coax at the rate of 1.5 ns/ft to obtain the desired result.

# 3.2.9 Two Phase Clocking

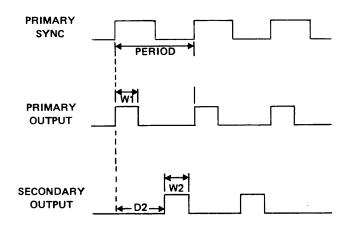

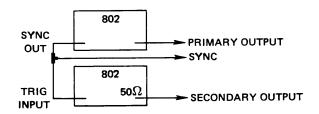

If a secondary 802 is triggered by the sync out from the primary 802, a two phase nonoverlapped clock source can be obtained as shown in figure 3-6.

Figure 3-6. Two Phase Clock Generation

# 3.2.10 Rise Time Measurements

When measuring rise time in a linear device under test, the error induced by the rise time of the testing system must be considered. For example, when observing the 802 rise time on an oscilloscope, 802 rise time is

$$t_{\text{observed}}^2 = t_{\text{scope}}^2 + t_{802}^2$$

or

$$t_{802} = \sqrt{t_{observed}^2 - t_{scope}^2}$$

That is, the observed rise time must be corrected for by the inherent oscilloscope rise time to determine the actual 802 rise time. Extending the method to include a circuit under test will determine circuit under test rise time:

$$t_{\text{observed}}^2 = t_{802}^2 + t_{\text{scope}}^2 + t_{\text{c.u.t.}}^2$$

or

$$t_{c.u.t.} = \sqrt{t_{observed}^2 - t_{802}^2 - t_{scope}^2}$$

# 3.3 OPERATION

In the following descriptions of operation, observe the pulse on an oscilloscope. In continuous mode, trigger oscilloscope on SYNC OUT. In all other modes, trigger on the trigger signal. (See figure 3-2 for pulse parameters.)

Observe the following constraints:

Delay  $\leq$  70% of period. Width  $\leq$  70% of period.

# 3.3.1 Continuous Pulses

Set the controls (and connectors) as follows:

| Control                      | Operation             |

|------------------------------|-----------------------|

| TRIG GATE INPUT<br>Connector | No signal present     |

| INT 50 $\Omega$ Switch       | ON                    |

| PERIOD Switch                | Desired range setting |

| Other Controls               | Set as desired        |

|                              |                       |

# 3.3.2 Wide Duty Cycle Pulses

For wider pulses than those that can be normally obtained, set up for a pulse with the complemented width, then press the COMP pulse switch ON. For example, if a 95 ns pulse with a 125 ns repetition rate is desired:

$$125 \text{ ns} - 95 \text{ ns} = 30 \text{ ns}$$

Set up for a 30 ns pulse, then press the COMP switch ON. (See figure 3-7.)

Figure 3-7. Greater Than 70% Duty Cycle Pulse

# 3.3.3 Externally Triggered Pulses

Set controls (and connectors) as follows:

| Control                      | Operation                                |

|------------------------------|------------------------------------------|

| PERIOD Switch                | TRIG                                     |

| TRIG/GATE INPUT<br>Connector | Apply TTL rectangular pulse              |

| INT 50 $\Omega$ Switch       | ON                                       |

| WIDTH Switch                 | Set to range desired (but not $ \Box $ ) |

| Other Controls               | Set as desired.                          |

# 3.3.4 Manually Triggered Pulses

Set controls (and connectors) as follows:

| Control        | Operation |

|----------------|-----------|

| PERIOD Switch  | MAN TRIG  |

| INT 50Ω Switch | ON        |

| Control        | Operation                                |

|----------------|------------------------------------------|

| WIDTH Switch   | Set to range desired (but not $ \Box $ ) |

| MAN TRIG       | Push to trigger                          |

| Other Controls | Set as desired                           |

# 3.3.5 Gated Pulses

Set up as in paragraph 3.3.1, except set the width of the TRIG GATE INPUT pulse to allow the desired number of output pulses.

# 3.3.6 Pulses With Width Controlled Externally

Set up as in paragraph 3.3.3, except set WIDTH switch to  $\square$ .

# 3.3.7 Double Pulses

For double pulses in any mode, additionally set controls as follows:

| Control   | Operation                                                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBL PULSE | ON                                                                                                                                                                    |

| DELAY     | Set for desired time between start of first pulse and second pulse of pulse pairs. (Since the same one-shot forms both pulses, a minimum recovery time is necessary.) |

Figure 4-1. Overall Block Diagram

# SECTION CIRCUIT DESCRIPTION

# 4.1 OVERALL BLOCK DIAGRAM

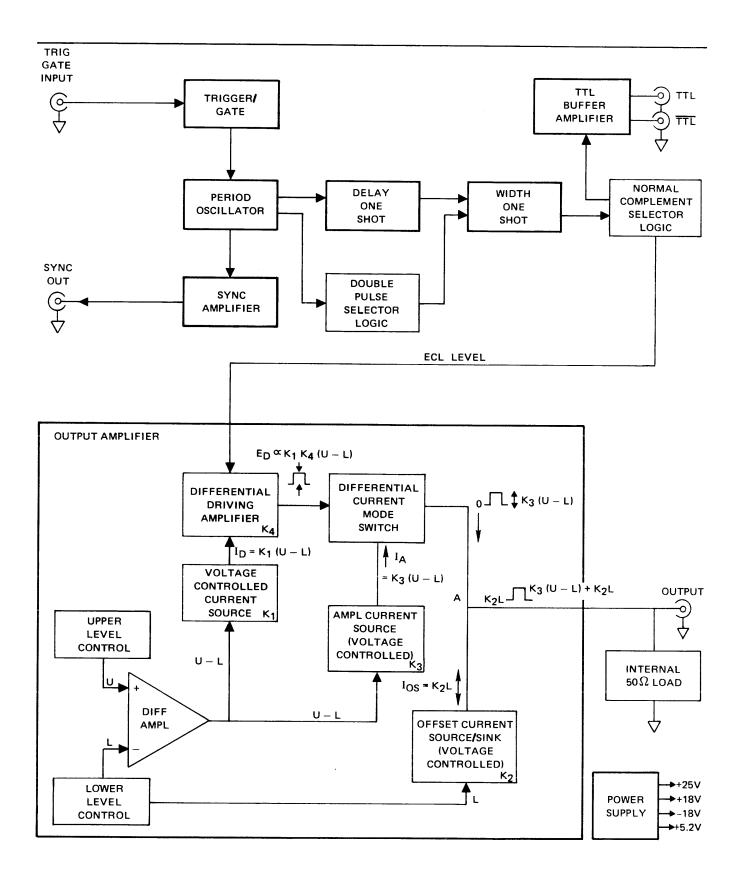

The Model 802 is made up of eight major circuit blocks: trigger/gate circuit, period oscillator, sync amplifier, delay one shot, width one shot, TTL buffer amplifier, output amplifier, and a power supply. (See figure 4-1.)

All the circuitry is on one PC board with a combination of ECL logic gates and discrete semiconductor devices. The ECL logic, in addition to making up individual circuit blocks, serves as a signal coupling medium between the blocks. The signal path changes depending on the mode selected.

# 4.2 PERIOD OSCILLATOR

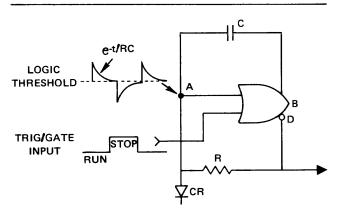

A simplified diagram of the period oscillator, an ECL multivibrator, appears in figure 4-2.

Figure 4-2. Simplified Diagram of the Period Oscillator

The RC time constant determines the charge and discharge rates for capacitor C and, therefore, the frequency of operation.

Positive feedback via the path through C results in a stable oscillator. Varying resistor R changes the frequency over a 10:1 range. Note that since the charging and discharging current are equal but opposite, the resulting waveform has a 50% duty cycle.

The oscillator may be gated via the trig/gate input. Whenever this input is high, it forces output D low and stops the oscillator. The oscillator starts synchronously when the input goes low.

# 4.3 TRIGGER/GATE CIRCUIT

The trigger circuit consists of an ECL gate connected to provide positive feedback which forms a Schmitt trigger. An input divider adjusts the trigger level to approximately +1.4V. This makes the input compatible with TTL logic. Triggering always occurs on the positive edge and the source can be either external or internal via the manual trigger switch.

The output of the trigger circuit is always connected to the oscillator. Gating occurs automatically. Whenever the input to the trigger circuit is 1.4V, it forces the trig/gate input of the oscillator high (figure 4-2) and stops the oscillator.

When the trigger mode is selected, node A of the oscillator is pulled low via diode CR. The IC now acts as an inverter to the trig/gate input and passes the signal on to the delay one shot.

# 4.4 SYNC CIRCUIT

The sync circuit acts as a buffer amplifier between the oscillator and the external equipment. It provides a TTL output level from a  $50\Omega$  source. The output from the sync circuit is an approximate square wave at the oscillator frequency.

When gating the generator, the sync signal should be taken from the gating source rather than the 802.

# 4.5 DELAY CIRCUIT

The delay one shot allows an adjustable time between the sync output and the leading edge of the final output pulse. The delay circuit consists of an ECL gate and discrete circuit one shot multivibrator. When the delay circuit is triggered by the oscillator, a timing capacitor is discharged by a constant current source until a threshold point is reached. The circuit then resets by rapidly recharging the timing capacitor. The output pulse from the ECL gate has a width proportional to the timing capacitor value and the magnitude of the current source. The pulse width is independent of the triggering rate as long as it is less than 70% of the trigger period.

# 4.6 WIDTH CIRCUIT

The width one shot determines the width of the output pulse. The width circuit, triggered by the trailing edge of the delay one shot, is identical in operation to the delay circuit. In the double pulse mode it is triggered on the leading and trailing edges of the delay one shot pulse. When the mode is selected, the delay and width one shots are disabled and the oscillator square wave passes through them to the output amplifier. An exclusive OR gate allows either phase of the width one shot output to be selected as the signal to drive the output amplifier.

# 4.7 TTL BUFFER AMPLIFIER

The output of the width one shot drives a current mode switch, the TTL buffer amplifier, in addition to the output amplifier. This switch is designed to drive TTL level signals into  $50\Omega$  loads. Both signal phases, TTL and  $\overline{\text{TTL}}$ , are available simultaneously.

# 4.8 OUTPUT AMPLIFIER

The output amplifier (figure 4-1) establishes the pulse lower level by passing a constant current through the  $50\Omega$  load. The current is provided by a voltage controlled current source programmed by the lower level control potentiometer. A current pulse of the proper amplitude is now added at node A to this base line for the duration of the width one shot time. The amplitude of the current pulse is equal to the difference between the upper and lower level controls (U-L). The upper level will be (U-L)+L=U at the output.

In order to generate a current pulse, the width one shot drives a current mode switch via a driving amplifier. The current mode switch connects a current source to the load whenever the output of the width one shot is high. The current source is voltage controlled and its output is equal to the difference between the upper and lower level controls (U-L).

The output of the driving amplifier varies in amplitude directly with the output level programmed by the level controls. This prevents overdriving the current mode switch and distorting the output at low levels.

Note that changing the lower level control will change both the base line and the current pulse amplitude which will cause the upper level to remain fixed. That is (U-L)+L=U, regardless of the value of L.

The internal  $50\Omega$  load may be switched in or out depending on the application.

# 4.9 POWER SUPPLY

The power supply converts the line voltage to four regulated dc voltages which power all the other circuit blocks.

# 4.10 MODES OF OPERATION

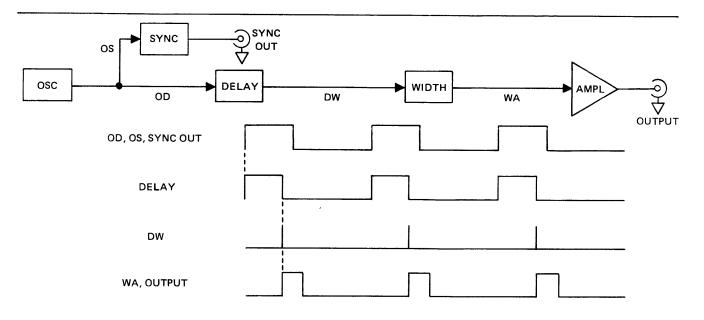

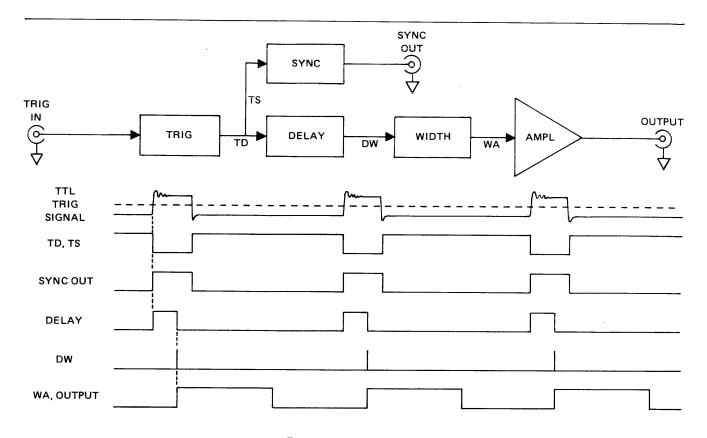

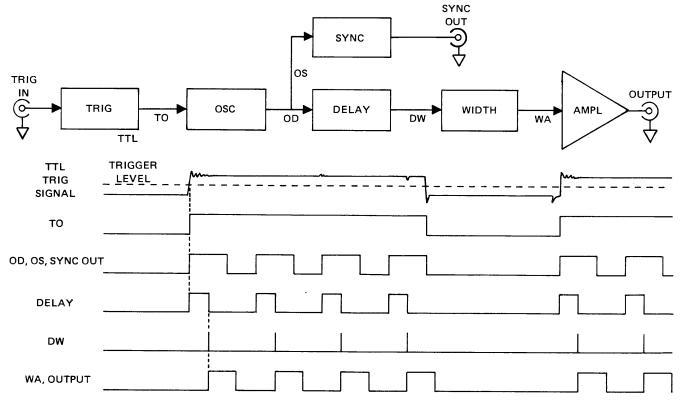

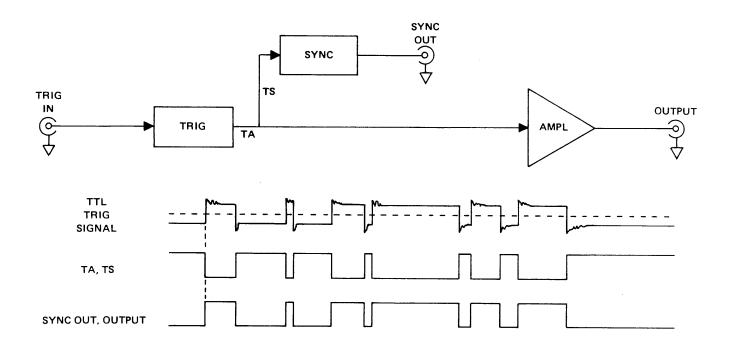

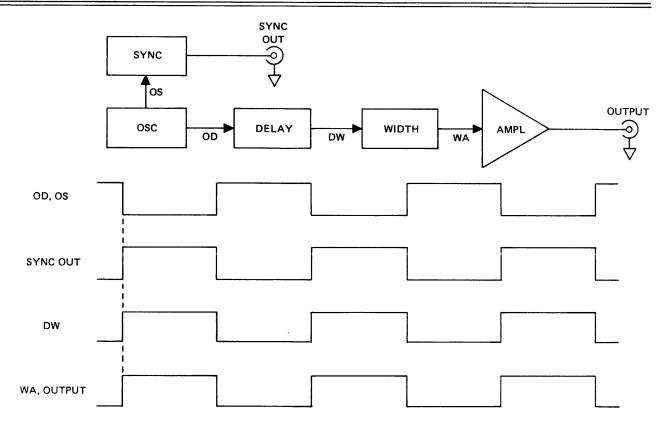

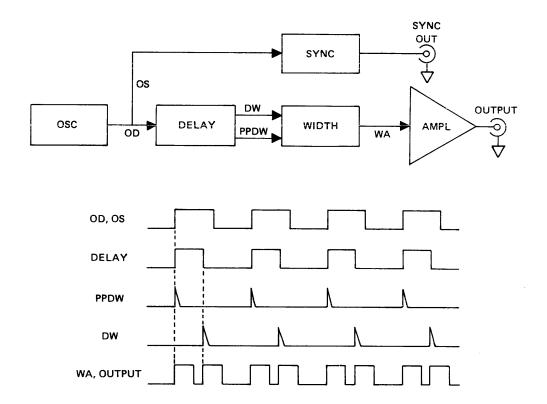

The major circuit block connections depend on the mode of operation selected. Block diagrams of the major modes and key waveforms are shown in figures 4-3 through 4-8.

Figure 4-3. Continuous Mode

Figure 4-4. Trigger Mode

Figure 4-5. Gate Mode

Figure 4-6. External Width Mode

Figure 4-7. Continuous Square Wave Mode

Figure 4-8. Continuous Double Pulse Mode

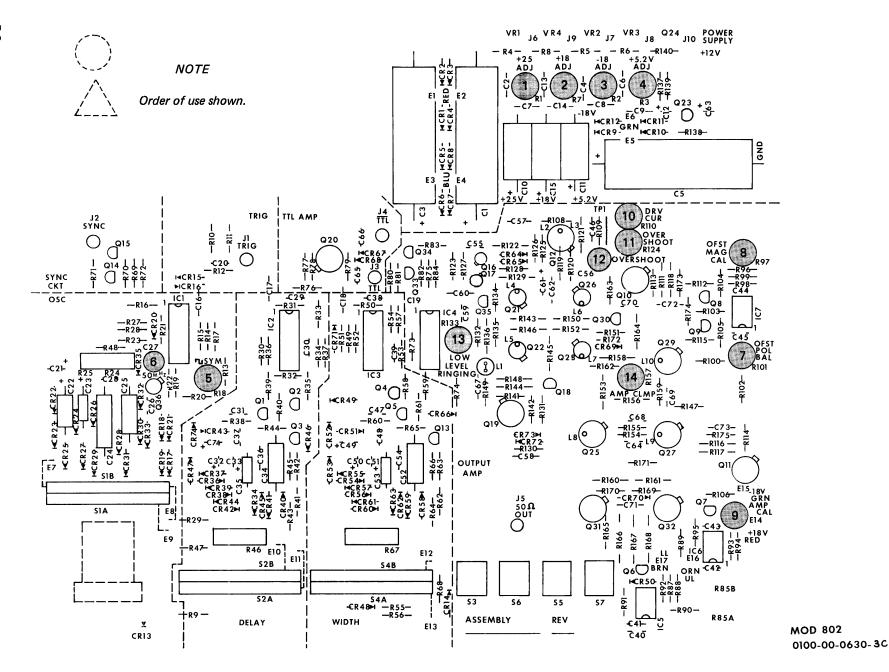

Figure 5-1. Calibration Points

# SECTION **5**CALIBRATION

#### 5.1 FACTORY REPAIR

Wavetek maintains a factory repair department for those custormers not possessing the necessary personnel or test equipment to maintain the instrument. If an instrument is returned to the factory for calibration or repair, a detailed description of the specific problem should be attached to minimize turnaround time.

# 5.2 REQUIRED TEST EQUIPMENT

# 5.3 REMOVING GENERATOR COVERS

- Invert the instrument and remove the four screws in the cover.

- 2. Turn the instrument upright, remove the top cover, and remove the four screws securing the bottom cover.

- Replace the cover and turn the instrument upside down.

# NOTE

Remove the cover only when it is necessary to make adjustments or measurements.

# 5.4 CALIBRATION

After referring to the following preliminary data, perform calibration, as necessary, per table 5-1. If performing partial calibration, check previous settings and adjustments for applicability. See figure 5-1 for calibration point location. location.

- 1. Unless otherwise noted, all measurements made at the  $\overline{TTL}$ ,  $\overline{TTL}$  or OUTPUT connectors must be terminated into a 50 $\Omega$  (±0.1%) load.

- Start the calibration by connecting the unit to an ac source and setting the front panel switches as follows:

| PERIOD 200 ns I 2 μs   |

|------------------------|

| PERIOD VERNIER Full cw |

| PULSE MODE OFF         |

| DELAY OFF              |

| WIDTH \_               |

| LOWER LEVEL            |

| UPPER LEVEL +10V       |

Allow the unit to warm up at least 30 minutes for final calibration. Keep the instrument covers on to maintain heat. Remove covers only to make adjustments or measurements.

Table 5-1. Calibration Chart

| Step | Check           | Tester | Cal<br>Points | Control<br>Settings | Adjust | Desired<br>Results | Remarks |

|------|-----------------|--------|---------------|---------------------|--------|--------------------|---------|

| 1    | Power<br>Supply | DVM    | -             |                     | R1     | +25V ±0.10V        |         |

| 2    |                 |        | _             |                     | R7     | +18V ±0.05V        |         |

| 3    |                 |        | _             | _                   | R2     | -18V ±0.05V        |         |

| 4    |                 |        | -             | _                   | R3     | +5.2V ±0.05V       |         |

Table 5-1. Calibration Chart (Continued)

| Step | Check                       | Tester | Cal<br>Points | Control<br>Settings                                                | Adjust      | Desired<br>Results             | Remarks                                                                                                                       |

|------|-----------------------------|--------|---------------|--------------------------------------------------------------------|-------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 5    | Duty Cycle                  | Scope  | TTL           | R157: Full cw                                                      | R18         | 50% duty cycle ±0.5%           |                                                                                                                               |

| 6    |                             |        |               | PERIOD: 20 ns   200 ms<br>PERIOD VERNIER: Full<br>ccw              | C27         | 51 MHz (19.6 ns)               |                                                                                                                               |

| 7    | Output<br>Amplifier         | DVM    | ОИТРИТ        | PERIOD: TRIG<br>COMP: ON<br>LOWER LEVEL: Full cw,<br>then full ccw | R101        | Equal cw & ccw voltage         |                                                                                                                               |

| 8    |                             |        |               | LOWER LEVEL: Full cw                                               | R97         | +10.5V ±0.05V                  | Repeat steps 7 and once.                                                                                                      |

| 9    |                             |        |               | LOWER LEVEL: 0V on DVM                                             |             |                                | Loosen and realign<br>LOWER LEVEL<br>knob at 0V, if<br>necessary.                                                             |

| 10   |                             |        |               | UPPER LEVEL: Full cw<br>COMP: OFF                                  | R107        | +10.5V ±0.05V                  |                                                                                                                               |

| 11   |                             |        |               | UPPER LEVEL: 0V on DVM                                             |             |                                | Loosen and realign<br>UPPER LEVEL<br>knob at 0V, if<br>necessary. Make<br>sure mechanical<br>interlock on knob<br>is engaged. |

| 12   |                             |        | TP1           | UPPER LEVEL: Full cw                                               | R110        | -0.6V ±0.05V                   |                                                                                                                               |

| 13   | Overshoot<br>& Ringing      | Scope  | ОИТРИТ        | INT 50Ω: ON<br>LOWER LEVEL: 0V                                     | R124<br>C56 | Minimum overshoot<br>& ringing |                                                                                                                               |

| 14   |                             |        |               | UPPER LEVEL: +0.5V                                                 | R133        | Minimum ringing                | Repeat steps 13 and 14 once.                                                                                                  |

| 15   | Overshoot<br>& Rise<br>Time |        |               | UPPER LEVEL: Full cw<br>LOWER LEVEL: Make a<br>+5V pulse           | R157        | Minimum overshoot              | Maintain ≥ 5.1V pulse and ≤ 5 ns rise time. A slight readjustment of R110 may be necessary.                                   |

# SECTION **G**TROUBLESHOOTING

# 6.1 INTRODUCTION

This section is organized as follows:

Safety

Circuit Board Access

Basic Techniques

Troubleshooting Individual Components

Flow Charts

Refer to paragraph 5.2 for required test equipment.

# NOTE

Wavetek maintains a factory repair department for those customers not possessing the necessary personnel or test equipment to maintain the instrument. If an instrument is returned to the factory for calibration or repair, a detailed description of the specific problem should be attached to minimize turnaround time.

# 6.2 SAFETY

# 6.2.1 Precautions

Refer all servicing and calibration to a qualified electronic technician.

Always disconnect the power cord when working on this instrument, unless electrical measurements are being taken. Never attempt to isolate the safety ground lug of the power cord.

Be sure that the fuse rating is correct and that the line voltage selector card is set to the proper range (refer to section 2).

Line voltage is present on the circuit board of the ac power connector, even when the power switch is off. This voltage is only accessible if the shield is removed from the ac power connector.

# 6.2.2 Safety Check

Disconnect the power cord from facility power and check that the resistance from the cord earth ground terminal to the instrument front panel metal is less than one ohm. Press the power switch on an measure the resistance between the instrument front panel metal and each of the power cord's two matching terminals. Resistance to each terminal should be greater than two megohms. Check the fuse for proper type and value. Remove the instrument covers and inspect the power supply and circuit boards for evidence of overheating or arcing. Check lines and cables for good physical connections. Correct any discrepancies detected.

#### 6.3 CIRCUIT BOARD ACCESS

Remove the top cover (paragraph 5.3) for access to the circuit board. Remove the four screws securing the board to the bottom cover for access to the bottom of the board.

# 6.4 BASIC TECHNIQUES

Troubleshooting requires no special technique. Listed below are a few reminders of basic electronic fault isolation.

- Check control settings carefully. Many times a seemingly malfunction is an incorrect control setting, or a knob that has loosened on its shaft.

- Check associated equipment connections. Make sure that all connections are securely connected to the correct connector.

- Perform the calibration procedure. Many out-of-specification indications can be corrected by performing specific calibration procedures.

- Visually check the interior of the instrument. Look for such indications as broken wires, charred components and loose leads.

- 5. Try to isolate the problem to a specific circuit by checking generator operation in all modes and referring to the block diagrams for each mode (see figures 4-3 thru 4-8). After the problem has been isolated to a specific stage, check the dc operating voltages at the pins of all solid state devices within that stage.

- Check the associated passive elements with a high impedance ohmmeter (instrument unplugged) before replacing a suspected semiconductor device.

# 6.5 TROUBLESHOOTING INDIVIDUAL COMPONENTS

# 6.5.1 Transistor

A transistor is defective if more than one volt is measured across its base emitter junction in the forward direction.

A transistor when used as a switch may have a few volts reverse bias voltage base to emitter.

If the collector and emitter voltages are the same, but the base emitter voltage is less than 500 mV forward voltage (or reversed bias), the transistor is defective.

A transistor is defective if its base current is larger than 10% of its emitter current (calculate currents from voltage across the base and emitter series resistors).

#### 6.5.2 Diode

A diode is defective if there is greater than 1 volt (typically 0.7 volts) forward voltage across it (except Zener and LED).

# 6.5.3 Operational Amplifier

The "+" and "-" inputs of an operational amplifier will have less than 15 mV voltage difference when operating under normal conditions.

If the output voltage stays at maximum positive, "+" input voltage should be more positive than "-" input voltage, or vice versa; otherwise, the operational amplifier is defective.

# 6.5.4 FET Transistor

No gate current should be drawn by the gate of an FET transistor. If so, the transistor is defective.

The gate-to-source voltage is always reverse biased under a normal operating condition; e.g., the source voltage is more positive than the gate voltage for 2N5485, and the source voltage is more negative than gate voltage for a 2N5462. Otherwise, the FET is defective.

# 6.5.5 MOSFET Transistor

For MOSFET's such as the SD214 or SD215, a positive gate source voltage causes the device to conduct drain current. Zero volts or a negative voltage cause the device to pinch off. A MOSFET transistor can be damaged by a static charge

buildup when out of the circuit. Keep MOSFET leads shorted together until soldered in the circuit board.

# 6.5.6 Capacitor

Shorted capacitors have zero volts across their terminals.

An unopened capacitor can be located (but not always) by using a good capacitor connected in parallel with the capacitor under test and observing the resulting effect.

#### 6.5.7 ECL Gate

The emitter coupled logic using NOR logic is:

| Inpu | ıts | NOR<br>Output | Exclusive OR<br>Output      |  |  |

|------|-----|---------------|-----------------------------|--|--|

| A    | В   | C = A + B     | $C = \overline{A \oplus B}$ |  |  |

| 0    | 0   | 1             | 1                           |  |  |

| 0    | 1   | 0             | 0                           |  |  |

| 1    | 0   | 0             | 0                           |  |  |

| 1    | 1   | 0             | 1                           |  |  |

The levels are:

"0" =

$$+3.4V \pm 0.1V$$

"1" =  $+4.3V \pm 0.1V$

Never short the output of an ECL gate to ground; this will damage the output transistor in the gate. Any input may be pulled high, even when driven by an output of another gate, by connecting a diode between the input and the +5.2V supply (anode to supply).

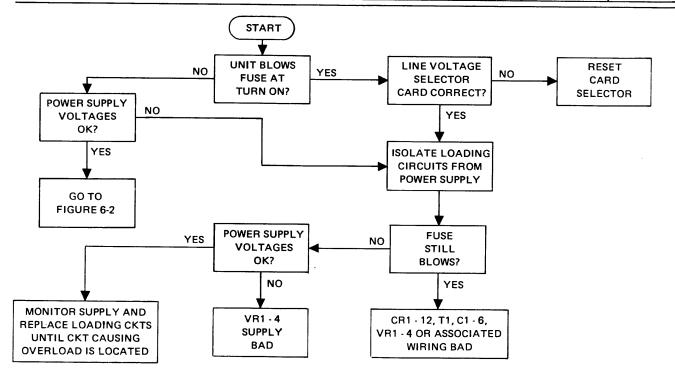

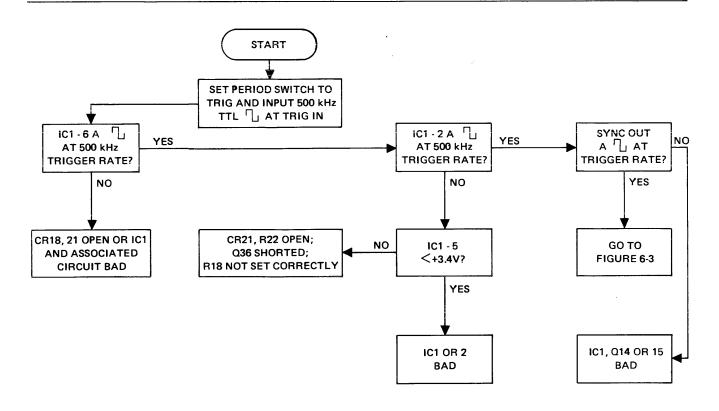

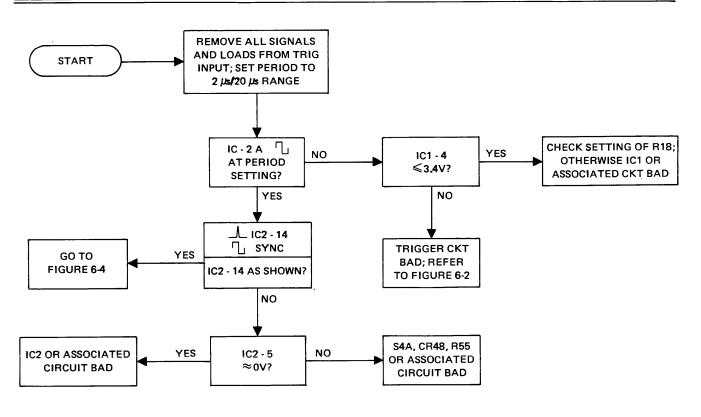

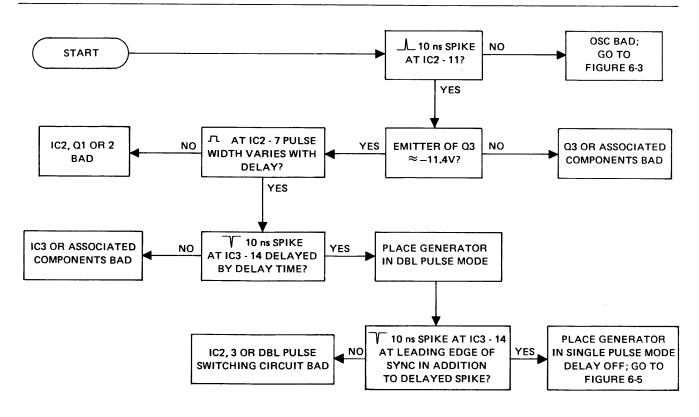

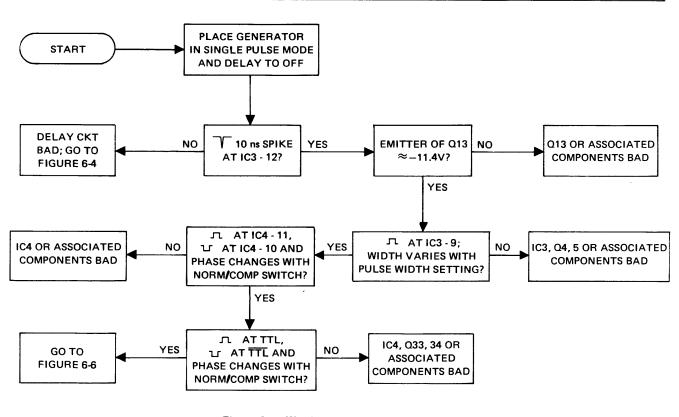

# **6.6 FLOW CHARTS**

The flow charts (see figures 6-1 thru 6-6) help isolate any malfunction to a specific stage. If you already know the specific circuit block at fault, go directly to that block in the flow chart. If a problem cannot be isolated to a portion of a flow chart, then follow the flow chart from the beginning.

If the problem cannot be located, return the instrument to the factory for servicing, with a description of the failure.

Before performing flow chart troubleshooting, set the front panel controls as follows:

| PERIOD 2 μs <b>l</b> 20 μs |

|----------------------------|

| PERIOD VERNIER 12 o'clock  |

| DELAY 10 ns i 100 ns       |

| DELAY VERNIER 12 o'clock   |

| WIDTH                      |

| WIDTH VERNIER 12:00        |

| LOWER LEVEL                |

| UPPER LEVEL +10V           |

| DBL PULSE OFF              |

| COMP OFF                   |

| INT $50\Omega$             |

Connect both the sync and the output BNC's to an oscilloscope with 3 foot  $50\Omega$  cables terminated with  $50\Omega$  feedthroughs.

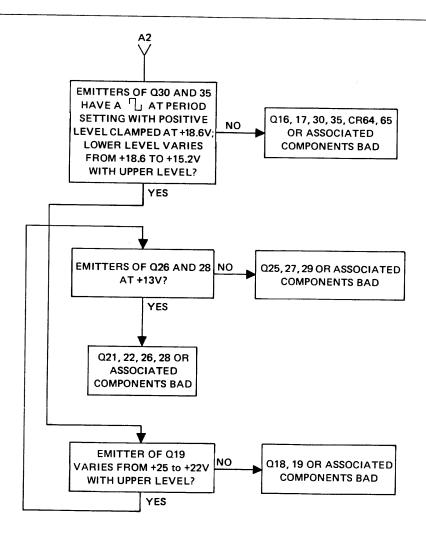

When troubleshooting the output amplifier, the flow chart in figure 6-6 should be followed. In addition, tables 6-1 and 6-2 provide additional guidance as to what voltages exist at the semiconductor devices and how they should vary with the output level controls.

Table 6-1. Level Control Dependent Voltages

| Level<br>Control<br>Knob<br>Setting | Output Waveform Into $50\Omega$ | E17<br>Voltage<br>Upper<br>Level | E16<br>Voltage<br>Lower<br>Level | TP1  | IC7-6 | Emitter<br>of Q6 | Emitter of Q19 |

|-------------------------------------|---------------------------------|----------------------------------|----------------------------------|------|-------|------------------|----------------|

|                                     | +10                             | -18                              | -18                              | -18  | -3.6  | +8.1             | +22            |

|                                     | +10                             | -18                              | 0                                | -0.6 | 0     | +8.1             | +22            |

| •                                   | + 5                             | -9                               | +9                               | -0.6 | +1.8  | +8.1             | +22            |

|                                     | 0 ———                           | 0                                | 0                                | -18  | 0     | 0                | +25            |

|                                     | 0                               | 0                                | +18                              | -0.6 | +3.6  | +8.1             | +22            |

| <u> </u>                            | -10                             | +18                              | +18                              | 0    | +3.6  | 0                | +25            |

# NOTE

These voltages apply with the controls set as follows.

| PERIOD TRIG             |

|-------------------------|

| DELAY OFF               |

| <i>WIDTH</i>            |

| COMP OFF                |

| DBL PULSE OFF           |

| $INT 50\Omega \dots ON$ |

| UPPER LEVEL Max cw      |

| LOWER LEVEL             |

| Transistor | В          | С          | E     | Transistor | В     | С     | E     |

|------------|------------|------------|-------|------------|-------|-------|-------|

| Q6         | +8.7       | +20.8      | +8.1  | Q22        | +18.6 | +12   | +20.5 |

| Q7         | -0.6       | -0.6       | 0     | Q23        | +10.8 | 0     | +11.4 |

| Q8         | 0          | +18        | ≈ 0   | Q24        | +11.4 | 0     | +12.0 |

| Q9         | 0          | <b>–18</b> | ≈ 0   | Q25        | +12.0 | +10.0 | +12.6 |

| Q10        | +18        | +13        | +18   | Q26        | +15.2 | +13.0 | +15.8 |

| Q11        | <b>–18</b> | -13        | -18   | Q27        | +12.0 | +10.0 | +12.6 |

| Q12        | -0.6       | +0.3       | -1.2  | Q28        | +15.2 | +13.0 | +15.8 |

| Q16        | +4.3       | +6.4       | +3.7  | Q29        | +12.0 | +10.0 | +12.6 |

| Q17        | +3.4       | +9.8       | +3.7  | Q30        | +14.6 | +12.0 | +15.2 |

| Q18        | +20.8      | 21.4       | +21.4 | Q31        | -12.0 | +10.0 | -12.6 |

| Q19        | +21.4      | 21.4       | +22.0 | Q32        | -12.0 | +10.0 | -12.6 |

| Q21        | +18.6      | +12        | +20.5 | Q35        | +18.0 | +12.0 | +18.6 |

Figure 6-1. Power Supply Troubleshooting

Figure 6-2. Trigger Circuit Troubleshooting

Figure 6-3. Oscillator Troubleshooting

Figure 6-4. Delay Circuit Troubleshooting

Figure 6-5. Width Circuit Troubleshooting

Figure 6-6. Output Amplifier Troubleshooting

Figure 6-6. Output Amplifier Troubleshooting (Continued)

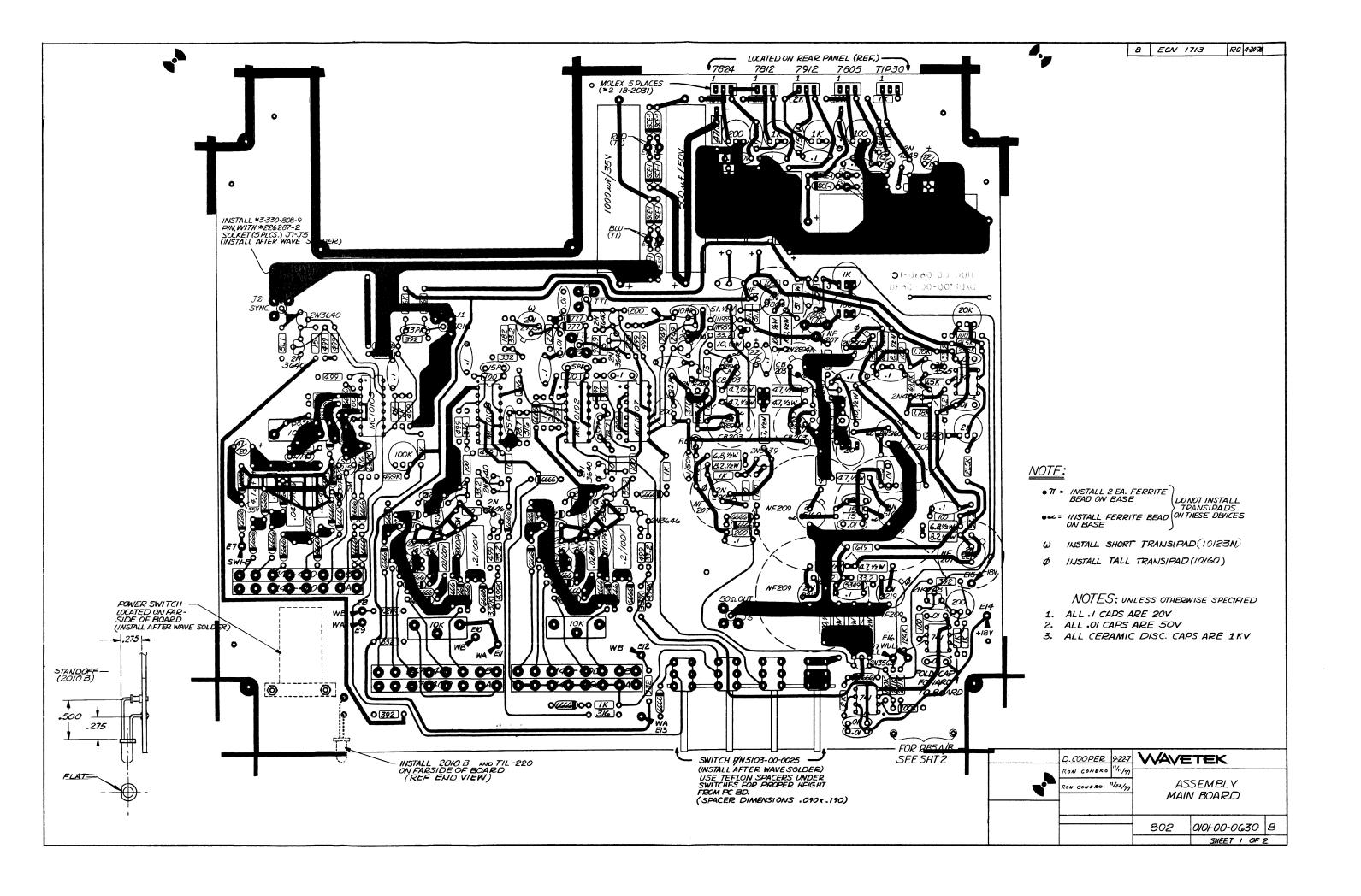

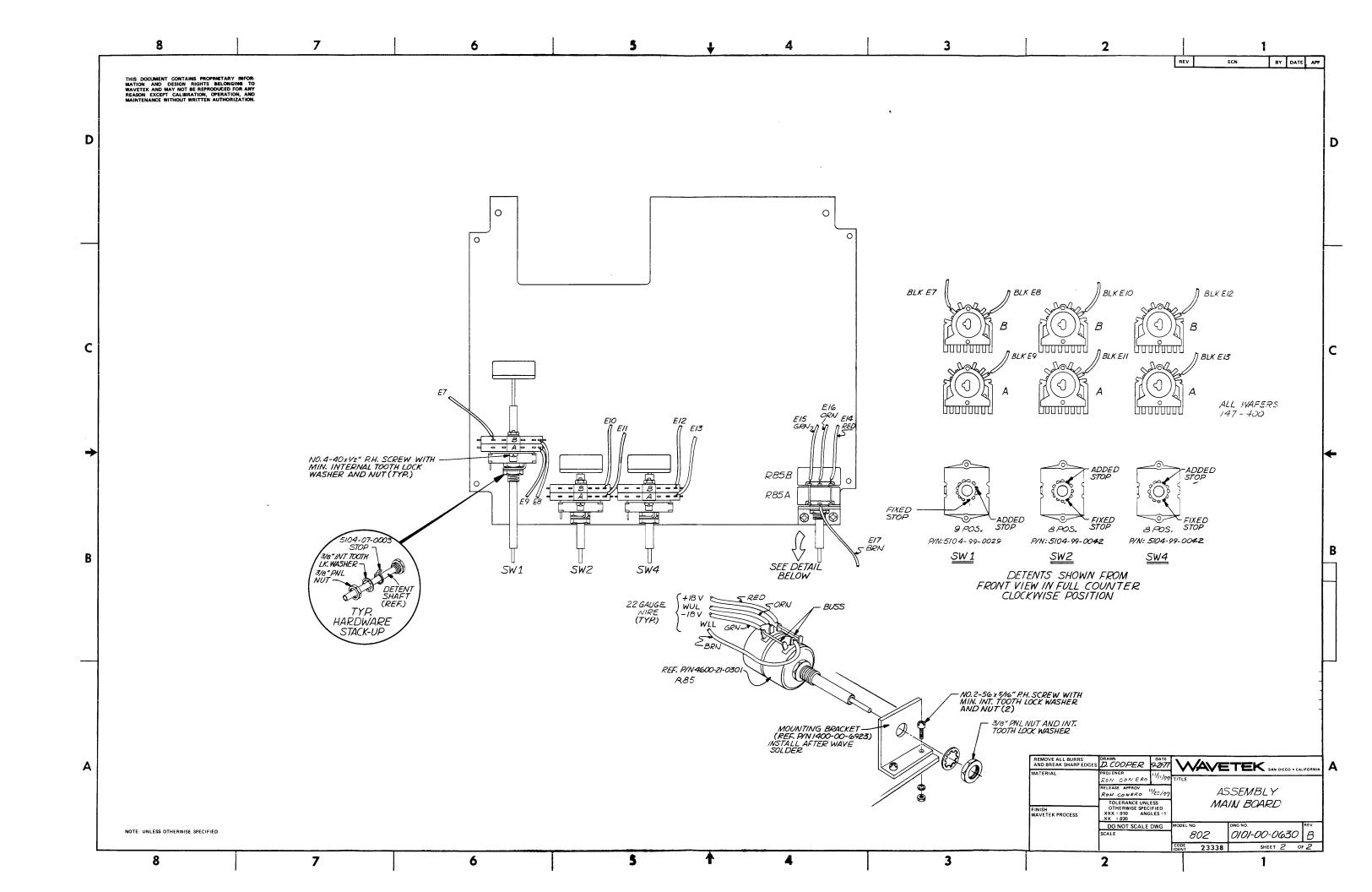

# SECTION PARTS AND SCHEMATICS

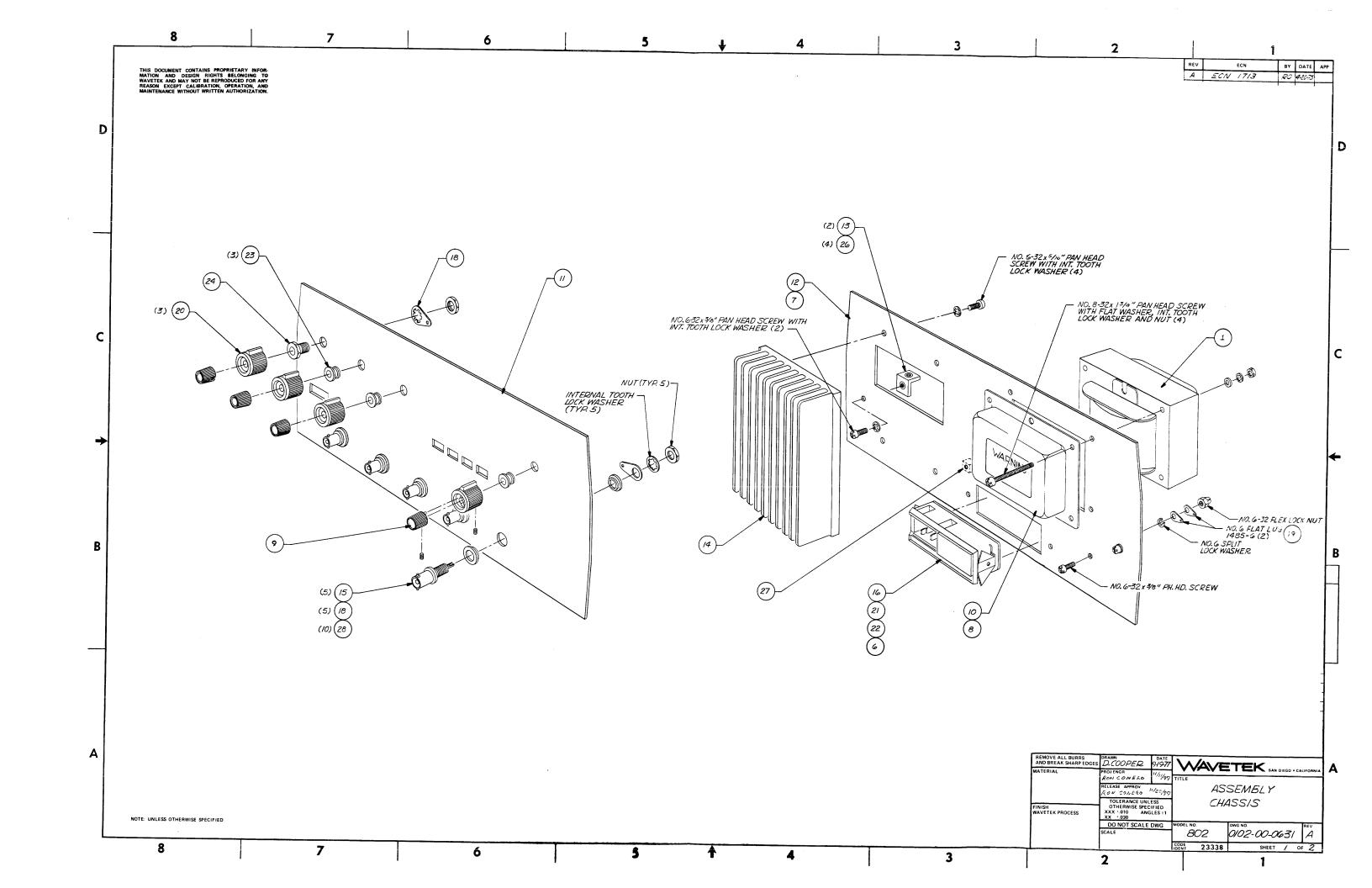

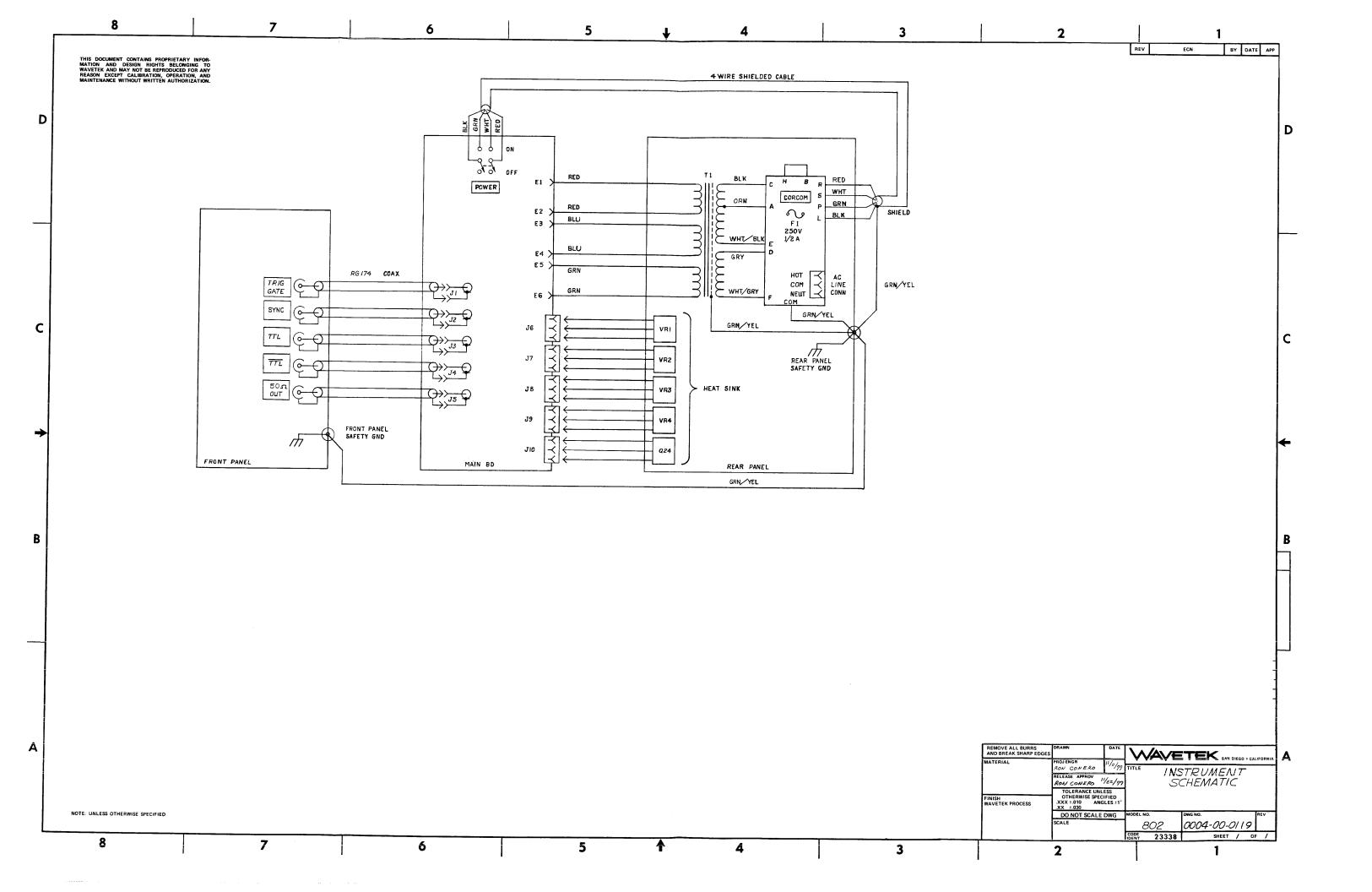

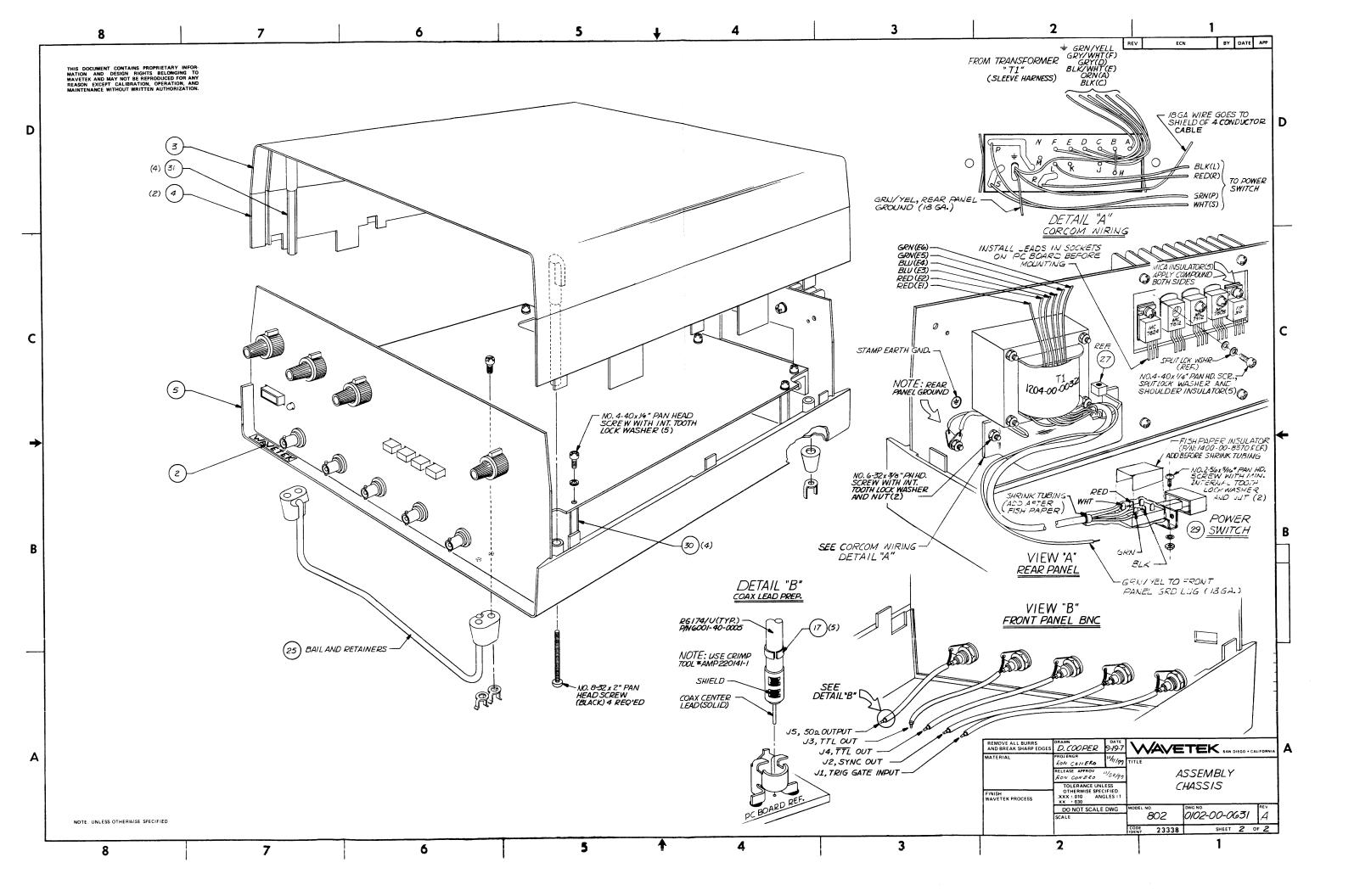

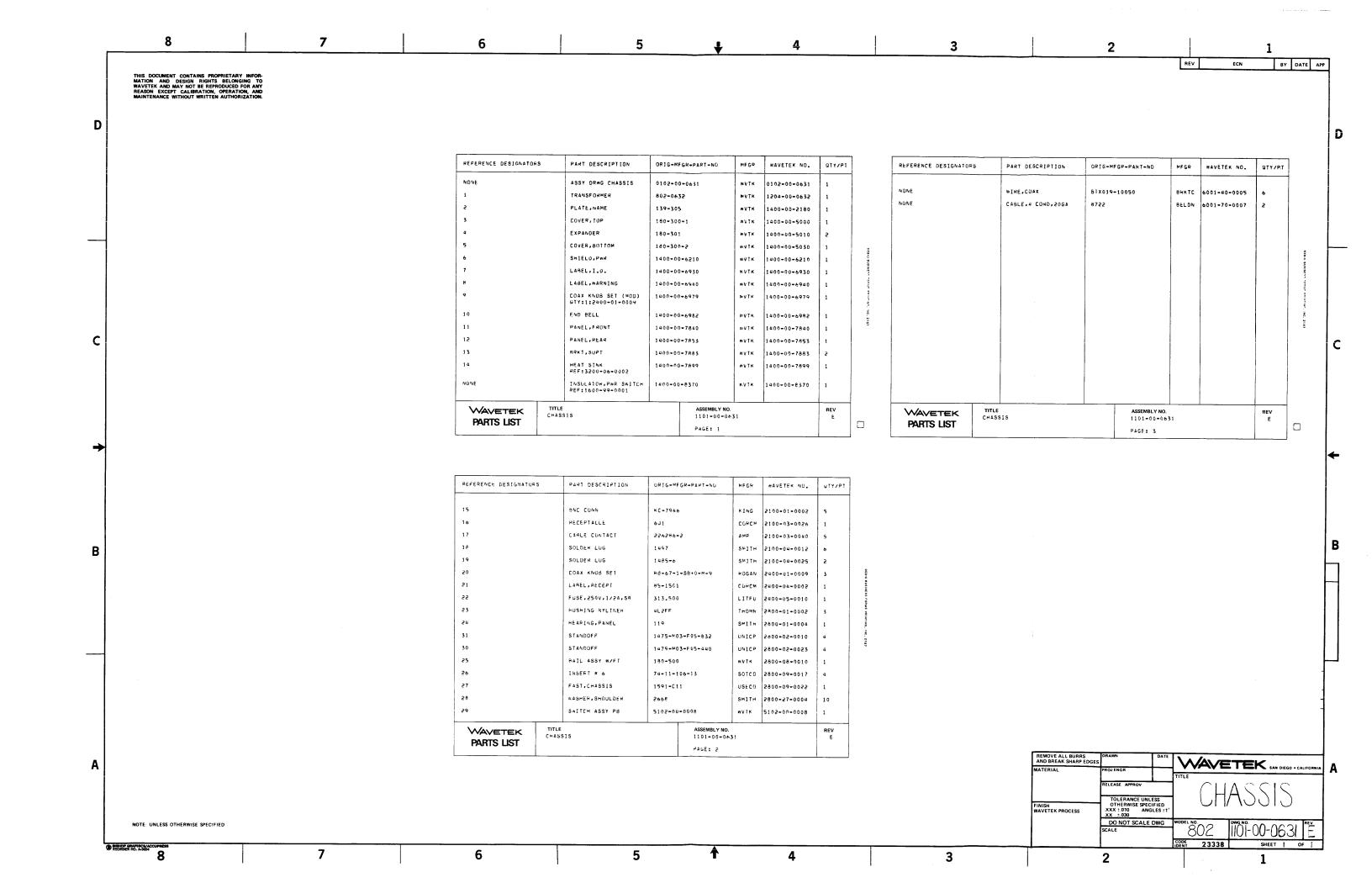

# 7.1 DRAWINGS

The following assembly drawings, parts lists and schematics are in the arrangement shown below.

# 7.2 ORDERING PARTS

When ordering spare parts, please specify part number, circuit reference, board, serial number of unit and the function performed.

# 7.3 ADDENDA

Under Wavetek's product improvement program, the latest electronic designs and circuits are incorporated into each Wavetek instrument as quickly as development and testing permit. Because of the time needed to compose and print instruction manuals, it is not always possible to include the most recent changes in the initial printing. Whenever this occurs, addendum pages are prepared to summarize the changes made and are inserted immediately inside the cover.

| Drawing                                                  | Drawing No.  | Drawing               | Drawing No.  |

|----------------------------------------------------------|--------------|-----------------------|--------------|

| Instrument Schematic Chassis Assembly Chassis Parts List | 0004-00-0119 | Main Board Assembly   | 0101-00-0630 |

|                                                          | 0102-00-0631 | Main Board Schematic  | 0103-00-0630 |

|                                                          | 1101-00-0631 | Main Board Parts List | 1100-00-0630 |