### INSTRUCTION MANUAL

## Model 191 20 MHz Pulse/Function Generator

#### O 1983 Wavetek

This document contains information proprietary to Wavetek and is provided solely for instrument operation and maintenance. The information in this document may not be duplicated in any manner without the prior approval in writing from Wavetek.

#### Wavetek Instruments Division

9045 Balboa Ave. San Diego, CA 92123 Tel: (619) 279-2200 800-223-9885 Fax: (619) 565-7942

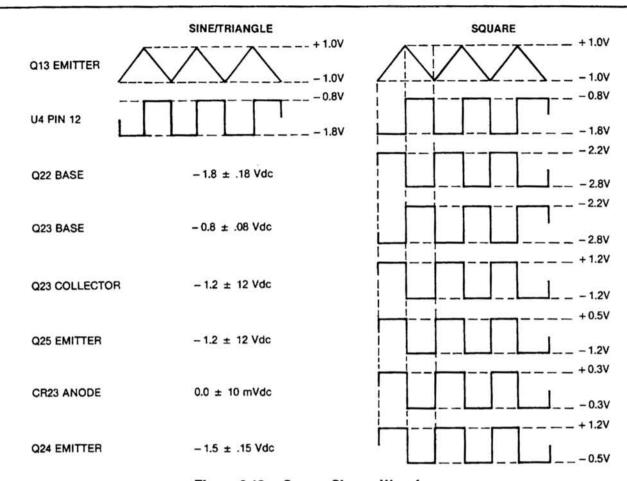

Manual Revision 8/91 Manual Part Number 1300-00-0181

### WARRANTY

Wavetek warrants that all products manufactured by Wavetek conform to published Wavetek specifications and are free from defects in materials and workmanship for a period of one (1) year from the date of delivery when used under normal operating conditions and within the service conditions for which they were furnished.

The obligation of Wavetek arising from a Warranty claim shall be limited to repairing, or at its option, replacing without charge, any product which in Wavetek's sole opinion proves to be defective within the scope of the Warranty. In the event Wavetek is not able to modify, repair or replace non-conforming defective parts or components to a condition as warrantied within a reasonable time after receipt thereof, Buyers shall be credited for their value at the original purchase price.

Wavetek must be notified in writing of the defect or nonconformity within the Warranty period and the affected product returned to Wavetek's factory or to an authorized service center within (30) days after discovery of such defect or nonconformity.

For product warranties requiring return to Wavetek, products must be returned to a service facility designated by Wavetek. Buyer shall prepay shipping charges, taxes, duties and insurance for products returned to Wavetek for warranty service. Except for products returned to Buyer from another country, Wavetek shall pay for return of products to Buyer.

Wavetek shall have no responsibility hereunder for any defect or damage caused by improper storage, improper installation, unauthorized modification, misuse, neglect, inadequate maintenance, accident or for any product which has been repaired or altered by anyone other than Wavetek or its authorized representative and not in accordance with instructions furnished by Wavetek.

#### **Exclusion of Other Warranties**

The Warranty described above is Buyer's sole and exclusive remedy and no other warranty, whether written or oral, is expressed or implied. Wavetek specifically disclaims the implied warranties of merchantability and fitness for a particular purpose. No statement, representation, agreement, or understanding, oral or written, made by an agent, distributor, representative, or employee of Wavetek, which is not contained in the foregoing Warranty will be binding upon Wavetek, unless made in writing and executed by an authorized Wavetek employee. Under no circumstances shall Wavetek be liable for any direct, indirect, special, incidental, or consequential damages, expenses, losses or delays (including loss of profits) based on contract, tort, or any other legal theory.

# **CONTENTS**

| SECTION 1 | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|           | 1.1 MODEL 191 1.2 SPECIFICATIONS 1.2.1 Main Generator 1.2.2 Pulse Generator 1.2.3 Frequency Precision 1.2.4 Amplitude Precision 1.2.5 Waveform Characteristics 1.2.6 General                                                                                                                                                                                                                                                                        | 1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-2<br>1-3                                    |

| SECTION 2 | INITIAL PREPARATION                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|           | 2.1 MECHANICAL INSTALLATION 2.2 ELECTRICAL INSTALLATION 2.2.1 Power Connection 2.2.2 Signal Connections 2.3 ELECTRICAL ACCEPTANCE CHECKOUT                                                                                                                                                                                                                                                                                                          | 2-1<br>2-1<br>2-1<br>2-1<br>2-1                                                  |

| SECTION 3 | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

|           | 3.1 CONTROLS AND CONNECTORS 3.2 OPERATION 3.2.1 Signal Termination 3.2.2 Manual Function Generator Operation 3.2.3 Voltage Controlled Function Generator Operation 3.2.4 Waveforms 3.2.5 Pulse Generator Operation 3.2.6 Burst Generator Operation                                                                                                                                                                                                  | 3-1<br>3-5<br>3-5<br>3-5<br>3-6<br>3-6<br>3-7                                    |

| SECTION 4 | CIRCUIT DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|           | 4.1 INTRODUCTION 4.2 FUNCTIONAL GENERATOR BLOCK DIAGRAM ANALYSIS 4.3 PULSE BLOCK DIAGRAM ANALYSIS 4.4 DETAILED CIRCUIT DESCRIPTIONS 4.4.1 Current Sources 4.4.2 Current Switch 4.4.3 Triangle Buffer Amplifier 4.4.4 Hysteresis Switch 4.4.5 Loop DC Delay Compensation 4.4.6 Capacitance Multiplier 4.4.7 Sine Converter 4.4.8 Trigger Circuit 4.4.9 Trigger Baseline 4.4.10 Sync 4.4.11 Square Shaper 4.4.12 Preamplifier 4.4.13 Output Amplifier | 4-1<br>4-2<br>4-2<br>4-5<br>4-5<br>4-6<br>4-6<br>4-7<br>4-7<br>4-7<br>4-8<br>4-8 |

|           | 4.4.14 Output Attenuator                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-9                                                                              |

# **CONTENTS (Continued)**

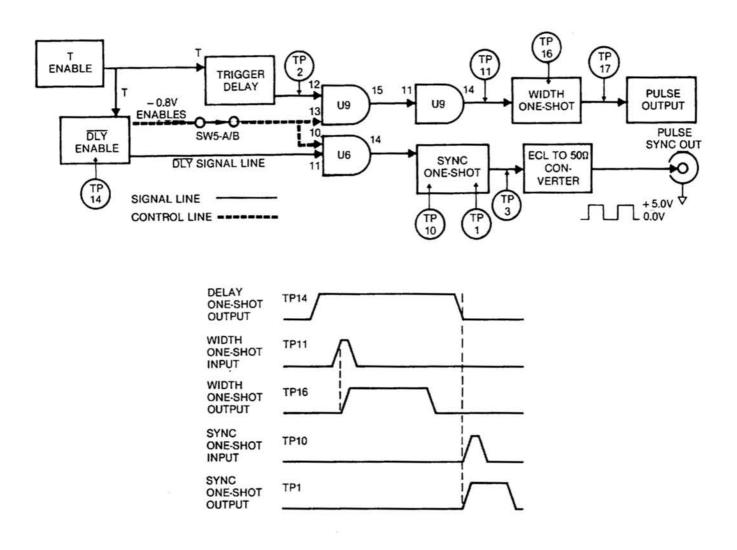

|           | 4.4.16 Variable Duty Cycle One-Shots 4.4.16.1 General Description 4.4.16.2 Width One-Shot 4.4.16.3 Delay One-Shot/Burst Oscillator 4.4.16.4 Sync One-Shot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-9<br>4-9<br>4-10<br>4-10                                                                                                               |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| SECTION 5 | CALIBRATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                          |

|           | 5.1 FACTORY REPAIR . 5.2 REQUIRED TEST EQUIPMENT . 5.3 COVER REMOVAL . 5.4 CALIBRATION .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-1<br>5-1<br>5-1<br>5-1                                                                                                                 |

| SECTION 6 | TROUBLESHOOTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |

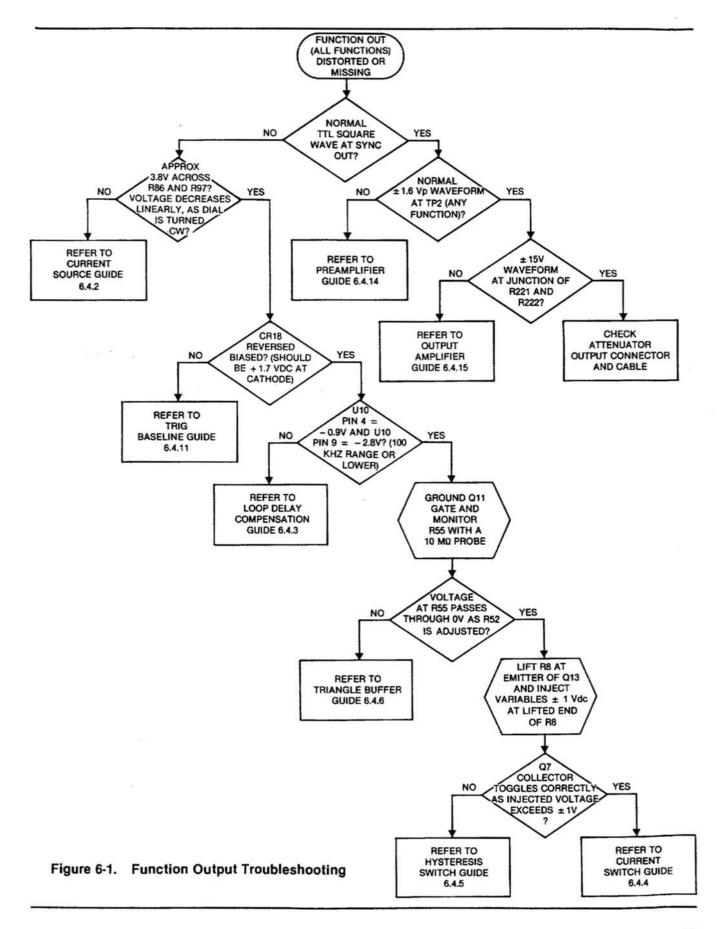

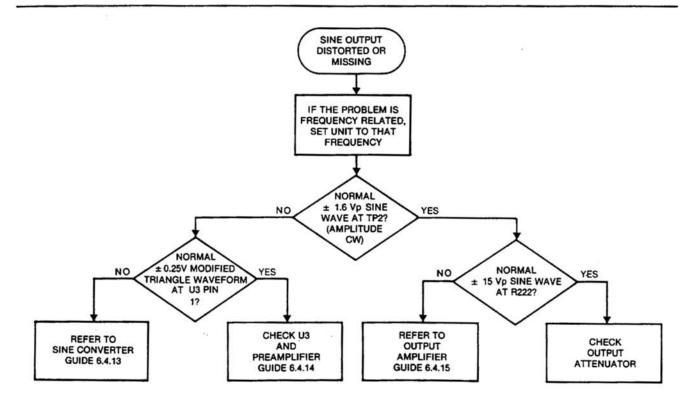

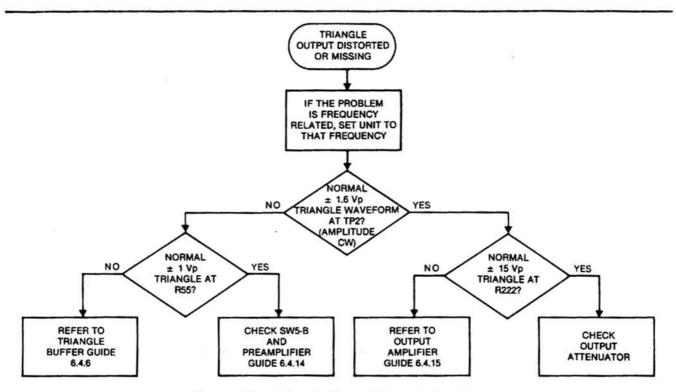

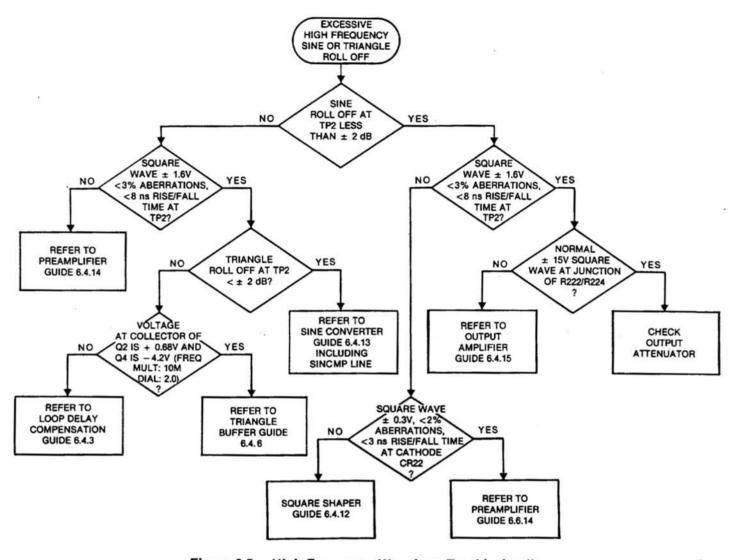

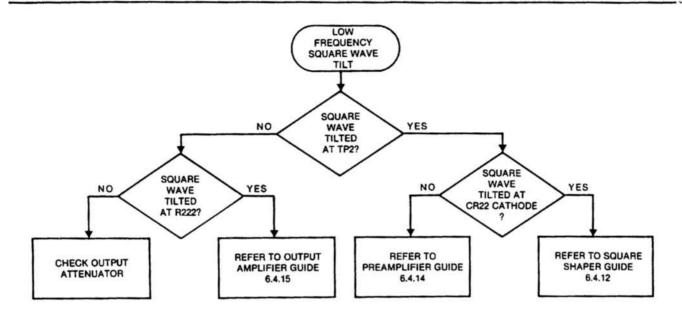

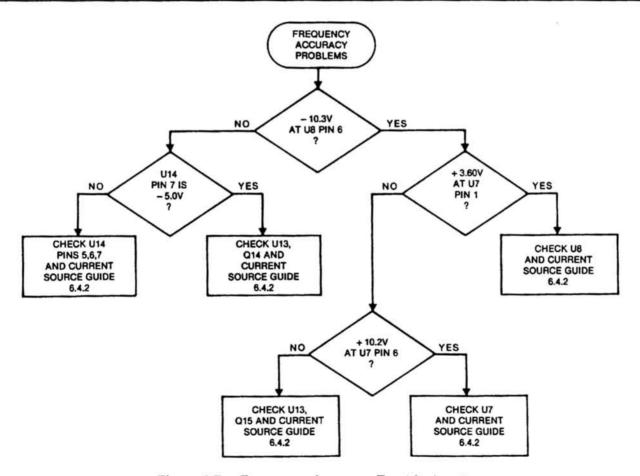

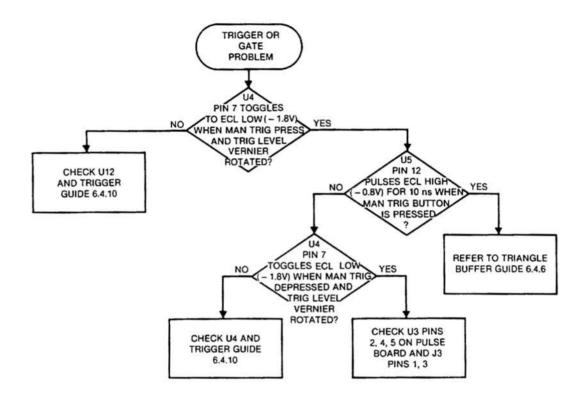

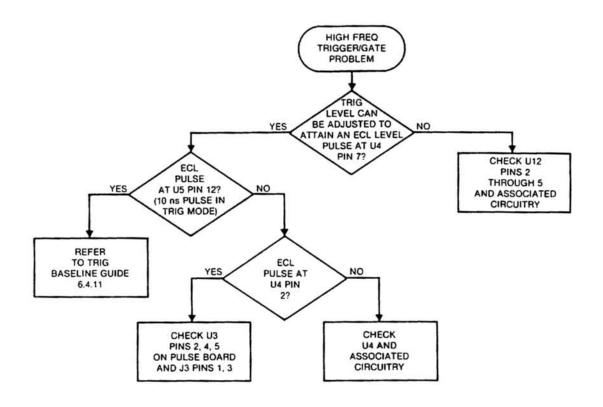

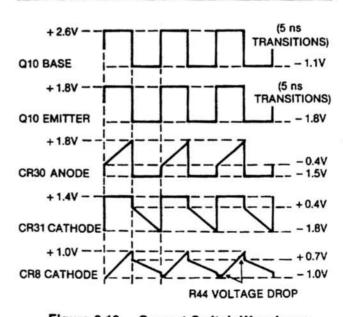

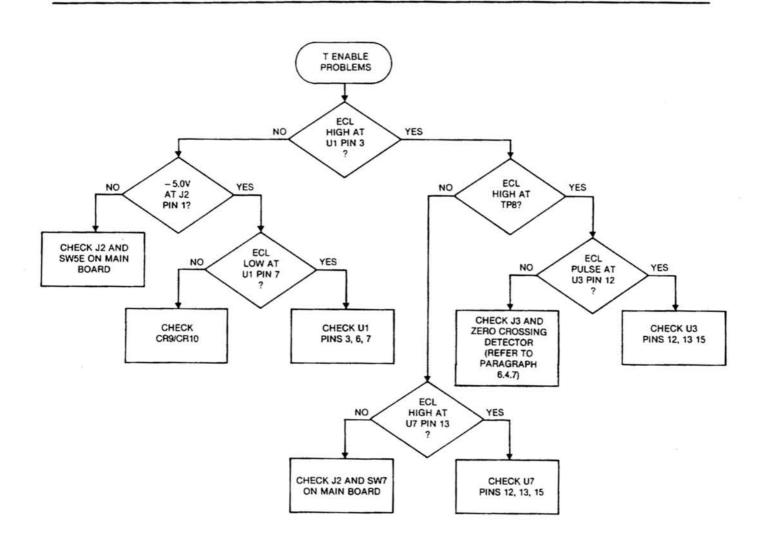

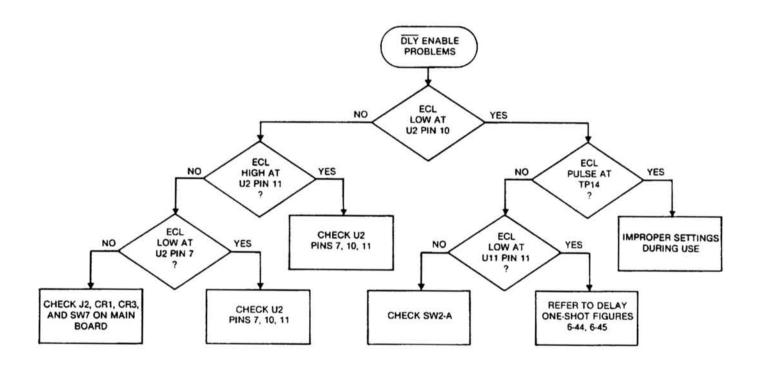

|           | 6.1 FACTORY REPAIR 6.2 BEFORE YOU START 6.3 MAIN BOARD TROUBLESHOOTING 6.3.1 Fuse Blows, No Dial Lamp 6.3.2 Power Supply > 100 mVp-p Ripple or Out of Specification 6.3.3 All Waveforms at FUNC OUT Distorted or Missing 6.3.4 Square Wave Distorted or Missing 6.3.5 Sine Wave Distorted or Missing 6.3.6 Triangle Distorted or Missing 6.3.7 Sync Output Distorted or Missing (FUNC OUT Normal) 6.3.8 Excessive High Frequency Sine or Triangle Roll Off 6.3.9 Low Frequency Square Wave Tilt 6.3.10 Time Symmetry Cannot Be Adjusted To Within Specifications 6.3.11 Frequency Accuracy and Dial Response Problems 6.3.12 Trigger, Gating and Trigger Baseline Problems 6.3.13 Voltage At VCG In Connector Not Changing Frequency Properly 6.3.14 DC Offset Not Functioning Correctly 6.3.15 Variable Symmetry Problems 6.4 CIRCUIT GUIDES 6.4.1 Power Supply Guide 6.4.2 Current Source Guide 6.4.3 Loop Delay Compensation Guide 6.4.4 Current Switch Guide 6.4.5 Hysteresis Switch Guide 6.4.6 Triangle Buffer Guide 6.4.7 Zero Crossing Detector Guide 6.4.9 Capacitance Multiplier Guide 6.4.1 Triange Cuide | 6-1<br>6-1<br>6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-5<br>6-5<br>6-6<br>6-6<br>6-6<br>6-10<br>6-11<br>6-12<br>6-12<br>6-13<br>6-14<br>6-14 |

|           | 6.4.10 Trigger Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-15<br>6-15                                                                                                                             |

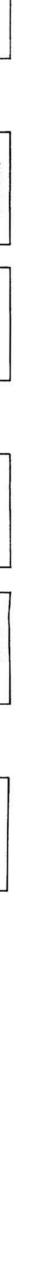

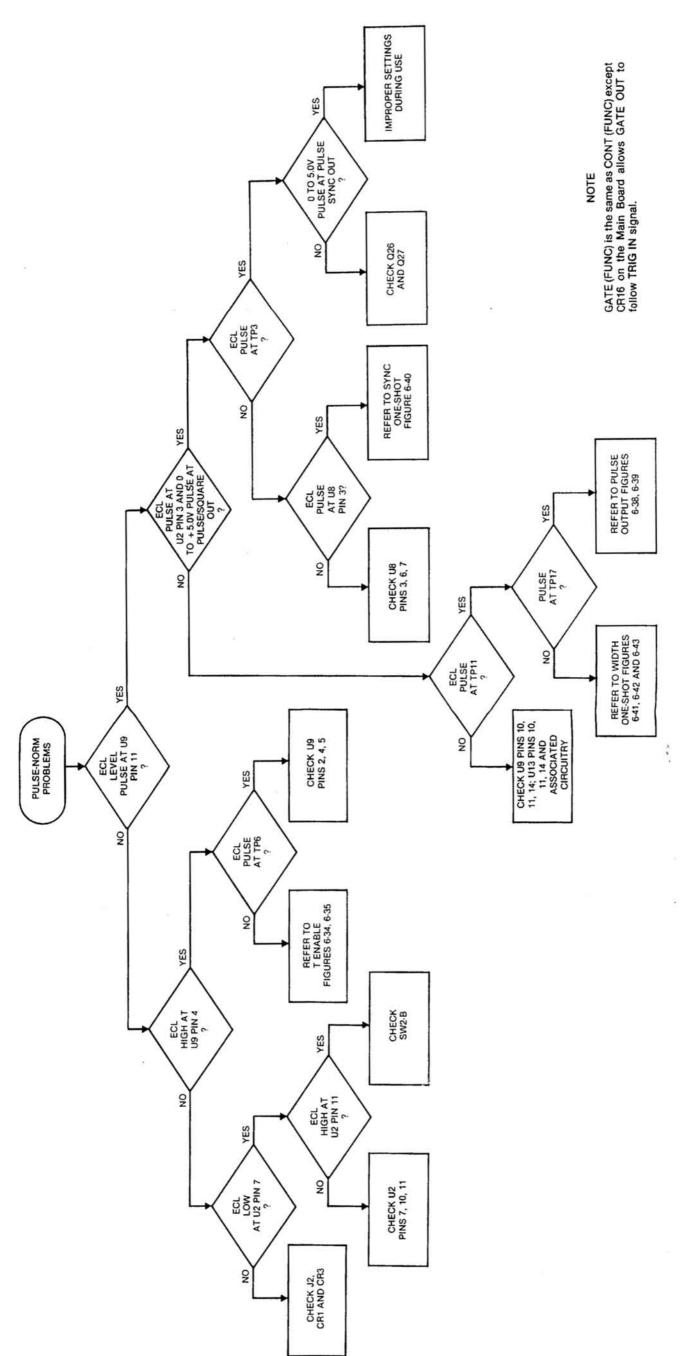

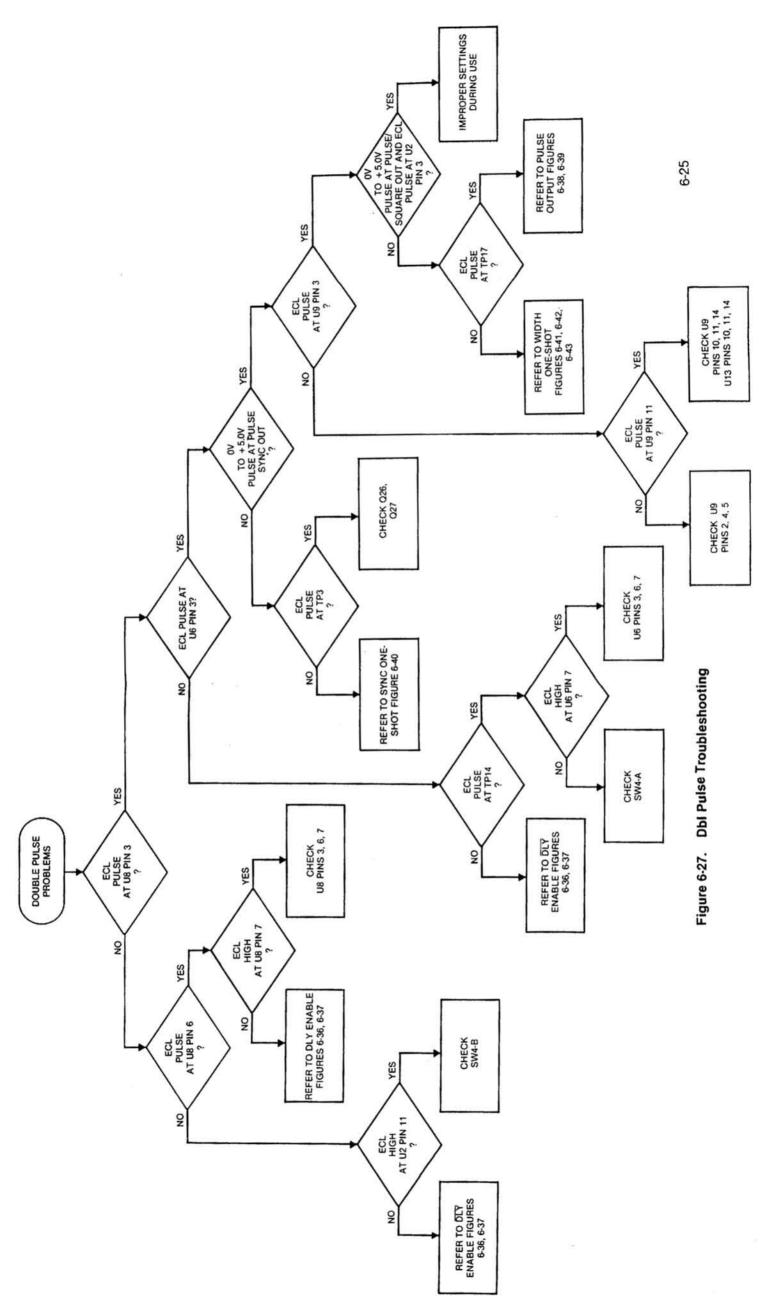

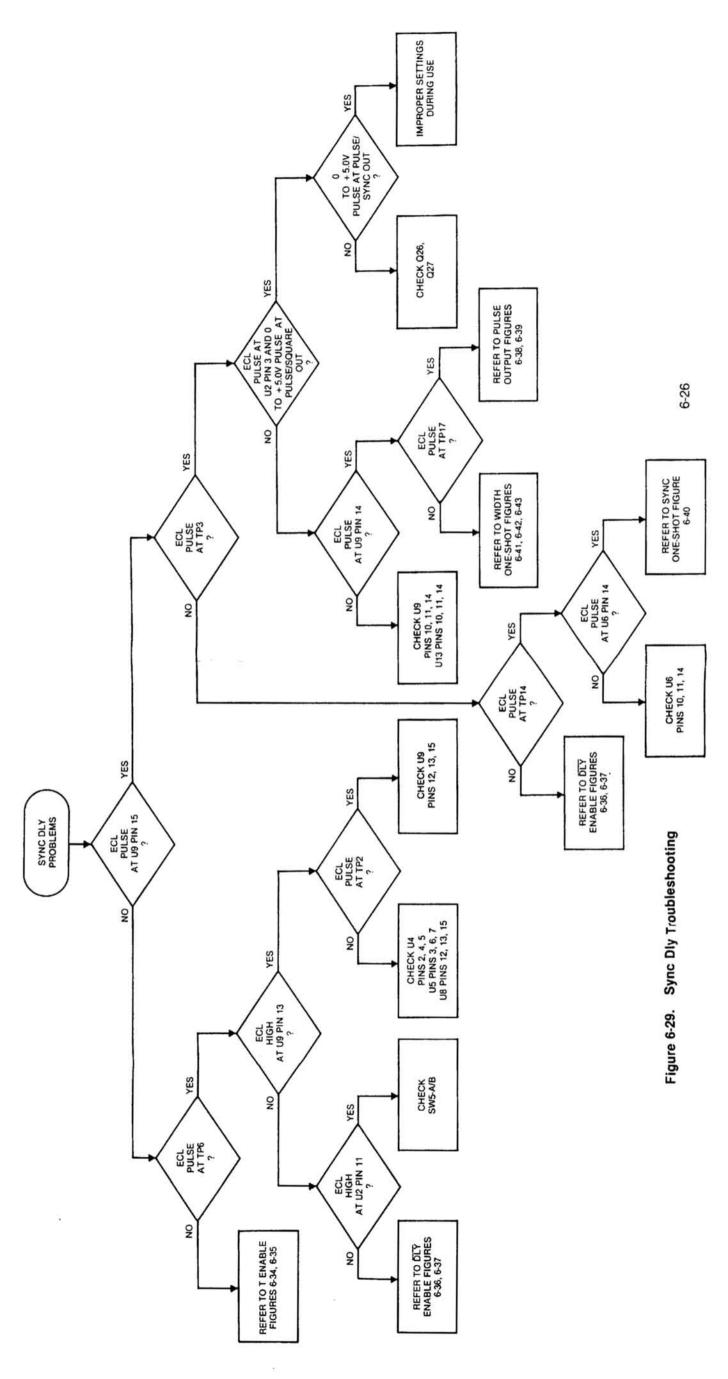

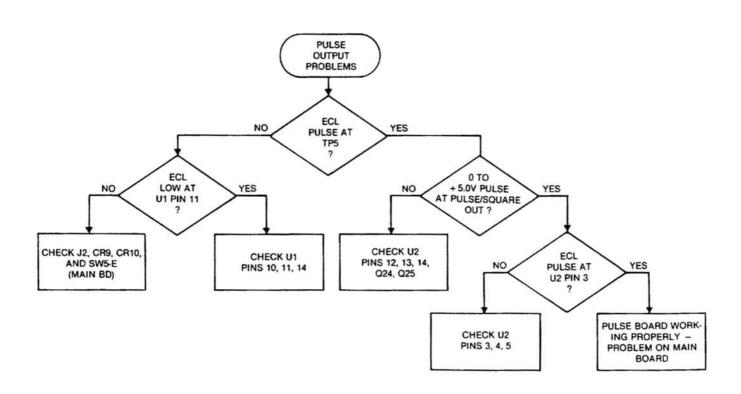

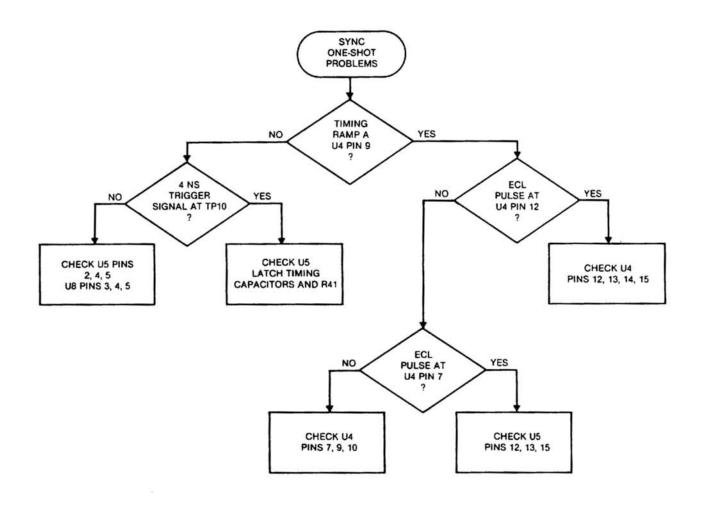

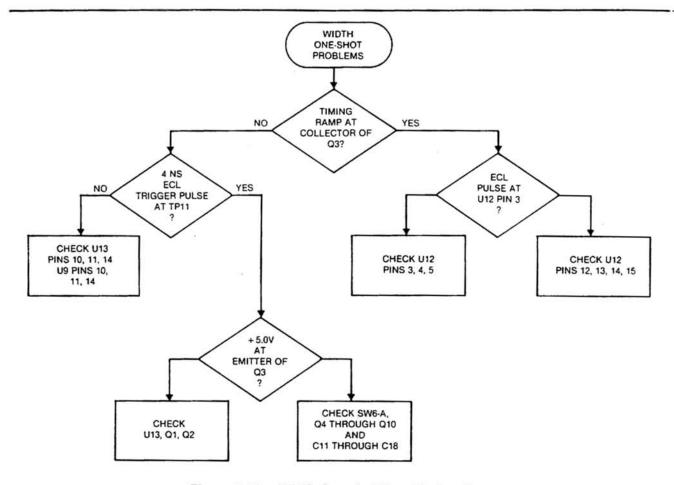

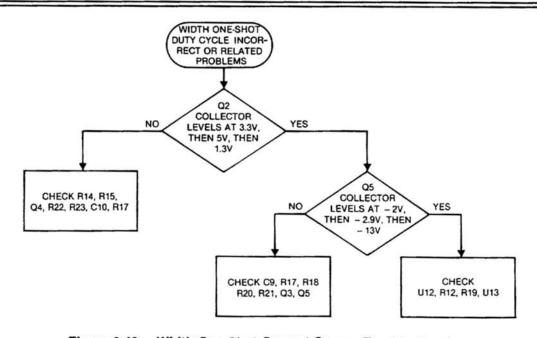

|           | 6.4.12 Square Shaper Guide 6.4.13 Sine Converter Guide 6.4.14 Preamplifier Guide 6.4.15 Output Amplifier Guide 6.5 PULSE BOARD TROUBLESHOOTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-16<br>6-18<br>6-18<br>6-19                                                                                                             |

|           | 6.6 TROUBLESHOOTING INDIVIDUAL COMPONENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6-38                                                                                                                                     |

# **CONTENTS** (Continued)

|           |       |     |        | T100 |

|-----------|-------|-----|--------|------|

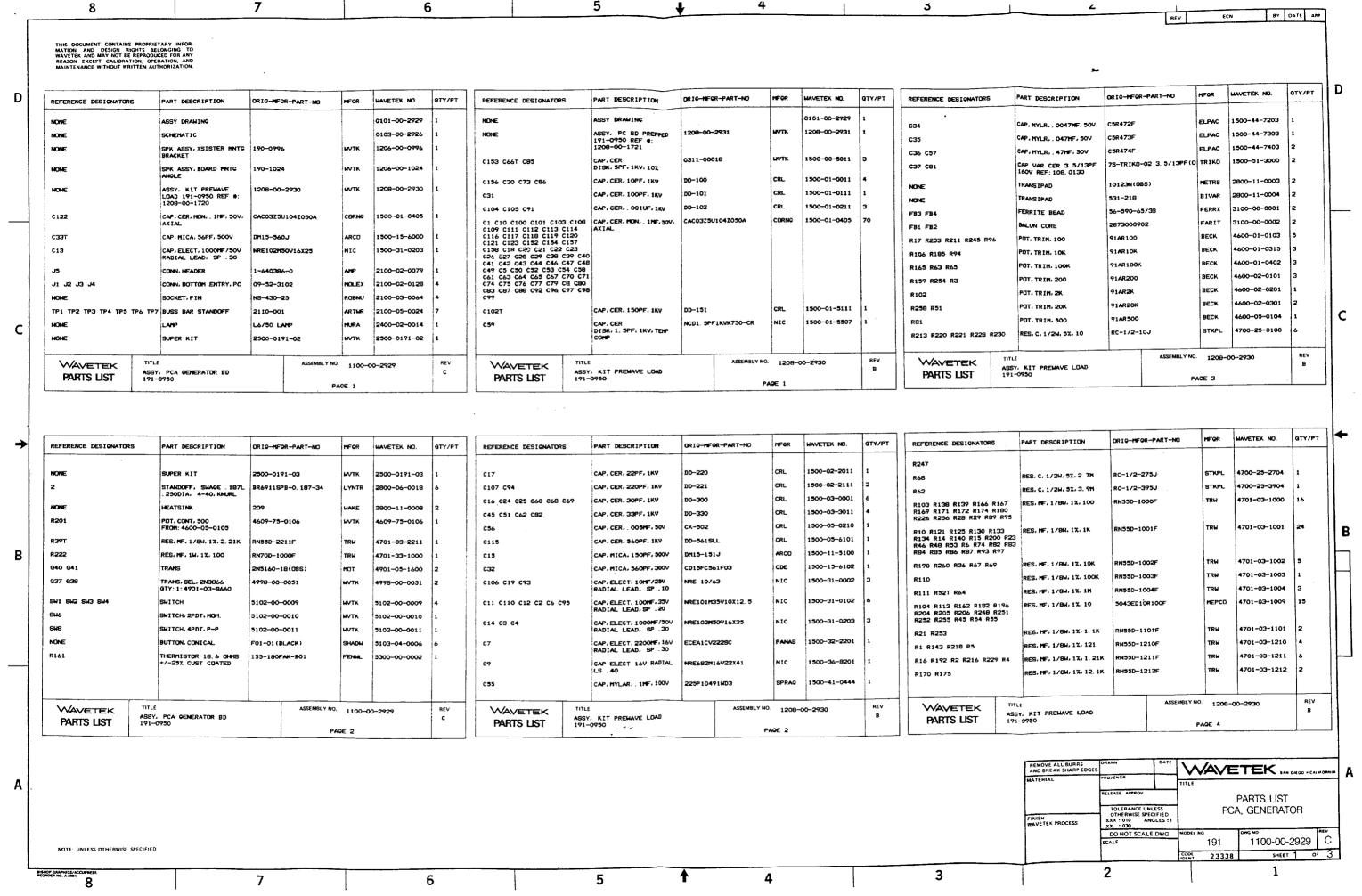

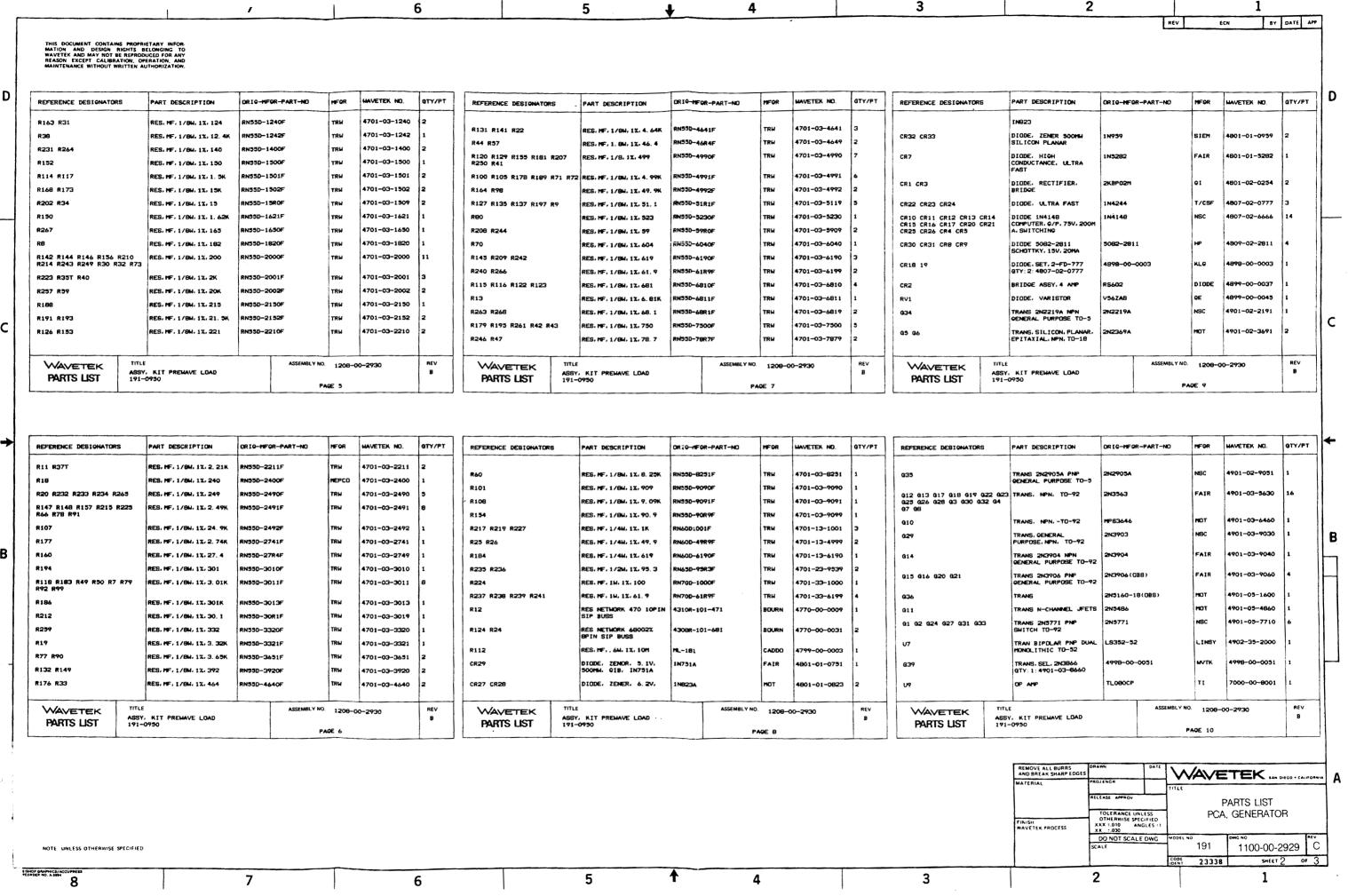

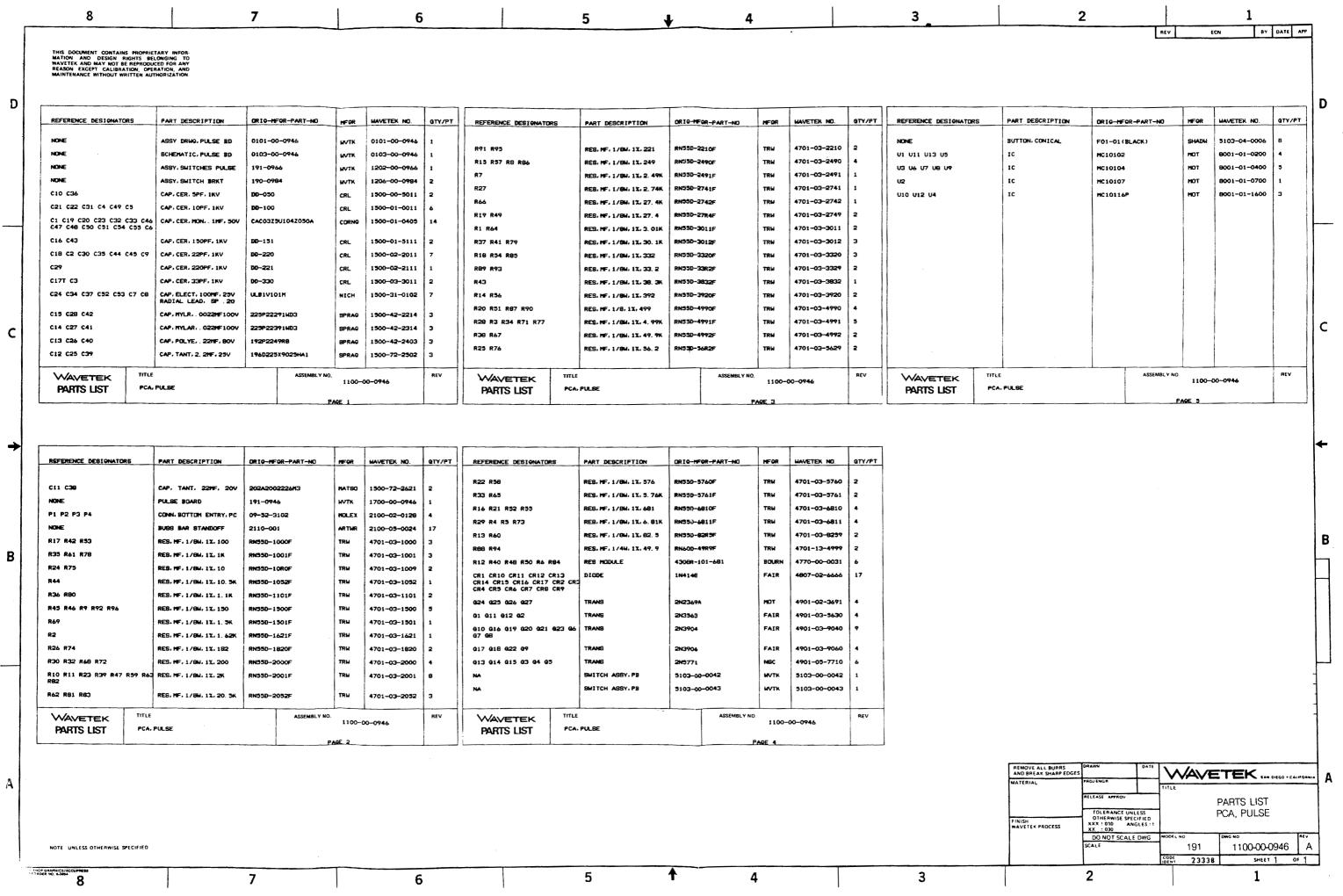

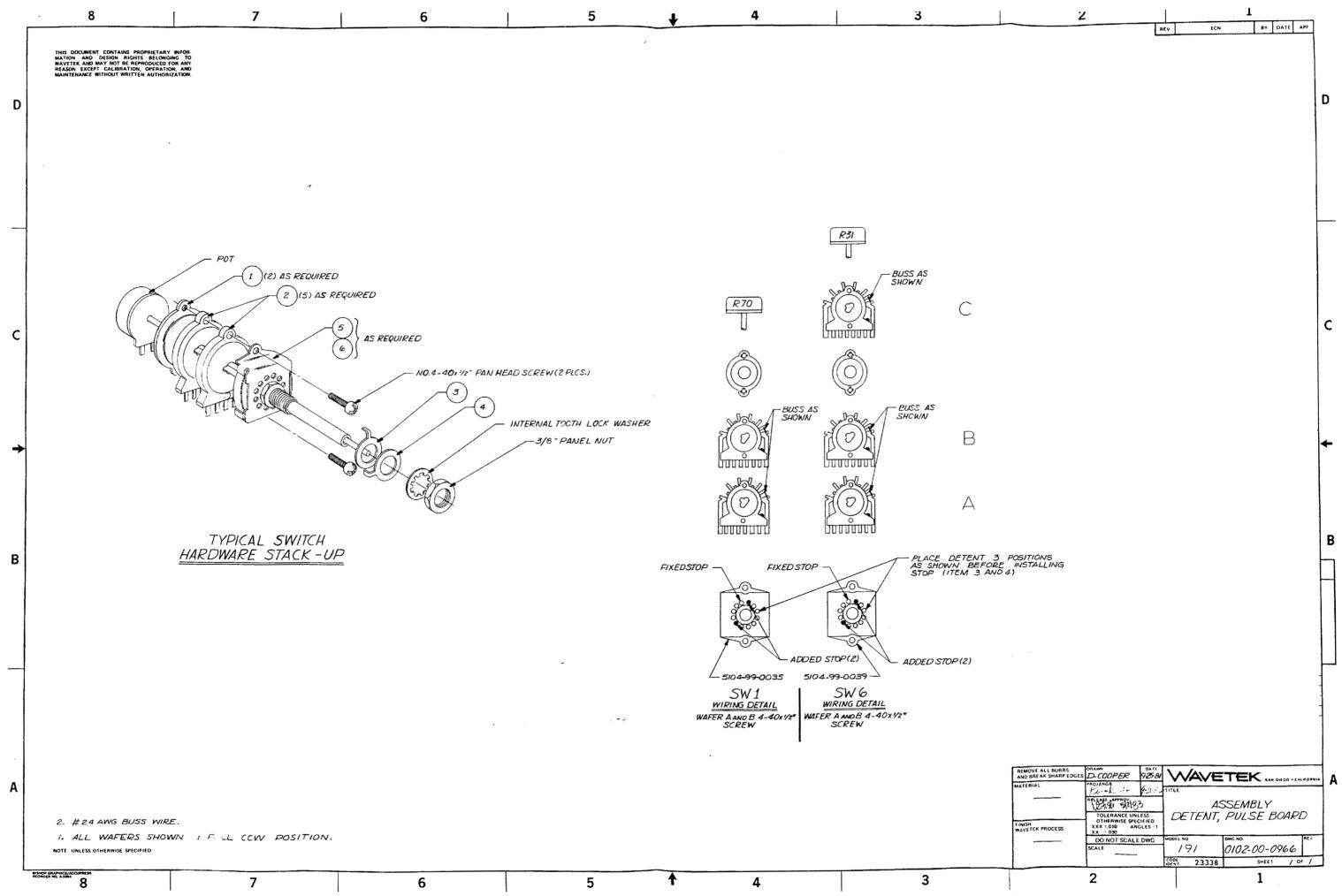

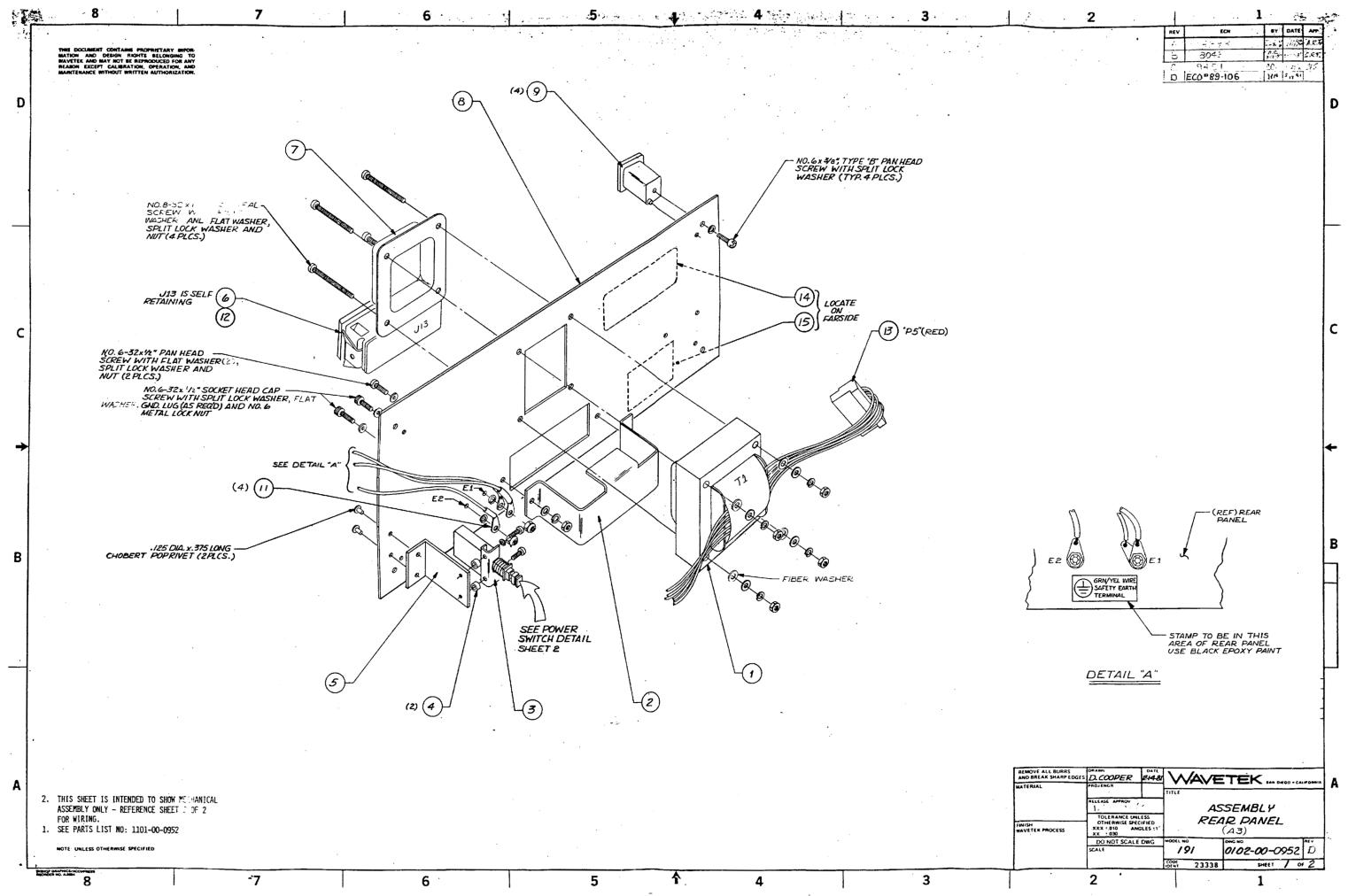

| SECTION 7 | PARTS | AND | SCHEMA | HUS  |

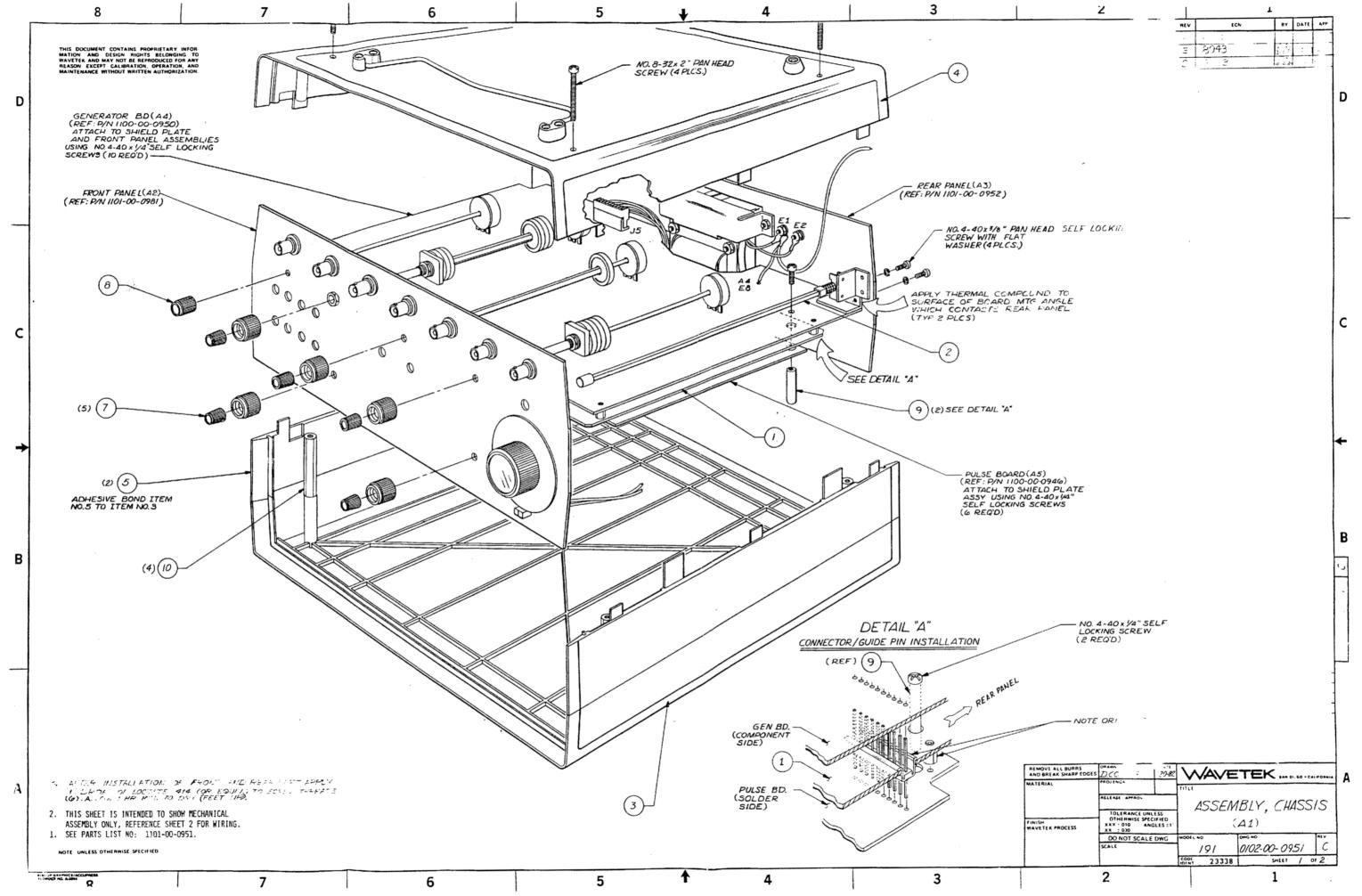

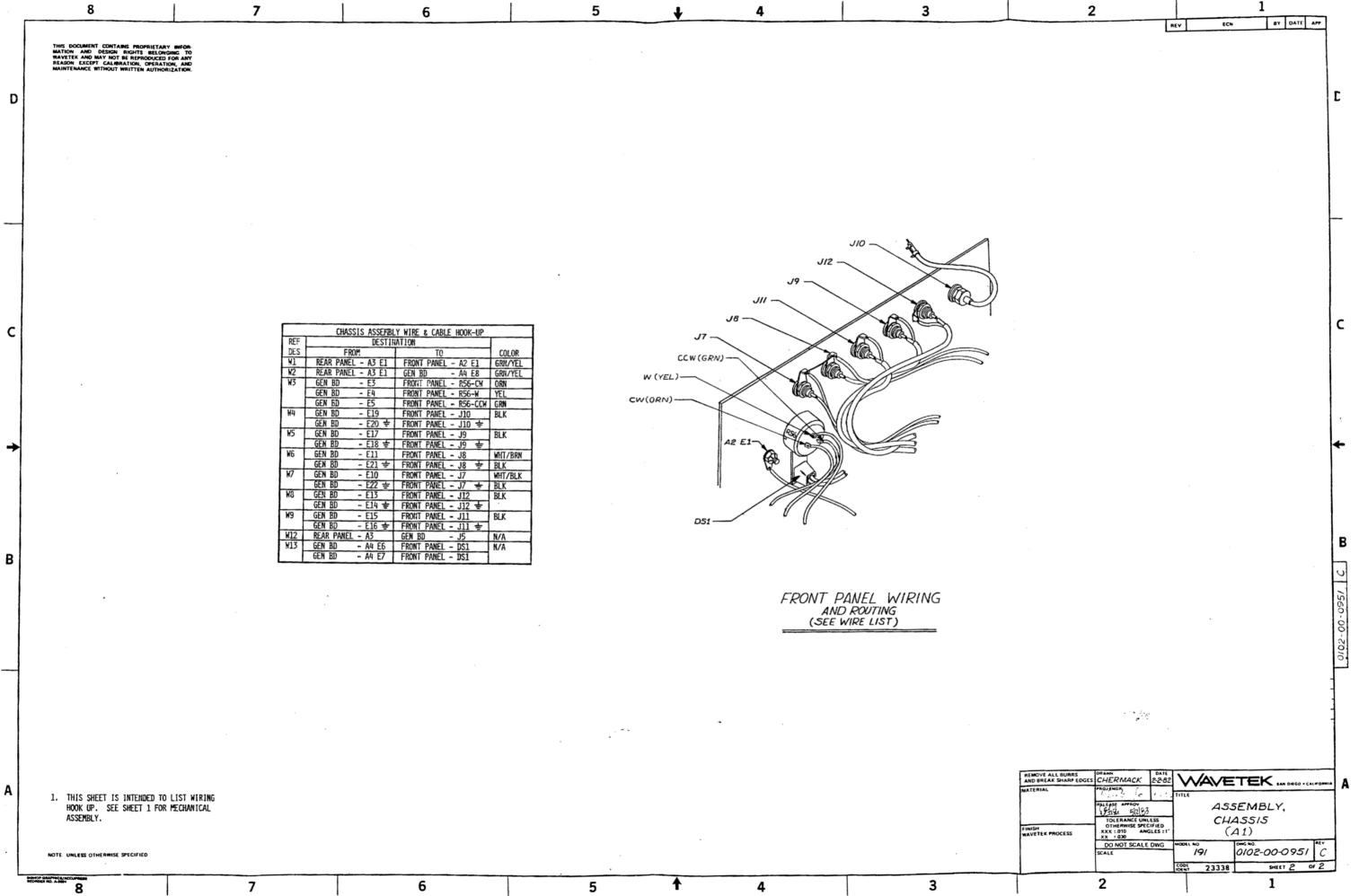

| 7.1 | DRAWINGS       | 7- |

|-----|----------------|----|

| 7.2 | ERRATA         | 7- |

| 7.3 | ORDERING PARTS | 7- |

## SAFETY FIRST-

#### Protect yourself. Follow these precautions:

- Don't touch the outputs of the instrument or any exposed test wiring carrying the output signals. This instrument can generate hazardous voltages and currents.

- Don't bypass the power cord's ground lead with two-wire extension cords or plug adaptors.

- Don't disconnect the green and yellow safety-earth-ground wire that connects the ground lug of the power receptacle to the chassis ground terminal (marked with ⊕ or / 1).

- Don't hold your eyes extremely close to an rf output for a long time. The normally nonhazardous low-power rf energy generated by the instrument could possibly cause eye injury.

- Don't plug in the power cord until directed to by the installation instructions.

- Don't repair the instrument unless you are a qualified electronics technician and know how to work with hazardous voltages.

- Pay attention to the WARNING statements. They point out situations that can cause injury or death.

- Pay attention to the CAUTION statements. They point out situations that can cause equipment damage.

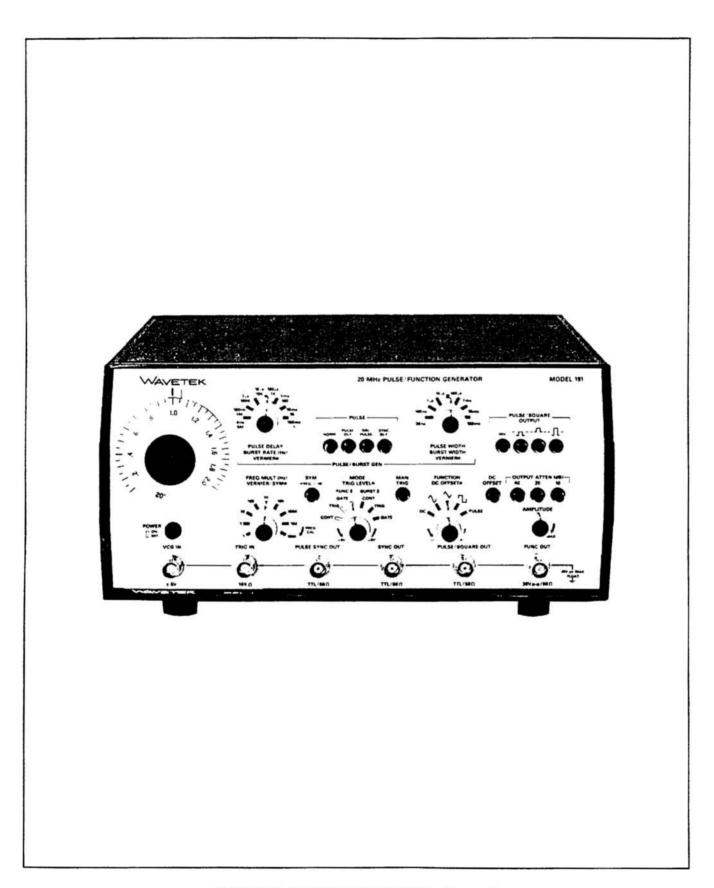

Model 191, 20 MHz Pulse/Function Generator

#### 1.1 THE MODEL 191

Wavetek Model 191, a 20 MHz Pulse/Function Generator, is a precision source of sine, triangle, square and pulse waveforms plus dc voltage. All waveforms are variable from 0.002 Hz to 20 MHz and can be externally modulated. Outputs can be continuous or can be triggered or gated by external signal or front panel switch. Variable width and delay, single or double pulses can be inverted or normal. Pulse and square wave fixed baseline selectable may be varied from fixed baseline to 15 Vp-p (7.5 Vp-p into  $50\Omega$ ). An internal burst generator gates main generator and operates in continuous, triggered and gated modes. Amplitude of the waveforms is variable from 30 Vp-p (15 Vp-p into 50Ω) down to 1.5 mVp-p. DC reference of the waveform can be offset positively or negatively. Maximum 150 mA peak current can be continuously varied over an 80 dB range. A sync output provides a TTL level into  $50\Omega$ .

#### 1.2 SPECIFICATIONS

#### 1.2.1 Main Generator

#### Waveforms

Selectable sine  ${}^{\textstyle \wedge}$  , triangle  ${}^{\textstyle \wedge}$  , square  ${}^{\textstyle \square}$  , pulses, double pulses and dc.

#### Symmetry

With SYM on, waveforms may be varied to produce sawtooth ✓ and variable duty cycle pulse

from 1:19 to 19:1.

#### NOTE

SYMMETRY and VERNIER controls affect frequency calibration. Maximum possible asymmetry is a function of frequency setting.

When SYM control is used, indicated frequency is divided by approximately 10.

#### **Operational Modes**

#### Function

Continuous: Generator oscillates continuously at selected frequency.

Triggered: Generator is quiescent until triggered by external signal or manual trigger, then generates one cycle at selected frequency.

Gated: As triggered mode, except generator oscillates for the duration of gate signal plus time to complete the last cycle.

#### Burst

Internal burst generator gates main generator and operates in continuous, triggered and gated modes.

Burst Rate: 1 Hz to 5 MHz in 7 ranges. Burst Width: 20 ns to 100 ms in 7 ranges.

#### Frequency Range

0.002 Hz to 20 MHz in 9 overlapping decade ranges with approximately 1% of full scale vernier.

#### **Function Output**

$^{\circ}$ ,  $^{\circ}$ ,  $^{\circ}$  and pulse selectable and variable to 30 Vp-p (15 Vp-p into 50 $\Omega$ ). Pulse and  $^{\circ}$ L fixed baseline selectable (  $^{\circ}$ H,  $^{\circ}$ H,  $^{\circ}$ H) and can be inverted.  $^{\circ}$ H, can be varied from fixed baseline to 15 Vp-p (7.5 Vp-p into 50 $\Omega$ ). All waveforms and dc may be attenuated in 10 db steps to 70 dB with 10 dB vernier for overall attenuation of 80 dB. 50 $\Omega$  source impedance.

#### DC Output and DC Offset

Selectable thru function output BNC. Controlled by front panel control with separate on-off switch. Adjustable between  $\pm\,15$  Vdc ( $\pm\,7.5$  Vdc into  $50\Omega$ ) with signal peak plus offset limit to  $\pm\,15$  Vdc ( $\pm\,7.5$  Vdc into  $50\Omega$ ). DC offset and output waveform attenuated proportionately by 0 to 70 dB output attenuator.

#### Sync Output

A TTL level square wave synchronized to the main generator. Duty cycle varies with symmetry control.  $50\Omega$  source impedance.

#### Pulse/Square Output

A TTL level pulse or square wave whose transitions are simultaneous with function output (square and pulse only),  $50\Omega$  source impedance.

#### VCG-Voltage Controlled Generator

Up to 1000:1 frequency change with external 0 to ±5V signal. Upper frequency limited to maximum of selected range.

Slew Rate: 2% of range per µs.

Linearity: ±0.5% thru ×100K range. ±5% on

$\times$ 1M and  $\times$ 10M range.

Impedance: 10 kΩ.

#### Trigger (and Gate) Input

Input Range: 1 Vp-p to ± 10V.

Trigger Level Adj: -5V to +5V.

Impedance: 1.5 kQ shunted by 1.5 pF.

Pulse Width: 25 ns minimum.

Repetition Rate: Input Max Rep Rate

±1V 1 MHz ±2.5V 10 MHz

#### 1.2.2 Pulse Generator

#### **Pulse Modes**

Normal Pulse: Adjustable width pulse in phase with pulse sync output. Repetition rate is set by frequency of main generator.

Pulse Delay: Pulse delayed with respect to pulse sync output. Pulse delay and pulse width adjustable.

Double Pulse: Two pulses for every period. Time between pulses and pulse width adjustable.

Sync Delay: Pulse sync output delayed with respect to pulse output. Delay is adjustable.

#### NOTE

The preceding Pulse Modes operate as defined when the Function Mode is Continuous, Triggered or Gated. However, Pulse Modes are not applicable in Burst Mode.

#### **Pulse Period Range**

50 ns to 500 sec in 9 decade ranges.

#### **Pulse Width**

20 ns to 100 ms in 7 ranges.

#### Pulse or Sync Delay

0 ns to 100 ms in 7 ranges.

#### **Duty Cycle**

Up to: 75% for pulse widths > 100 ns; 50% for pulse widths of 20 to 100 ns.

#### Pulse/Burst Sync Output

A TTL level pulse when terminated with  $50\Omega$ . Reference for pulses and bursts at function output BNC and TTL pulse BNC.

In pulse function mode (normal pulse) and burst mode, sync output is coincident with leading edge of pulse/burst output and has width of 20 to 60% of maximum selected pulse/burst width, except on the 20 to 100 ns range which will have a sync pulse width between 10 and 30 ns.

#### NOTE

Also see Pulse Modes.

#### 1.2.3 Frequency Precision

#### **Dial Accuracy**

$\pm$  3% of full scale from  $\times$  0.1 Hz to  $\times$  1 MHz.  $\pm$  5% of full scale on  $\times$  10M range.

# 1.2.4 Amplitude Precision

#### **Amplitude Change with Frequency**

Sine variation with frequency:

< ±0.2 dB on all ranges thru

× 100K.

$< \pm 0.5$  dB on  $\times 1M$  range.  $< \pm 1.0$  dB on  $\times 10M$  range.

#### Step Attenuator Accuracy

±0.3 dB with 10, 20 and 40 dB.

± 0.6 dB with 30, 50 and 60 dB.

±0.9 dB with 70 dB setting.

#### 1.2.5 Waveform Characteristics

#### Sine Distortion

<0.5% on  $\times 100$ ,  $\times 1K$  and  $\times 10K$ . <1.0% on  $\times 0.1$  to  $\times 100$  ranges.

All harmonics 30 dB below fundamental on  $\times 100$ K,  $\times 1$ M range, and 25 dB below on  $\times 10$ M range.

#### Square Wave and Pulse

Rise/Fall Time at Function Output BNC: <15 ns (10% to 90%).

Total Aberrations:

±5% of full amplitude.

#### **Time Symmetry**

Square wave variation from 0.1 to 2 on dial:  $< \pm 1\%$  to 200 kHz.  $< \pm 10\%$  to 20 MHz.

#### **Triangle Linearity**

>99% for 0.002 Hz to 200 kHz.

#### 1.2.6 General

#### Stability

Main generator amplitude, frequency and dc offset.

After 2 hour warm-up:

± 0.05% for 10 minutes.

± 0.25% for 24 hours.

#### Environmental

Specifications apply at  $25^{\circ}\text{C} \pm 5^{\circ}$ . Instrument operates  $0^{\circ}\text{C}$  to  $+50^{\circ}$ .

#### **Dimensions**

28.6 cm (11 ¼ in.) wide; 13.3 cm (5 ¼ in.) high; 28.6 cm (11 ¼ in.) deep.

#### Weight

4.6 kg (10 lb) net; 6.4 kg (14 lb) shipping.

#### Powe

100/120/220/240V (+5%, -10%), 48 Hz to 66 Hz,  $\leq$  95 VA.

#### NOTE

All specifications apply from 0.1 to 2.0 on frequency dial, when FUNC OUT amplitude is maximum and  $50\Omega$  terminated, and with SYM control OFF.

#### 2.1 MECHANICAL INSTALLATION

After unpacking the instrument, visually inspect all external parts for possible damage to connectors, surface areas, etc. If damage is discovered, file a claim with the carrier who transported the unit. The shipping container and packing material should be saved in case reshipment is required.

#### 2.2 ELECTRICAL INSTALLATION

#### 2.2.1 Power Connection

#### WARNING

To preclude injury or death due to shock, the third wire earth ground must be continuous to the facility power outlet. Before connecting to the facility power outlet, examine extension cords, autotransformers, etc., between the instrument and the facility power outlet for a continuous earth ground path. The earth ground path can be identified at the plug on the instrument power cord; of the three terminals, the earth ground terminal is the nonmatching shape, usually cylindrical.

#### CAUTION

To prevent damage to the instrument, check for proper match of line and instrument voltage and proper fuse type and rating.

#### NOTE

Unless otherwise specified at the time of purchase, this instrument was shipped from the factory with the power transformer connected for operation on a 120 Vac line supply and with a 3/8 amp fuse.

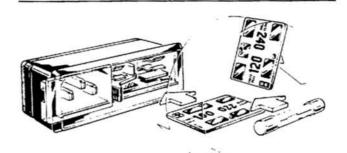

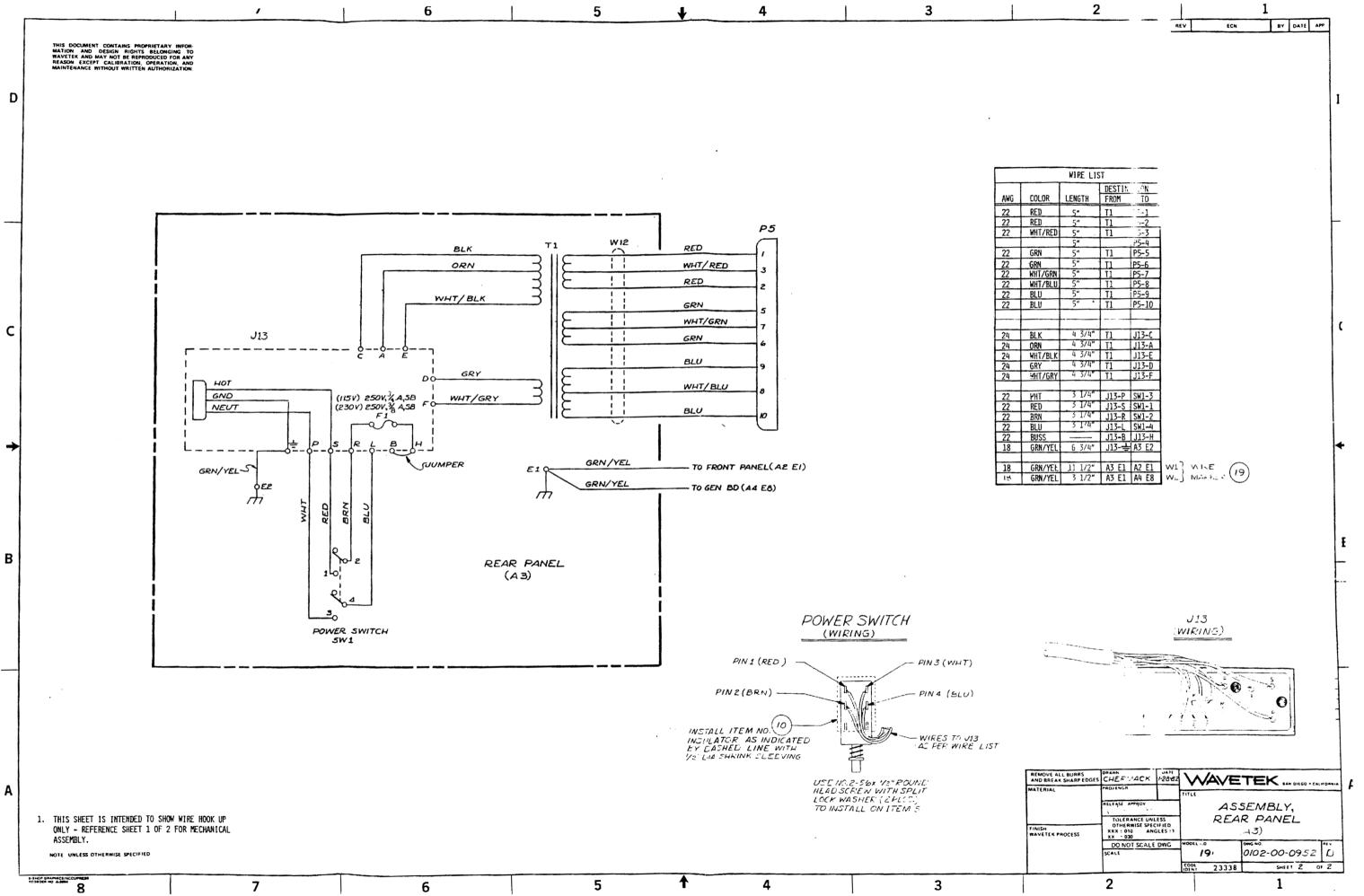

Conversion to other input voltages requires a change in rear panel fuse holder voltage card position and fuse (figure 2-1) according to the following procedure.

Figure 2-1. Voltage Selector and Fuse

- Disconnect the power cord at the instrument, open fuse holder cover door and rotate fuse-pull to left to remove the fuse.

- Remove the small printed circuit board and select operating voltage by orienting the printed circuit board to position the desired voltage to the top left side. Push the board firmly into its module slot.

- Rotate the fuse-pull back into the normal position and insert the correct fuse into the fuse holder. Close the cover door.

- Connect the ac line cord to the mating connector at the rear of the unit and the power source.

| Card Position | d Position Input Vac |         |

|---------------|----------------------|---------|

| 100           | 90 to 105            | 3/4 amp |

| 120           | 108 to 126           | 3/4 amp |

| 220           | 198 to 231           | 3/8 amp |

| 240           | 216 to 252           | 3/8 amp |

#### 2.2.2 Signal Connections

Use RG58U  $50\Omega$  coaxial cables equipped with BNC connectors to distribute signals when connecting this instrument to associated equipment.

#### 2.3 ELECTRICAL ACCEPTANCE CHECKOUT

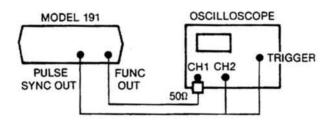

This checkout procedure verifies the generator operation. If a malfunction is found, refer to the Warranty in the front of this manual. A dual trace, 150 MHz bandwidth oscilloscope with X 10 time base magnification, a  $50\Omega$  load, a coaxial tee and three  $50\Omega$  cables are required to perform this checkout.

Set up as in figure 2-2 and preset the generator front panel controls as follows. Perform the steps in table 2-1.

| Position          |

|-------------------|

| 1.0               |

| 1K                |

| . FREQ CAL (cw)   |

| Off(extended)     |

| CONT (FUNC)       |

| 10 o'clock        |

| ∿                 |

| . OFF(Extended)   |

| ccw               |

| All Extended      |

| MAX (cw)          |

| . 10 µs to 100 µs |

| ccw               |

| NORM (Pressed)    |

| . 10 µs to 100 µs |

| cw                |

|                   |

| OSCI                             | LLOSCOPE                                    |

|----------------------------------|---------------------------------------------|

| VERT, CH1: 5V/DIV<br>CH2: 2V/DIV | HORIZ SWP: 0.5 ms/DIV<br>TRIG MODE: DC, EXT |

| MODEL 191                        | OSCILLOSCOPE                                |

|                                  | OUT CH1 CH2 TRIG                            |

|                                  | 50Ω<br>MINATION                             |

Table 2-1. Checkout Procedure

| Step | Control                   | Position/Operation                                                                                                                   | Observation                                                                                                                                                                                                                                                                                                                       |

|------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Oscilloscope              | Trig level and slope, both positive.                                                                                                 | CH2: Square wave that begins on positive going edge. CH1: 15 Vp-p sine wave.                                                                                                                                                                                                                                                      |

| 2    | Dial and<br>VERNIER/SYM   | Rotate dial full cw, vernier full ccw.<br>Then the opposite. Return dial to 1.0,<br>vernier to CAL.                                  | CH2: Square wave remains in sync for all dial positions. Range is greater than from 2 Hz to 2000 Hz (1000:1).                                                                                                                                                                                                                     |

| 3    | FREQ MULT                 | Rotate to all positions.<br>Return to 1K position.                                                                                   | Frequency is 1 × each range position.                                                                                                                                                                                                                                                                                             |

| 4    | AMPLITUDE                 | Set to 6 Vp-p on scope.                                                                                                              | CH1: Amplitude decreases to approximately 6 Vp-p.                                                                                                                                                                                                                                                                                 |

| 5    | DC OFFSET                 | Depress DC OFFSET switch, then rotate DC OFFSET Control CW. Release DC OFFSET to extended (off) position at completion of this step. | Full CCW gives negative offset. Clipping occurs when the offset plus waveform peak amplitude exceeds approximately $\pm 7.5 \text{V}$ into $50 \Omega$ . Initially the negative peak is clipped, but as the DC offset is rotated cw the clipping of the negative peak disappears and eventually the positive peak begins to clip. |

| 6    | AMPLITUDE                 | Rotate cw.                                                                                                                           | Waveform returns to 15 Vp-p.                                                                                                                                                                                                                                                                                                      |

| 7    | OUTPUT<br>ATTN 10, 20, 40 | Depress buttons in various combinations. Then release all buttons.                                                                   | Output level varies from 15 Vp-p (0 dB) to 4.7 mV (70 dB).                                                                                                                                                                                                                                                                        |

| 8    | FUNCTION                  | Rotate ccw.<br>Select DC ◇ , ◇ , □ .<br>Reset to ◇ .                                                                                 | Observe 0 Vdc level; $\land$ , $\land$ and $\lnot$ are 15 Vp-p. Note phase relationships; $\lnot$ in phase with $\land$ and $\land$ .                                                                                                                                                                                             |

Table 2-1. Checkout Procedure (Cont)

| Step | Control              | Position/Operation                                                                                     | Observation                                                                                                                                                                 |

|------|----------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9    | SYM,<br>VERNIER/SYM. | Depress SYM switch and rotate<br>VERNIER/SYM control ccw.<br>Extend SYM, return VERNIER/SYM<br>to CAL. | Frequency decreases to approximately 100 Hz. CCW of the 12 o'clock position gives 1:19; CW gives 19:1 (a skewed sinewave and variable duty cycle pulses can be observed for |

| 10   | MODE and<br>FUNCTION | Select GATE. Select ◇, ◇, □. Return to ◇.                                                              | A dc level near zero volts (except 'L' function; quiescent level is at negative peak value).                                                                                |

| 11   | MANUAL<br>TRIGGER    | Press, hold and release.<br>Return to FUNC CONT.                                                       | A burst of ∿ for the period the MAN TRIG is depressed.                                                                                                                      |

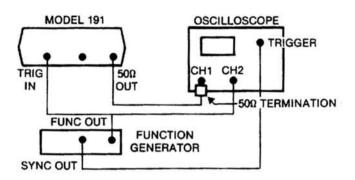

Set MODE to CONT (FUNC). (All other controls will be as for initial setup.) Setup oscilloscope and Model 191 as shown in figure 2-3. Display both channels.

Figure 2-3. Pulse Checkout Setup

| 12 | FUNCTION               | PULSE                                         | Pulse                                                                                 |

|----|------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------|

| 13 | AMPLITUDE              | Vary, then return cw.                         | Upper and lower levels vary from 0.5V to 15 Vp-p.                                     |

| 14 | PULSE/SQUARE<br>OUTPUT | Depress INV, then release INV.                | 180° phase inversion of pulse relative to PULSE SYNC OUT.                             |

| 15 |                        | Depress n.                                    | Positive offset pulse + 7.5V.                                                         |

| 16 | AMPLITUDE              | Vary, then return to full cw.                 | Upper level varies, lower level remains fixed. Full variation from 0.5V to +7.5 Vp-p. |

| 17 | PULSE/SQUARE<br>OUTPUT | Depress T.                                    | Negative offset pulse - 7.5 Vp-p.                                                     |

| 18 | AMPLITUDE              | Vary, then return to full cw.<br>Return to A. | Low level varies, upper level remains fixed. Full variation from 0.5V to -7.5 Vp-p.   |

The next 2 steps demonstrate maximum and minimum pulse width range.

Table 2-1. Checkout Procedure (Cont)

| Step | Control                                                                                    | Position/Operation                                                                 | Observation                                                                                                       |

|------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 19   | Dial<br>FREQ MULT<br>PULSE WIDTH<br>Scope<br>PULSE WIDTH<br>VERNIER                        | 20 ms/div.                                                                         | Minimum PULSE WIDTH at ccw; maximum PULSE WIDTH at cw.                                                            |

| 20   | Scope                                                                                      | .2<br>10M<br>20 ns - 100 ns.<br>0.05 µs/div.<br>Rotate ccw, cw.                    | Minimum PULSE WIDTH at ccw; maximum PULSE WIDTH at cw.                                                            |

|      | The next s                                                                                 | steps demonstrate maximum and                                                      | minimum pulse delay range.                                                                                        |

| 21   | PULSE<br>PULSE DELAY<br>Scope<br>PULSE DELAY<br>VERNIER                                    | Depress PULSE DLY. 0 ns - 100 ns. 0.05 µs/div. Rotate ccw, cw.                     | Minimum PULSE DELAY from PULSE SYNC at ccw; maximum PULSE DELAY from PULSE SYNC at cw.                            |

| 22   | Dial<br>FREQ MULT<br>PULSE WIDTH<br>PULSE DELAY<br>Scope<br>PULSE DELAY<br>VERNIER         | 2.0<br>1<br>10 ms - 100 ms.<br>10 ms - 100 ms.<br>20 ms/div.<br>Rotate ccw, cw.    | Minimum PULSE DELAY from PULSE SYNC at ccw; maximum PULSE DELAY from PULSE SYNC at cw.                            |

|      |                                                                                            | The next step demonstrate                                                          | es double pulse.                                                                                                  |

| 23   | Dial FREQ MULT PULSE PULSE WIDTH PULSE DELAY Scope PULSE WIDTH VERNIER PULSE DELAY VERNIER | 0.5<br>10K<br>DBL pulse<br>10 μs - 100 μs<br>10 μs - 100 μs<br>0.05 ms/div.<br>ccw | Double Pulse — maximum delay of second pulse from first pulse at cw. Second pulse merges with first pulse at ccw. |

The next step demonstrates sync delay.

Table 2-1. Checkout Procedure (Continued)

| Step | Control                | Position/Operation                                                      | Observation                                                                |

|------|------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 24   | PULSE<br>Scope         | Depress SYNC DLY Trigger: INT CHANNEL 1 (FUNC OUT). Then return to EXT. |                                                                            |

|      | PULSE DELAY<br>VERNIER | Rotate ccw, cw.                                                         | Minimum SYNC DELAY from PULSE at ccw. Maximum SYNC DELAY from PULSE at cw. |

|      | <u> </u>               | The next step demonstrate                                               | s burst control.                                                           |

| 25   | MODE                   | BURST CONT                                                              |                                                                            |

|      | FUNCTION               | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                  |                                                                            |

|      | Dial<br>FREQ MULT      | 2.0<br>10K                                                              |                                                                            |

|      | BURST RATE             | 100 - 1K                                                                |                                                                            |

|      | BURST RATE<br>VERNIER  | 12 o'clock.                                                             |                                                                            |

|      | BURST WIDTH            | 100 μs - 1 ms.                                                          |                                                                            |

|      | Scope                  | 0.5 ms/div.                                                             |                                                                            |

|      | BURST WIDTH            | Rotate cw, ccw.                                                         | Number of cycles in burst increases (cw) and                               |

Set up trigger source as shown in figure 2-4. Set trigger source for 200 Hz triangle 10 Vp-p signal. Set scope for one cycle of triggering waveform; display both channels. Setup Model 191 controls for initial setup except set MODE to FUNC GATE.

decreases (ccw).

VERNIER

| 26 | TRIG LEVEL                                                                             | Rotate throughout its range.<br>Return to 10 o'clock.                      | The number of waveform cycles in each gated "burst" varies with the trigger level.  Notice relationships between Channels 1 and 2 waveforms as the TRIGGER LEVEL is rotated. |  |

|----|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 27 | MODE                                                                                   | Select FUNC TRIG                                                           | A single triggered ◇ recurring at the 200 Hz trigger rate.                                                                                                                   |  |

| 28 | Dial FREQ MULT MODE BURST RATE BURST RATE VERNIER BURST WIDTH BURST WIDTH VERNIER MODE | 2.0 1M BURST GATED 1K - 10K 12 o'clock 100 µs - 1 ms 12 o'clock BURST TRIG | CW reduces number of bursts per gate. CCW increases number of bursts per gate.  A single triggered burst at 200 Hz trigger rate.                                             |  |

Figure 2-4. Trigger Checkout Setup

# SECTION 3

#### 3.1 CONTROLS AND CONNECTORS

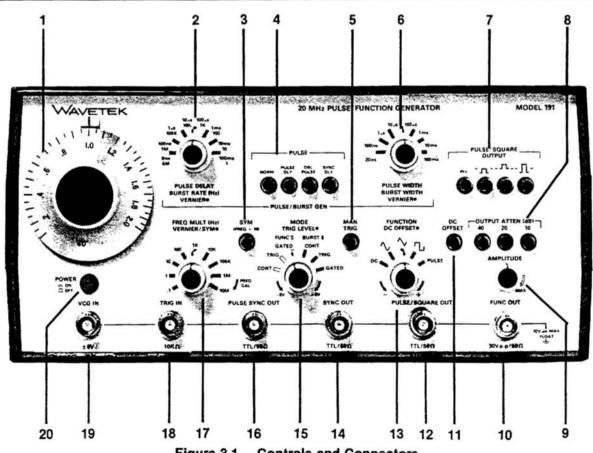

The generator front panel controls and connectors are shown in figure 3-1 and keyed to the following descriptions.

- Frequency Dial Settings under the dial index mark summed with VCG IN 19 and multiplied by FREQ MULT 17 determine the output signal frequency.

- 2 PULSE DELAY/BURST RATE Selector Outer coax knob selects one of seven ranges. An inner coax knob, VERNIER, controls the delay or rate within each range.

In pulse function, these controls set the delay of the pulse at FUNC OUT 10 and PULSE/SQUARE OUT 12 (PULSE DLY 4 depressed), or the delay of the pulse at PULSE SYNC OUT 16 relative to FUNCTION OUT 10 and PULSE/SQUARE OUT 12 (SYNC DLY 4 depressed). Pulse delay and sync delay are variable between 0ns to 100 ms.

In burst modes, the BURST RATE and VERNIER controls set the burst repetition rate. Repetition varies between 1 Hz and 5 MHz.

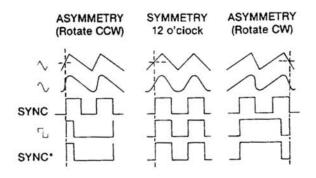

3 SYM Pushbutton — When depressed, allows the waveform symmetry to be varied from 19:1 to 1:19 by the VERNIER/SYM control 17; (as a result the generator frequency is divided by 10).

Figure 3-1. Controls and Connectors

When extended, the switch allows the generator to produce normal (50% duty cycle) waveforms.

4 PULSE Pushbuttons — Four mutually exclusive switches that select either normal pulse, pulse delay, double pulse or sync delay when FUNCTION switch 13 is set to PULSE.

NORM — Selects a pulse at FUNC OUT 10 and PULSE/SQUARE OUT 12 in phase with PULSE SYNC OUT 16. PULSE WIDTH 6 controls the width or the normal pulse, and the frequency dial 1 and FREQ MULT 17 set the pulse repetition rate.

PULSE DLY — Selects a pulse that is delayed relative to PULSE SYNC OUT 16. PULSE DELAY 2 controls the delay of the pulse, the frequency dial 1 and FREQ MULT 17 control pulse repetition rate, and PULSE WIDTH 6 sets the width of each pulse.

DBL PULSE — Selects two pulses for each pulse period. In double pulse, PULSE DELAY 2 sets the start of the second pulse relative to the first. The frequency dial 1 and FREQ MULT 17 control the repetition rate for each pulse pair. PULSE WIDTH 6 controls pulse width of both pulses.

SYNC DLY — Selects a variable delay sync pulse at the PULSE SYNC OUT 16 relative to FUNC OUT 10 and PULSE/SQUARE OUT 12. PULSE DELAY 2 controls the delay of the pulse sync. Frequency dial 1 and FREQ MULT 17 set repetition rate of the pulse.

- MAN TRIG Pushbutton Triggers or gates the output signals when generator mode is TRIG or GATED 15. In function trigger mode, one waveform cycle is output when the button is pushed; in burst trigger mode, one burst. In function gated mode, waveform cycles are continuously output as long as the button is held in; in burst gated mode, burst are continuously output.

- PULSE WIDTH/BURST WIDTH Outer coax knob selects one of seven decade ranges. An inner coax knob, VERNIER, controls the width within each range. In pulse function PULSE WIDTH sets the width of the pulse at FUNC OUT 10 and PULSE/SQUARE OUT 12.

In burst modes, BURST WIDTH sets the burst duration at FUNC OUT 10 and, in  $\Box$  function only, at PULSE/SQUARE OUT 12.

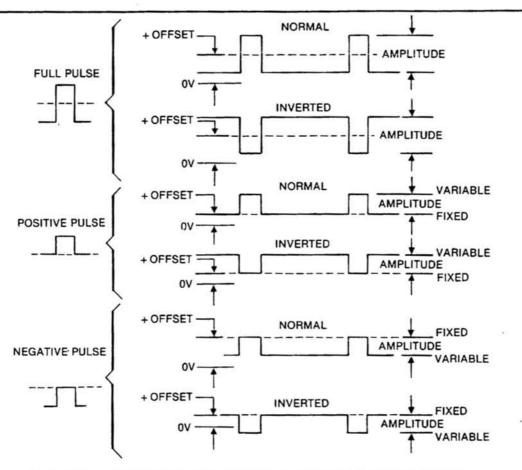

7 PULSE/SQUARE OUTPUT — Selects the pulse amplitude symmetry relative to the baseline (ref: figure 3-2). With DC OFFSET 11 off, the baseline is 0 volts. With DC OFFSET on, the baseline is varied by the DC OFFSET control 13.

∏ selects a pulse that maintains amplitude

symmetry about its centerline. AMPLITUDE 9

adjust the peak-to-peak level of the pulse.

selects the positive pulse. AMPLITUDE **9** adjust the positive peak while the negative peak remains a fixed baseline.

selects the negative pulse. AMPLITUDE control **9** adjusts the negative peak while the positive peak remains a fixed baseline.

INV pushbutton — selects normal or inverted pulse output. An inverted pulse is a reversal of the active and inactive levels of the pulse. The net result for a square pulse inversion would be a 180° phase shift with respect to the PULSE SYNC OUT 16.

- 8 OUTPUT ATTEN Pushbuttons Select the attenuation range of the FUNC OUT 10 signal. The AMPLITUDE control 9 allows continuous waveform level variations within each attenuator range. Each of the three buttons may be used individually for 40, 20 or 10 dB steps of attenuation, or pressed in combinations for up to 70 dB of attenuation. The attenuator attenuates both the waveform and dc offset.

- 9 AMPLITUDE Control Continuously varies the waveform amplitude within each OUTPUT ATTEN 8 range. CCW rotation reduces waveform amplitudes at FUNC OUT 10 by greater than 10 dB. DC and dc offset voltages are not affected by this control.

- FUNC OUT Connector This BNC is the waveform (or dc) output of the generator. Maximum output is 30 Vp-p (15 Vp-p into 50Ω). Source impedance is 50Ω.

- 11 DC OFFSET Pushbutton Depressed button activates the dc offset (ref: 13). Extended button ensures zero dc offset.

Figure 3-2. PULSE/SQUARE OUTPUT Amplitude/Offset Relationship

- 12 PULSE/SQUARE OUT Connector BNC output is a TTL level into 50Ω. Output is simultaneous and exclusive with FUNC OUT 10 square wave or pulse output. Source impedance is 50Ω.

- 13 FUNCTION Selector Outer coaxial knob selects one of four waveforms (sine, triangle, square, pulse) or dc.

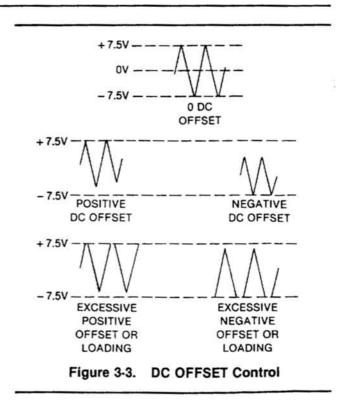

DC OFFSET Control — Inner coaxial knob offsets the FUNC OUT 10 output waveform vertically from its normal position and when FUNCTION (outer coaxial knob 13) is in the DC position, controls polarity and voltage of dc output. DC output range is  $0 \pm 10 \, \text{Vdc} \, (\pm 5 \, \text{Vdc}$  into  $50\Omega$ ). DC OFFSET switch 11 must be depressed to enable this DC OFFSET Control. Extending the DC OFFSET switch ensures zero volt offset. DC offset and waveform are attenuated by the OUTPUT ATTEN control 8 but dc offset is not attenuated by the AMPLITUDE control 9. Waveform peak voltage plus dc offset is limited to  $\pm 15 \, \text{Vdc} \, (\pm 7.5 \, \text{Vdc}$  into  $50\Omega$ ). See figure 3-3.

- 14 SYNC OUT Connector The sync signal from this BNC is a TTL level into 50Ω synchronous with FUNC OUT 10 signal. Duty cycle varies with waveform symmetry. Source impedance is 50Ω.

- MODE Control This outer coax knob selects one of the six operating modes. Three of the modes are burst generator modes (switch detents are solid black) and three are function generator modes (switch detents are white). Figure 3-8 illustrates the output in each of these modes.

#### **FUNC Modes**

CONT — Continuous output at FUNC OUT 10 and SYNC OUT 14 connectors.

TRIG — A dc level output at FUNC OUT 10 until the generator is triggered by the MAN TRIG 5 or with a signal at the TRIG IN connector 18. When triggered the generator output is one cycle of waveform followed by a dc level.

GATED — As for TRIG except the output is continuous for the duration of the manual or external trigger signal. The last waveform cycle started is always completed.

#### **BURST Modes**

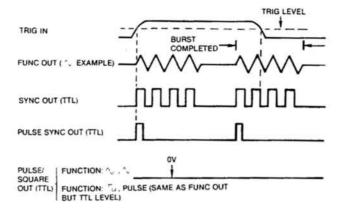

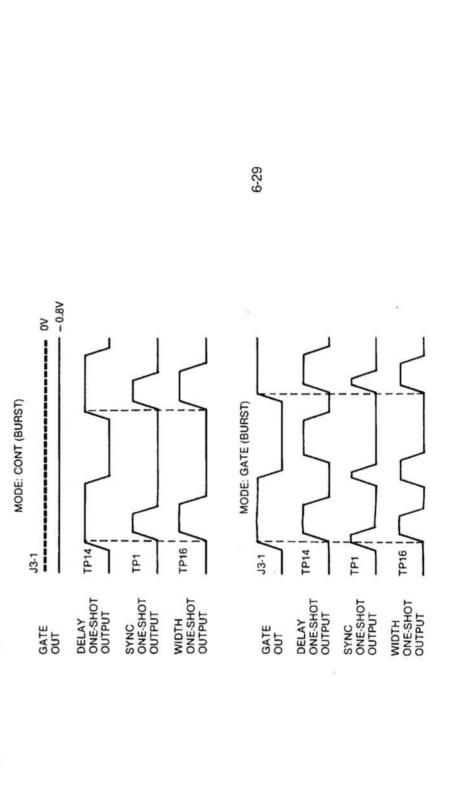

CONT — Continuous burst is a series of bursts from FUNC OUT 10 at a continuous repetition rate. BURST RATE 2 sets the repetition rate of each burst. Frequency dial 1 and FREQ MULT 17 determine the frequency of waveform cycles in each burst. BURST WIDTH 6 sets the number of cycles within each burst.

TRIG — A trigger (manual 5 or external 18) initiates a burst of cycles from FUNC OUT 10. The trigger rate determines the burst repetition rate. Frequency dial 1 and FREQ MULT 17 determine the frequency of waveform cycles in each burst. BURST WIDTH 6 sets the number of cycles within each burst.

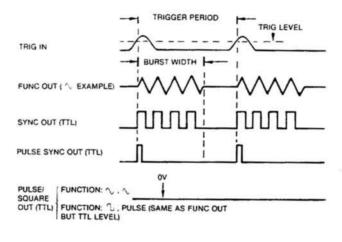

GATED — When triggered (external 18 or manual 5), FUNC OUT 10 produces a series of bursts for the active period of the trigger signal. Frequency dial 1 and FREQ MULT 17 sets the frequency of the cycles in the burst. BURST RATE 2 controls the repetition rate between bursts and BURST WIDTH 6 sets the number of cycles within each burst.

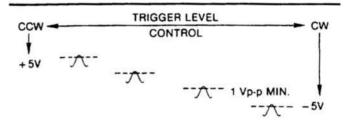

TRIG LEVEL Control — This inner coax knob is a continuously variable adjustment of the trigger circuitry firing point. When full ccw, a positive going signal at approximately +5V is required for triggering (see figure 3-4). In the full cw position, a positive going signal at approximately –5V or more positive voltage is required for triggering. In the GATED modes, the generator will run continuously when the control is cw of 12 o'clock.

Trigger signal must be a positive going signal exceeding the TRIGGER LEVEL setting.

Figure 3-4. Minimum Trigger Signal

PULSE SYNC OUT Connector — With normal pulse function or burst mode selected, this BNC output supplies a TTL level pulse that is coincident with the leading edge of the pulse or burst at FUNC OUT 10.Sync pulse with is 20 to 60% of minimum selected pulse/burst width except on the 20 ns to 100 ns range, which will have a sync pulse width between 10 and 30 ns. Source impedance is 50Ω.

In sync delay (ref: 4), PULSE DELAY 2 controls the delay of PULSE SYNC OUT relative to FUNC OUT 10 and PULSE/SQUARE OUT 12.

#### NOTE

PULSE SYNC OUT is the correct sync signal for the pulse waveform and the burst mode.

17 FREQ MULT Control — Outer coax knob selects one of nine frequency multipliers for dial 1 setting.

VERNIER/SYM Control — When the SYM switch 3 is off (extended) this inner coax knob is a fine adjustment of the frequency dial 1 setting. CCW rotation decreases the frequency by approximately 1%. When in cw position (FREQ CAL), the settings on the dial will be accurate. When SYM switch is on (depressed) this control

varies the symmetry of the waveforms (normally 50% duty cycle). Symmetry range is 19:1 to 1:19 (half cycle to half cycle ratio). When SYM is used, the main generator frequency is divided by 10. Extending SYM switch ensures 1:1 (50%) symmetry. See figure 3-5.

\* SYNC DUTY CYCLE VARIES SAME AS FUNC OUT SIGNAL WHEN SQUARE FUNCTION (  $\neg_1$  ) IS SELECTED.

Figure 3-5. Effect of Symmetry Control

- 18 TRIG IN Connector BNC receives the external trigger and gate signals. These signals are applied to the trigger and gate circuit when the MODE switch 15 is in the TRIG or GATED positions. Refer to Section 1 Trigger (and Gate) Input specifications, for trigger signal requirements. The TRIG LEVEL control 15 selectively accepts trigger and gate signals for the trigger and gate circuits.

- VCG IN Connector BNC accepts ac or do voltages to proportionately control frequency within the range determined by the FREQ MULT 17. Positive voltages increase the frequency set by the dial 1; negative voltages decrease the frequency. The VCG IN will not drive the generator frequency beyond the normal limits of a range. Input impedance is 10 kΩ.

- 20 POWER Pushbutton Depressed is power on, extended is power off.

#### 3.2 OPERATION

Perform the initial checkout in Section 2 for the feel of the instrument. Any questions concerning individual controls and connectors may be answered in paragraph 3.1.

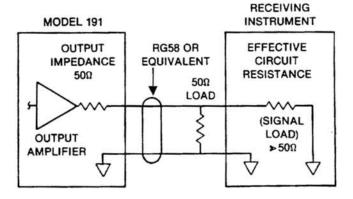

#### 3.2.1 Signal Termination

Proper signal termination, or loading, of the generator connectors is necessary for its specified operation. For example, the proper termination of the  $50\Omega$  OUT connector is shown in figure 3-6. Placing the 50 ohm terminator, or 50 ohm resistance, in parallel with a higher impedance, matches the receiving instrument input impedance to the coax characteristic and generator output impedance, thereby minimizing signal reflection or power loss on the line due to impedance mismatch.

The input and output impedances of the generator connectors are listed below.

| Connector              | Impedance   |  |  |

|------------------------|-------------|--|--|

| FUNC OUT               | 50 <b>Q</b> |  |  |

| SYNC OUT (TTL)         | 50Ω         |  |  |

| PULSE/SQUARE OUT (TTL) | 50♀         |  |  |

| PULSE SYNC OUT (TTL)   | 50Ω         |  |  |

| TRIG IN                | 1.5kΩ       |  |  |

| VCG IN                 | 10kΩ        |  |  |

Figure 3-6. Signal Termination

#### 3.2.2 Manual Function Generator Operation

The following steps demonstrate manual control of the function generator. (Bold numbers are keys to figure 3-1.)

| Step | Control/Connector |  | Setting                                               |  |

|------|-------------------|--|-------------------------------------------------------|--|

| 1    | FUNC OUT 10       |  | Connect circuit to output (refer to paragraph 3.2.1). |  |

| 2 | MODE             | 15   | Select CONT (FUNC).                                                         |

|---|------------------|------|-----------------------------------------------------------------------------|

| 3 | SYM              | 3    | Extended.                                                                   |

| 4 | FREQ MULT        | 17   | Set to desired range of frequency.                                          |

| 5 | Frequency Dial   | 1    | Set to desired fre-<br>quency within the<br>range.                          |

| 6 | FUNCTION         | 13   | Set to desired waveform.                                                    |

| 7 | DC OFFSET 11,    | , 13 | Set as desired. Limit offset to prevent waveform clipping (see figure 3-3). |

| 8 | OUTPUT ATTEN     | 8    | Select for desired attenuator range.                                        |

| 9 | <b>AMPLITUDE</b> | 9    | Select for desired                                                          |

#### 3.2.3 Voltage Controlled Function Generator Operation

waveform amplitude.

Operation as a voltage controlled function generator (VCG) is as for a manually controlled function generator, only the frequency within particular ranges is additionally controlled by an external voltage (±5V excursions) injected at the VCG IN connector. Perform the steps given in paragraph 3.2.2, only set the frequency dial to determine a reference from which the frequency is to be voltage controlled.

- For frequency control with positive dc inputs at 1. VCG IN, set the dial for a lower frequency limit.

- 2. For frequency control with negative dc inputs at VCG IN, set the dial for an upper frequency limit.

- 3. For modulation with an ac input at VCG IN, set the dial at the desired center frequency. Do not exceed the maximum dial range of the selected frequency range.

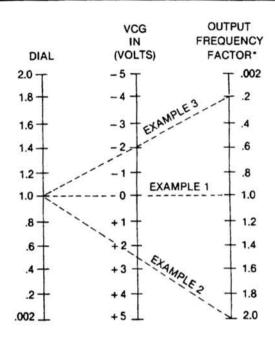

Figure 3-7 is a nomograph with examples of dial and voltage effects. Example 1 shows that with 0V VCG input, frequency is determined by the main dial setting, 1.0 in this example. Example 2 shows that with a positive VCG input, output frequency is increased. Example 3 shows that with a negative VCG input, output frequency is decreased. (Note that the Output Frequency Factor column value must be multiplied by a frequency range multiplier to give the actual output frequency.)

#### NOTE

Nonlinear operation may result when the VCG input voltage is excessive: that is, when the attempted generator frequency exceeds the range limits. The upper limit is 2 times the multiplier setting, and the lower limit is 1/1000th of the upper limit.

\*Must be multiplied by FREQ MULT switch setting

Figure 3-7. VCG Voltage-to-Frequency Nomograph

The up to 1000:1 VCG sweep of the generator frequencies available in each range results from a 5V excursion at the VCG IN connector. With the frequency dial set to 2.0, excursions between -5V and 0V at VCG IN provide the up to 1000:1 sweep within the set frequency range.

#### 3.2.4 Waveforms

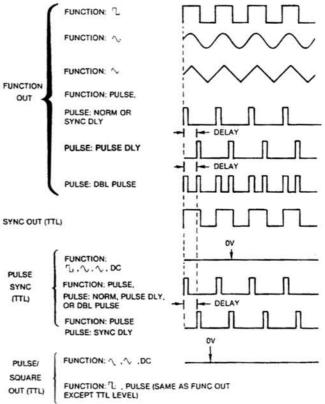

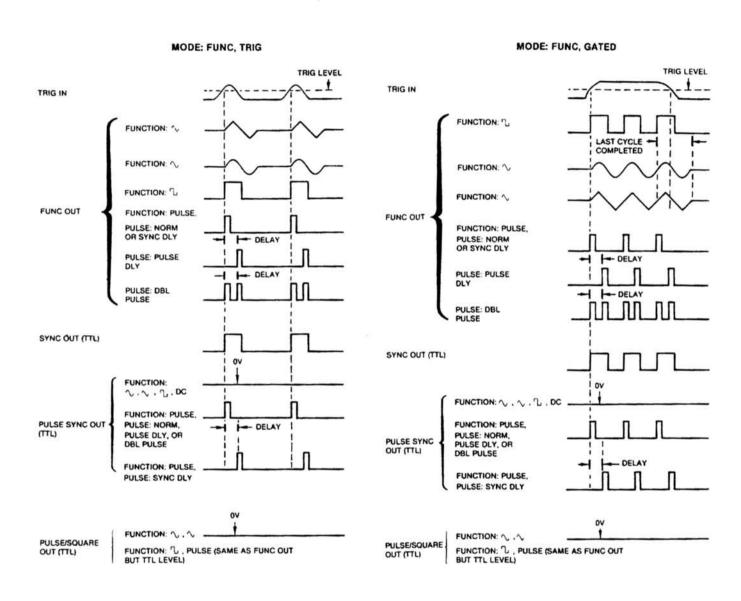

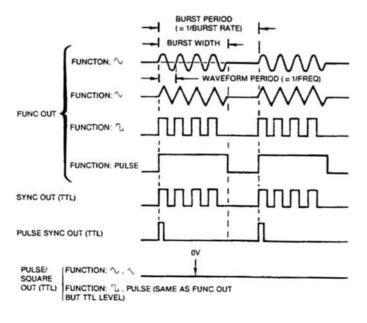

See figure 3-8 for definition of controllable waveform characteristics.

#### **Pulse Generator Operation** 3.2.5

Operation as a pulse generator is similar to the manual and VCG controlled generator except a single pulse, double pulse or square wave may be selected.

The following steps describe the pulse operation setup.

| Step | Control/Connector         | Setting                                                                                                                                    | Step            | Contr                                |

|------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------|

| 1    | MODE 15                   | CONT (FUNC)                                                                                                                                | 1               | MODE                                 |

| 2    | Frequency dial 1          | Select pulse repetition rate.                                                                                                              | •               | DUDO                                 |

| 3    | FREQUENCY 17 MULTIPLIER   | Select pulse repetition rate.                                                                                                              | 2               | BURS                                 |

| 4    | FUNCTION 13               | Select PULSE.                                                                                                                              | 3               | BURS                                 |

| 5    | PULSE/SQUARE 12<br>OUTPUT | Select desired pulse format.                                                                                                               | 25              |                                      |

| 6    | PULSE 4                   | Select desired pulse mode.                                                                                                                 |                 |                                      |

| 7    | PULSE WIDTH 6             | Select desired pulse width range and approximate portion of range.                                                                         |                 | <b>FUNC</b>                          |

| 8    | PULSE DELAY 2             | Select desired pulse<br>delay range and ap-<br>proximate portion of<br>range. (Applicable only<br>if PULSE DLY was<br>selected in step 6.) | FUNCTION<br>OUT | FUNC<br>FUNC<br>FUNC<br>PULS<br>SYNC |

| 9    | DC OFFSET 11, 13          | Set as desired. Limit pulse amplitude as necessary to prevent clipping (see figure 3-2).                                                   | SYNC OUT        | PULS                                 |

| 10   | AMPLITUDE 8,9             | Select desired amplitude.                                                                                                                  | PULSE           | FUNC                                 |

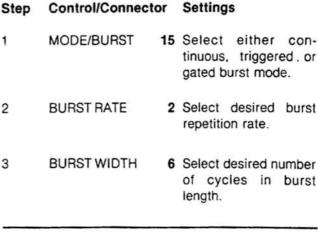

#### 3.2.6 Burst Generator Operation

In burst mode, the burst generator initiates a gate pulse, controlled by BURST RATE and BURST WIDTH, that gates the main generator. The main generator controls parameters of the signal being burst; i.e., frequency, function and amplitude. Refer to figure 3-8 for burst characteristics.

Set the main generator controls as for manual function generator operation (paragraph 3.2.2) and verify that the output signal is correct (other than not being in a "burst" mode). Then, set the burst controls as follows. (Bold numbers are keys to figure 3-1.)

MODE: FUNC, CONT

Figure 3-8. Waveform Characteristics

Figure 3-8. Waveform Characteristics (Cont)

#### MODE: BURST, GATED

#### MODE: BURST, TRIG

#### MODE: BURST, CONT

Figure 3-8. Waveform Characteristics (Cont)

# SECTION CIRCUIT DESCRIPTION

#### 4.1 INTRODUCTION

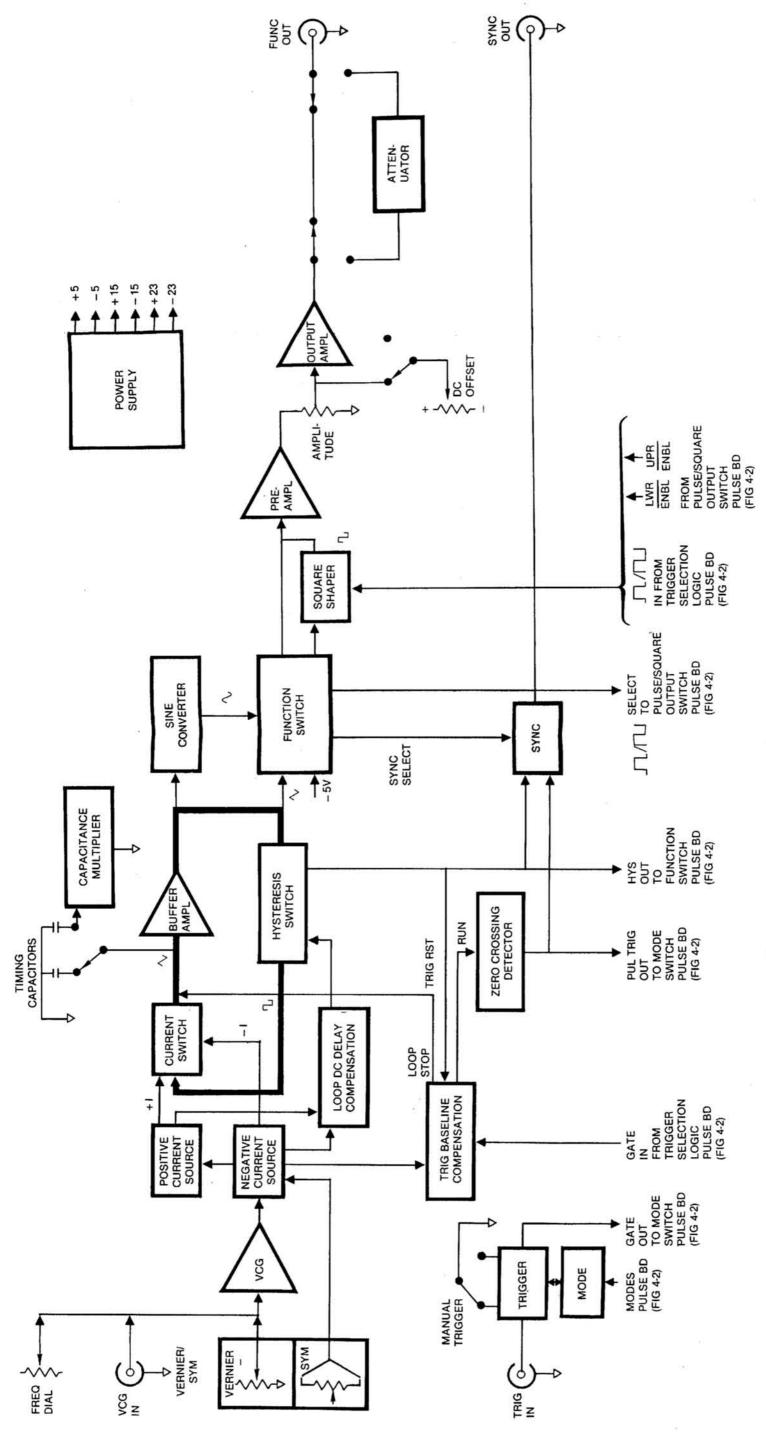

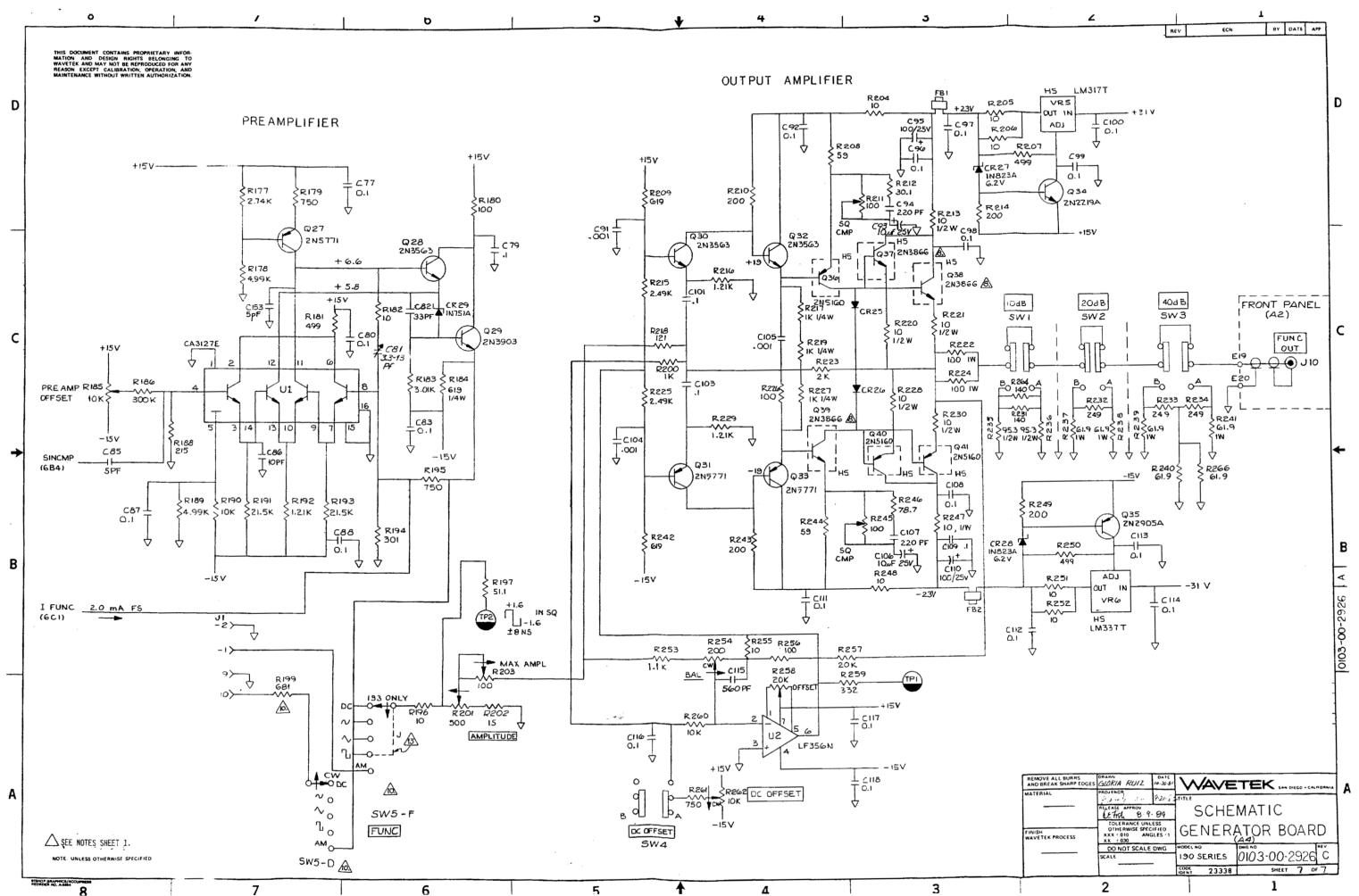

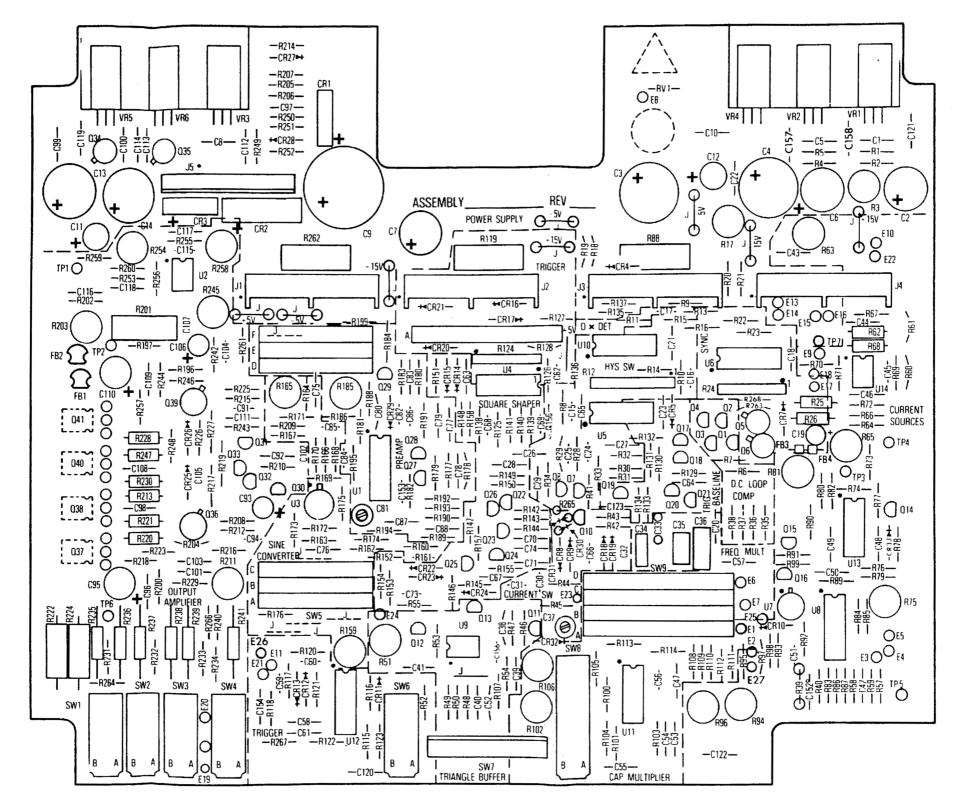

This section describes the functions of the major circuits elements and their relationships to one another as shown in figures 4-1 and 4-2. First, the function generator portion is described, then the pulse circuit and, last, detailed circuit descriptions are given.

#### 4.2 FUNCTION GENERATOR BLOCK DIAGRAM ANALYSIS

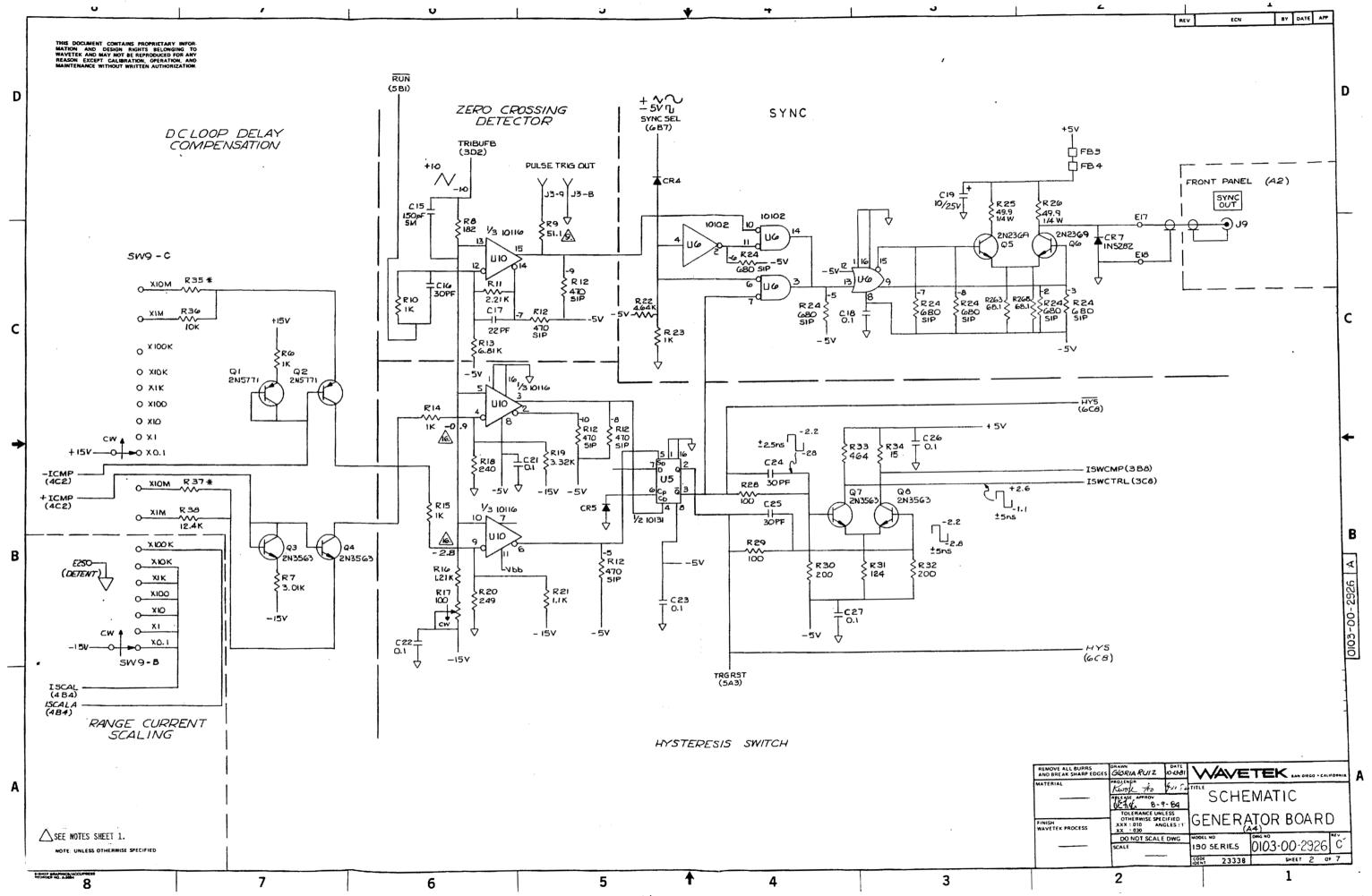

As shown in figure 4-1, the VCG (Voltage Controlled Generator) sums the voltage inputs from the frequency dial, VCG IN, and frequency vernier to provide a voltage control signal for the positive and negative current sources. The positive and negative current sources generate precision currents, linearly related to the output of the VCG summing amplifier, which pass through the current switch to the timing capacitors. Additional linear currents are generated for loop dc delay compensation and the trigger baseline compensation.

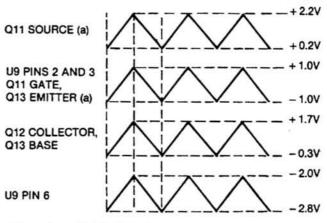

The current switch, controlled by the hysteresis output, causes either the positive current source or the negative current source to charge the timing capacitor selected by the frequency multiplier. When the positive current source is switched in, the charge on the timing capacitor will rise linearly producing the positive-going triangle slope. Likewise the negative current source produces the negative going triangle slope.

The triangle buffer amplifier is a unity gain amplifier whose output is fed to the hysteresis switch, sine converter and output circuits. The hysteresis switch operates as a "window" comparator with limit points set to the triangle peaks. When the positive going ramp reaches + 1.0V, the hysteresis switch toggles to a low state causing the current switch to connect the negative current source. This causes the timing capacitor voltage to linearly ramp to -1.0V as the timing capacitor voltage reaches -1.0V, the hysteresis switch toggles to a high state, switching in the positive current source. The generator loop continues to oscillate producing simultaneous triangle and square waves, at a frequency determined by the frequency multiplier and the magnitude of the timing

current controlled by the sum of the dial setting, the VCG input, and the vernier.

Depressing the SYM button produces an unsymmetrical waveform and a division of the frequency by a factory of 10. The VERNIER/SYM control creates an imbalance in the current sources and therefore an imbalance in the waveform symmetry up to a ratio of 19:1. The result is variable duty cycle pulse, variable askewed sine wave and variable "sawtooth" triangle waves.

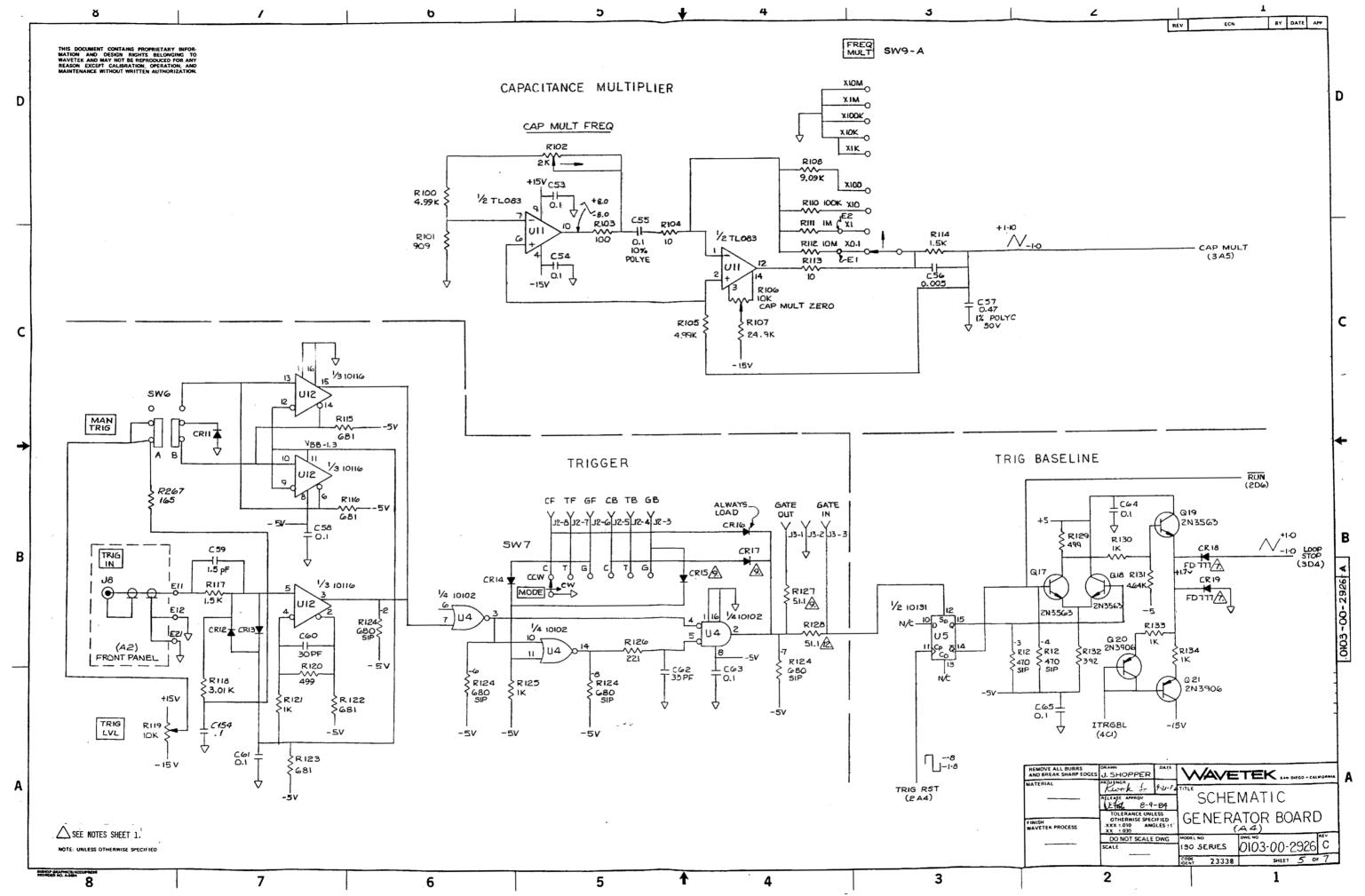

The dc loop delay compensation circuit is used on the two highest frequency ranges to compensate for loop delay. This circuit causes the hysteresis switch trip points to switch earlier in the cycle, and prevents the timing capacitors from charging beyond  $\pm 1.0$ V. The switch points are adjusted in proportion to the charging current, thus ensuring a constant amplitude as frequency is varied.

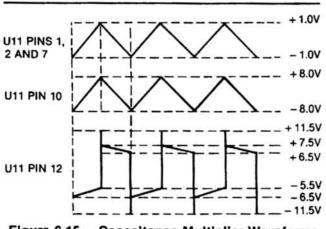

The capacitance multiplier is an active circuit which simulates capacitors up to 10,000 times larger than the timing capacitor, thus allowing very long charging times using physically small capacitors. This circuit is used in the four lowest frequency ranges.

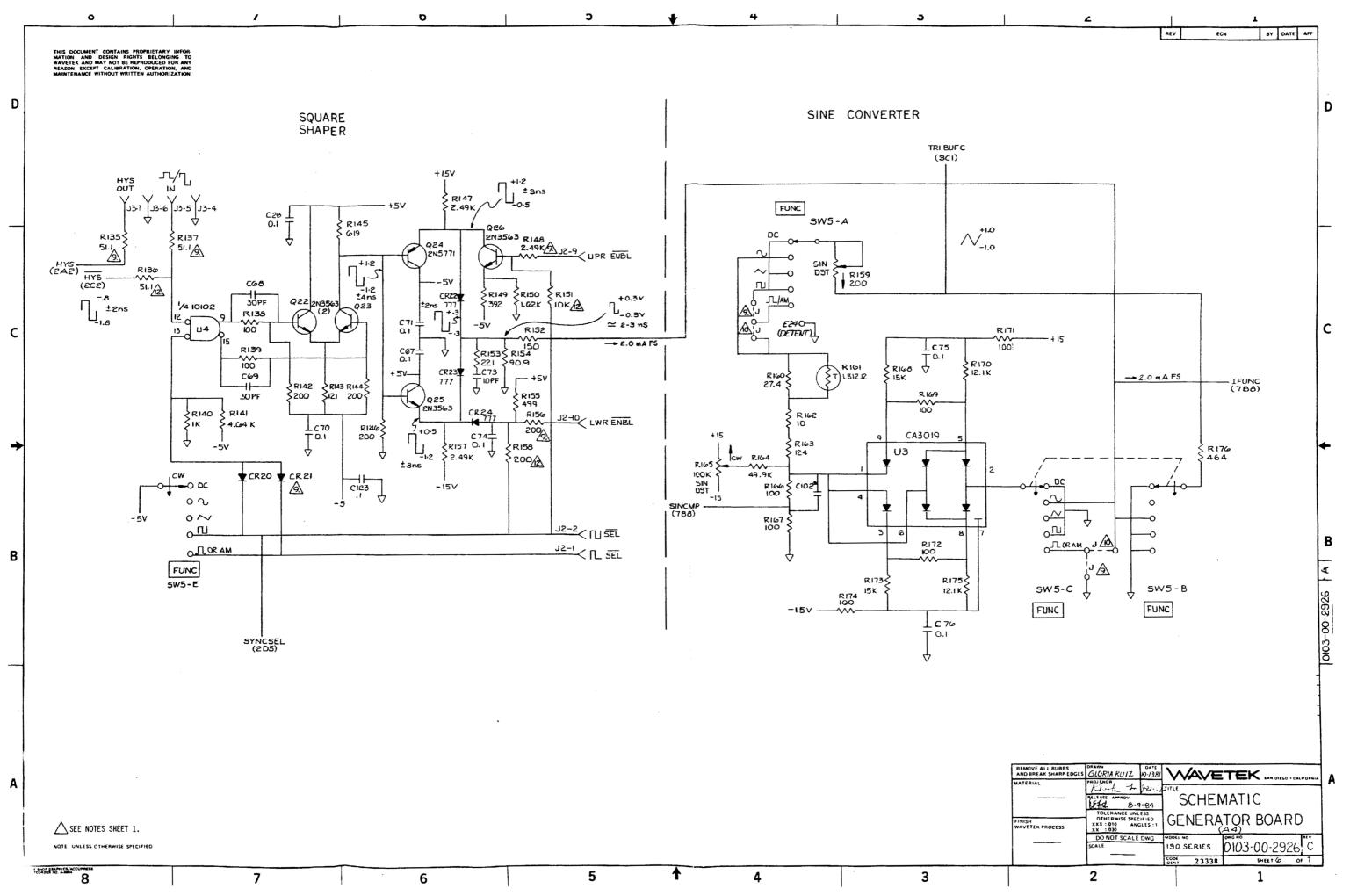

The sine converter accepts a  $\pm$  1.0 volt triangle signal from the triangle buffer and converts it to a sine wave current. The output is fed via the function switch to the preamplifier.

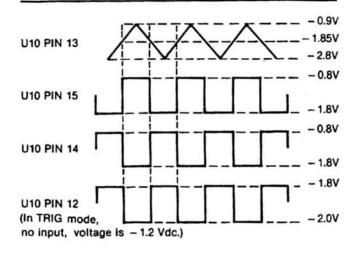

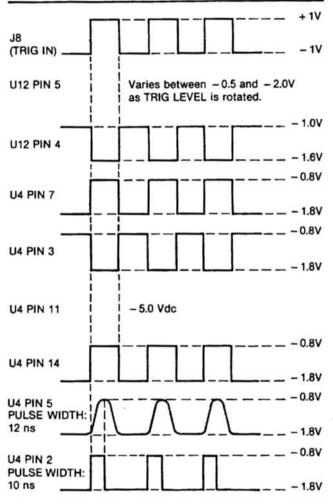

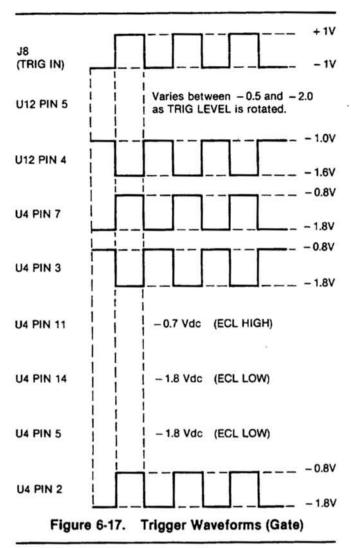

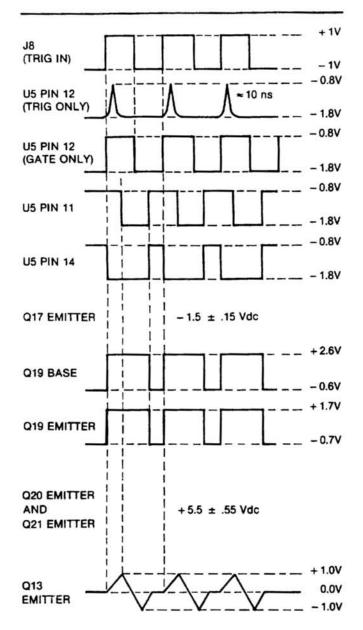

The trigger circuit allows precise single or multiple (gated) cycles at the output in response to external trigger signals or manual trigger operation. The trigger circuit operates by holding the timing capacitor at 0 volts, via the loop stop signal, on the positive going triangle ramp, until a trigger signal occurs. In the TRIG mode a single cycle is produced for each trigger signal above the variable trigger level threshold. In the GATED mode continuous cycles are generated for the time period at which the external signal is above the trigger level threshold plus the time for completion of the last partial cycle. The RUN signal causes the SYNC output to stay in the low state when the generator is quiescent. The TRGRST signal resets the trigger circuit and generator to the quiescent state on every generator cycle to arm it for the next trigger input. The trigger baseline compensation circuit holds the generator output at zero volts (within specified limits) during the quiescent intervals at any position (value) of the frequency dial, FREQ MULT, VCG IN, or VERNIER.

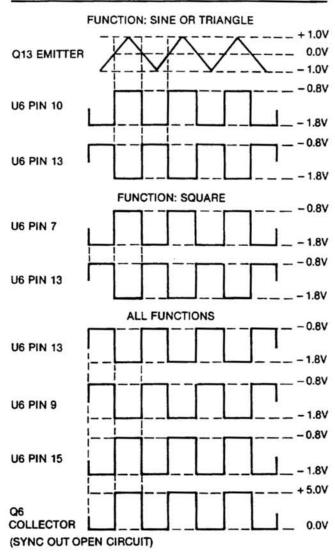

The sync circuit accepts the square wave signal from the hysteresis switch and converts it to a true  $50\Omega$  TTL level output. In square wave function the sync is in phase with the output, but in triangle or sine functions, a zero crossing detector causes the sync output to be in phase with the zero crossing of the output waveform.

When square is selected by the function switch, the square shaper accepts the signal from the hysteresis switch and converts it to a clean, fast square wave current to drive the preamplifier. The function switch also sends a signal to the sync circuit, causing the sync output to be in phase with the positive going edge of the output squarewave. In sine, triangle or DC functions, the square shaper input and output are disabled so as not to interfere with the selected waveform.

The preamplifier is fed from both the function switch and the square shaper. The voltage output drives the output amplifier via the amplitude control.

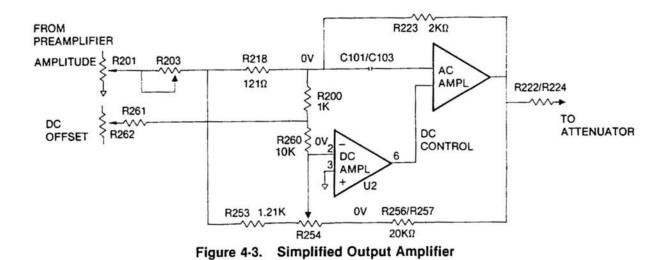

The output amplifier accepts signals from the preamplifier by way of the amplitude control and drives the output attenuator. DC offset is achieved by offsetting the output amplifier.

The output attenuator, fed directly from the output amplifier, provides up to 70 dB of attenuation to the selected waveform or DC offset. This signal is connected directly to the FUNC OUT BNC.

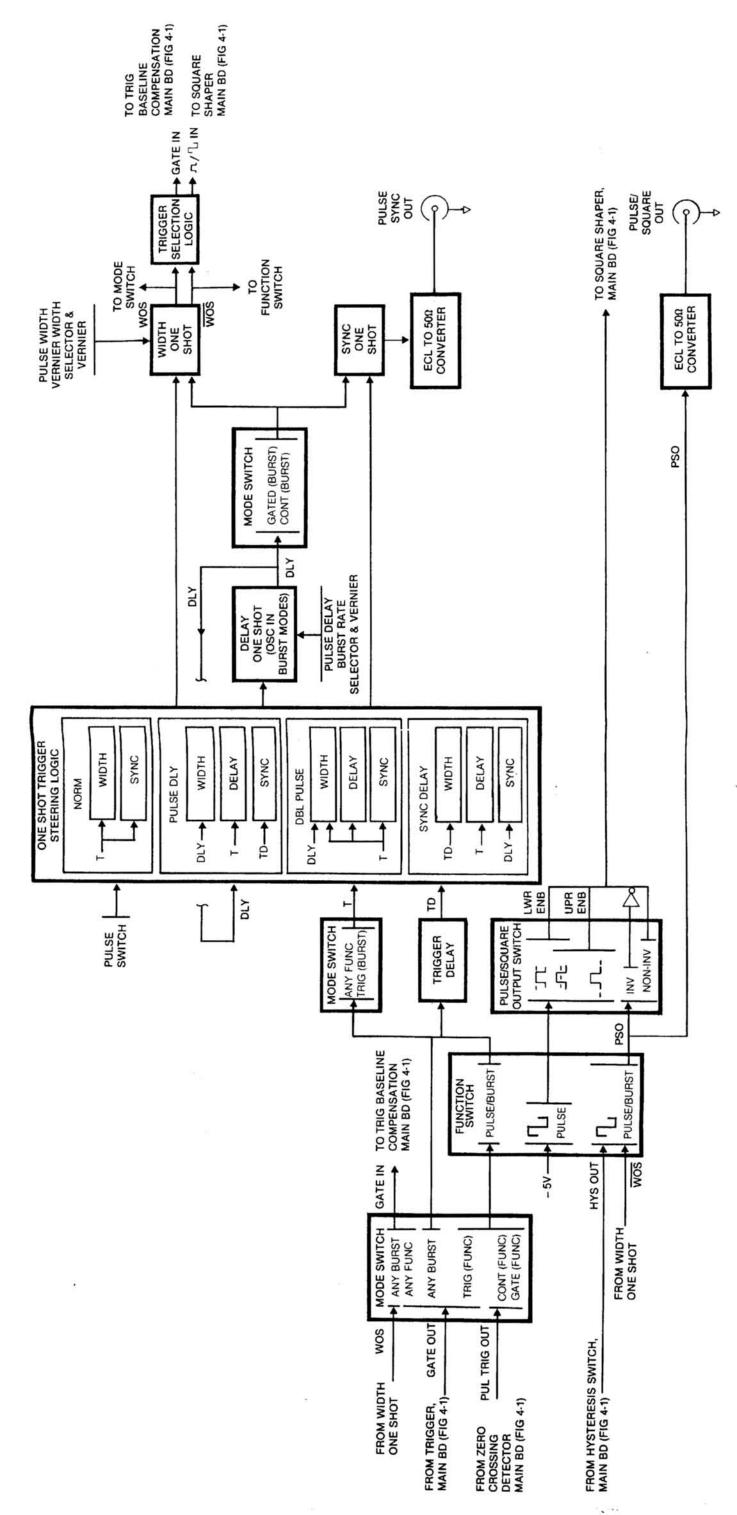

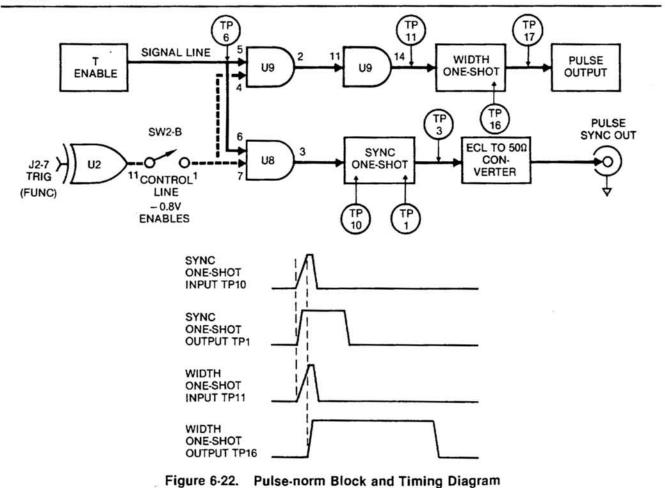

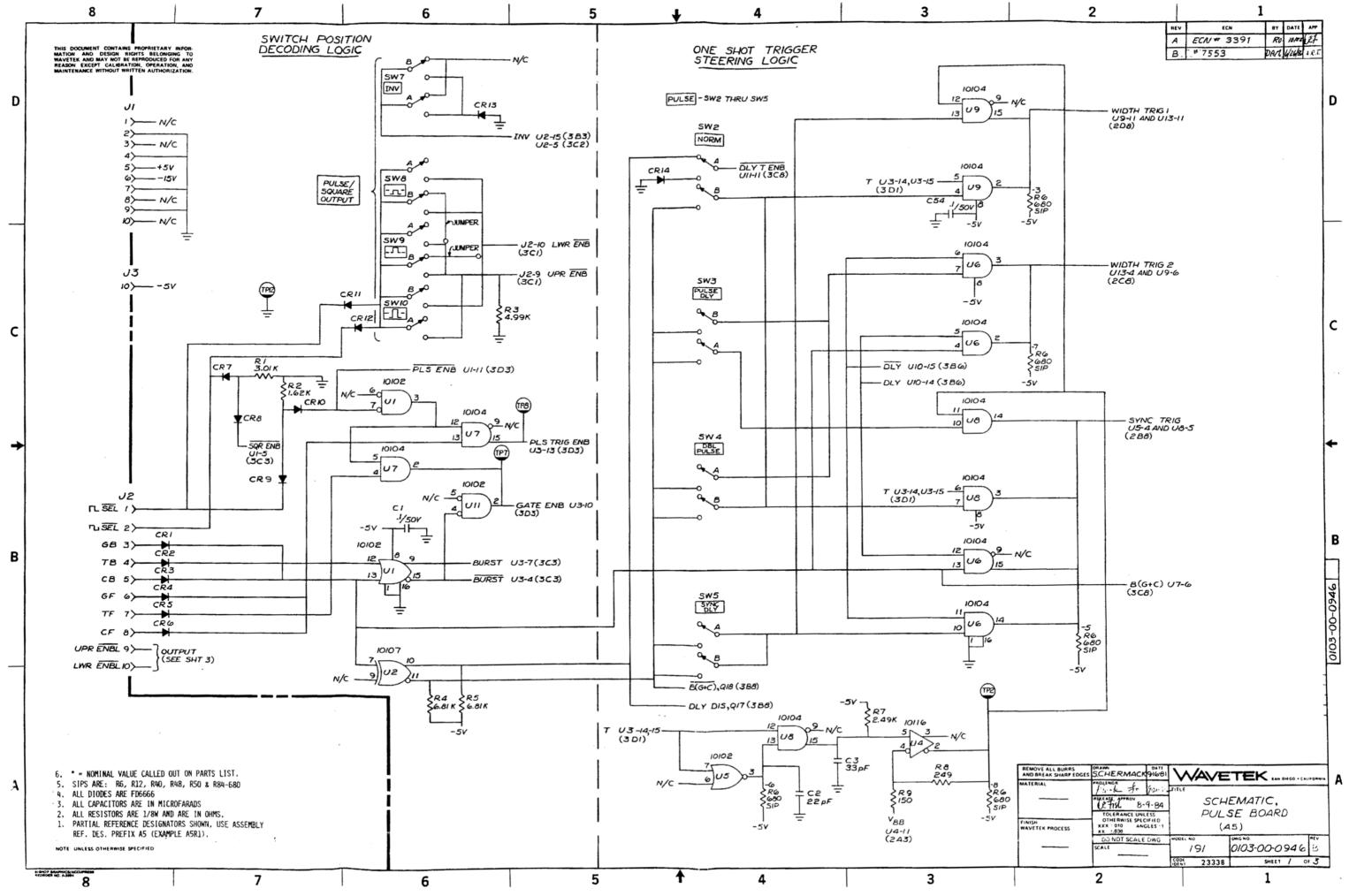

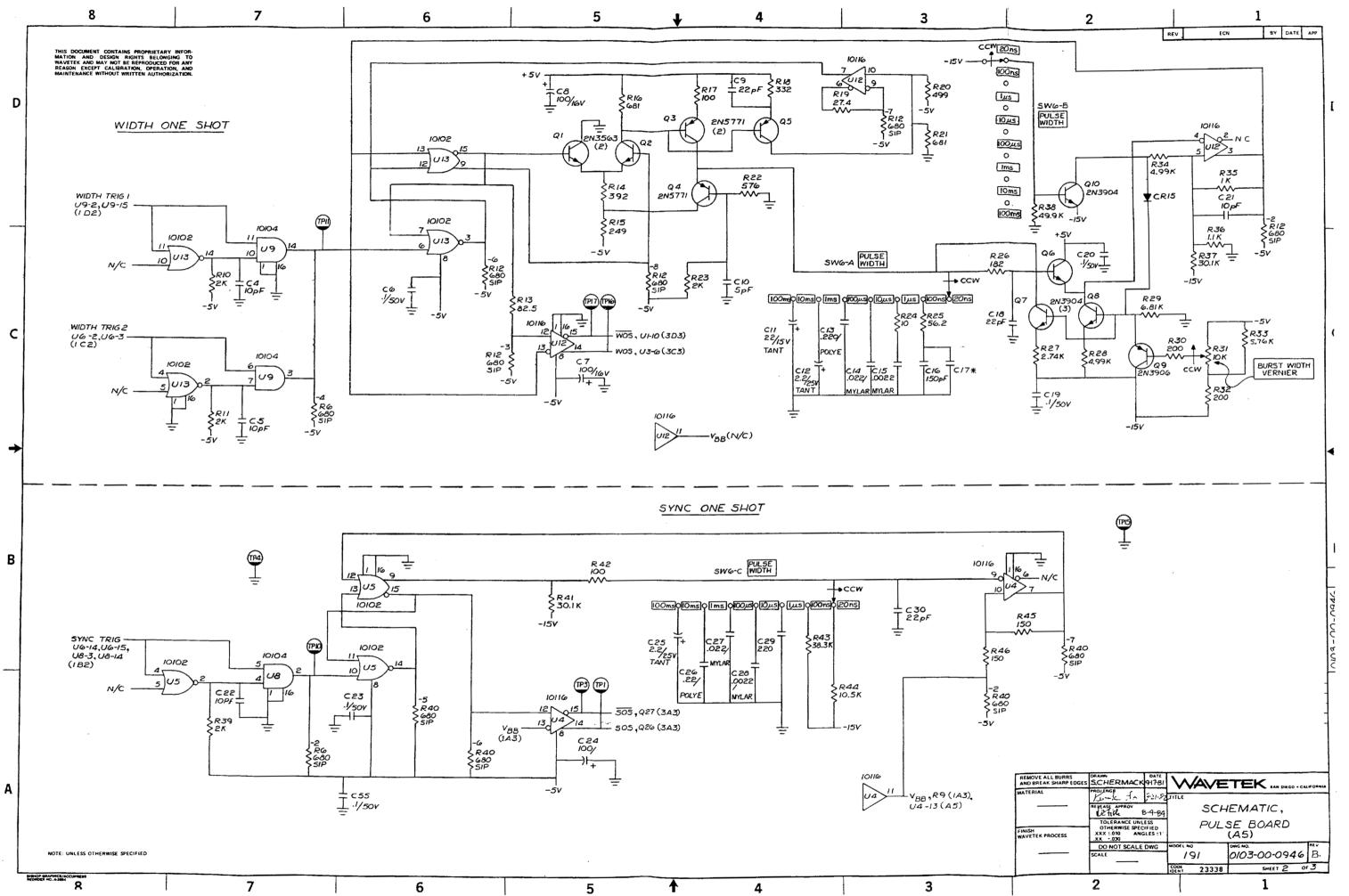

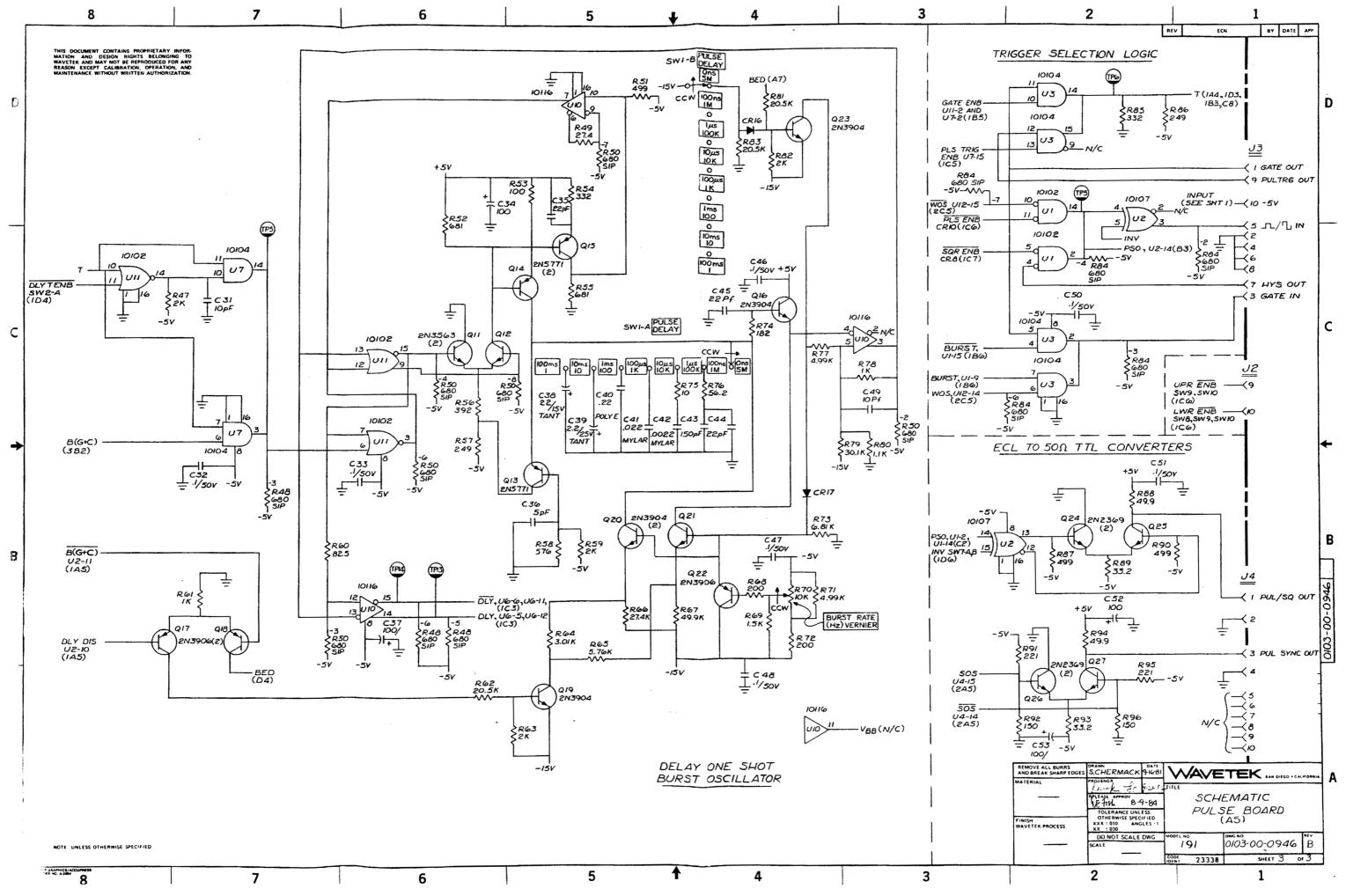

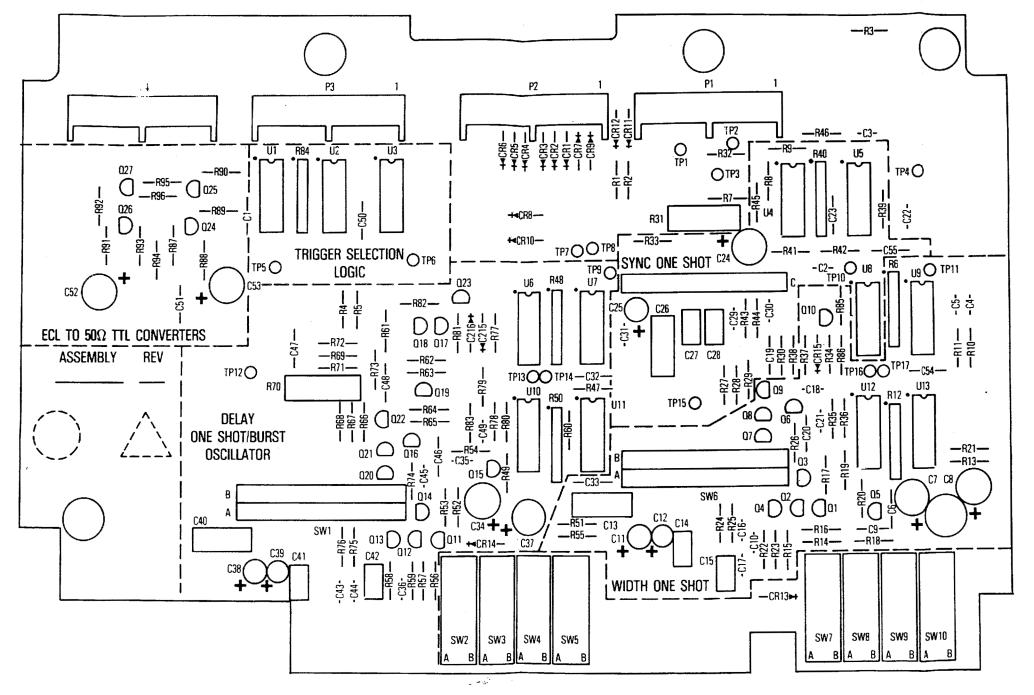

#### 4.3 PULSE BLOCK DIAGRAM ANALYSIS

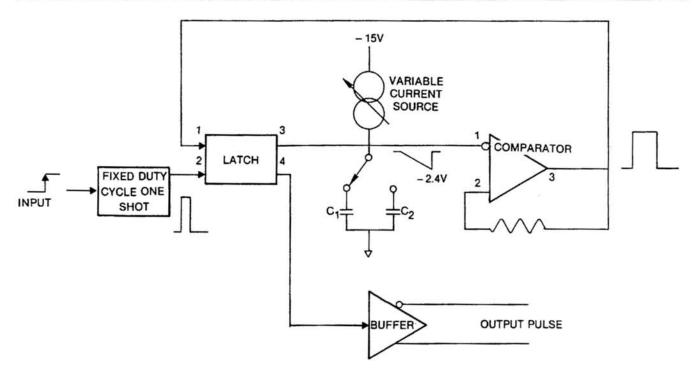

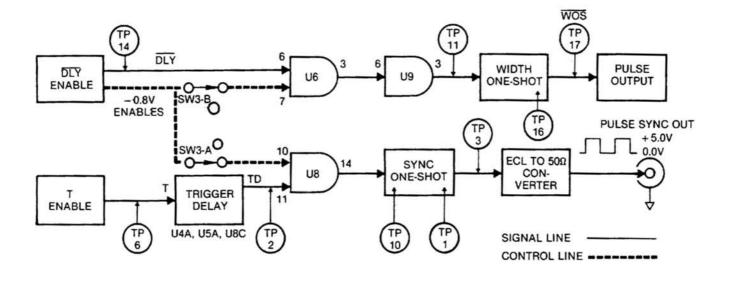

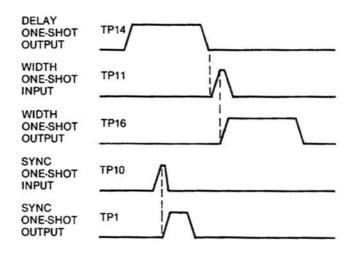

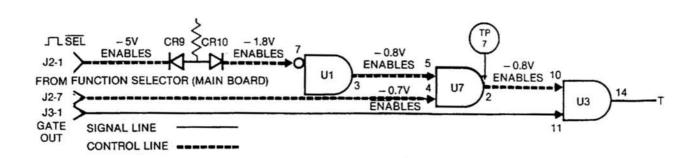

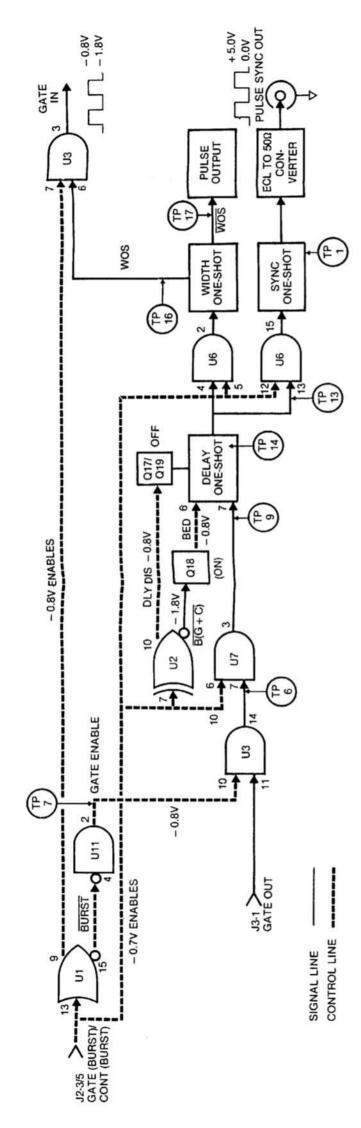

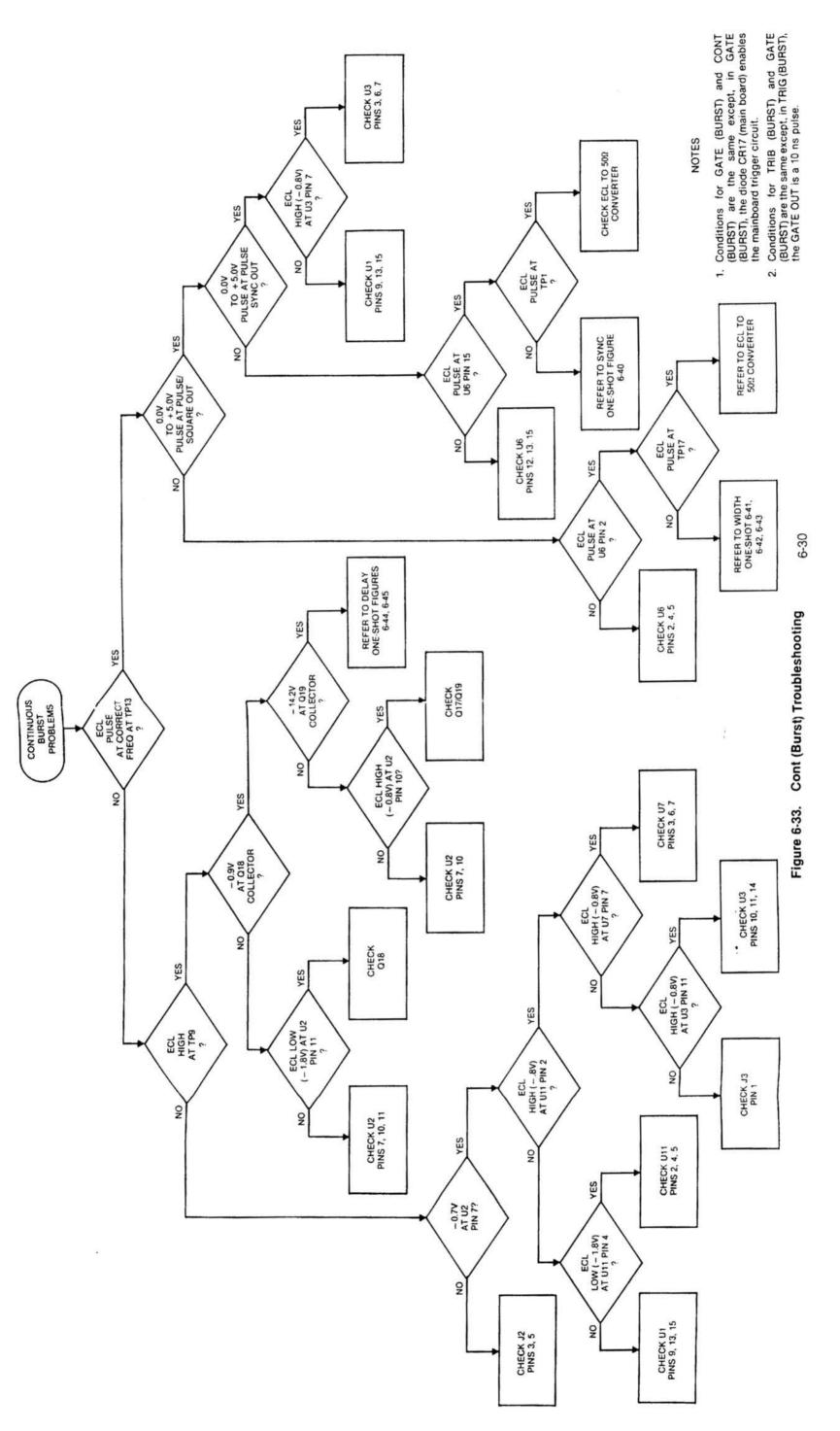

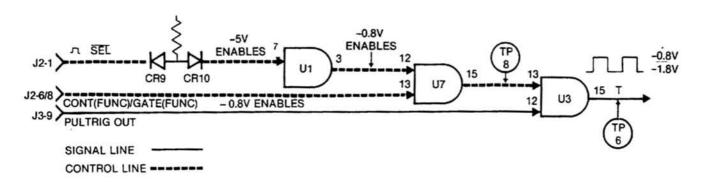

Refer to figure 4-2. All signals found on the pulse board originate from the hysteresis switch, trigger circuit, and zero crossing detector, all on the main board. In addition, when the unit is in one of the three BURST modes, the delay one shot acts as an auxiliary generator which can be triggered and gated from the front panel TRIG controls and TRIG IN connector. The signals return to the square shaper and trigger baseline circuits on the main board, and terminate at the PULSE/SQUARE OUT and PULSE SYNC OUT front panel connectors.

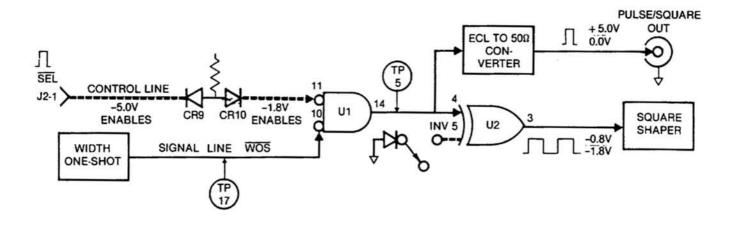

In the  $\ \Box$  function, the hysteresis switch output (HYS OUT) is sent directly to the PULSE/SQUARE OUT connector by way of the ECL-to-50 $\Omega$  converter. This signal also passes through a normal/invert circuit before being sent to the main board square shaper, where it can be modified to a positive pulse, negative pulse, or

provide an output balanced about ground, depending on which PULSE/SQUARE OUTPUT button is depressed. In PULSE function, the output of the width one shot  $(\overline{WOS})$  is substituted for the  $\ \Box$  function.

With the MODE switch in one of the three FUNC positions, the output of the trigger circuit is sent directly to the trigger baseline compensation circuit.

Three signal lines labeled T, DLY, and TD are used to drive the width, delay and sync one shot. T originates from either the trigger or zero crossing detector circuits on the main board. With the FUNCTION switch set to PULSE/BURST and the MODE switch set to CONT FUNC or GATE FUNC, T is driven by the zero crossing detector, but when the MODE switch is set to TRIG FUNC or one of the three BURST modes, T is driven by the trigger circuit. TD is a delayed T signal and originates from the trigger delay circuit. DLY is the one shot output of the delay one shot. The one shot trigger steering logic circuit connects T, DLY, and TD to the three one shot circuits depending on which PULSE button is depressed. Refer to the one shot trigger steering logic of figure 4-2 and use PULSE DLY as an example: DLY is connected to the width one shot, T is connected to the delay one shot, and TD is connected to the sync one shot.

In the CONT BURST or GATED BURST modes, DLY is also sent to the width and sync one shots. The sync one shot output (SOS) is sent to the ECL-to-50 $\Omega$  converter which drives the PULSE SYNC OUT connector.

In BURST mode, the width one shot output (WOS) is sent to the main board trigger baseline circuit.

The PULSE DELAY/BURST RATE selector controls the delay one shot and the PULSE WIDTH/BURST WIDTH selector controls the width one shot, along with their respective verniers.

#### 4.4 DETAILED CIRCUIT DESCRIPTIONS

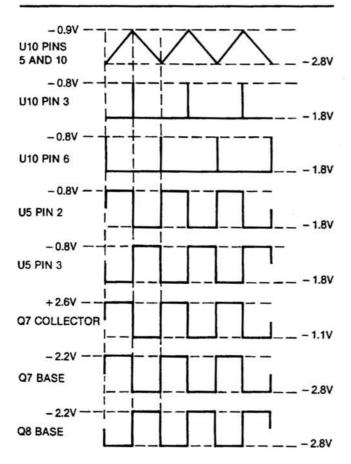

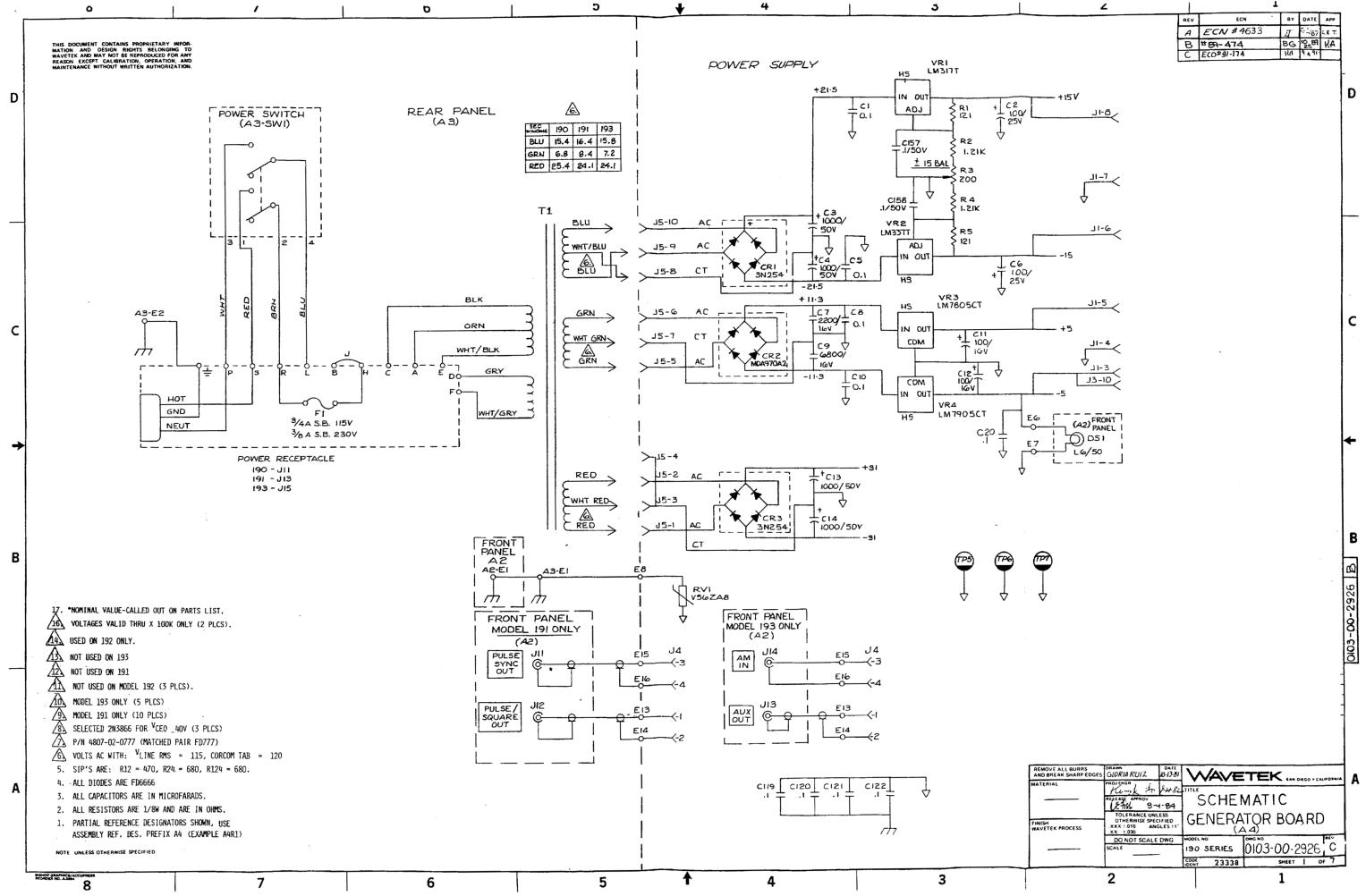

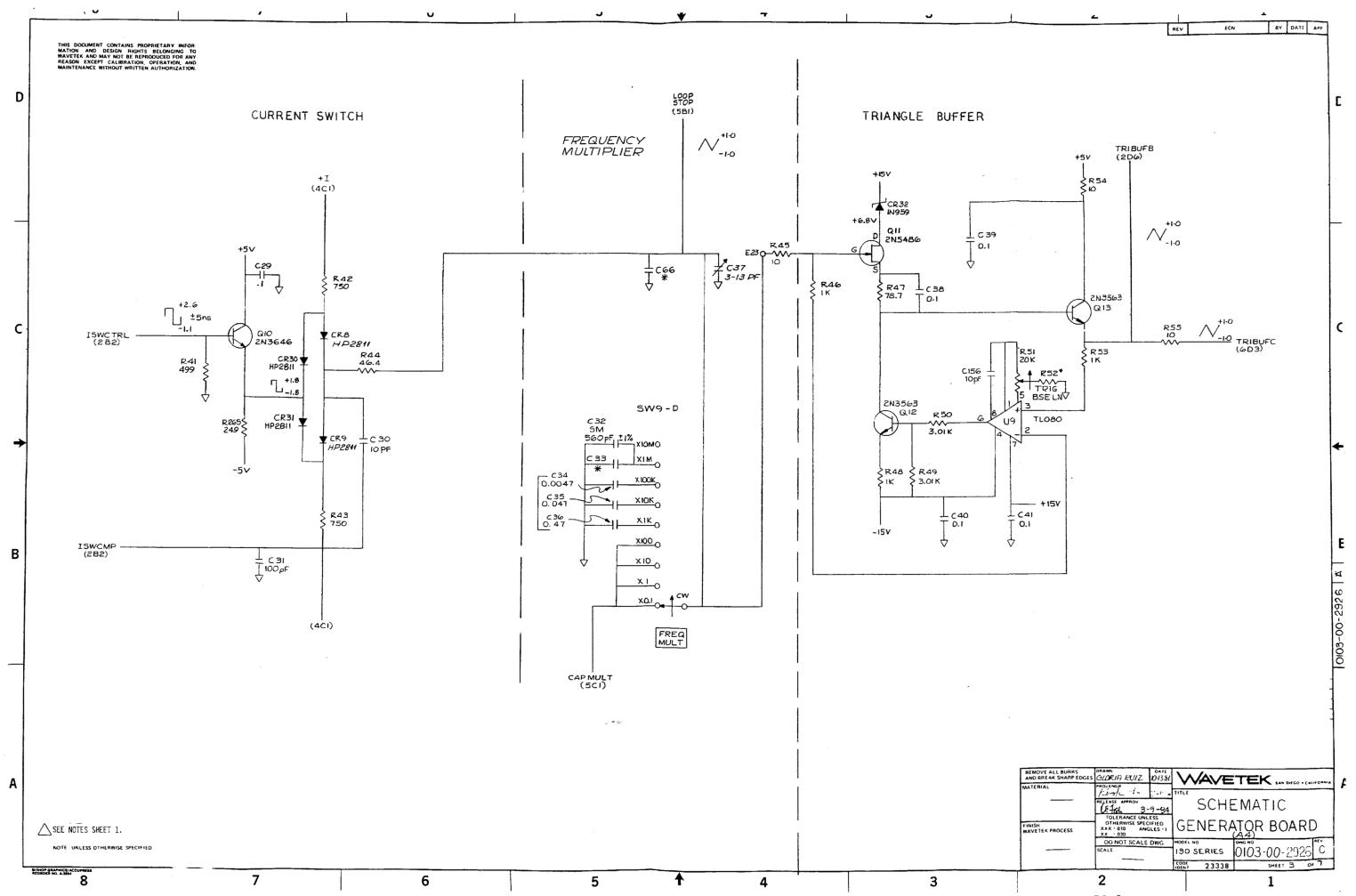

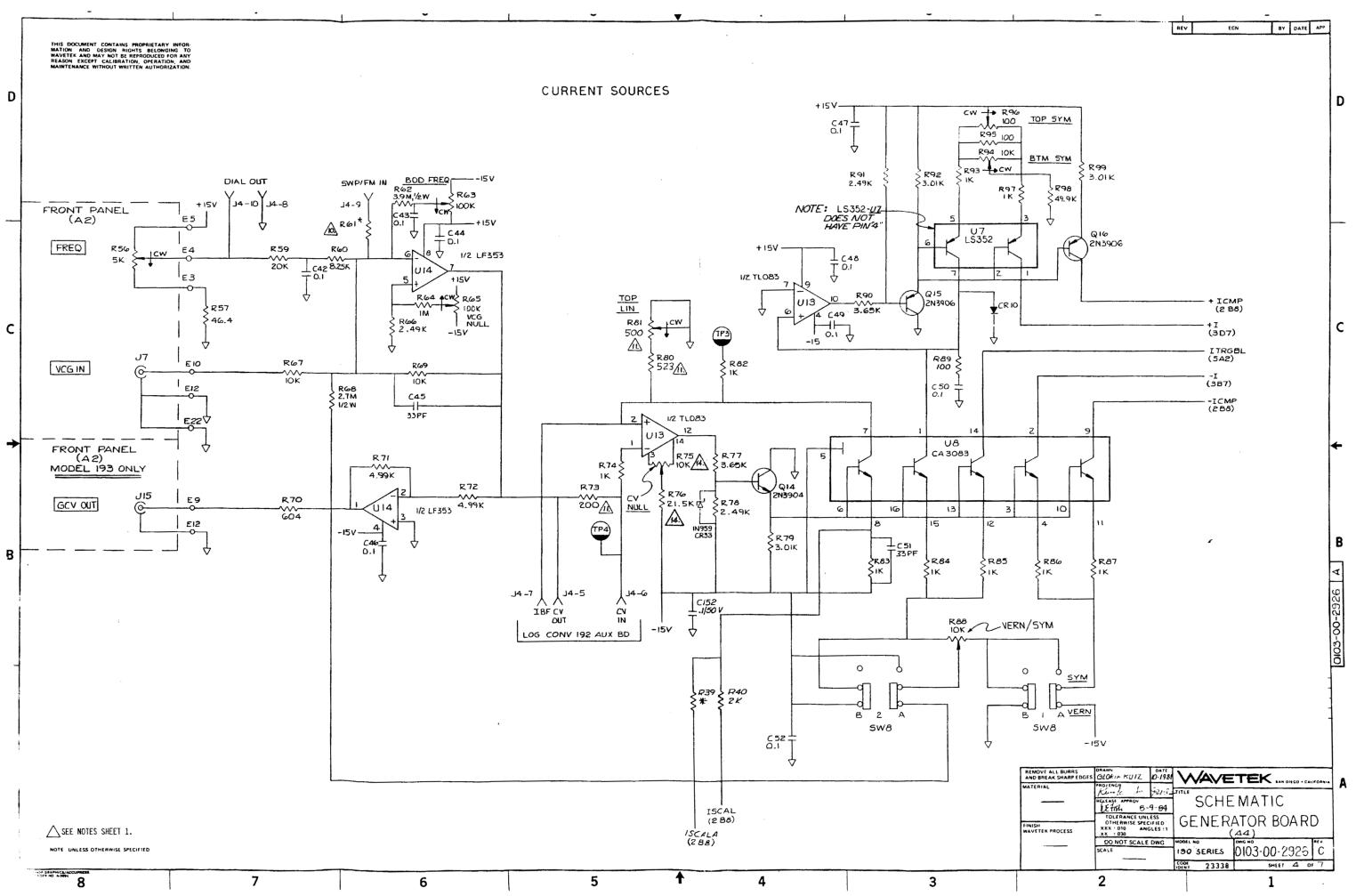

#### 4.4.1 Current Sources

Refer to the Generator Board Schematic sheet 4. The VCG IN (J7) and FREQ VERNIER (R88) are summed with the dial potentiometer (R56) at the summing node, U14 pin 6 of the VCG amplifier. Full scale on the dial causes a -5 volt control signal at the dial buffer output U14 pin 7. Rotating the dial to minimum, plus turning the FREQ VERNIER ccw produces -5 mV at U14 pin 7. The output of the buffer drives both the GCV buffer and current sources. The GCV output at U14 pin 1 is +5.0 volts at full scale.

The current source from U14 pin 7 is present at U13 pin 1. The output of U13 at pin 12 is fed through level

Figure 4-1. Function Generator Functional Block Diagram

shifting transistor Q14 to U8 pin 6. The collector current at pin 7 flows from ground through R81 and R80. As the voltage at U14 pin 7 varies, amplifier U13 and transistor Q14 adjust the base drive of U8 pin 6, and hence the collector current, until the voltage at U13 pin 2 equals the voltage at U13 pin 1. Because U8 is an array of matched transistors with the bases connected together, and all emitter resistors are equal with VERNIER selected, all collector currents are also equal.

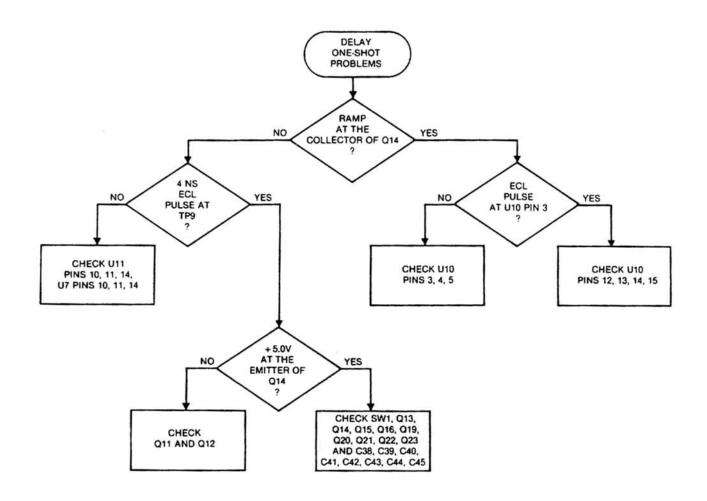

The positive current source is controlled by a current control signal at U8 pin 1, which is held at 0 volts by the servo action of U13 pins 6, 7 and 10, level shifting transistor Q15 and U7 pins 6 and 7. The current "I" in R84 must flow through R93, and because these resistors are both  $1k\Omega$ , an equal but opposite base control voltage is present on U7 pin 6 compared to U8 pin 6. Because the transitors in U7 are matched and their bases are at the same point, a positive current "I" flows in R97 and hence the positive current source. A small amount of adjustable balance is provided by R95 and R94 to enable the positive and negative currents to be set for correct symmetry.