### **INSTRUCTION MANUAL**

### MODEL 175 ARBITRARY WAVEFORM GENERATOR

WAVETEK SAN DIEGO, INC.

9045 Balboa Ave., San Diego, CA 92123

### **INSTRUCTION MANUAL**

### MODEL 175 ARBITRARY WAVEFORM GENERATOR

© - 1978 - Wavetek

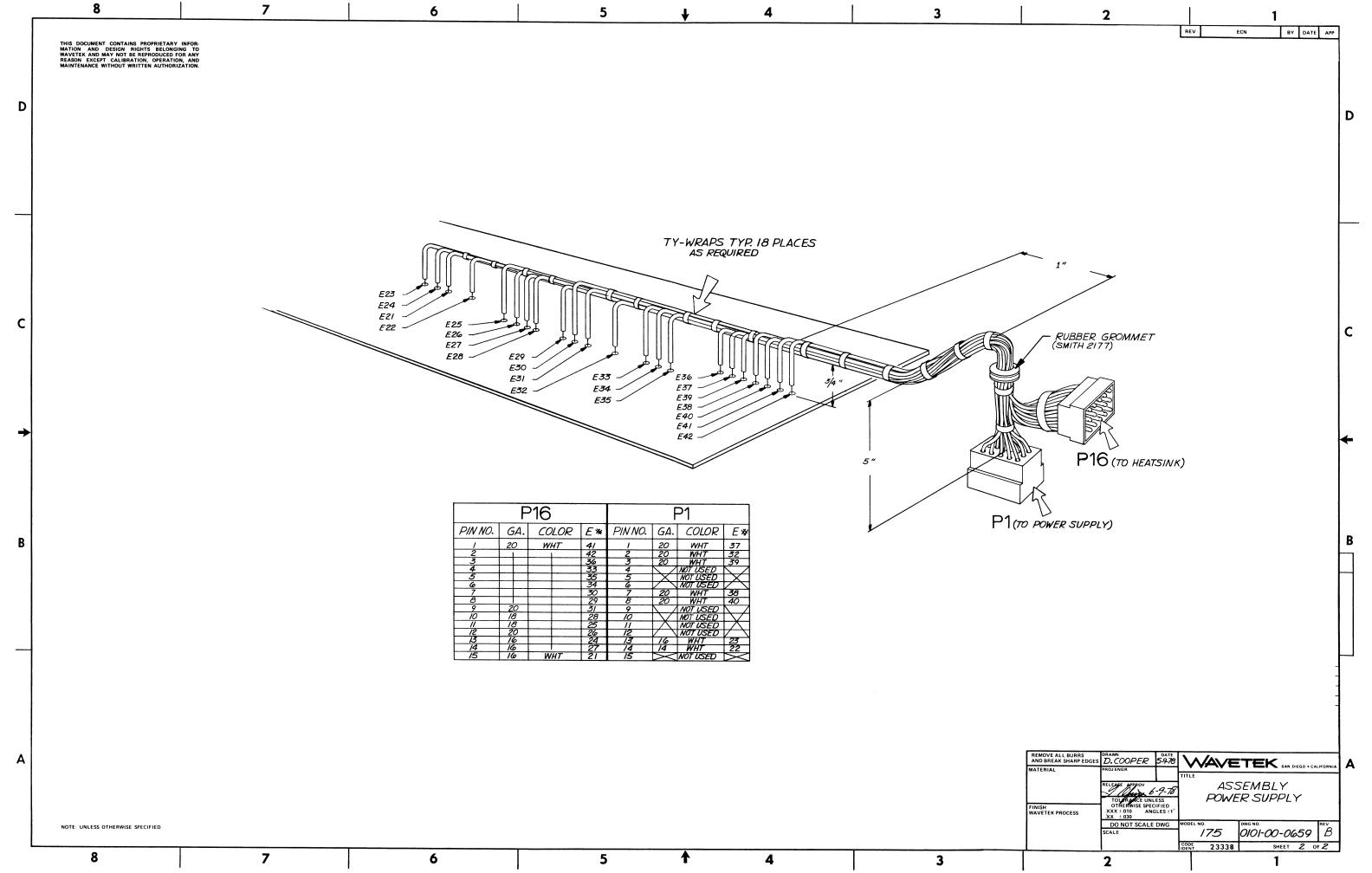

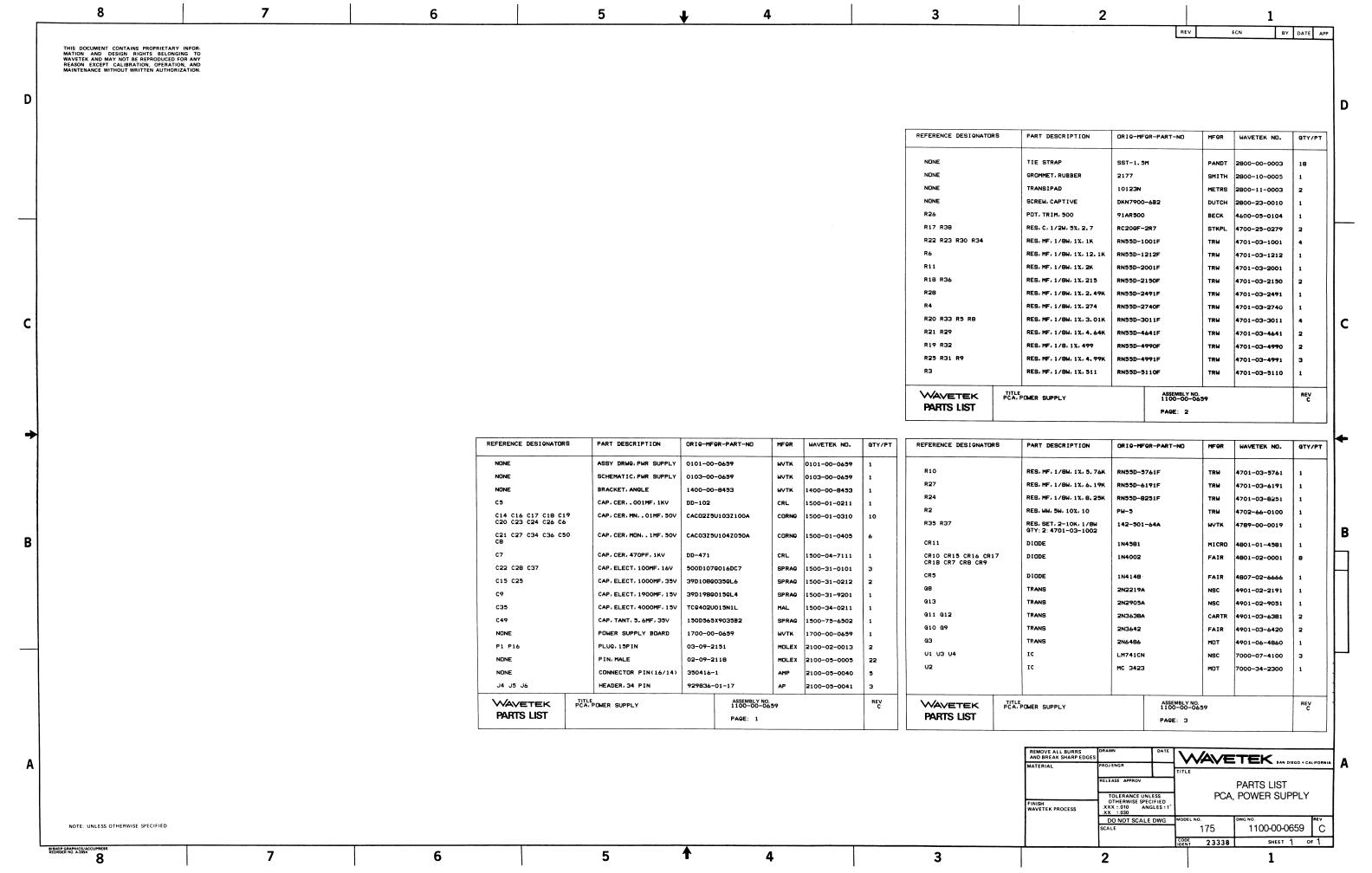

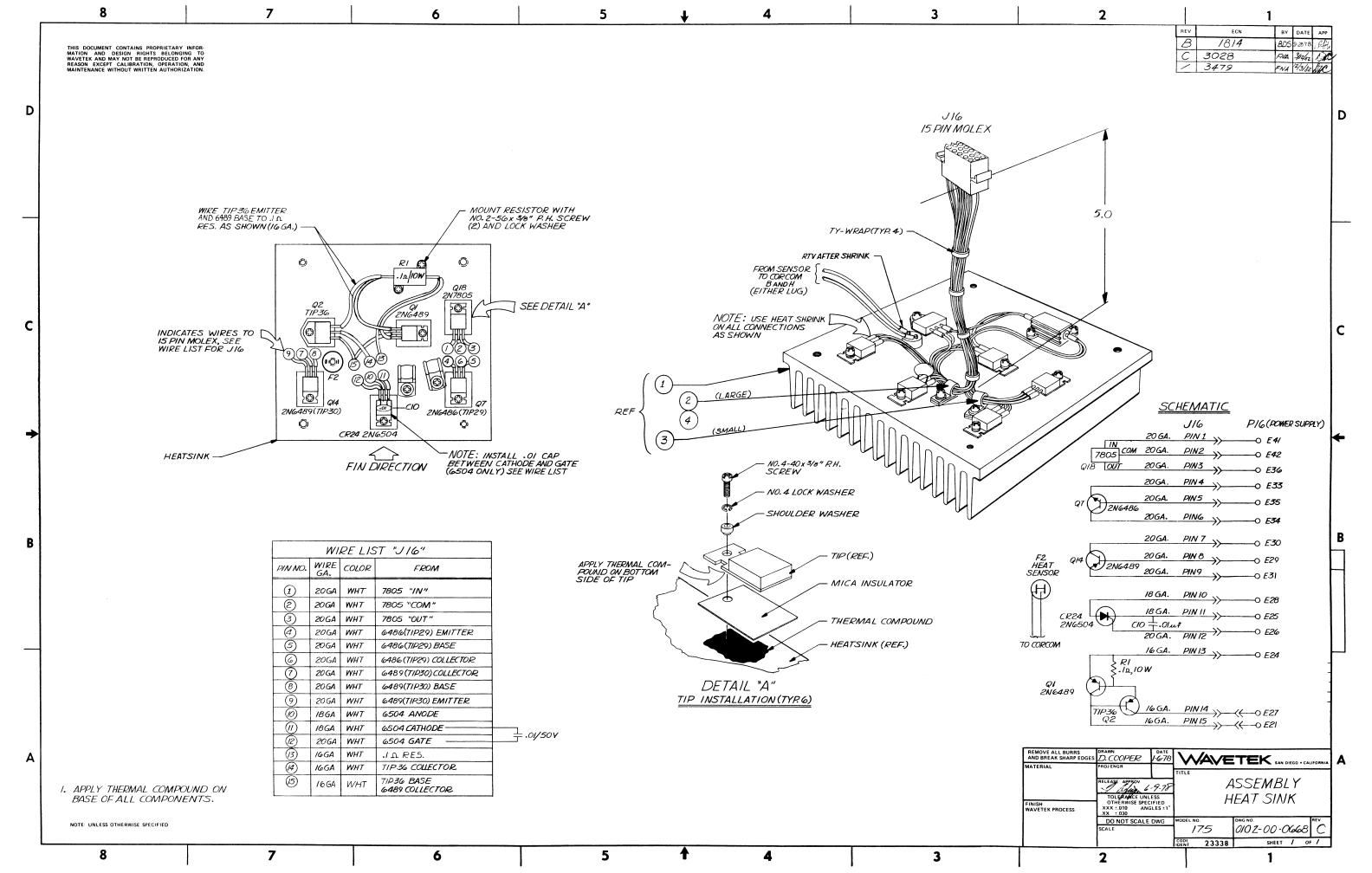

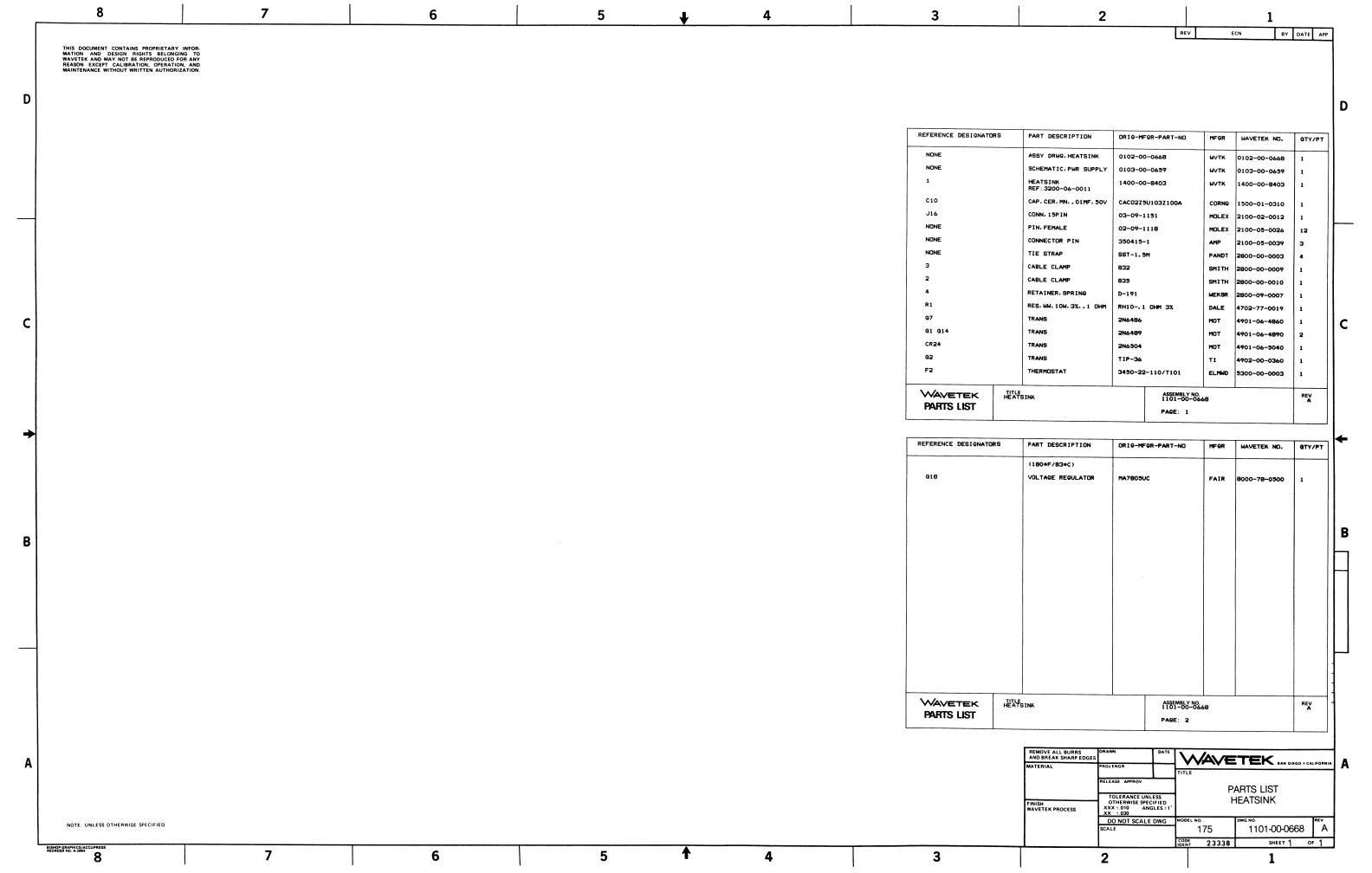

THIS DOCUMENT CONTAINS INFORMATION PROPRIETARY TO WAVETEK. THE INFORMATION IN THIS DOCUMENT IS NOT TO BE USED OR DUPLICATED IN ANY MANNER WITHOUT THE PRIOR APPROVAL IN WRITING OF WAVETEK.

i

WAVETEK SAN DIEGO, INC. 9045 Balboa Ave., San Diego, CA 92123 P. O. Box 85265, San Diego, CA 92138 Tel 619/279-2200 TWX 910/335-2007

### WARRANTY

Wavetek warrants that all products of its own manufacture conform to Wavetek specifications and are free from defects in material and workmanship when used under normal operating conditions and within the service conditions for which they were furnished.

The obligation of Wavetek hereunder shall expire one (1) year after delivery and is limited to repairing, or at its option, replacing without charge, any such product which in Wavetek's sole opinion proves to be defective within the scope of this Warranty. In the event Wavetek is not able to repair or replace defective products or components within a reasonable time after receipt thereof, Buyer shall be credited for their value at the original purchase price.

Wavetek must be notified in writing of the defect or nonconformity within the warranty period and the affected product returned to Wavetek's factory or to an authorized service center within thirty (30) days after discovery of such defect or nonconformity. Shipment shall not be made without prior authorization by Wavetek.

This is Wavetek's sole warranty with respect to the products delivered hereunder. No statement, representation, agreement or understanding, oral or written, made by an agent, distributor, representative or employee of Wavetek, which is not contained in this warranty, will be binding upon Wavetek, unless made in writing and executed by an authorized Wavetek employee. Wavetek makes no other warranty of any kind whatsoever, expressed or implied, and all implied warranties of merchantability and fitness for a particular use which exceed the aforestated obligation are hereby disclaimed by Wavetek and excluded from this agreement. Under no circumstances shall Wavetek be liable to Buyer, in contract or in tort, for any special, indirect, incidental or consequential damages, expenses, losses or delays however caused.

## **CONTENTS**

| SECTION 1 | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|           | 1.1 THE MODEL 175 1.2 SPECIFICATIONS 1.2.1 Versatility 1.2.2 Timing Precision 1.2.3 Amplitude Precision 1.2.4 General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-1<br>1-2<br>1-2                            |

| SECTION 2 | INSTALLATION AND INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

|           | 2.1 MECHANICAL INSTALLATION 2.2 ELECTRICAL INSTALLATION 2.2.1 Power Connection 2.2.2 Signal Connections 2.2.3 General Purpose Instrument Bus (GPIB) Connections 2.2.4 GPIB Address 2.2.5 Initial Checkout and Operation Verification 2.2.6 Permanent Custom Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1<br>2-1<br>2-1<br>2-2<br>2-2<br>2-3       |

| SECTION 3 | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              |

|           | 3.1 GENERAL 3.2 KEYBOARD 3.2.1 Notes 3.2.2 Key Descriptions 3.3 POWER 3.4 INPUTS AND OUTPUTS 3.5 BASIC COMMAND STRUCTURE 3.6 COUNTER GENERATED WAVEFORMS 3.7 MEMORY DATA (Y) FOR ARBITRARY WAVEFORMS 3.8 SMOOTHING (O) 3.9 SAMPLE TIME (T) AND WAVEFORM SMOOTHING 3.10 CLOCK TIME UNITS (S) 3.11 FULL OR PARTIAL BLOCK (U) 3.12 BLOCK RATE (F) 3.13 AMPLITUDE (A) AND OFFSET (D) 3.14 ERRORS 3.15 PRESET AND MONITOR TRIGGER (M) 3.16 GPIB 3.16.1 Bus Lines Defined 3.16.2 GPIB Commands 3.16.3 GPIB Data Transfers 3.16.4 GPIB Talk Message and Terminator Character (R) 3.16.5 GPIB Service Request Enable (Q) 3.17 INPUT AND OUTPUT IMPEDANCES 3.17.1 Arbitrary Waveform Outputs 3.17.2 TTL Outputs 3.17.3 TTL Inputs 3.17.4 Changing Source Impedance of the Main Output | 3-12<br>3-12<br>3-12<br>3-13<br>3-13<br>3-14 |

# **CONTENTS (Continued)**

| SECTION 4 | CALIBRATION                                                                                                                                                                                                                                                                                               |                                                                                                    |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

|           | 4.1 INTRODUCTION                                                                                                                                                                                                                                                                                          | 4-1<br>4-1                                                                                         |  |  |  |  |

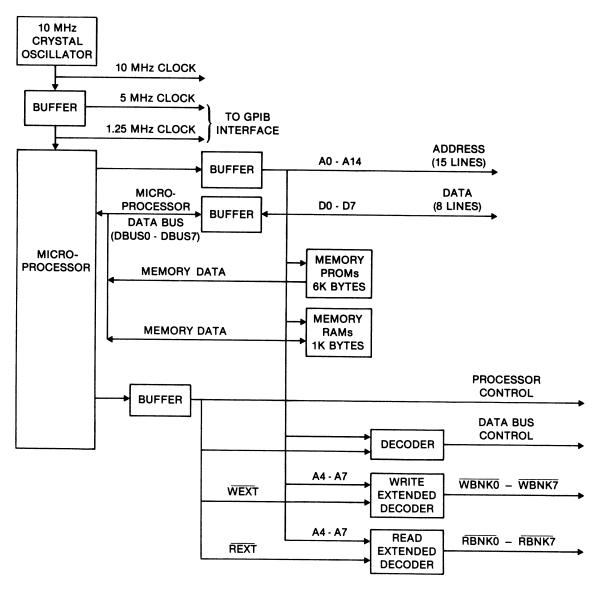

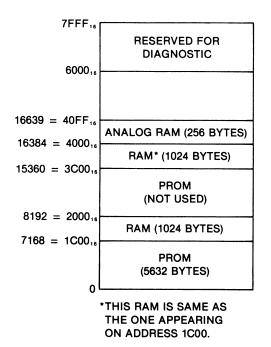

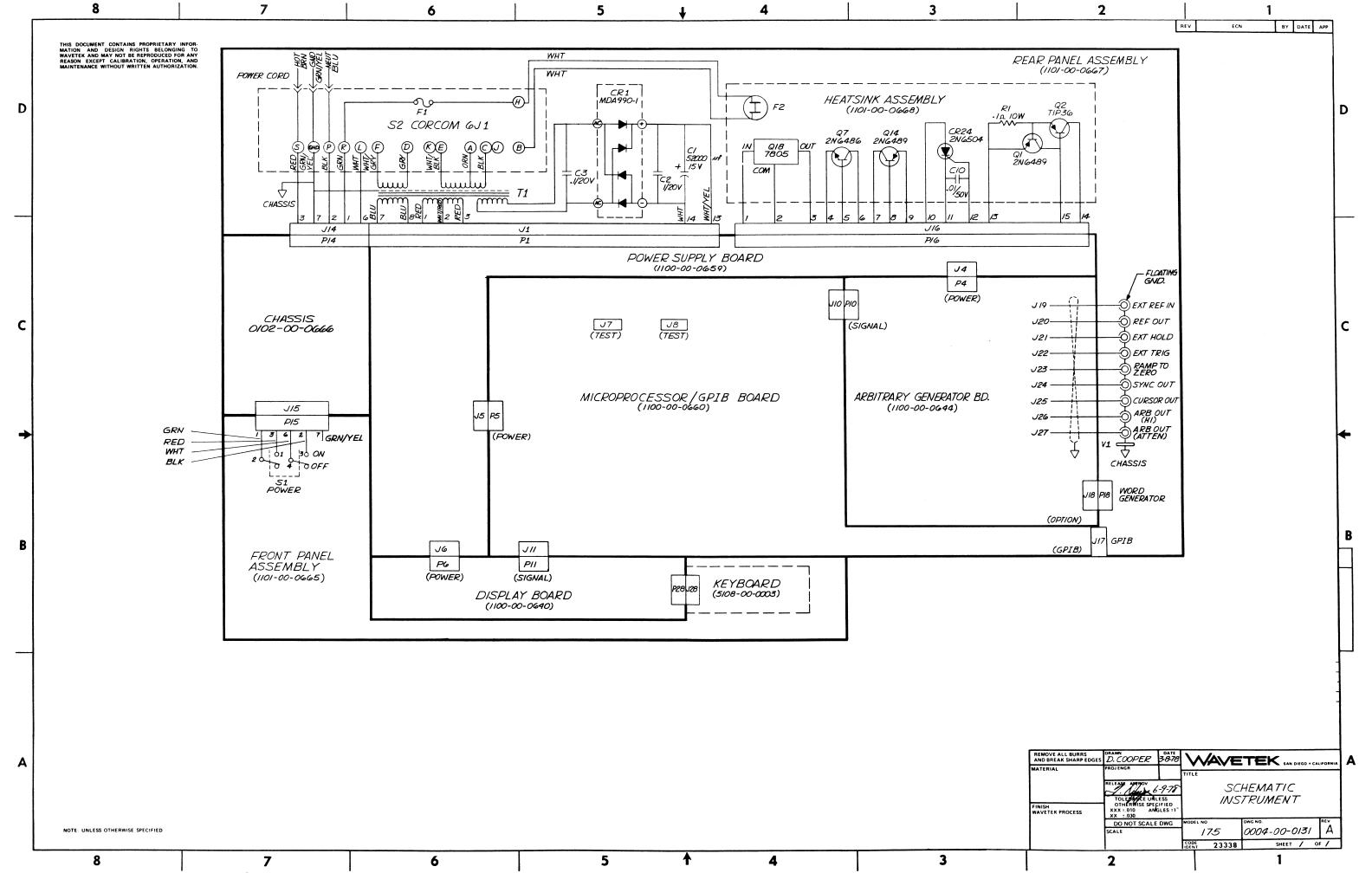

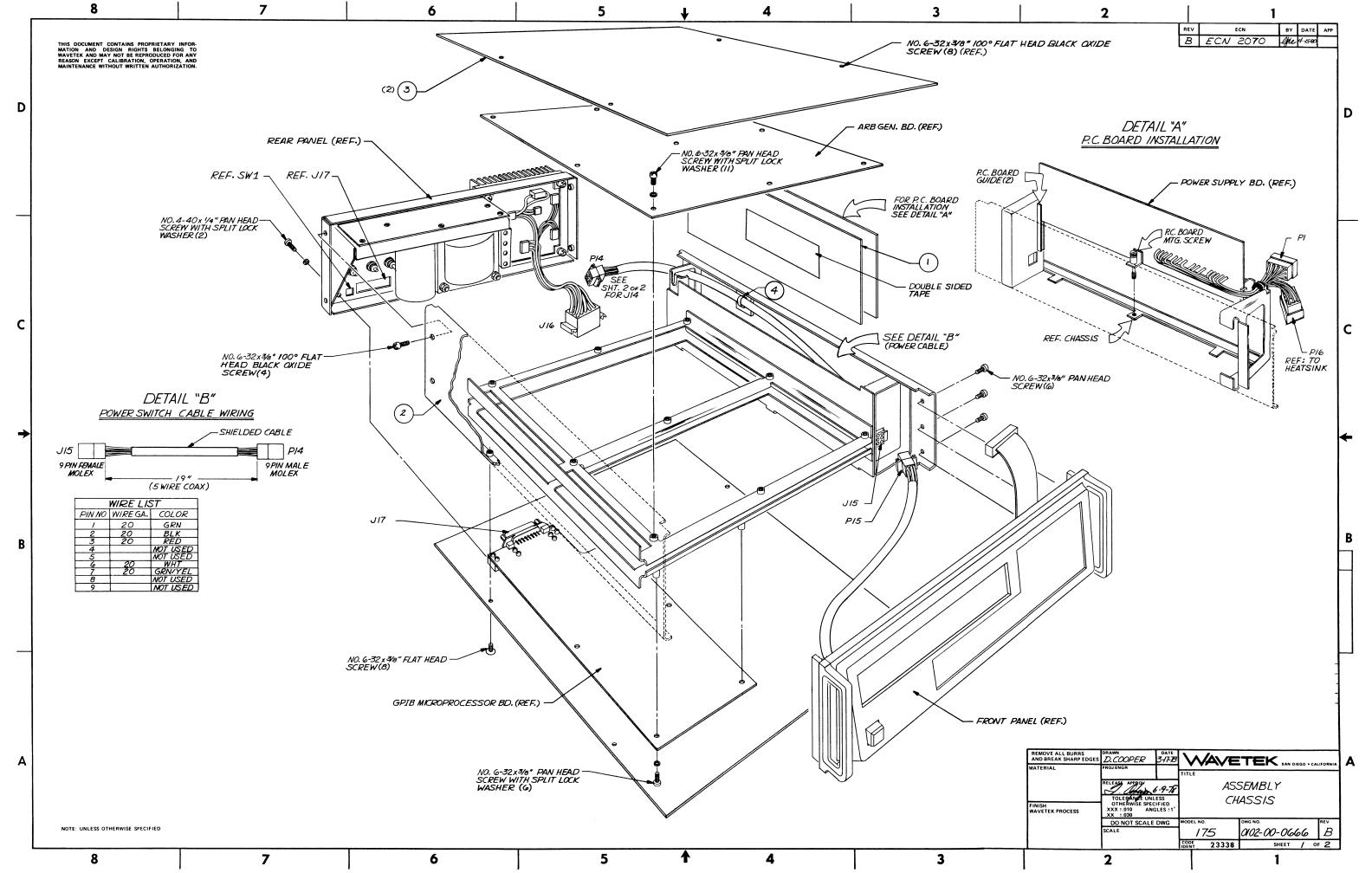

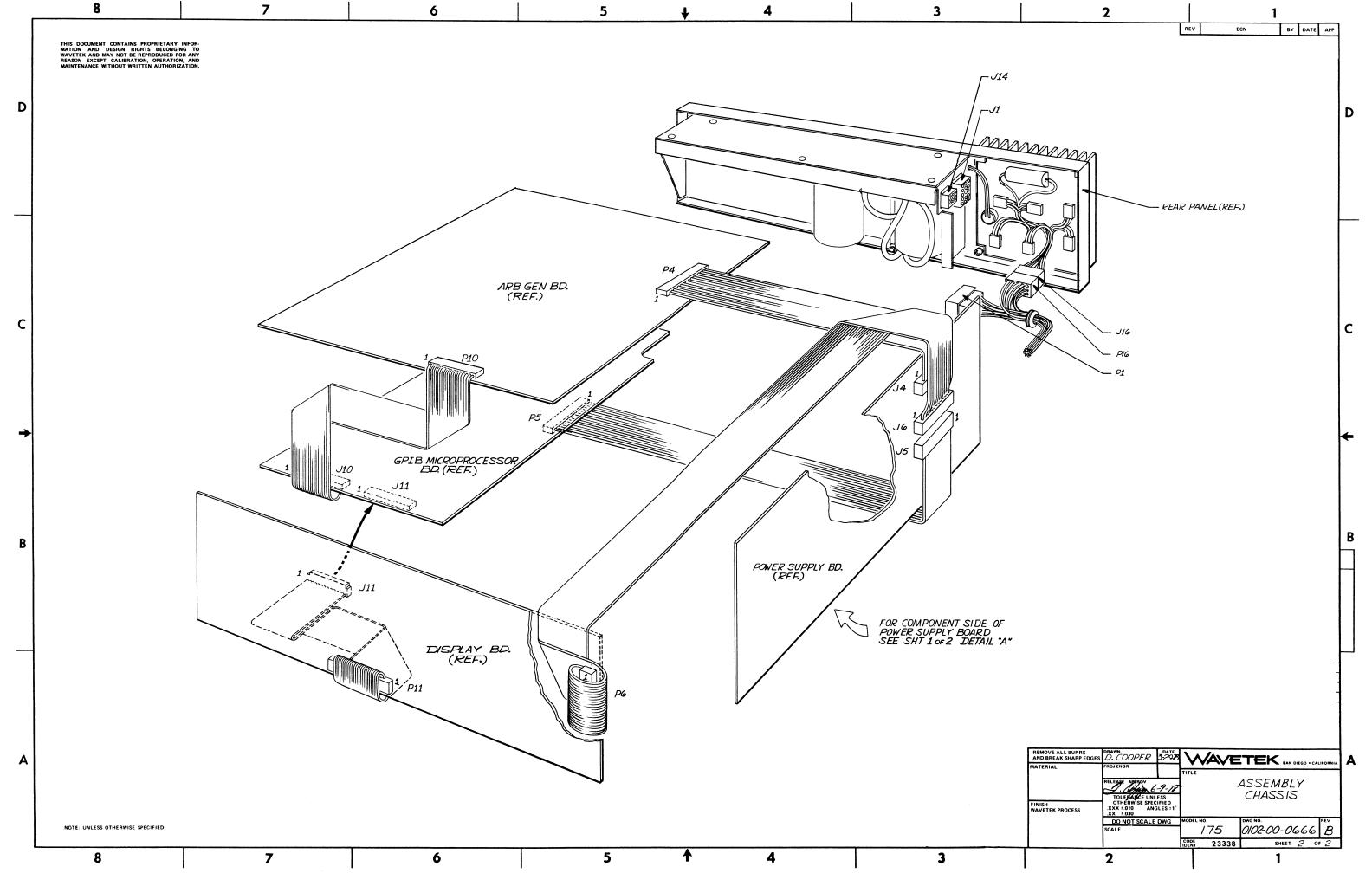

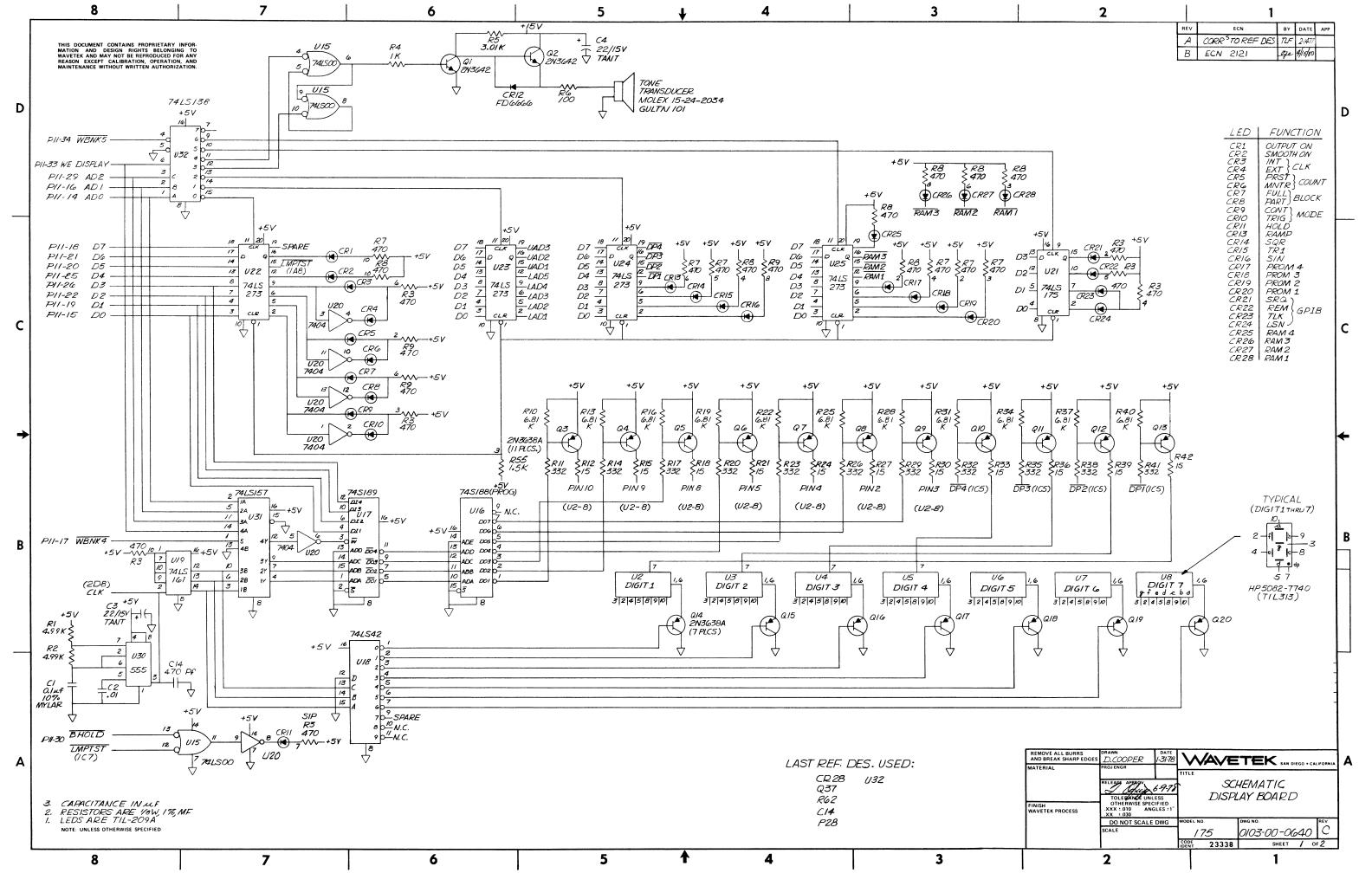

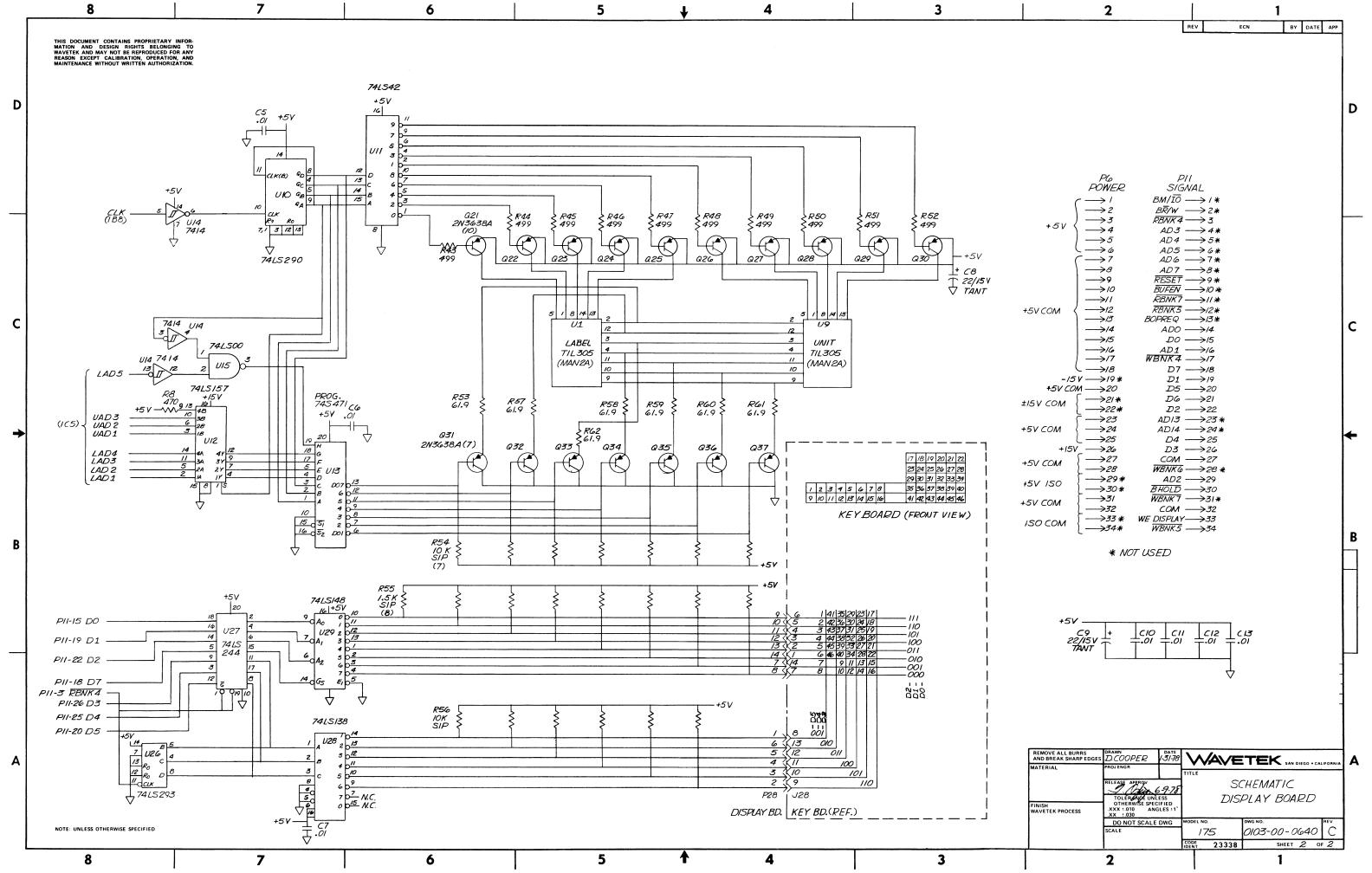

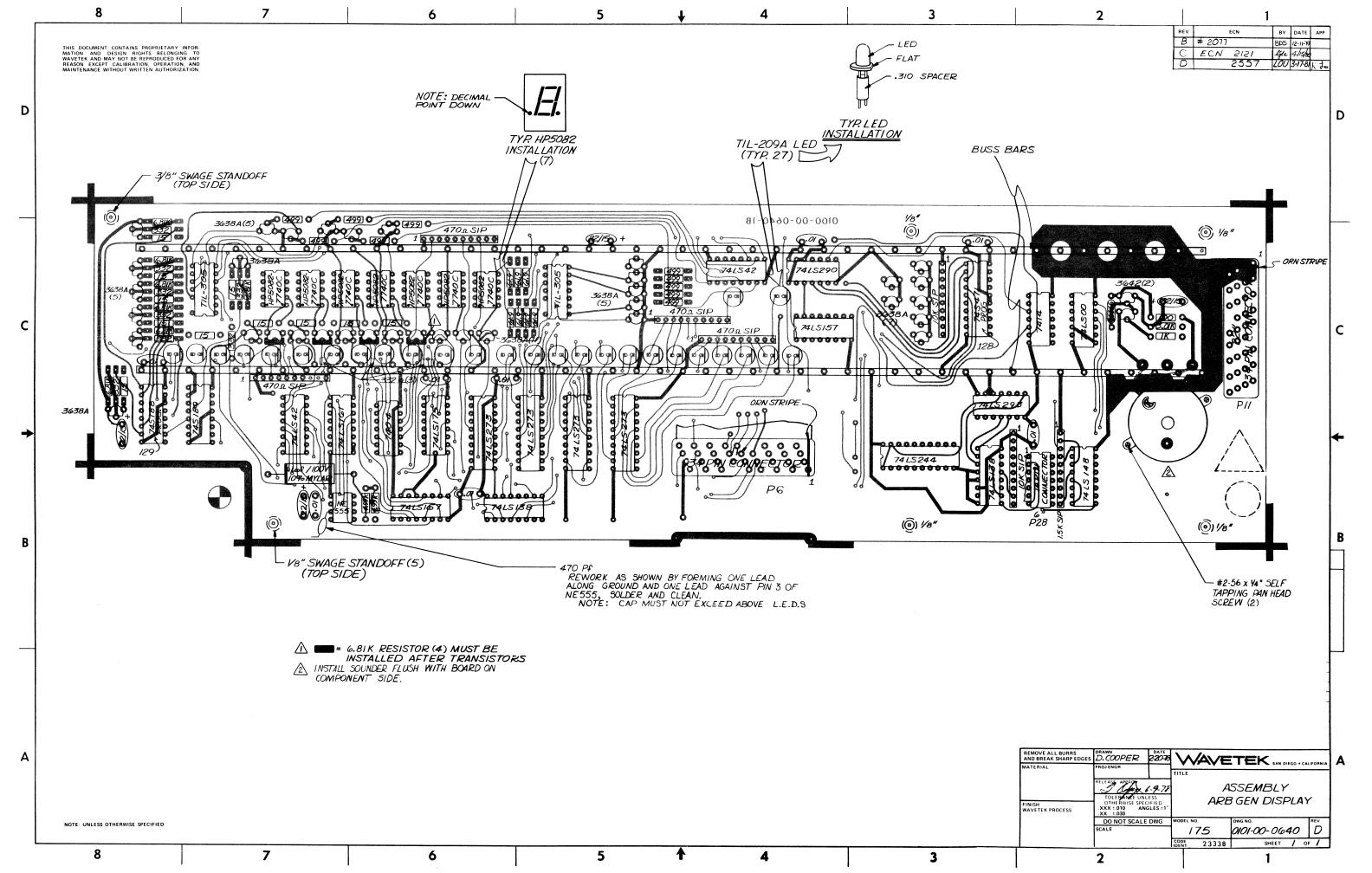

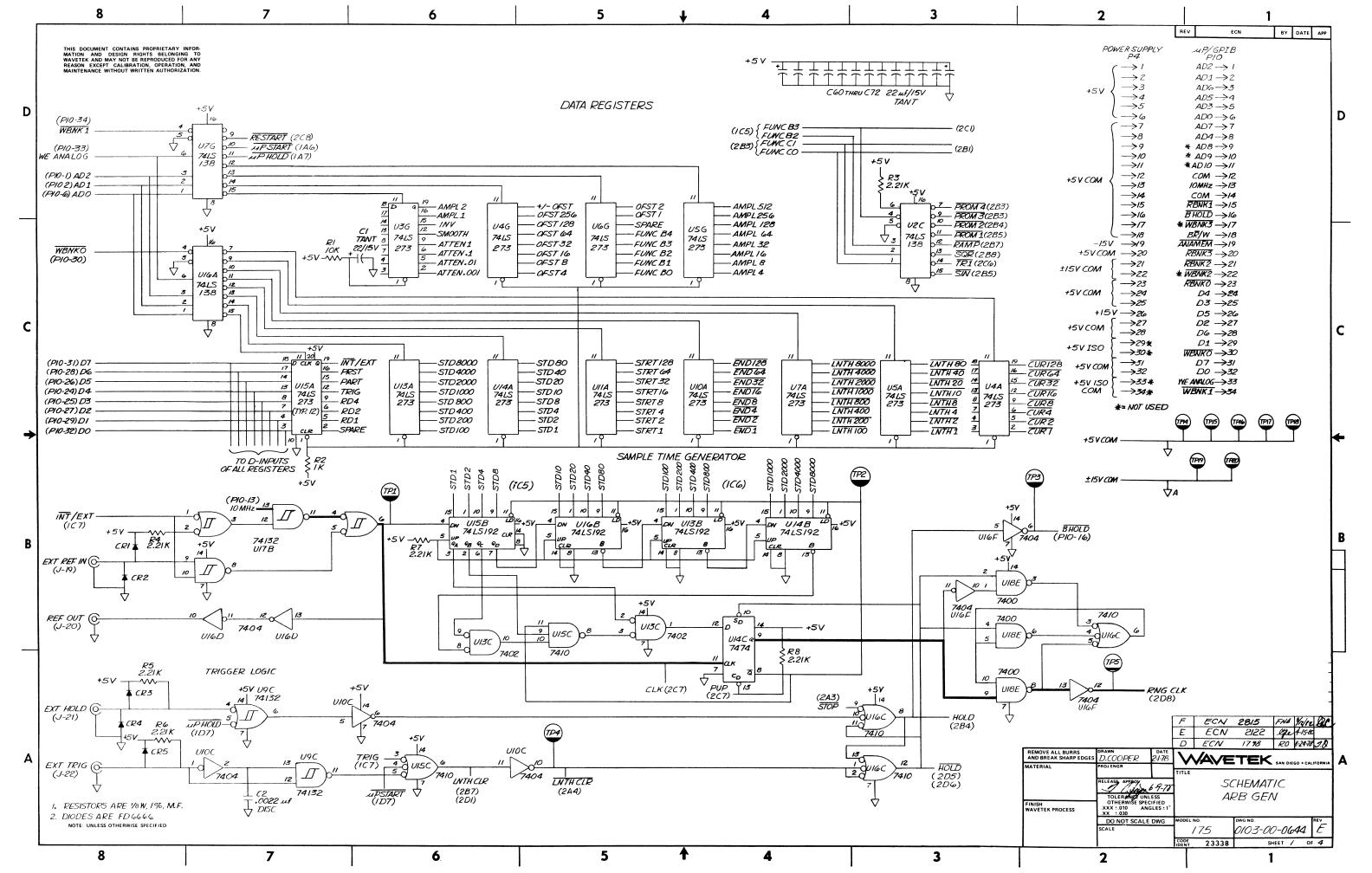

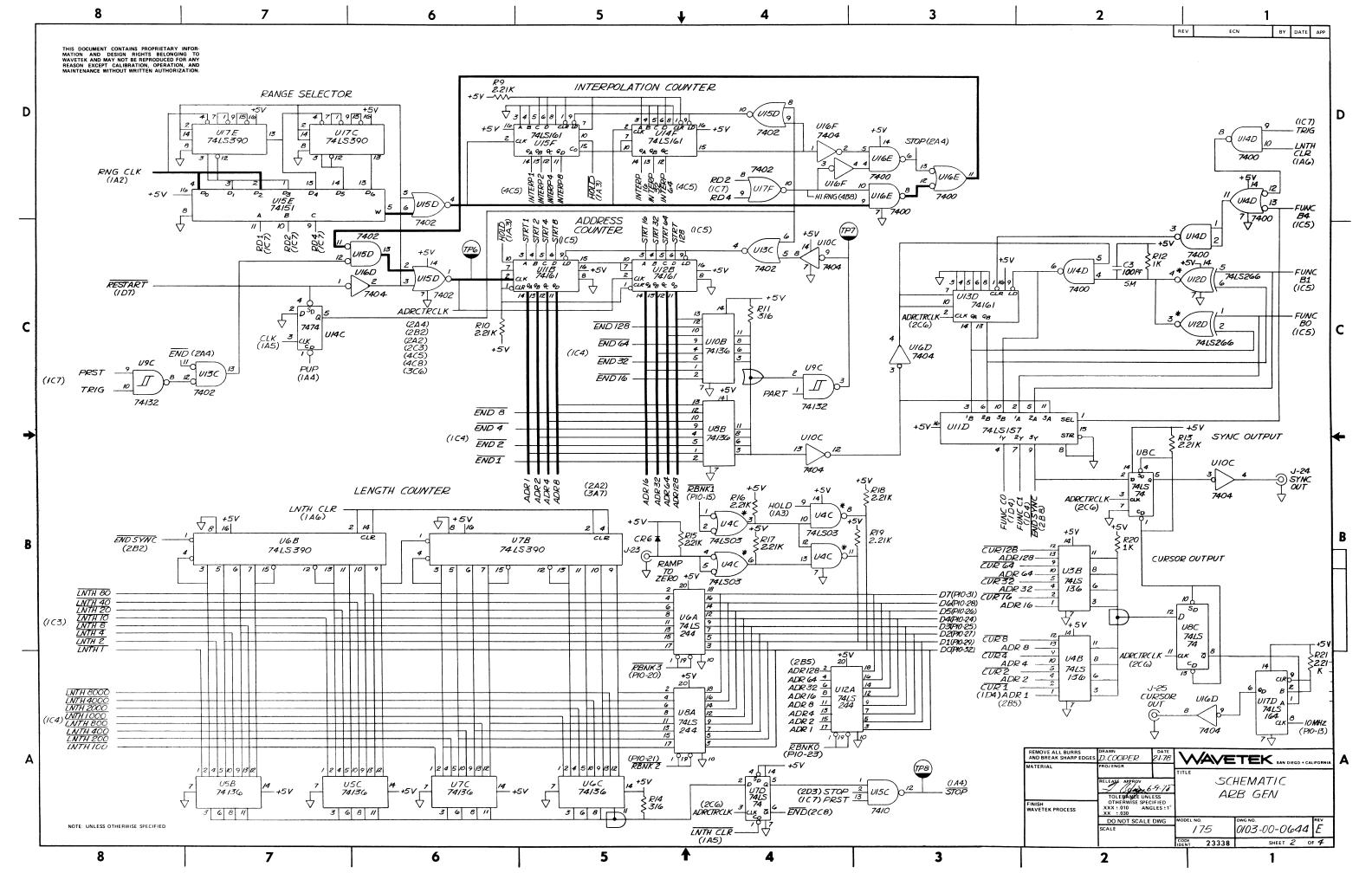

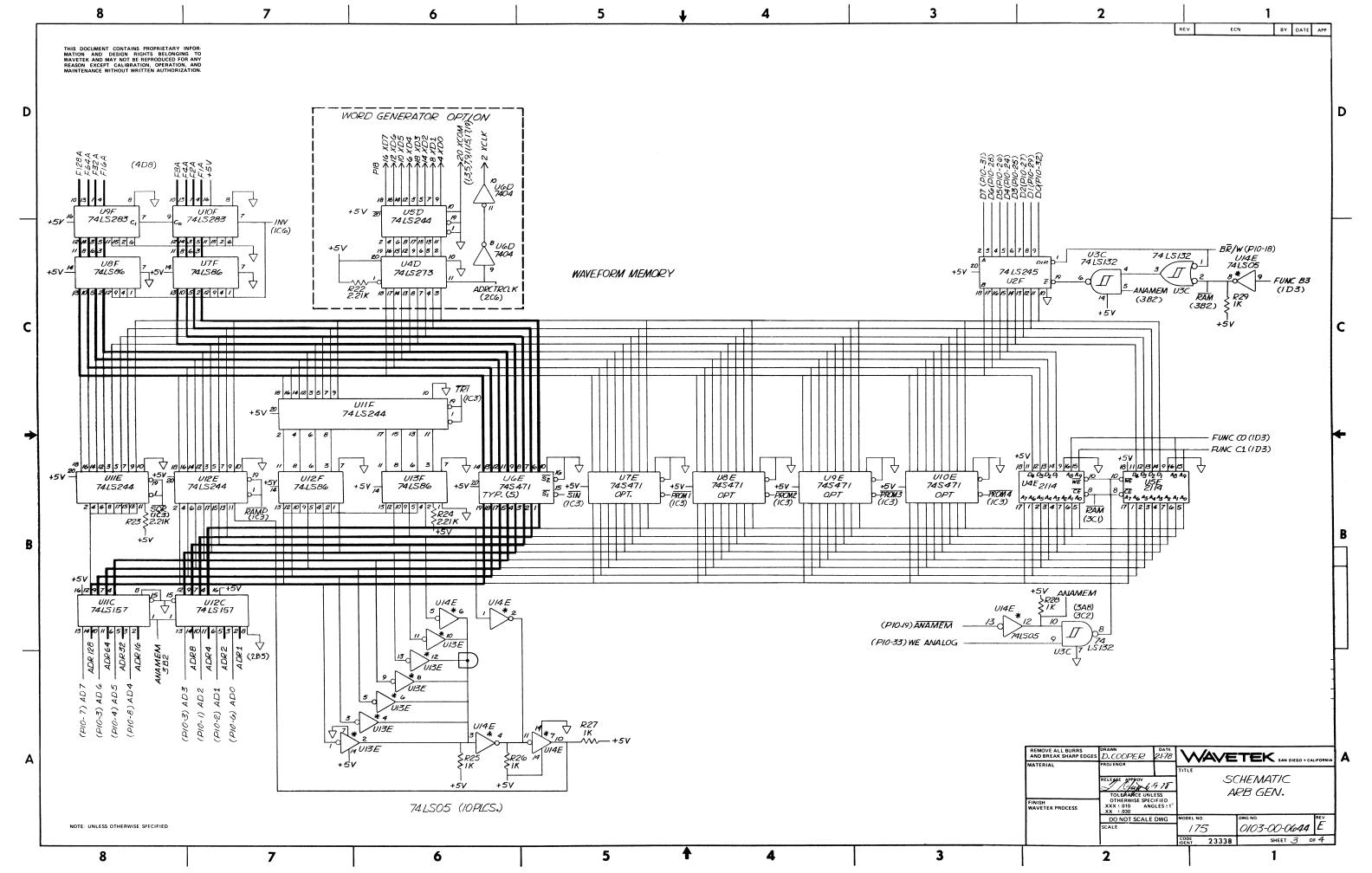

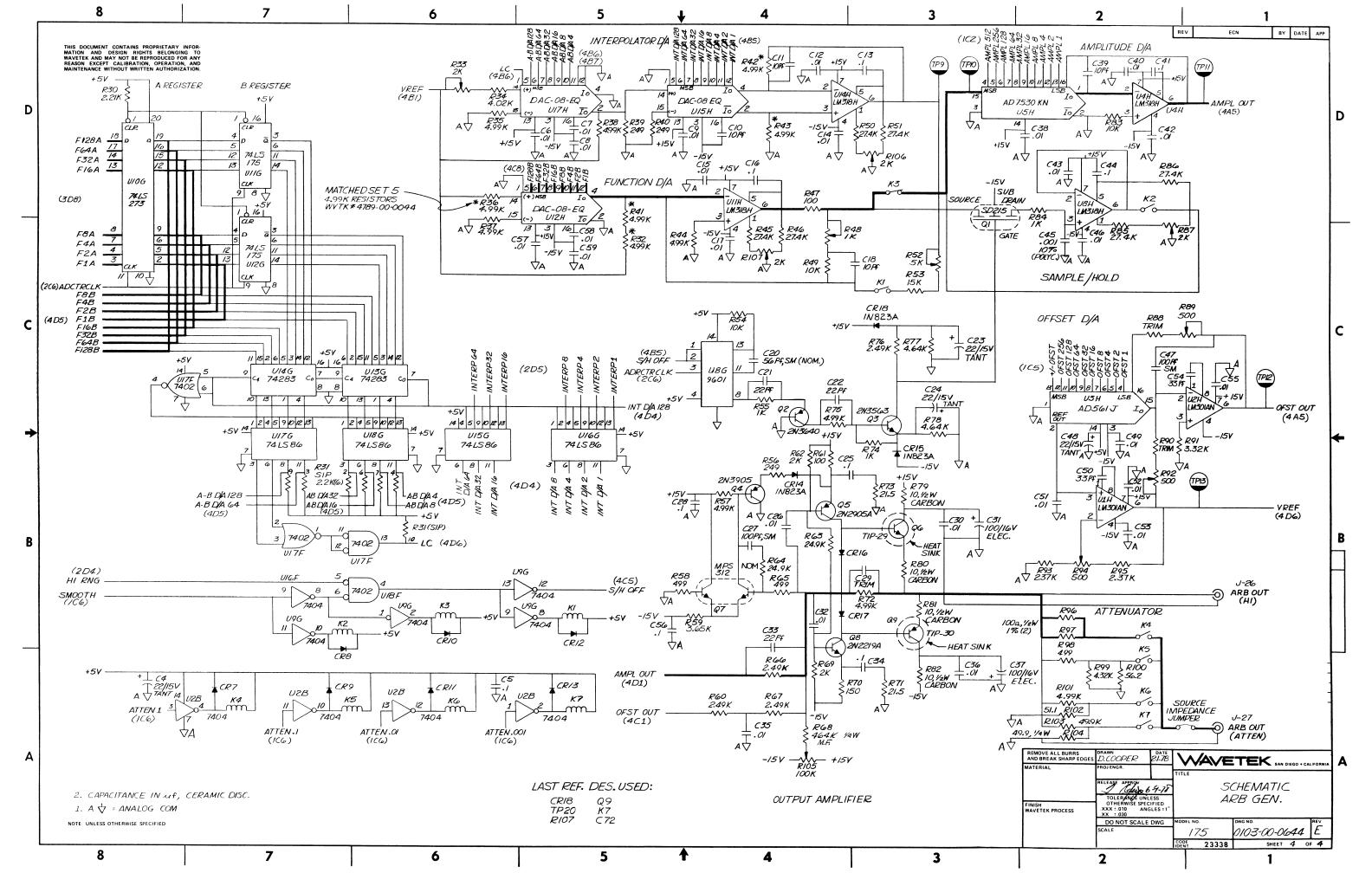

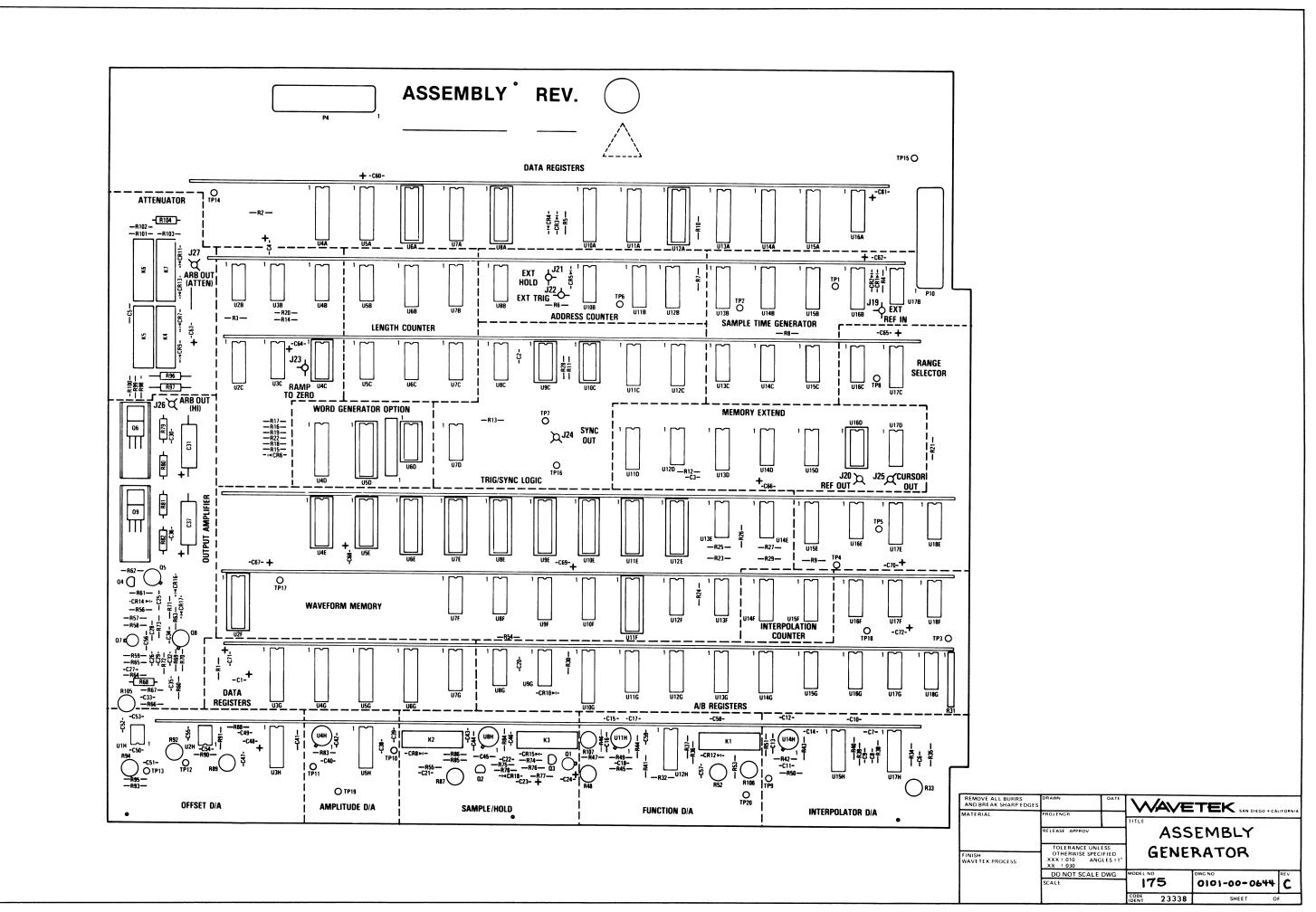

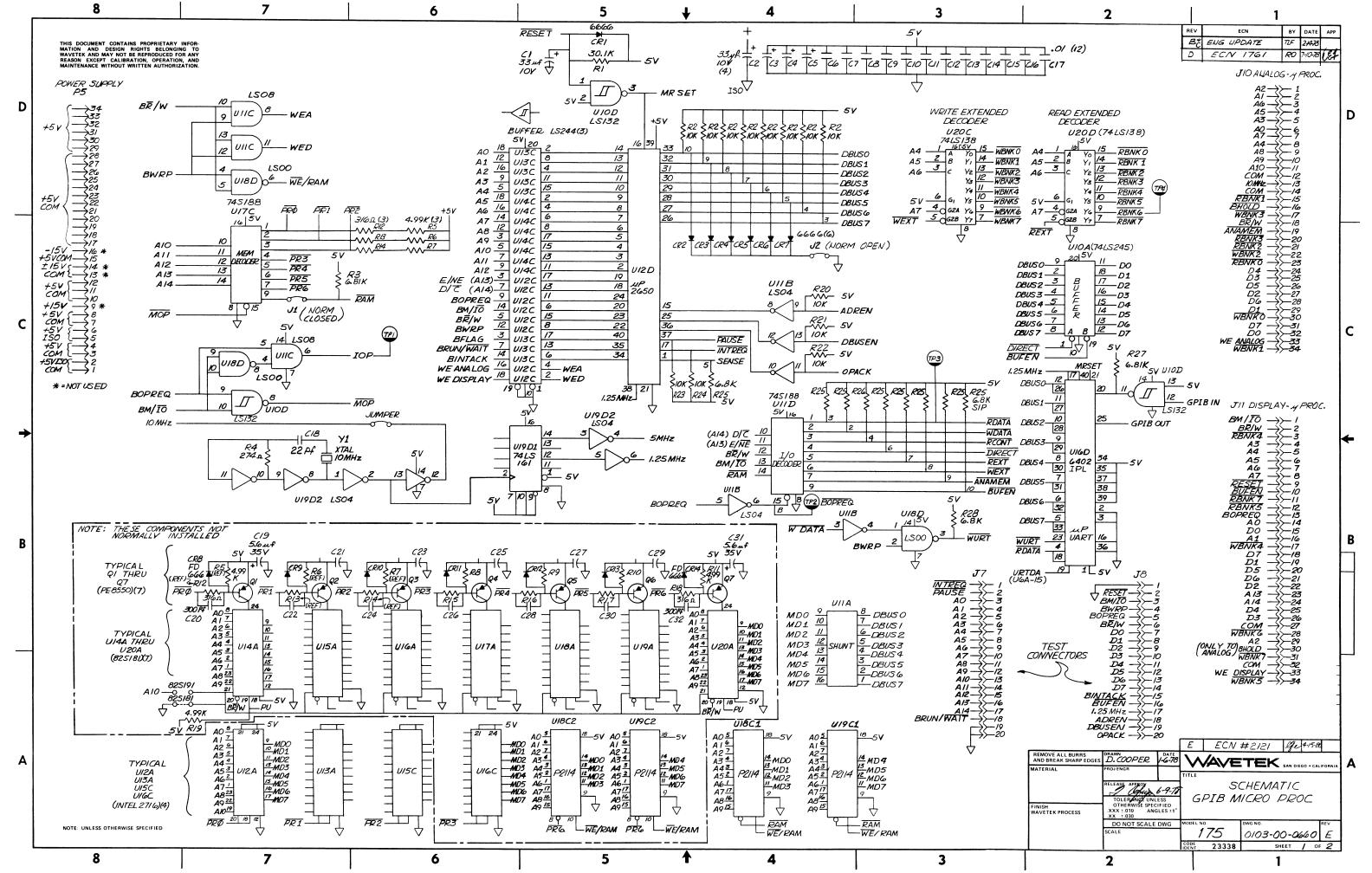

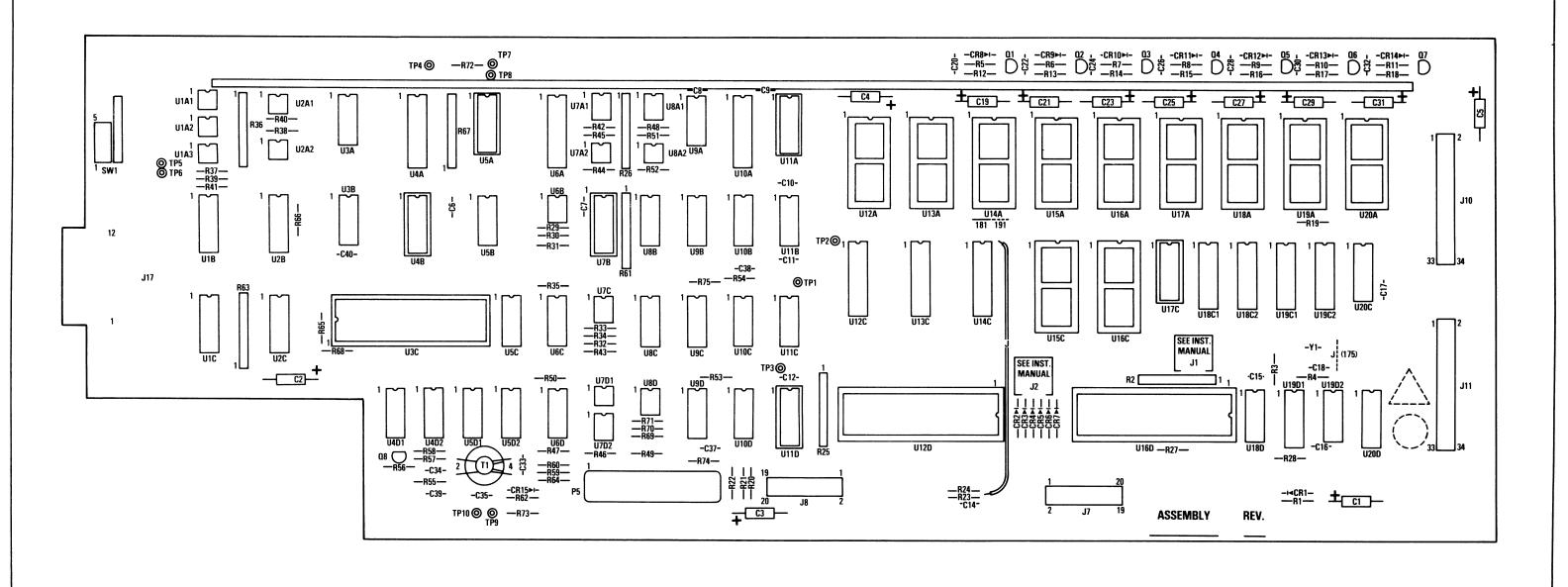

| SECTION 5 | CIRCUIT DESCRIPTION                                                                                                                                                                                                                                                                                       |                                                                                                    |  |  |  |  |

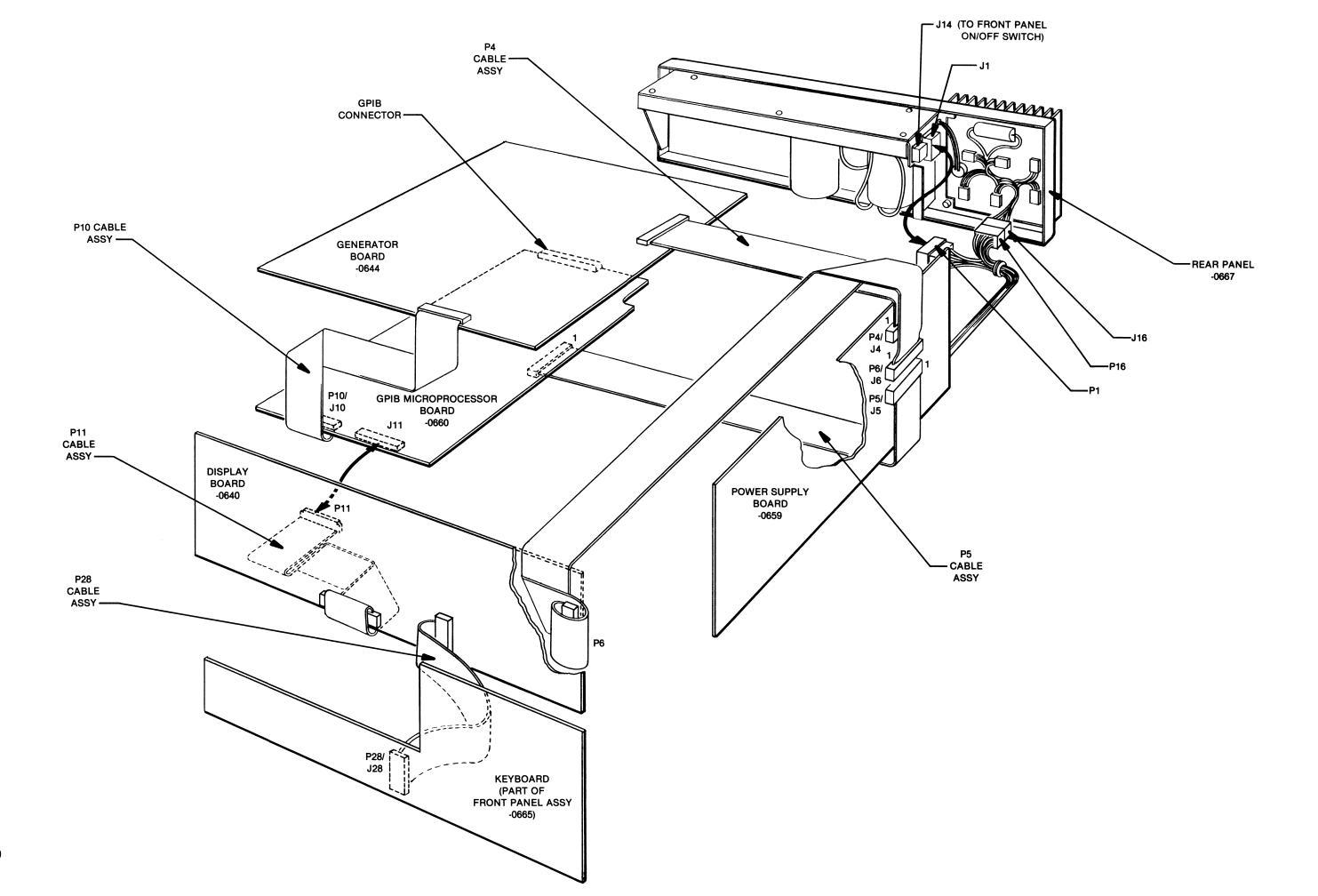

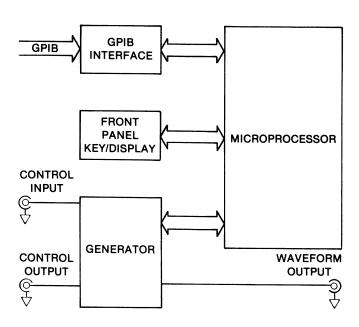

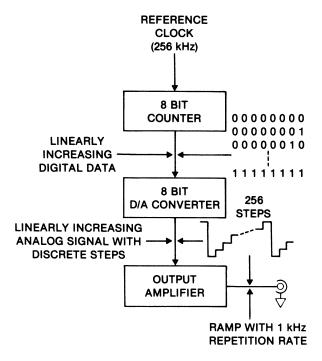

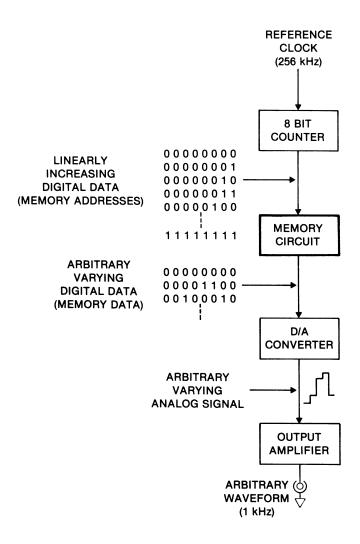

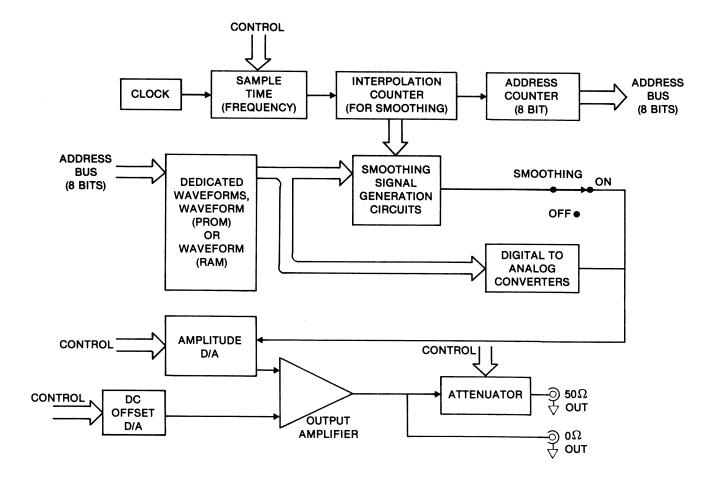

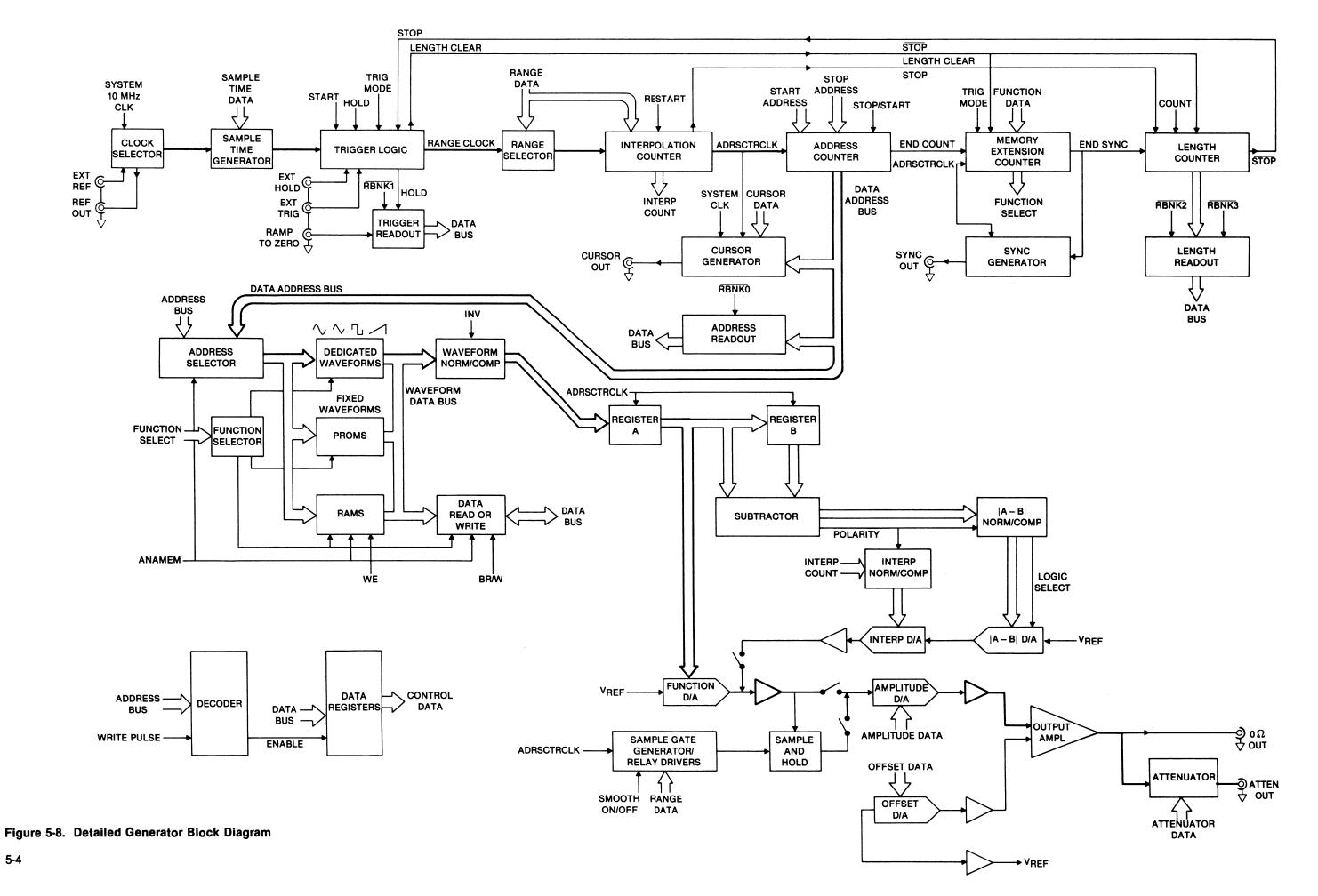

|           | 5.1 BOARD FUNCTIONS AND CONNECTIONS 5.2 GENERATOR 5.2.1 General 5.2.2 Generator Circuits 5.3 DISPLAY AND KEYBOARD 5.3.1 Display 5.3.2 Keyboard 5.4 MICROPROCESSOR 5.5 MICROPROCESSOR/GPIB INTERFACE 5.5.1 Data Ready 5.5.2 GPIB Busy 5.5.3 End 5.5.4 Remote 5.5.5 Talk 5.5.6 Listen 5.5.7 Service Request | 5-1<br>5-3<br>5-15<br>5-15<br>5-17<br>5-17<br>5-23<br>5-23<br>5-23<br>5-23<br>5-23<br>5-23<br>5-23 |  |  |  |  |

| SECTION 6 | TROUBLESHOOTING                                                                                                                                                                                                                                                                                           |                                                                                                    |  |  |  |  |

|           | 6.1 INTRODUCTION 6.2 POWER SUPPLY 6.3 FRONT PANEL DISPLAY 6.4 MICROPROCESSOR 6.5 GPIB INTERFACE 6.5.1 Test 1 — Bus Hung Up 6.5.2 Test 2 — Handshake 6.5.3 Test 3 — Listen Mode 6.5.4 Test 4 — Talk Address 6.5.5 Test 5 — Talk Mode 6.6 GENERATOR                                                         | 6-1<br>6-2<br>6-4<br>6-6<br>6-6<br>6-9<br>6-10<br>6-11                                             |  |  |  |  |

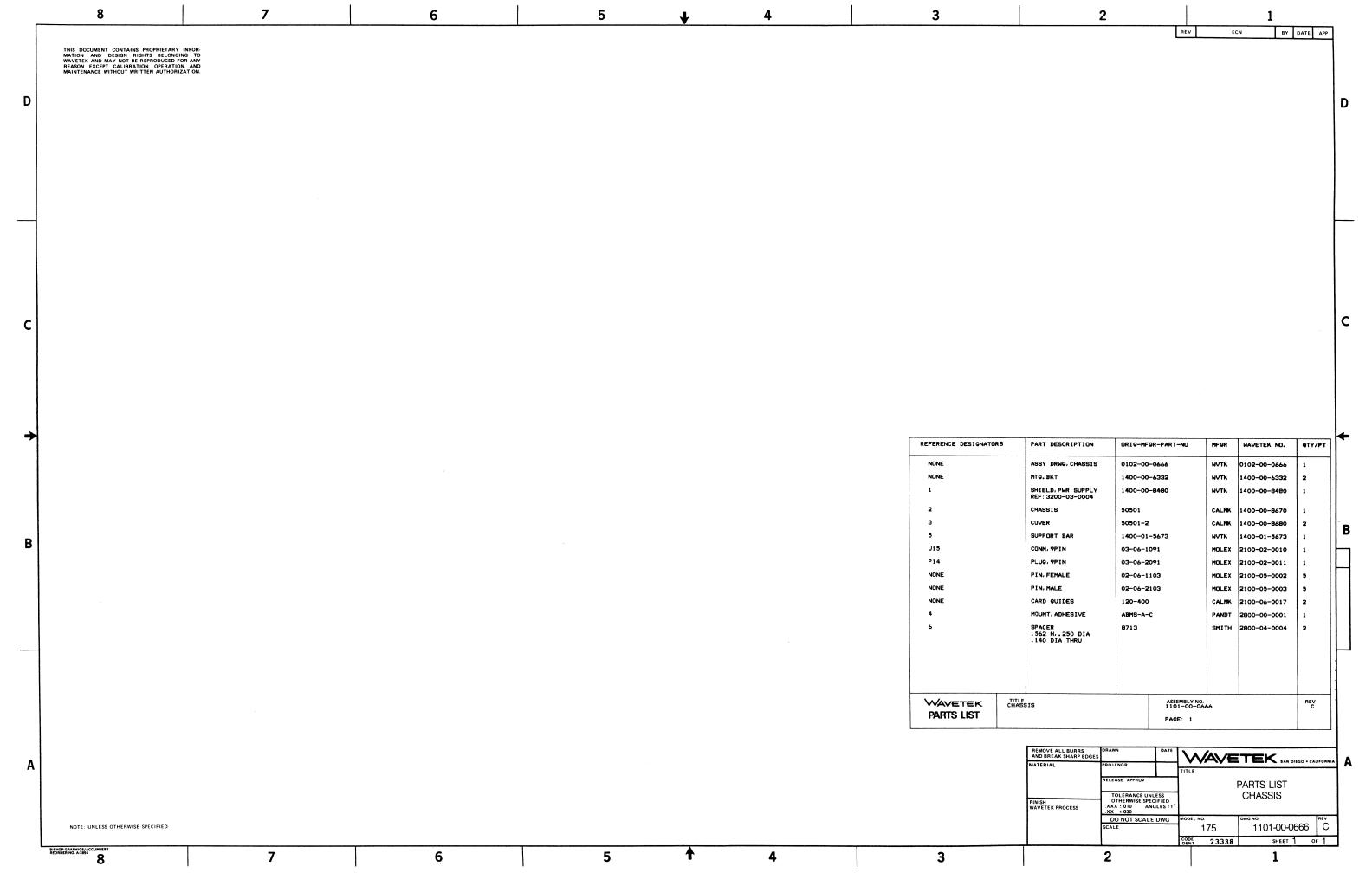

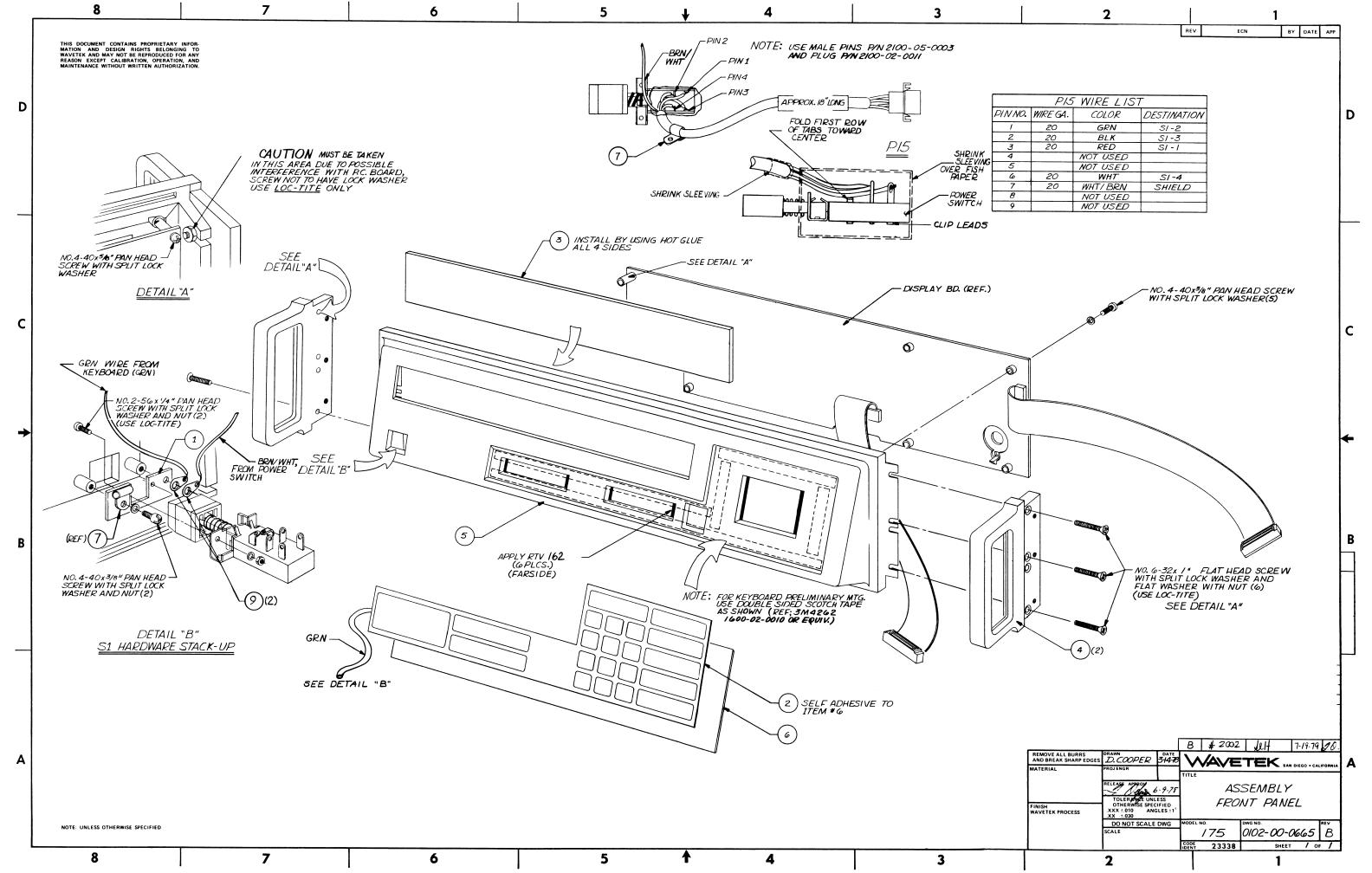

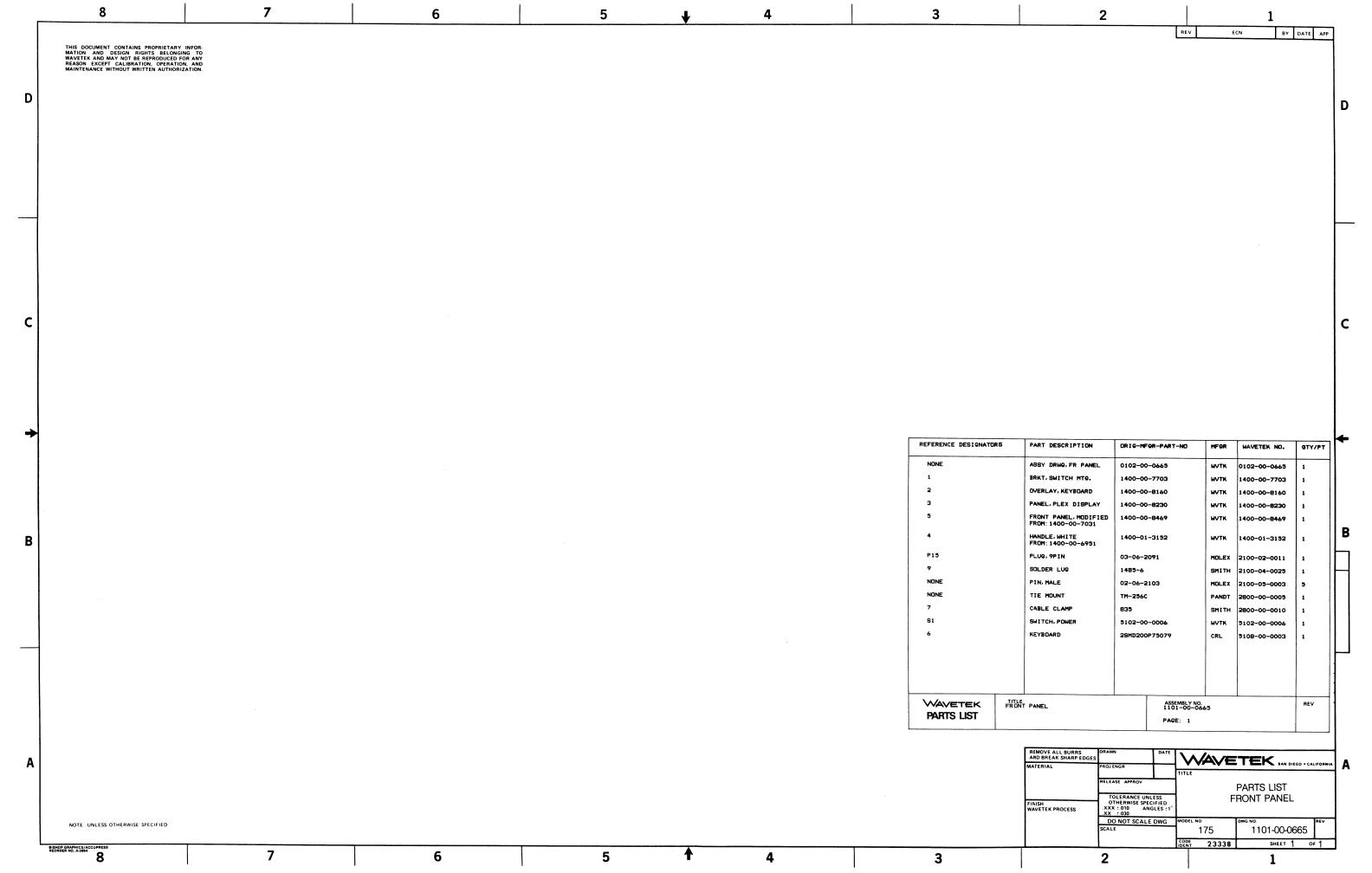

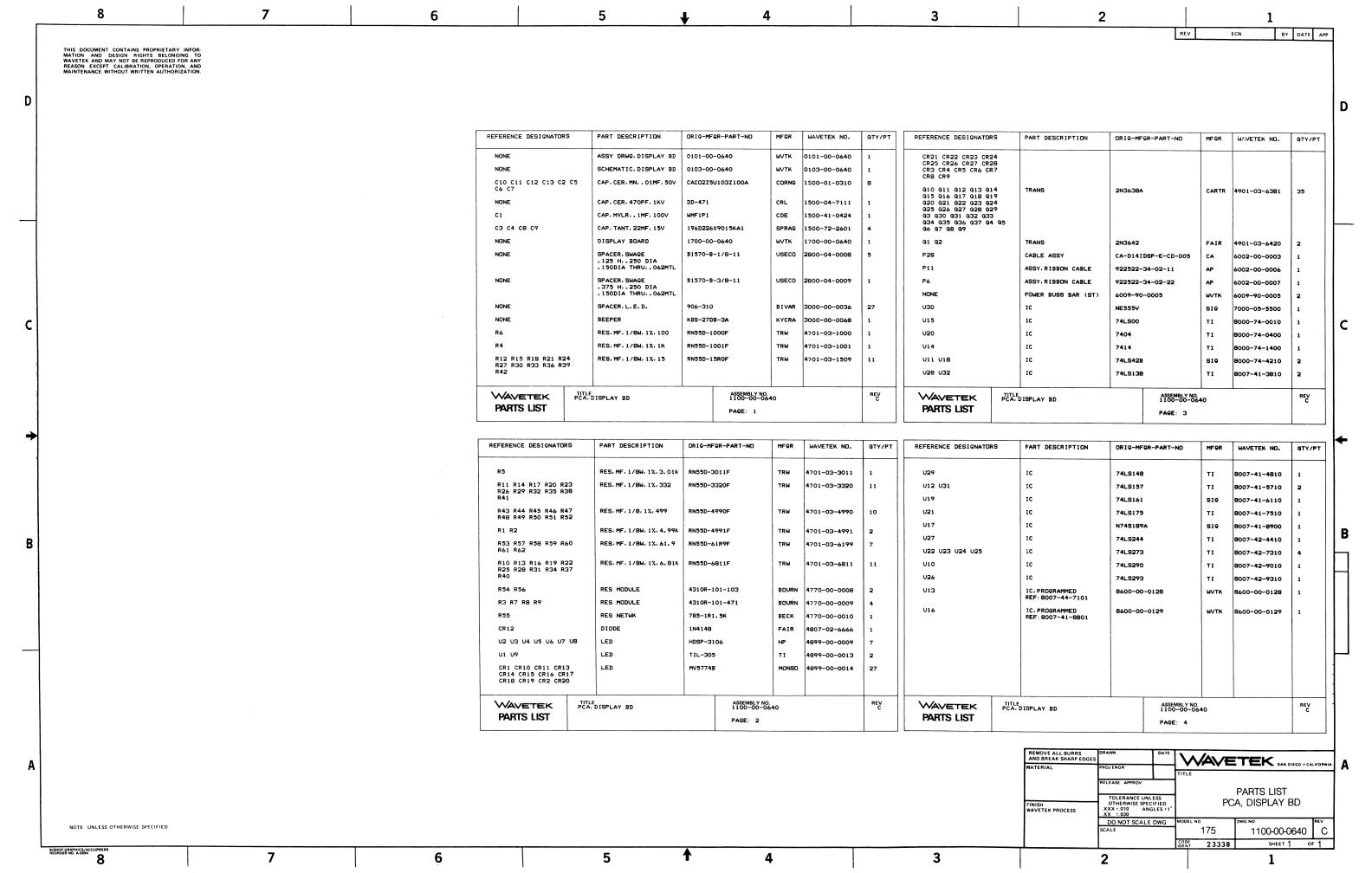

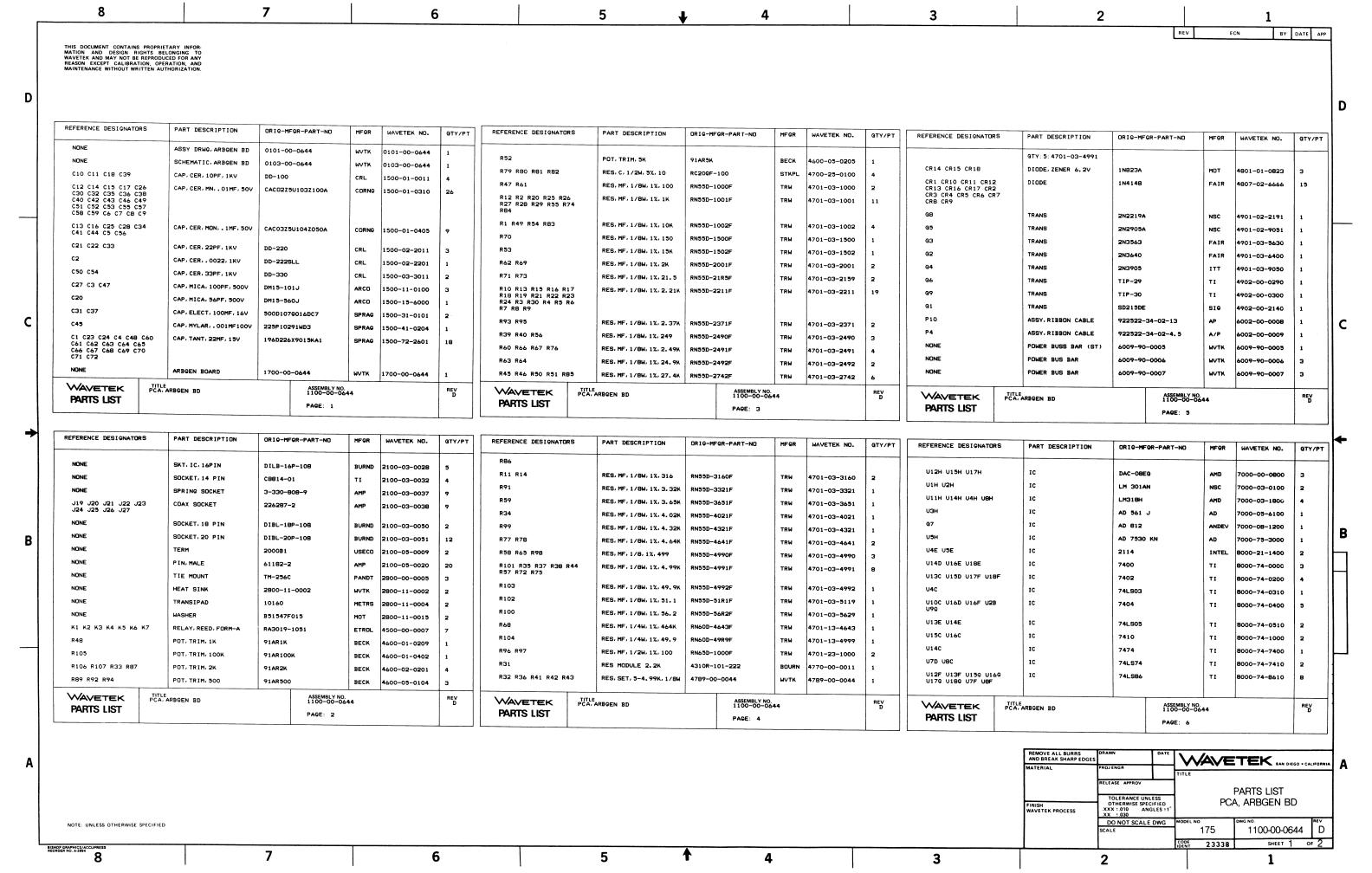

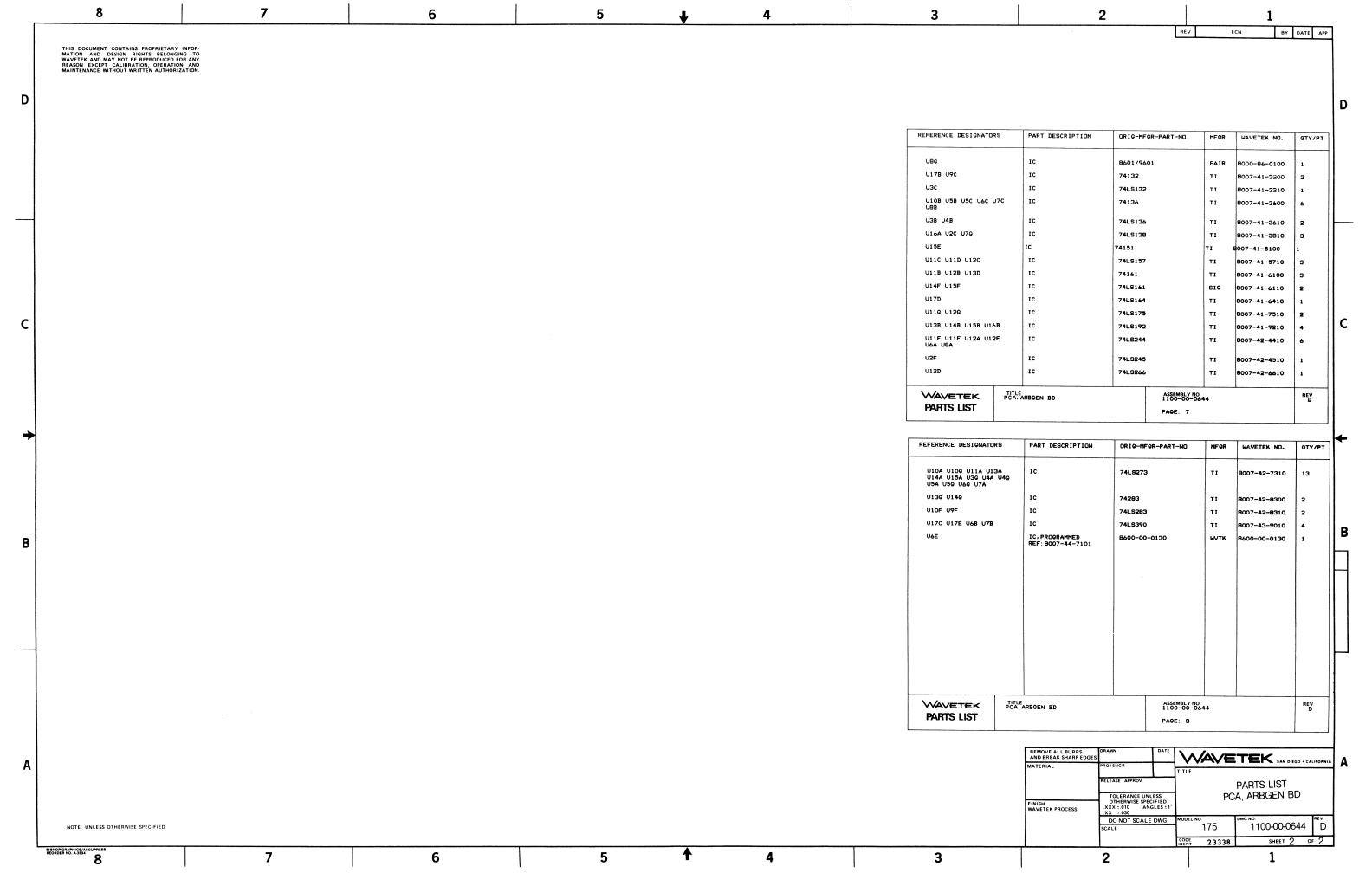

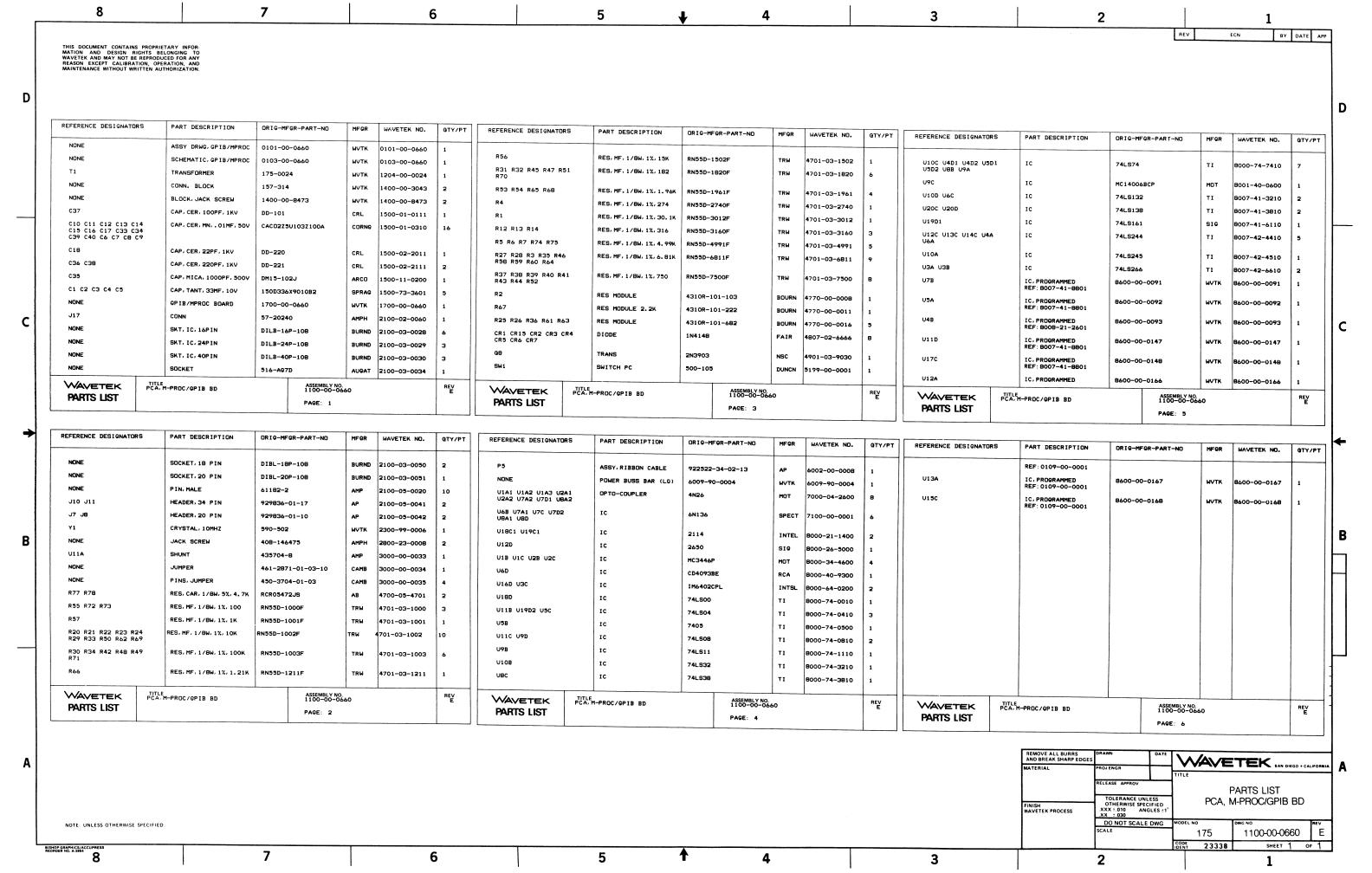

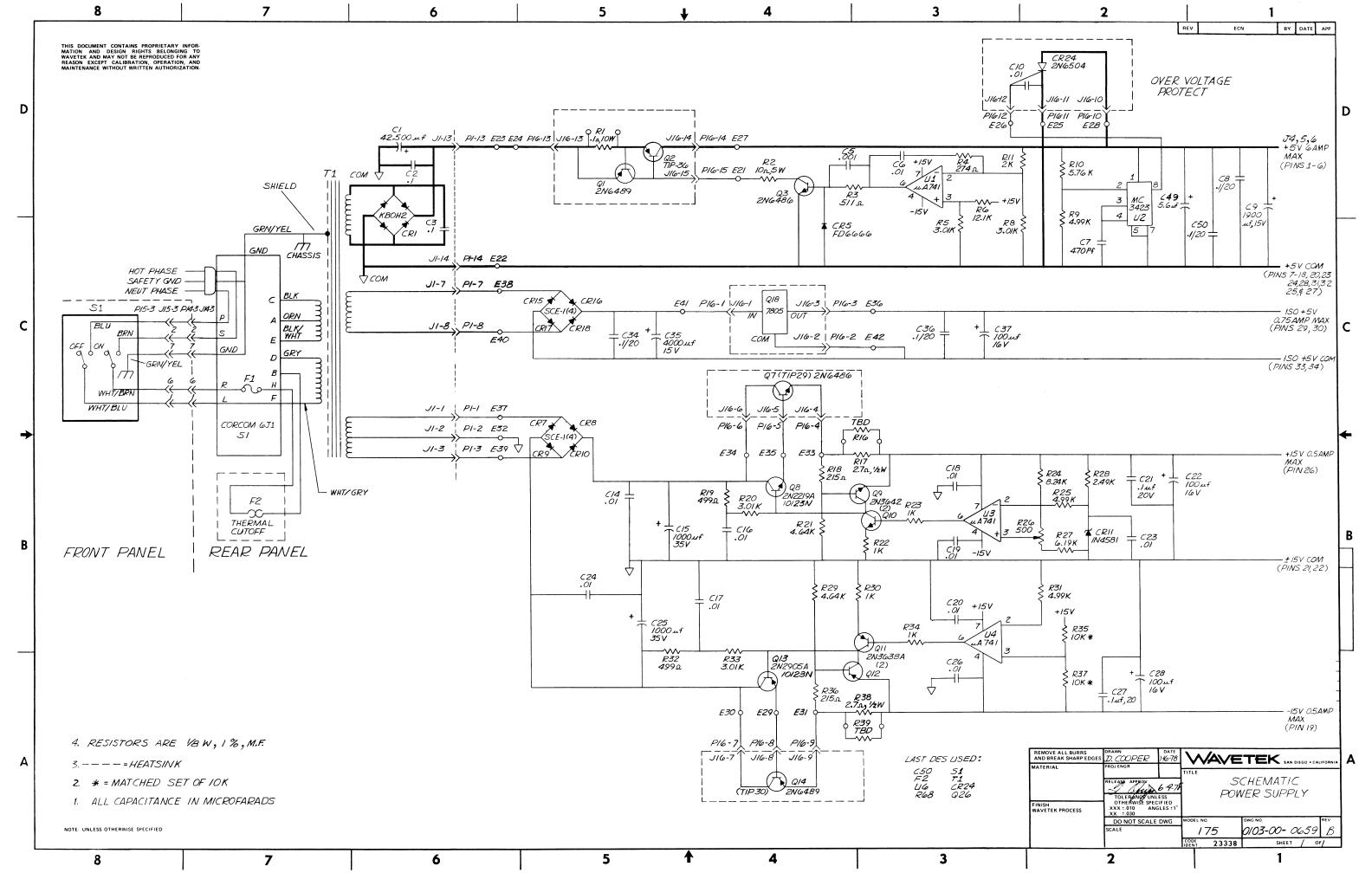

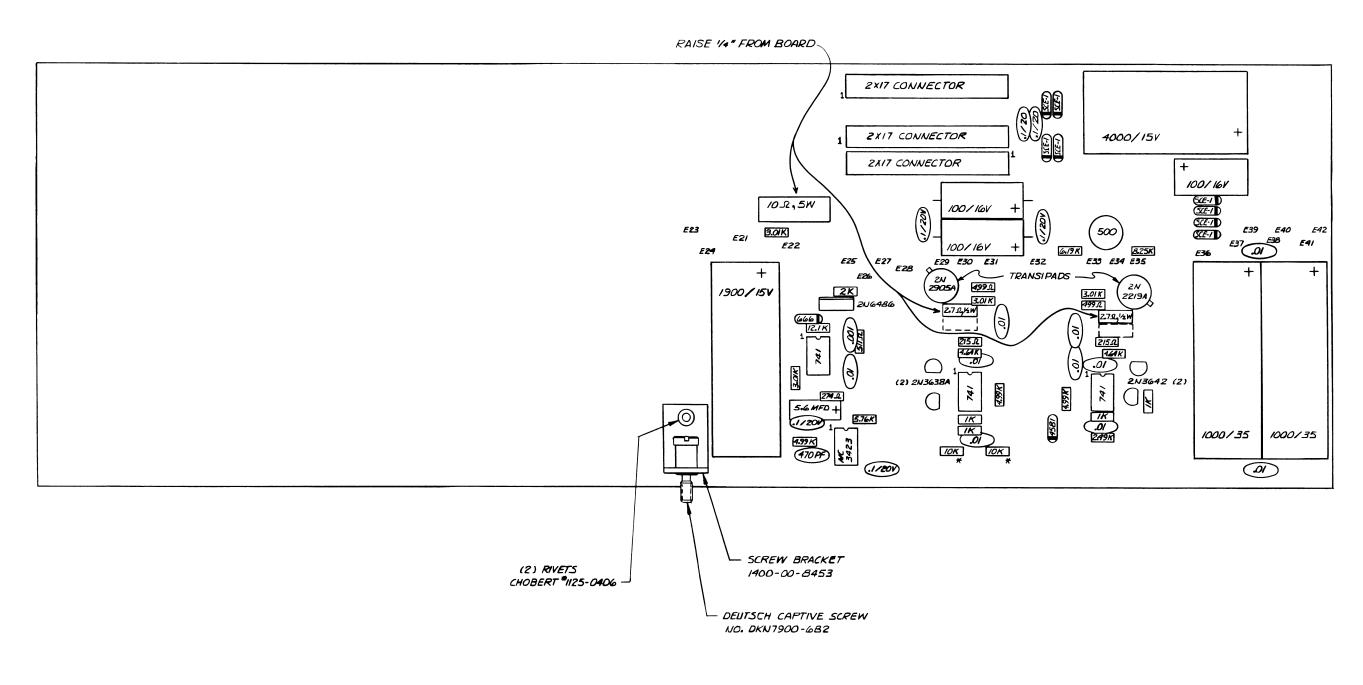

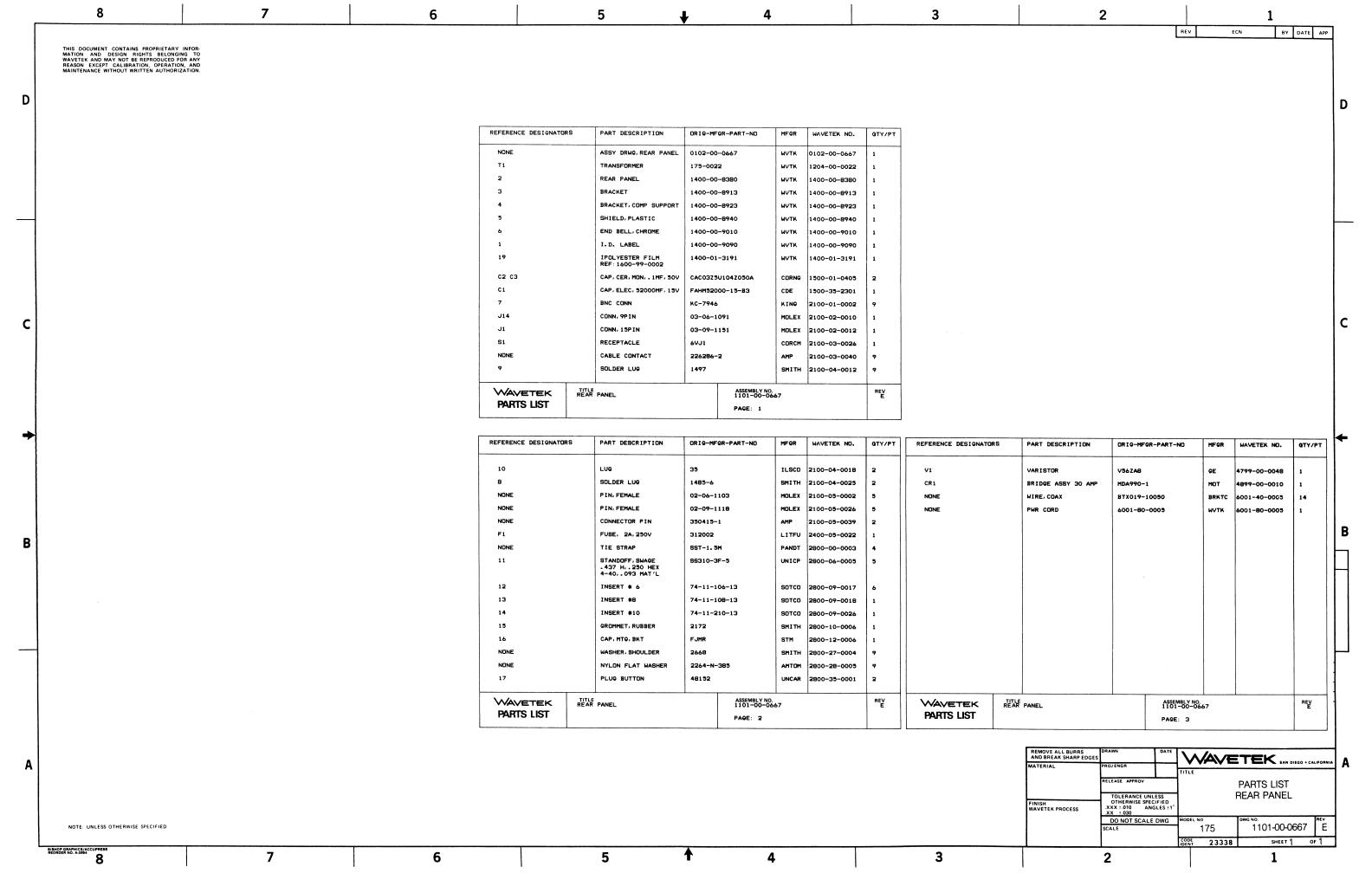

| SECTION 7 | PARTS AND SCHEMATICS                                                                                                                                                                                                                                                                                      |                                                                                                    |  |  |  |  |

| APPENDIX  | 7.1 DRAWINGS 7.2 ORDERING PARTS 7.3 ADDENDA                                                                                                                                                                                                                                                               | 7-1<br>7-1<br>7-1                                                                                  |  |  |  |  |

|           | APPENDIX A American Standard Code for                                                                                                                                                                                                                                                                     |                                                                                                    |  |  |  |  |

|           | Information Interchange (ASCII)  APPENDIX B Programming Examples  APPENDIX C Permanent Custom Waveforms                                                                                                                                                                                                   | B-1                                                                                                |  |  |  |  |

### **SAFETY**

This instrument is wired for earth grounding via the facility power wiring. Do not bypass earth grounding with two wire extension cords, plug adapters, etc.

BEFORE PLUGGING IN the instrument, comply with installation instructions.

MAINTENANCE may require power on with the instrument covers removed. This should be done only by qualified personnel aware of the electrical hazards.

The instrument power receptacle is connected to the instrument safety earth terminal with a green/yellow wire. Do not alter this connection. (Reference: or stamped inside the rear panel near the safety earth terminal.)

WARNING notes call attention to possible injury or death hazards in subsequent operations.

CAUTION notes call attention to possible equipment damage in subsequent operations.

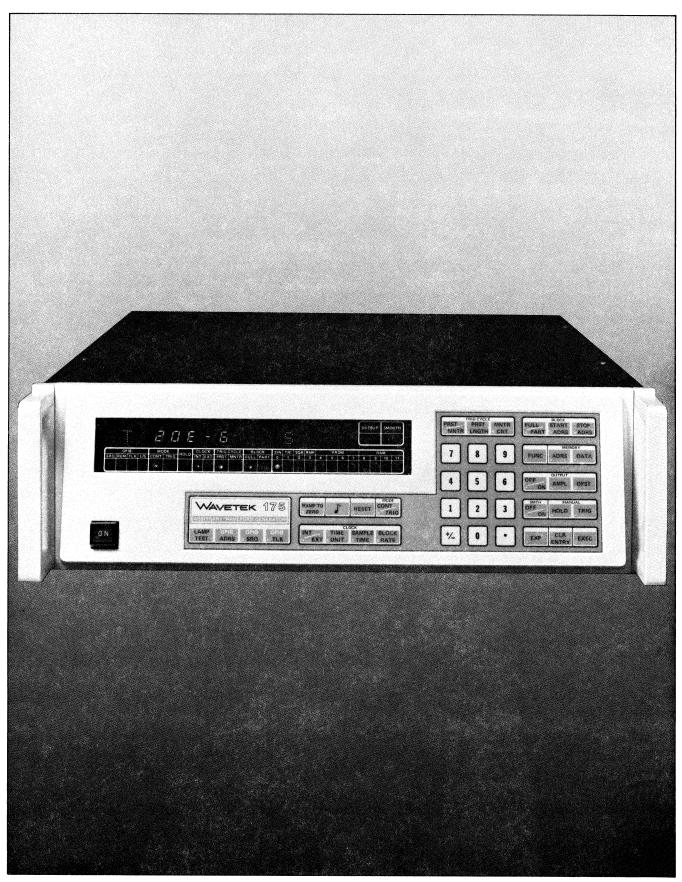

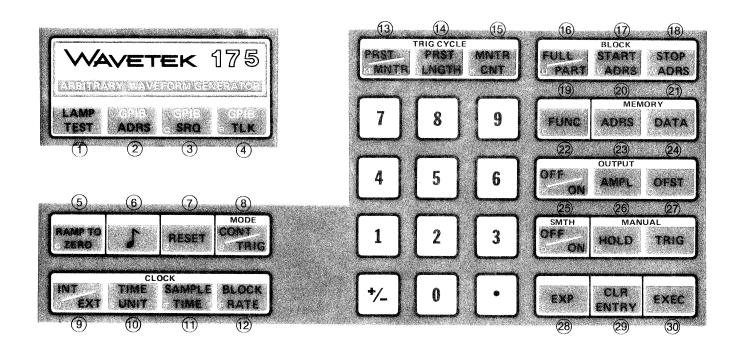

Figure i — Model 175 Arbitrary Waveform Generator

# SECTION GENERAL DESCRIPTION

### 1.1 THE MODEL 175

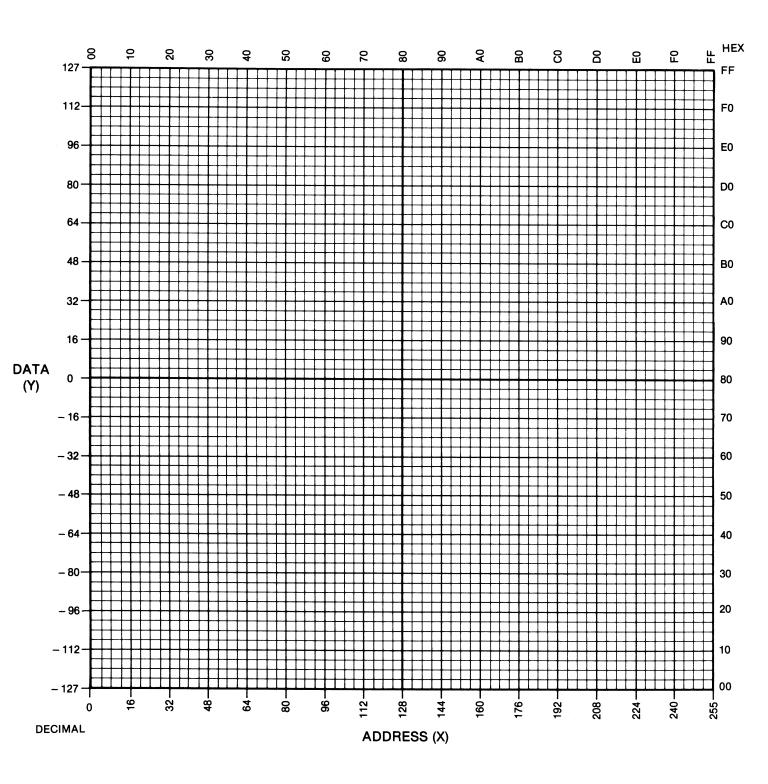

The Model 175, Arbitrary Waveform Generator (Arb), generates any waveform that can be expressed as a function of time. The working Random Access Memory (RAM) has four sets of 256 addresses and each address accepts an 8 bit word. This corresponds to a 1024 (time) by 255 (amplitude) matrix in which to draw waveforms. These storage addresses can be manually loaded by front panel controls or remotely loaded via the GPIB interface. The stored waveform, or any portion thereof, then can be generated at selectable clock rates and amplitudes.

In addition to the four working Random Access Memories (RAMs), four optional Programmable Read Only Memories (PROMs) allow the same capacity for permanent waveform storage. Sine, triangle, square and ramp waveforms are always available.

Operation can be continuous or triggered. Triggering can be for a preset number of cycles or the number of cycles triggered can be monitored and displayed. Start and stop addresses are selectable for partial waveform output. At low frequencies, point-to-point smoothing can be selected to minimize digital step size. Output may be held at any level, or amplitude and offset can be slowly ramped to zero when a ramp to zero command is given.

Front panel operation is by keyboard and display which gives immediate verification of parameter and value in memory.

The Model 175 is fully compatible with the requirements of IEEE Standard 488-1975 for integration into a General Purpose Interface Bus (GPIB).

### 1.2 SPECIFICATIONS

### 1.2.1 Versatility

### 1.2.1.1 Waveforms

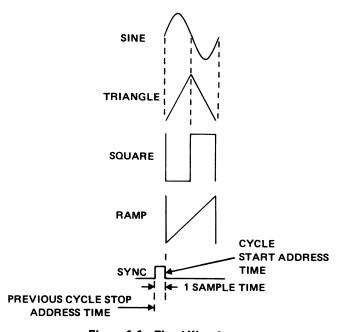

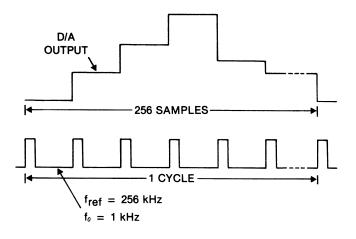

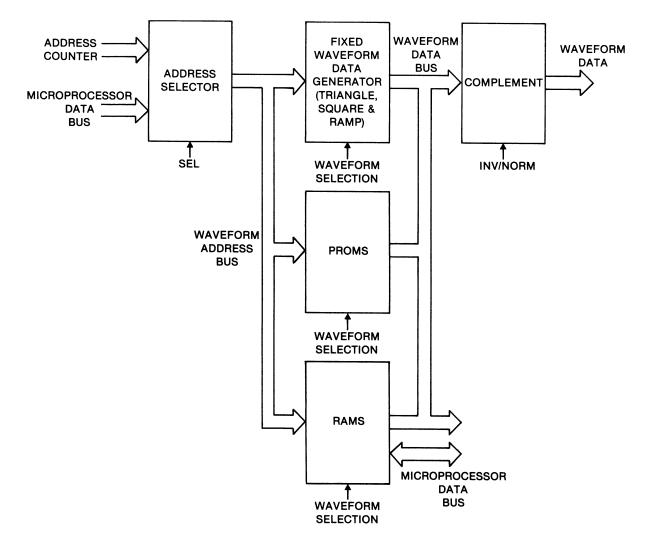

Sine  $\bigcirc$  , square  $\square$  , triangle  $\bigcirc$  , ramp  $\bigcirc$  , arbitrary waveforms and TTL sync. (See figure 1-1.)

Figure 1-1. Fixed Waveforms

### 1.2.1.2 Arbitrary Waveforms

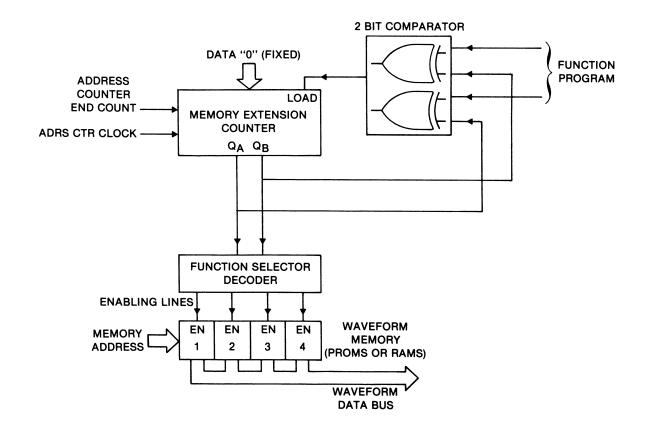

Arbitrary waveforms are stored on four 256 X 255 point RAM matrices and four 256 X 255 user-supplied PROM matrices. Each PROM or RAM block can be addressed individually or they can be addressed in sequence; e.g., PROMs 1 and 2, PROMs 1, 2 and 3 or PROMs 1, 2, 3 and 4. This feature allows additional address resolution of custom waveforms. Block length can be from 2 to 256 address points, or when blocks are stacked, up to 1024 address points.

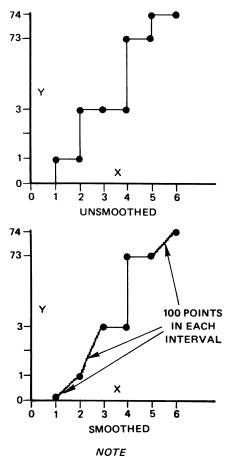

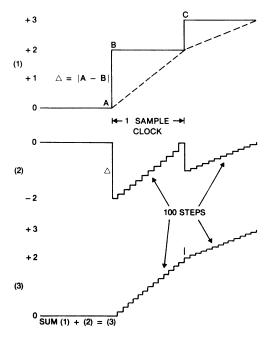

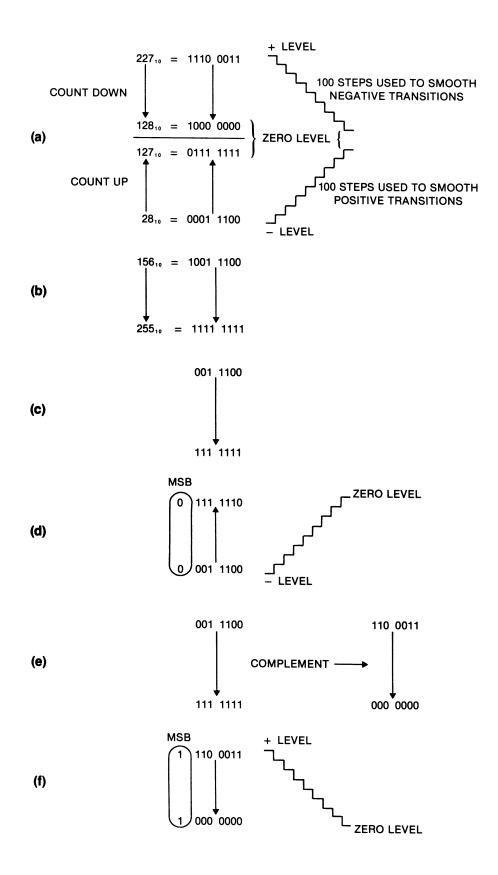

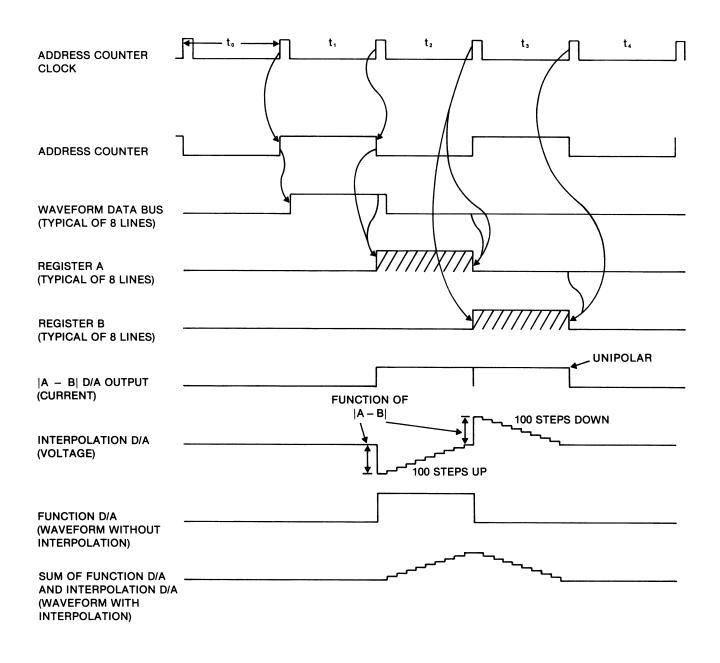

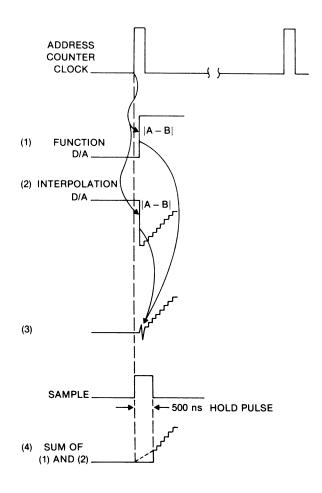

### 1.2.1.3 Digital Smoothing

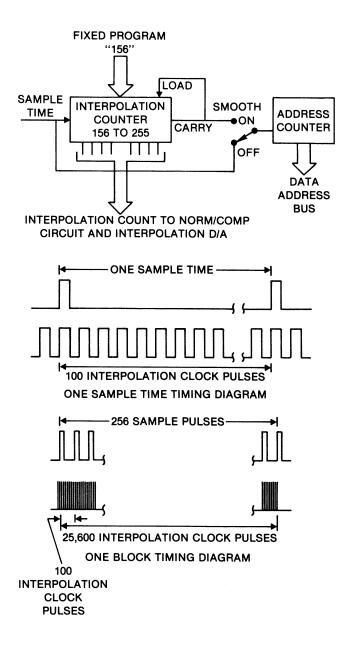

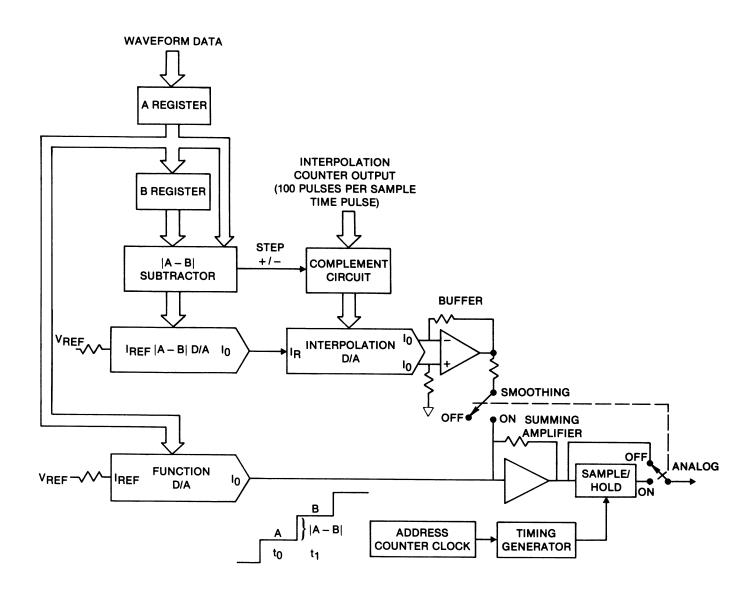

When smoothing is selected, each change in amplitude data is subdivided into 100 substeps per sample time. Smoothing is automatically limited to 20  $\mu$ s or slower sampling times and to point-to-point data differentials less than 64.

### 1.2.1.4 Sync Output

TTL level pulse with a trailing edge coincident with the start address. Pulse width is one sample time. Available at rear panel BNC.

### 1.2.1.5 Cursor Output

TTL level output coincident with a selected data address. Available at rear panel BNC.

### 1.2.1.6 Operational Modes

Continuous: Generator operates continuously at selected frequency.

Preset Triggered: Generator quiescent until triggered via front panel key, GPIB program or TTL pulse at rear panel BNC; then a preset number of cycles to 9999 are generated at a selected frequency.

Monitor Triggered: As for Preset Triggered, except the cycles are output continuously after triggering, until a hold command (via front panel key, GPIB program or TTL low at rear panel BNC) is given. The number of cycles generated up to 9999 can be displayed.

Hold Control: Front panel key, GPIB program or TTL low at rear panel BNC can stop the waveform asynchronously to the reference clock. Triggered modes only. (Restart from the held level by trigger signal.)

Ramp-to-Zero: Front panel key, TTL low at rear panel BNC or GPIB program can step output linearly to 0V in approximately 15 seconds.

### 1.2.2 Timing Precision

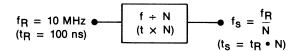

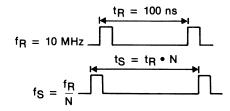

### 1.2.2.1 Sample Time

The stepping time from data point to adjacent data point is selectable as 200 ns to 999.9s for fixed waveforms and optional PROM stored data points (500 ns to 999.9s for RAM stored data points). Sample time accuracy is  $\pm 0.03\%$  of setting. Resolution is 100 ns (10  $\mu$ s when smoothing). Output frequency is 19.5 kHz to 3.90  $\mu$ Hz (71 hr/cycle) rate for a 256 word block. Sample time can be displayed and programmed in seconds, minutes, hours or as data block rate in hertz.

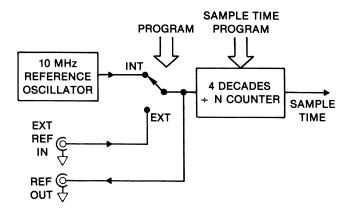

### 1.2.2.2 Reference Clock

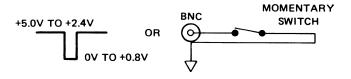

Internal 10 MHz crystal controlled oscillator or external TTL compatible frequency source input at rear panel BNC. TTL compatible reference clock output provided.

### 1.2.2.3 External Clock

TTL compatible signal applied at rear panel BNC. Permissible external clock frequency is dc to 11 MHz for contin-

uous modes. Ratio of external clock to reference clock determines output frequency.

### 1.2.3 Amplitude Precision

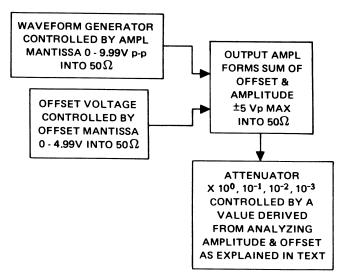

### 1.2.3.1 Main Output (Attenuated, $50\Omega$ Source)

### 1.2.3.2 Auxiliary Output ( $< 1\Omega$ Source)

Same waveform as main output from 0 to 10V peak (at fixed 0 dB attenuation). Same offset as main output and limited to 100 mA peak.

### 1.2.3.3 Output Amplifier Rise/Fall Time

Less than 500 ns,  $50\Omega$  termination, main output.

### 1.2.4 General

### 1.2.4.1 Display

LED seven segment display with alphabetical index of key functions and units. All status, modes and functions are shown by LED annunciator displays.

### 1.2.4.2 Keyboard

Membrane type with acoustic feedback. Acoustic tone may be turned off by front panel key.

### 1.2.4.3 External Program Interface

IEEE Standard 488-1975 compatible General Purpose Interface Bus (GPIB). Connector and address switch on rear panel. The interface provides listener (AH1 and L4), talker (SH1 and T6), service request (SR1), remote/local (RL1), device clear (DC1) and device trigger (DT1) capabilities. Handshake rate is 2  $\mu$ s per character in command mode (10  $\mu$ s typical for command sequence) and 220  $\mu$ s per character in data mode, with data storage of up to 80 characters. The following table may be used to determine particular through-put times. Measurements were made with a 175 and an HP9825 controller. Data rates will follow

the slowest listener on the bus and vary with different controllers.

| Parameter         | Time   |

|-------------------|--------|

| Command Handshake | 2 μs   |

| Data Handshake    | 220 μs |

| Sample Time       | 35 ms  |

| Block Rate        | 50 ms  |

| Amplitude Setting | 65 ms  |

| DC Offset Setting | 65 ms  |

| Burst Length      | 20 ms  |

| Function          | 20 ms  |

| Int/Ext Clock     | 20 ms  |

| Time Unit         | 25 ms  |

| Mode CONT/TRIG    | 20 ms  |

| PRST/MNTR Trigger | 20 ms  |

| FULL/PART Block   | 25 ms  |

| Start Address     | 25 ms  |

| Stop Address      | 25 ms  |

| Output OFF/ON     | 20 ms  |

| X Address         | 30 ms  |

| Y Data            | 40 ms  |

| Smoothing OFF/ON  | 35 ms  |

| Execute           | 16 ms* |

| GET               | 1.6 ms |

<sup>\*2</sup> ms when via GET

### 1.2.4.4 Stability

### **Amplitude and DC Offset**

Measured at full output and 25  $\pm 1^{\circ}$ C. Change is less than  $\pm 0.25\%$  per day. Change with temperature is less than  $\pm 0.2\%$  over 0 to  $50^{\circ}$ C.

### Frequency

Crystal aging rate is less than 2  $\times$  10<sup>-5</sup> per year. Temperature coefficient is 1  $\times$  10<sup>-6</sup>/°C.

### 1.2.4.5 Environmental

Specifications apply for 25  $\pm 10^{\circ}$ C after ½ hour. Instrument will operate from 0 to 50°C to 10,000 ft altitude at 95% relative humidity.

### 1.2.4.6 Dimensions

Fits standard 48.3 cm (19 in.) rack. Dimensions behind front panel are 43.2 cm (17 in.) wide; 13.3 cm (5½ in.) high; 51.4 cm (20½ in.) deep.

### 1.2.4.7 Weight

15.9 kg (35 lb) net; 20.4 kg (45 lb) shipping.

### 1.2.4.8 Power

90 to 105V, 108 to 126V, 198 to 231V or 216 to 252V; 48 to 66 Hz; less than 120 watts.

# SECTION 2 INSTALLATION AND INTERFACE

### 2.1 MECHANICAL INSTALLATION

After unpacking the instrument, visually inspect all external parts for possible damage to connectors, surface areas, etc. If damage is discovered, file a claim with the carrier who transported the unit. The shipping container and packing material should be saved in case reshipment is required.

The generator can be used as a bench instrument or rack mounted. In either use, ensure that there is no impedance to air flow at any surface of the instrument.

### 2.2 ELECTRICAL INSTALLATION

### 2.2.1 Power Connection

### NOTE

Unless otherwise specified at the time of purchase, this instrument was shipped from the factory with the power transformer connected for operation on a 120 Vac line supply and with a 2 amp fuse.

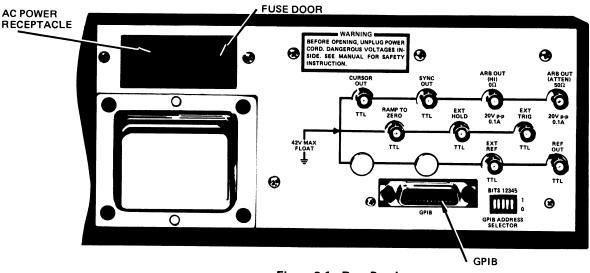

Conversion to other input voltages requires a change in rear panel fuse holder voltage card position and fuse (figure 2-1) according to the following procedure.

| Card Position | Input Vac  | Fuse  |

|---------------|------------|-------|

| 100           | 90 to 105  | 2 amp |

| 120           | 108 to 126 | 2 amp |

| 220           | 198 to 231 | 1 amp |

| 240           | 216 to 252 | 1 amp |

- Disconnect the power cord at the instrument, open fuse holder cover door and rotate fuse pull to left to remove the fuse.

- Remove the small printed circuit board and select operating voltage by orienting the printed circuit board to position the desired voltage to the top left side.

Push the board firmly into its module slot.

- Rotate the fuse-pull back into the normal position and insert the correct fuse into the fuse holder. Close the cover door.

- 4. Connect the ac line cord to the mating connector at the rear of the unit and the power source.

### 2.2.2 Signal Connections

Use RG58U  $50\Omega$  shielded cables equipped with BNC connectors to distribute signals (figure 2-1) when connecting this instrument to associated equipment.

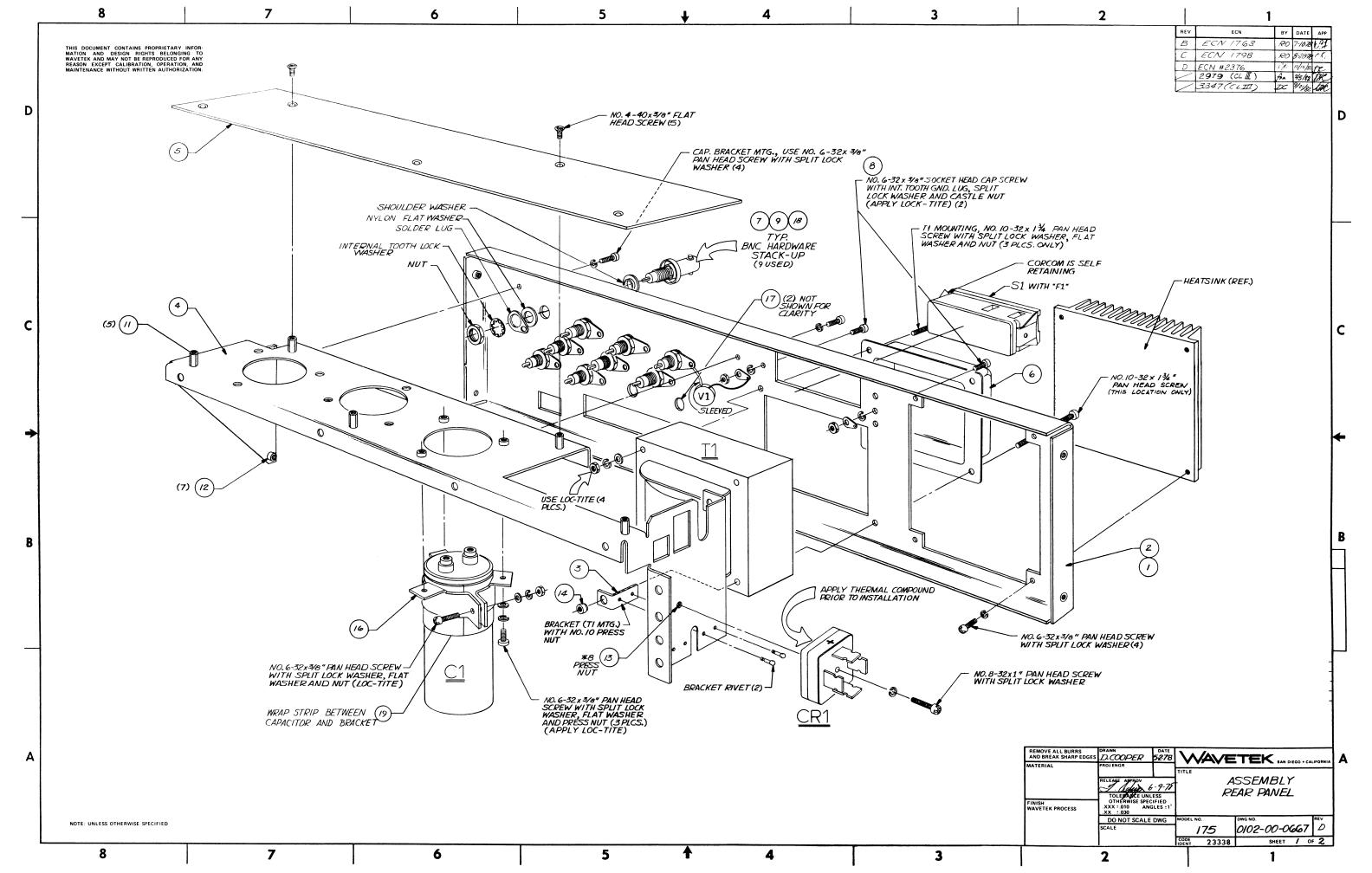

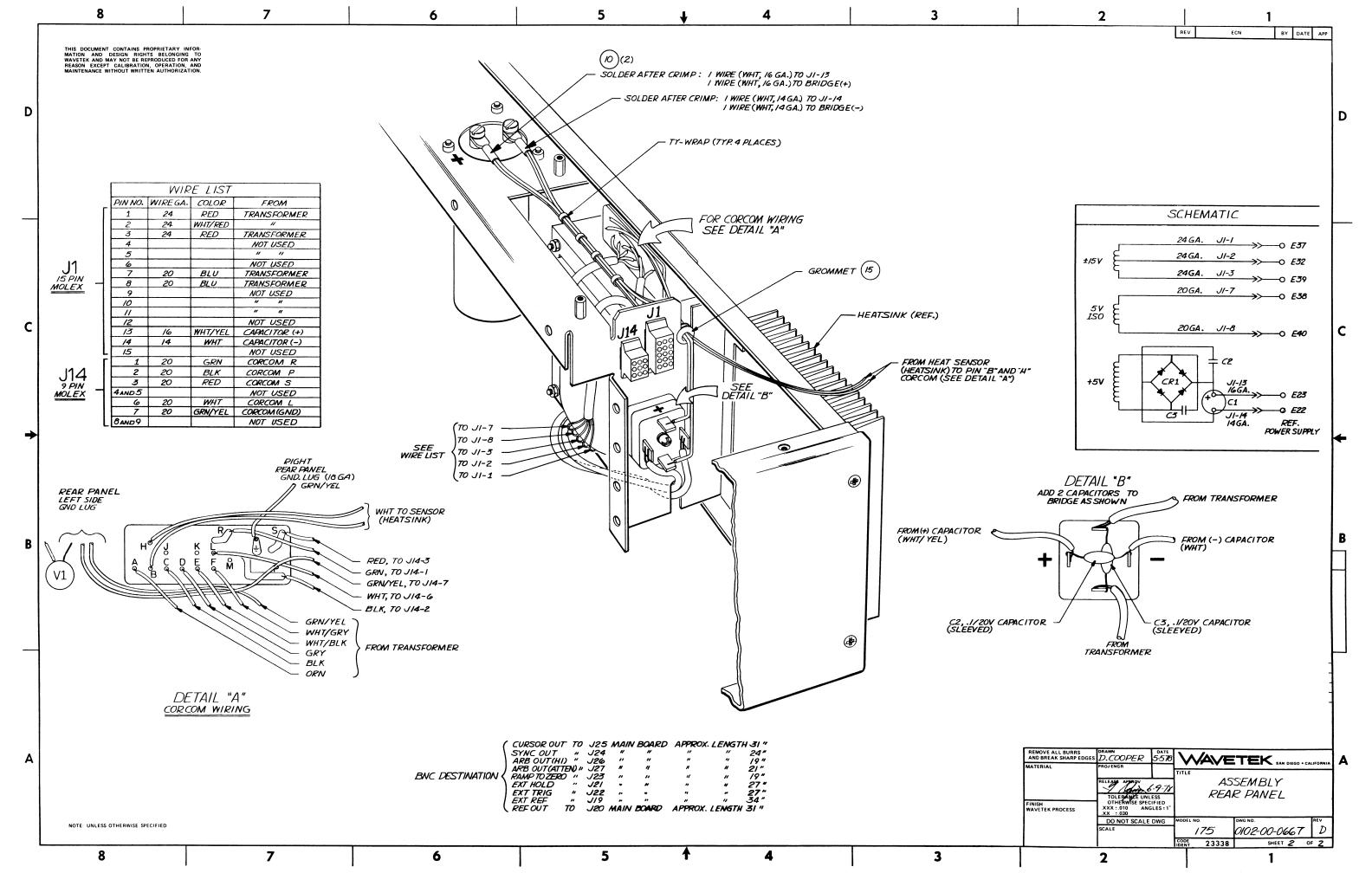

Figure 2-1. Rear Panel

## 2.2.3 General Purpose Interface Bus (GPIB) Connections

The GPIB I/O rear panel connection is shown in figure 2-1; pin connections and signal names are given in table 2-1. The panel connector is an Amphenol 57-10240 or equivalent and connects to a GPIB bus cable (available from Wavetek). The GPIB interface is optically isolated from the instrument.

### 2.2.4 GPIB Address

For instruments on the GPIB, ensure that the GPIB address is correct.

The GPIB address can be changed by the switch on the rear of the instrument (see figure 2-1) by simply setting the multiple section switch according to table 2-2. The switch sections are labeled from 1 through 5 and their open position noted (OPEN = "0" in table 2-2). To verify the address, press GPIB ADR on the front panel. The device number (decimal) will be displayed as "0, 1, --- 30."

Table 2-1. GPIB Data In/Out

| Pin | Signal     |   |                |  |  |  |

|-----|------------|---|----------------|--|--|--|

| 1   | DIO1 `     | ) |                |  |  |  |

| 2   | DIO2       | 1 |                |  |  |  |

| 3   | DIO3       | Ş | True When Low  |  |  |  |

| 4   | DIO4       |   |                |  |  |  |

| 5   | EOI        |   |                |  |  |  |

| 6   | DAV <      | , |                |  |  |  |

| 7   | NRFD       |   | Two Mhan High  |  |  |  |

| 8   | NDAC       | ſ | True When High |  |  |  |

| 9   | IFC   <    | ì |                |  |  |  |

| 10  | SRQ        | } | True When Low  |  |  |  |

| 11  | ATN        | J |                |  |  |  |

| 12  | Safety Gno | b |                |  |  |  |

| 13  | DIO5       | ) |                |  |  |  |

| 14  | DIO6       | l | T - 14/0 - 1 - |  |  |  |

| 15  | DIO7       | 7 | True When Low  |  |  |  |

| 16  | DIO8       |   |                |  |  |  |

| 17  | REN (      | , |                |  |  |  |

| 18  | `          | ) |                |  |  |  |

| 19  |            |   |                |  |  |  |

| 20  |            |   |                |  |  |  |

| 21  |            | ? | Signal Gnd     |  |  |  |

| 22  |            |   |                |  |  |  |

| 23  |            |   |                |  |  |  |

| 24  | /          | J |                |  |  |  |

Table 2-2. GPIB Address Codes

|        | Address    |        |     |                    |   |   |              |            |            |

|--------|------------|--------|-----|--------------------|---|---|--------------|------------|------------|

|        | ASC        | ASCII  |     | Switch<br>Position |   |   | Hex<br>decir |            |            |

| Device | Listen     | Talk   | 1   | 2                  | 3 | 4 | 5            | Listen     | Talk       |

| 0      | (space)    | @      | 0   | 0                  | 0 | 0 | 0            | 20         | 40         |

| 1      | !          | Α      | 1   | 0                  | 0 | 0 | 0            | 21         | 41         |

| 2<br>3 |            | В      | 0   | 1                  | 0 | 0 | 0            | 22         | 42         |

| 3<br>4 | #          | С      | 1   | 1                  | 0 | 0 | 0            | 23         | 43         |

|        | \$         | D      | 0   | 0                  | 1 | 0 | 0            | 24         | 44         |

| 5<br>6 | %<br>  &   | E<br>F | 1 0 | 0                  | 1 | 0 | 0            | 25         | 45<br>40   |

| 7      | α,         | G      | 1   | 1                  | 1 | 0 | 0            | 26         | 46<br>47   |

| 8      | <b> </b> , | Н      | 0   | 0                  | 0 | 1 | 0            | 27<br>28   | 47<br>48   |

| 9      | (          |        | 1   | 0                  | 0 | 1 | 0            | 26<br>29   | 40<br>49   |

| 10     | <b>,</b>   | J      | 0   | 1                  | 0 | 1 | 0            | 29<br>2A   | 49<br>4A   |

| 11     | +          | K      | 1   | 1                  | 0 | 1 | 0            | 2B         | 4B         |

| 12     |            | L      | Ö   | Ö                  | 1 | 1 | 0            | 2C         | 4C         |

| 13     | ,          | М      | 1   | 0                  | 1 | 1 | 0            | 2D         | 4D         |

| 14     | •          | N      | 0   | 1                  | 1 | 1 | 0            | 2E         | 4E         |

| 15     | /          | 0      | 1   | 1                  | 1 | 1 | 0            | 2F         | 4F         |

| 16     | Ó          | Р      | 0   | 0                  | 0 | 0 | 1            | 30         | 50         |

| 17     | 1          | Q      | 1   | 0                  | 0 | 0 | 1            | 31         | 51         |

| 18     | 2          | R      | 0   | 1                  | 0 | 0 | 1            | 32         | 52         |

| 19     | 3          | S      | 1   | 1                  | 0 | 0 | 1            | 33         | 53         |

| 20     | 4          | Т      | 0   | 0                  | 1 | 0 | 1            | 34         | 54         |

| 21     | 5          | U      | 1   | 0                  | 1 | 0 | 1            | 35         | 55         |

| 22     | 6          | V      | 0   | 1                  | 1 | 0 | 1            | 36         | 56         |

| 23     | 7          | W      | 1   | 1                  | 1 | 0 | 1            | 37         | 57         |

| 24     | 8          | X      | 0   | 0                  | 0 | 1 | 1            | 38         | 58         |

| 25     | 9          | Υ      | 1   | 0                  | 0 | 1 | 1            | 39         | 59         |

| 26     | :          | Z      | 0   | 1                  | 0 | 1 | 1            | 3 <b>A</b> | 5 <b>A</b> |

| 27     | ;          | [      | 1   | 1                  | 0 | 1 | 1            | 3B         | 5B         |

| 28     | <          | \ \    | 0   | 0                  | 1 | 1 | 1            | 3C         | 5C         |

| 29     | =          | ]      | 1   | 0                  | 1 | 1 | 1            | 3D         | 5D         |

| 30     | >          | 1      | 0   | 1                  | 1 | 1 | 1            | 3E         | 5E_        |

### 2.2.5 Initial Checkout and Operation Verification

The equipment and procedures in tables 2-3 and 2-4 are recommended for incoming inspection and for testing the instrument after repair. However, additional after repair tests or calibration (Section 4) may be necessary for certain circuits.

Operation verification includes the following procedures.

- Power On: Verifies initial conditions as determined by microprocessor and firmware circuits.

- 2. Lamp Test: Verifies condition of display lamps.

- 3. **Output Waveform Test:** Sine wave output is visually checked for correct frequency and visible irregularities. Smoothing also checked.

- 4. **Function Test:** Verifies standard waveforms.

- 5. **Waveform Generation Test:** Verifies data may be entered and appropriate waveform generated.

- 6. **Ramp To Zero Test:** Verifies ramp to zero operation.

- Reset Test: Verifies proper resetting of instrument.

- 8. **Amplitude Accuracy Test:** Verifies amplitude accuracy of dc and ac operations.

- 9. Frequency Accuracy Test: Verifies block rate accuracy.

- 10. **Interface Test:** Verifies remote control capabilities of listening and talking.

Before making an initial checkout, review power and signal connection requirements (paragraphs 2.2.1 and 2.2.2) and ensure the availability of test equipment equivalent to that listed in table 2-3. An acceptance test record sheet (table 2-5) may be reproduced for recording checkout test results.

### 2.2.6 Permanent Custom Waveforms

Four 74S471 PROMs containing custom waveform data may be added in socket positions U7E through U10E on the generator board 1100-00-0644 (drawing 0101-00-0644).

Refer to Appendix C for PROM encoding and to paragraph 3.2.2(19) for operator access to these waveforms.

Table 2-3. Equipment Required for Incoming Inspection and Operation Verification

| Instrument           | Critical Specifications                                    | Model<br>Recom-<br>mended |

|----------------------|------------------------------------------------------------|---------------------------|

| Oscillo-<br>scope    | ≥30 MHz vertical band-<br>width                            | Tektronix<br>7903         |

| 50Ω Load             | BNC feedthru                                               | Tektronix<br>011009900    |

| Voltmeter            | 0.1 to 10V ranges 3 digit resolution ±0.1% accuracy        | Dana<br>6000<br>Series    |

| Frequency<br>Counter | 20 MHz capability<br>5 digit resolution<br>±0.01% accuracy | Dana<br>9000<br>Series    |

| Calculator           | IEEE 488-1975 compat-<br>ible                              | HP9825                    |

**Table 2-4. Operation Verification**

| Step | Test      | Tester and Setup | Program   | Desired Results                                                                                                                                                   |

|------|-----------|------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Power On  | None.            | Power ON  | Several LEDs light momentarily, then darken, with only the following remaining lit:  MODE — CONT; CLOCK — INT; TRIG CYCLE - PRST; BLOCK — FULL; Function — SIN 0. |

| 2    | Lamp Test | None.            | LAMP TEST | All display LEDs lit. The last three 8's are not followed by decimal points.                                                                                      |

Table 2-4. Operation Verification (Continued)

| Step | Test                   | Tester and Setup                                                                                                                                                                                                      | Program                                                                                                               | Desired Results                                                                                                                                      |

|------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3    | Output Waveform        | Oscilloscope. Connect ARB OUT (ATTEN) $50\Omega$ with $50\Omega$ load at the scope input. Set for $2\text{V/div}$ , horizontal 1 ms/div, external auto trigger. Connect ARB SYNC OUT to scope external trigger input. | OUTPUT:<br>OFF/ON 1<br>AMPL 10<br>SMTH:<br>OFF/ON 1<br>EXEC                                                           | Approximately 5 div per cycle, 10V p-p visually nondistorted sine wave.                                                                              |

| 4    |                        | Oscilloscope. Set horizontal for .02 ms/ div.                                                                                                                                                                         |                                                                                                                       | Nearly straight line (expanded sine curve) on scope.                                                                                                 |

| 5    |                        |                                                                                                                                                                                                                       | SMTH:<br>OFF/ON 0<br>EXEC                                                                                             | Stair step waveform on scope.                                                                                                                        |

| 6    |                        | Oscilloscope. Set horizontal for 1 ms/div.                                                                                                                                                                            |                                                                                                                       | Sine waveform on scope.                                                                                                                              |

| 7    | Function               |                                                                                                                                                                                                                       | FUNC 1<br>EXEC                                                                                                        | Triangle waveform on scope.                                                                                                                          |

| 8    |                        |                                                                                                                                                                                                                       | FUNC 2<br>EXEC                                                                                                        | Square waveform on scope.                                                                                                                            |

| 9    |                        |                                                                                                                                                                                                                       | FUNC 3<br>EXEC                                                                                                        | Ramp waveform on scope.                                                                                                                              |

| 10   | Waveform<br>Generation |                                                                                                                                                                                                                       | SMTH 1 FUNC 8 EXEC MEMORY: ADRS 0 DATA 0 ADRS 50 DATA 127 ADRS 100 DATA - 127 ADRS 150 DATA + 35 ADRS 255 DATA 0 EXEC | Triangle waveform followed by down slope ramp waveform on scope.                                                                                     |

| 11   | Ramp To Zero           | Oscilloscope. Set horizontal to .2s/div. Adjust scope intensity to safe level.                                                                                                                                        | BLOCK RATE .1<br>EXEC                                                                                                 | Trace moves slowly across scope.                                                                                                                     |

| 12   |                        |                                                                                                                                                                                                                       | Depress RAMP TO ZERO key when scope trace is near a + or – peak on waveform.                                          | HOLD LED lights. Trace changes desired waveform to a ramp that slowly approaches zero. The ARB display indicates a 'G' within 15 seconds.            |

| 13   | Reset                  |                                                                                                                                                                                                                       | EXEC                                                                                                                  | Trace same as in step 11.                                                                                                                            |

| 14   |                        | Oscilloscope. Set horizontal for .02 ms/ div.                                                                                                                                                                         | RESET                                                                                                                 | Scope display is 0 volts. The following LED display indicators are lit: MODE — CONT; CLOCK — INT; TRIG CYCLE — PRST; BLOCK — FULL; FUNCTION — SIN 0. |

Table 2-4. Operation Verification (Continued)

| Step | Test               | Tester and Setup                                                                                                                                                                                                                                                       | Program                                                                                                                                                                          | Desired Results                                                        |

|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 15   |                    | Oscilloscope. Set horizontal for 1 ms/div.                                                                                                                                                                                                                             | OUTPUT:<br>OFF/ON 1<br>AMPL 10<br>SMTH:<br>OFF/ON 1<br>EXEC                                                                                                                      | Visually nondistorted sine wave.                                       |

|      |                    | NOTE: Allow 30 minute warm-up before                                                                                                                                                                                                                                   | performing the following                                                                                                                                                         | tests.                                                                 |

| 16   | Amplitude Accuracy | (Disconnect oscilloscope.) Voltmeter. Set to Vrms, ac. Connect to ARB OUT (ATTEN) $50\Omega$ with a precision $50\Omega$ load at voltmeter input.                                                                                                                      |                                                                                                                                                                                  | 3.35 to 3.71 Vrms.                                                     |

| 17   |                    | Voltmeter. Set to read Vdc.                                                                                                                                                                                                                                            | AMPL 0<br>OFST 5<br>EXEC                                                                                                                                                         | + 4.75 to + 5.25 Vdc.                                                  |

| 18   | Frequency Accuracy | (Disconnect voltmeter.) Counter. Set to read frequency nominal 200 Hz at 10V p-p input. Connect to ARB OUT (ATTEN) 50Ω with 50Ω load at counter input.                                                                                                                 | AMPL 5<br>OFST 0<br>EXEC<br>FUNC 2                                                                                                                                               | 192 to 198 Hz.                                                         |

| 19   | Interface          | Oscilloscope. Connect ARB OUT (ATTEN) 50Ω with 50Ω load at the scope input. Set trigger to ext, dc, normal. Calculator. Connect to ARB GPIB connector. Set ARB rear panel GPIB ADDRESS SWITCH to 00100. Press GPIB ADRS key and verify GPIB address is "4" on display. | Calculator: 0: dim A\$[100] 1: fxd 2 2: wrt 704,"ZI" 3: wait 1000 4: wrt 704, "A5O1 P1I" 5: stp                                                                                  | 10V p-p sine wave of 5.12 ms period.                                   |

| 20   |                    |                                                                                                                                                                                                                                                                        | 6: wrt 704,"C11I<br>X100Y-127X153Y1<br>27X154Y-127IB1D<br>0M0L3U1V100W154<br>T5E-6I"<br>7: wait 500<br>8: for I = 1 to 20<br>9: wait 500<br>10: trg 704<br>11: next I<br>12: stp | 20 bursts of 3 partial ramp wave forms in approximately 0.5s intervals |

| 21   |                    |                                                                                                                                                                                                                                                                        | 13: wrt 704,"ZI" ;wait 1000 14: wrt 704,"R3I F" 15: red 704,A\$ 16: prt A\$;stp 17: lcl 704 18: prt "175 test complete" 19: stp                                                  | Calculator printout.<br>V F 195.31                                     |

# Table 2-5. Acceptance Test Record (for reproduction)

|    |                                                                           |           | Location | n       |                |  |

|----|---------------------------------------------------------------------------|-----------|----------|---------|----------------|--|

|    |                                                                           |           | QA Insp  | pector  |                |  |

|    |                                                                           |           | Date     |         |                |  |

|    |                                                                           |           | Instrum  | ent S/N |                |  |

|    |                                                                           |           |          |         |                |  |

|    |                                                                           |           |          |         |                |  |

|    |                                                                           |           |          |         |                |  |

|    |                                                                           |           |          |         |                |  |

|    |                                                                           |           |          |         |                |  |

|    |                                                                           |           |          |         |                |  |

|    |                                                                           |           |          |         | Acceptable (✓) |  |

| A. | Manual Checks,<br>Data Entry and<br>Visual Checks<br>(steps 1 through 15) |           |          |         |                |  |

|    |                                                                           |           |          |         |                |  |

|    |                                                                           |           |          |         |                |  |

| B. | Amplitude Accuracy                                                        |           |          |         |                |  |

|    |                                                                           | (step 16) |          | Vrms    |                |  |

|    |                                                                           | (step 17) |          | Vdc     | 4              |  |

|    |                                                                           |           |          |         |                |  |

|    |                                                                           |           |          |         |                |  |

| C. | Frequency Accuracy                                                        |           |          |         |                |  |

|    |                                                                           | (step 18) |          | . Hz    |                |  |

|    |                                                                           |           |          |         |                |  |

|    |                                                                           |           |          |         |                |  |

|    |                                                                           |           |          |         |                |  |

| D. | Interface-GPIB (steps 19 through 21)                                      |           |          |         |                |  |

|    |                                                                           |           |          |         |                |  |

# SECTION 3 OPERATION

### 3.1 GENERAL

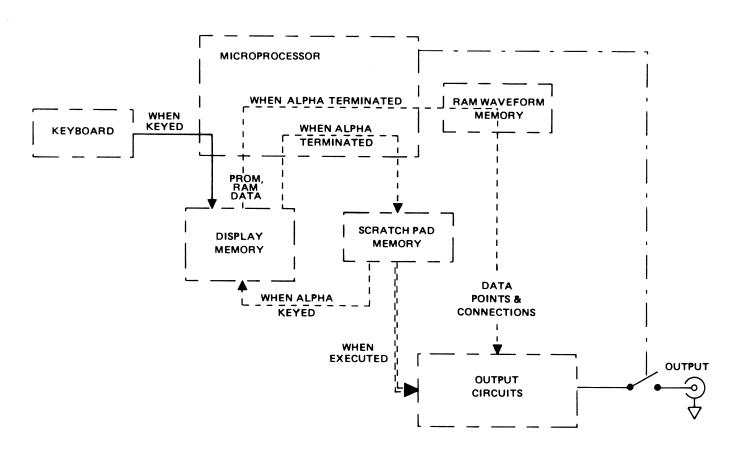

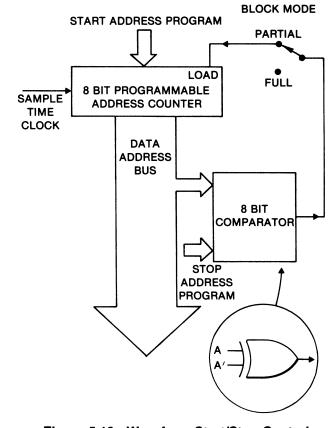

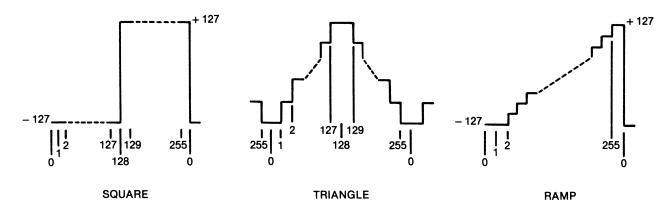

The waveforms to be output are contained as a series of values in storage, which are read and output at some selected rate. There are 12 blocks each of 256 addresses (4 blocks are optional). Four blocks have fixed waveforms of sine, triangle, square and ramp, respectively. For example, in the sine wave block, the values for each address determine 256 data points that approximate the shape of a sine wave. Four optional PROM blocks each contain custom waveforms. Four RAM blocks may be loaded with waveform data and erased, as required.

The selected block of waveform may be output from address zero to address 255 (one cycle) repeatedly to form a continuous waveform output. As a variation, any start address and any stop address may be specified for the cycle. Or, two, three or four blocks may be linked together for one cycle of the output waveform. Blocks that can be linked are PROM blocks 1 and 2; 1, 2 and 3; 1, 2, 3 and 4. Similarly, the RAM blocks may be linked. The dwell time at each

address, the time the output is the value for that address, can be selected as either sample time (in seconds, minutes or hours) or block rate (in Hertz).

Besides the continuous output of a waveform, triggered output may be selected. A preset number of cycles may be output when the Arb is triggered. Or, when triggered, the output waveform can be continuous until stopped by a Hold command. The number of cycles output can then be read by a Monitor Count command.

The waveform amplitude may be dc offset, attenuated and smoothed. Smoothing minimizes the transition between amplitude steps for amplitude step differences less than 64.

The  $50\Omega$  output is off at power on time, which allows programming before electrically connecting the Arb output to the outside world. To change the output, the change must be programmed or keyed and then executed by an Execute command or pressing the EXEC key. An example of front panel operation is given in table 3-1.

Table 3-1. Example of Front Panel Data Entry

|    | Instruction                                                                                                                         | Front Panel Entry<br>(Press Keys) | Equivalent<br>Program | Front Panel Display      |

|----|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|--------------------------|

| 1. | Power on. The display shows most of the initial conditions.                                                                         | OFF (becomes ON)                  |                       | See figure 3-1.          |

| 2. | Test lamps. (27 status lamps, a 5 X 7 dot matrix, four 8's with decimals, three 8's without decimals and an asterisk.               | LAMP<br>TEST                      |                       | All lamps should be lit. |

| 3. | Check initial conditions at every key.                                                                                              | Press each front panel key        |                       | See paragraph 3.2        |

| 4. | Connect an oscilloscope to the ARB OUT (ATTEN) $50\Omega$ connector using a $50\Omega$ load. Enable the output and observe the sine | OUTPUT 1                          | P1                    | P1                       |

|    | waveform.                                                                                                                           | EXEC                              | I                     | I OUTPUT ●               |

| 5. | Use the oscilloscope to amplify the wave-<br>form until the individual steps of the wave-<br>form can be seen. Smooth the waveform. | SMTH OFF 1                        | 01                    | 01                       |

|    |                                                                                                                                     | EXEC                              | I                     | I SMOOTH                 |

Table 3-1. Example of Front Panel Data Entry (Continued)

| Instruction                                                          | Front Panel Entry<br>(Press Keys) | Equivalent<br>Program | Front Panel Display |

|----------------------------------------------------------------------|-----------------------------------|-----------------------|---------------------|

| 6. Change the amplitude and offset to:                               | AMPL 4 • 7 2                      | A4.72                 | A4.72               |

| 0V <u>♥</u>                                                          | OFST + 1 · 2                      | D-1.2                 | D-1.2               |

| -1.2V                                                                | EXEC                              | I                     | I                   |

| 7. Oberserve the other waveforms. (There may                         | FUNC 1                            | C1                    | C1                  |

| be no waveforms in C4 thru C7.) C8 thru C11 will have a OV baseline. | EXEC                              | I                     | I TRI               |

|                                                                      | FUNC 2                            | C2                    | C2                  |

|                                                                      | EXEC                              | I                     | I SQR 2             |

|                                                                      | FUNC 3                            | C3                    | C3                  |

|                                                                      | EXEC                              | I                     | I RMP               |

|                                                                      | FUNC 4                            | C4                    |                     |

|                                                                      | EXEC                              | I                     | I PROM              |

|                                                                      | (etc. to C11)                     |                       | •                   |

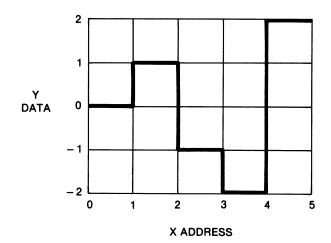

| 8. Design a simple waveform in C11. This                             | ADRS 0                            | Х0                    | X0                  |

| illustrates the use of automatic interpola-<br>tion.                 | DATA 8 5                          | Y85                   | Y85                 |

| +127 N                                                               | ADRS 2 9                          | X29                   | X29                 |

| 85                                                                   | DATA 0                            | Y0                    | Y0                  |

| 47-                                                                  | ADRS 3 0                          | X30                   | X30                 |

| 29 71 110                                                            | DATA +/_ 1 2 5                    | Y-125                 | Y-125               |

| °                                                                    | ADRS 7 1                          | X71                   | X71                 |

|                                                                      | DATA 0                            | Y0                    | Y0                  |

| 125                                                                  | ADRS 1 1 0                        | X110<br>Y47           | X110                |

| -127 $V-125$ $0$ 30 $255$                                            | DATA 4 7 ADRS 1 1 1 1             | X111                  | Y47<br>X111         |

| A line is drawn to the plotted point when                            | DATA [1] [2] [7]                  | Y127                  | Y127                |

| the following ADR key is pressed.                                    | ADRS [2] [5] [5]                  | X255                  | X255                |

|                                                                      | DATA +/- 127                      | Y-127                 | Y-127               |

| 9. Observe this waveform on the oscilloscope.                        | EXEC                              | I                     | I                   |

|                                                                      |                                   |                       |                     |

|                                                                      |                                   |                       |                     |

|                                                                      | I                                 | I                     | 1                   |

Table 3-1. Example of Front Panel Data Entry (Continued)

| Instruction                                                                                                        | Front Panel Entry<br>(Press Keys) | Equivalent<br>Program | Front Panel Display    |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|------------------------|

| 10. Select only one portion of this waveform and observe it on the oscilloscope. (Fre-                             | FULL 1                            | U1                    | U1                     |

| quency increases because there are less data<br>points being sampled. The sampling rate has<br>remained the same.) | START 2 0 ADRS                    | V20                   | V20 BLOCK<br>FULL PART |

| remained the sume.                                                                                                 | STOP 1 1 1 1 ADRS                 | W111                  | W111                   |

|                                                                                                                    | EXEC                              | I                     | I                      |

| 11. Prepare to output exactly 321 cycles of this waveform.                                                         | CONT 1                            | B1                    | B1                     |

|                                                                                                                    | PRST 0 MNTR                       | МО                    | МО                     |

|                                                                                                                    | PRST 3 2 1<br>LNGTH               | L321                  | L321                   |

|                                                                                                                    | EXEC                              | I                     | I                      |

| 12. When triggering, observe the Hold status light.                                                                | TRIG                              | J                     | J HOLD then            |

| 13. Return to full block mode.                                                                                     | FULL 0                            | UO                    | UO                     |

| 14 Change the frequency to approximately 10 kHz.                                                                   | BLOCK 1 0 E 3                     | F10E3                 | F10E3                  |

|                                                                                                                    | EXEC                              | I                     | I                      |

| 15. Examine the actual sample time.                                                                                | SAMPLE<br>TIME                    | т                     | T400E-9 S              |

| 16. Examine the actual frequency.                                                                                  | BLOCK<br>RATE                     | F                     | F9.7656E3 Hz           |

NOTE: Frequency is determined by the number of blocks stacked, the number of data points in a cycle and the sample time per data point. Therefore, desired frequencies can only be approximate.

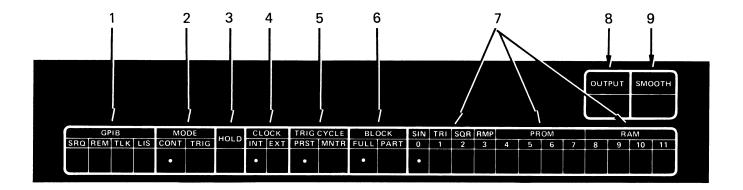

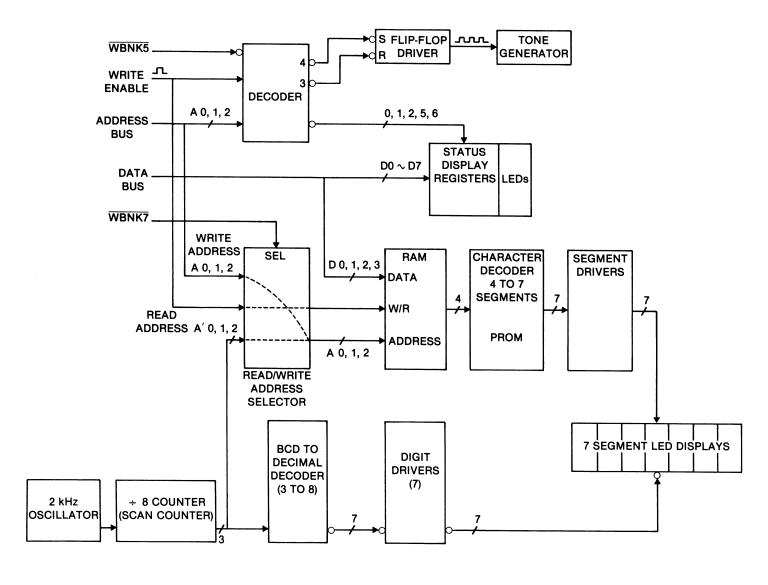

1. **GPIB Status:** SRQ — Service request being sent

REM — Remote (GPIB) control

TLK — Arb talking on the GPIB

LIS — Arb listening on the GPIB

if lit

2. Mode Status: Continuous or triggered output.

3. Hold Status: Output is being held at some data point if lamp is lit.

4. Clock Status: Internal 10 MHz clock or external clock (11 MHz maximum).

5. Triggered Cycle Status: Preset number of cycles or monitor the number of cycles output.

6. Block Status: The full block or a partial block of data points is being used.

7. Function Status: Sine, triangle, square, ramp, PROM stored or RAM stored waveform output. The lamp of the

selected block is lit. If multiple blocks of RAM or of PROM are being stacked together, then

the lamps of the stacked blocks are lit.

8. Output Status: Output on if lamp is lit.

9. Smoothing Status: Smoothing of digital waveform steps active if lamp is lit.

### **NOTES:**

"Power On" condition shown: 1. Local Control – Not GPIB (Remote Control)

2. Continuous Mode

3. Generator Running

4. Internal Clock

5. Preset Number of Triggered Cycles (however, mode is continuous)

6. Full Block of 256 Data Points Used

7. Sine Waveform

8. Output Off

9. Smoothing Off

Figure 3-1. Status Display

NOTE: See paragraph 3.2 for item descriptions.

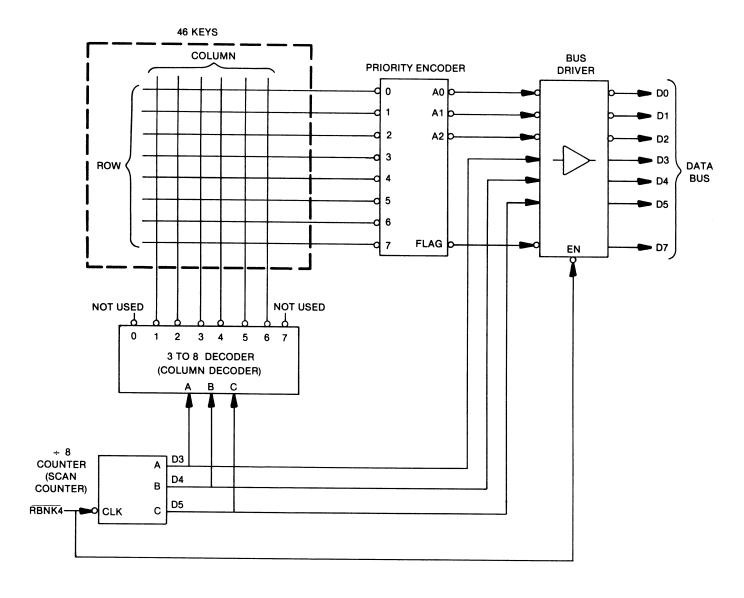

Figure 3-2. Keyboard

### 3.2 KEYBOARD

### 3.2.1 Notes

- Most keys (figure 3-2) are associated with a parameter and, when pressed, give the status of that parameter. The parameter status or value is changed by pressing number keys after the parameter key. Other keys give immediate action when pressed.

- 2. The key functions that can be GPIB programmed have their GPIB ASCII character in the lower left corner and are called alpha keys. (The block of number keys may also be programmed.)

- Because of the variety of format that the operator can use when entering values, the microprocessor does not assume that programming is complete until another alpha key (except EXP) is pressed. At this time, the value is tested and, if ok, placed in a scratch pad memory.

- When an asterisk (\*) appears in the display, it indicates that a number is being entered from either the keyboard or GPIB.

- 5. Initial conditions (I/C) at power-on time are noted in paragraph 3.2.2.

- 6. Brief key descriptions are given in paragraph 3.2.2. Details on the use of the keys are in the following paragraphs and referenced where applicable.

- 7. Errors detected are flagged by an "ERROR" in the display. Refer to paragraph 3.14.

### 3.2.2 Key Descriptions

The following item numbers correspond to those in figure 3-2.

- Lamp Test Lights all display status blocks and display segments.

- GPIB Address Shows GPIB decimal address set by switches on rear panel.

- GPIB Service Request Enable (Q) Shows what conditions will cause the Arb to send a service request over the GPIB:

- Q0 Suppresses all service requests.

- Q1 Enables service request for errors (I/C).

- Q2 Enables service request when the waveform generation circuits make a transition from not holding to holding.

Q3 — Enables service request for errors and transition to holding.

Refer to paragraph 3-16 for related GPIB data.

- 4. GPIB Talk (R) Shows the status of two parameters: The particular type of talk message that will be given when the Arb is addressed to talk over the GPIB is shown on the left of the display. A minus sign prefix and the decimal equivalent of the ASCII coded terminator character is shown on the right. The talk message codes are:

- R0 State of hold status (returns "0" if not holding, "1" if holding (I/C).

- R1 List of first nine errors since this message was last read.

- R2 Reason why this instrument is requesting service.

- R3 Current value of the setting, if any, selected by the last alphabetical character used.

Refer to paragraph 3.16.4 for details.

- 5. Ramp to Zero (G) An abort action that increments the amplitude and offset in linear steps to zero in about 15 seconds. The Arb does not respond to new inputs during ramping. "G" is not displayed until zero is reached. Press EXEC to restore prior status.

- 6. **Musical Note** Key tone (I/C) is cut out or, if out, restored.

- 7. **Reset (Z)** Sets everything to initial conditions except RAM storage (waveforms programmed are not lost as long as power is on). Initial conditions for items in paragraph 3.2.2 are annotated with (I/C).

When programming this action via the GPIB, the controller should wait for the instrument to start resetting before sending any futher commands. If the instrument microprocessor is idle, a 3 millisecond wait will suffice, but if it is busy scanning an input buffer (refer to paragraph 3.16.3), the wait required could be as long as a second. The wait is necessary to avoid losing the commands following the reset command.

8. Mode, Continuous or Triggered (B) — Shows status:

BO - Continuous (I/C).

B1 - Triggered.

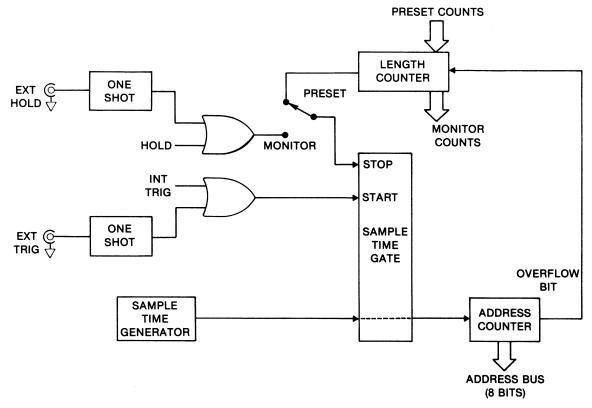

In continuous mode, the Arb continuously generates the selected waveform, and it cannot be triggered or held. In triggered mode, the Arb is idle until a trigger stimulus is received. When a trigger (J) occurs, the Arb starts to generate the selected waveform until a hold (H) command is received or, if the trigger cycle parameter (M) is set to the preset mode, until the number of blocks specified by the preset length parameter (L) have been generated. Refer to item 13 and paragraph 3.15 for details.

- 9. Clock, Internal or External (N) Shows source status:

- NO Internal 10 MHz clock (I/C).

$N1 - External clock (\leq 11 MHz)$ .

This parameter selects the source of the clock which provides timing for the waveform generator circuits. If the external clock is selected, it must be within these limits:

dc - 11 MHz, if mode is continuous (B0) 500 kHz - 11 MHz, if mode is triggered (B1)

- Clock, Time Unit (S) Shows the units used for sample time:

- S0 Seconds (I/C)

- S1 Minutes

- S2 Hours

Refer to paragraph 3.10 for conditions that affect time unit.

Clock, Sample Time (T) — Shows duration of each data point of the output waveform.

Example: T20E-6s = 20  $\mu$ s (I/C)

See paragraph 3.12 for conditions that affect sample time.

Clock, Block Rate (F) — Shows frequency of the output waveform.

Example: F195.313 Hz (I/C)

See paragraph 3.12 for conditions that affect block rate.

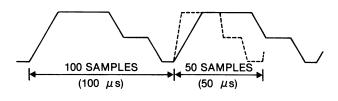

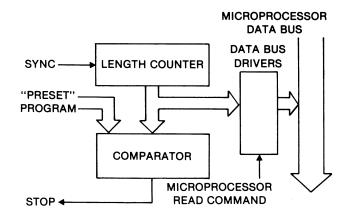

- 13. Trigger Cycle, Preset or Monitor (M) Shows status:

- M0 Preset Mode (I/C). A preset number of cycles will be output following a trigger signal. (Refer to item 14.)

- M1 Monitor Mode. When triggered (J) output is continuous.

Refer to paragraph 3.15 for details.

Trigger Cycle, Preset Length (L) — Shows the number of waveform blocks generated when a trigger (J) is received in triggered mode (B0) with preset trigger cycle mode (M0) selected.

Example: L216 – When in preset mode (M0) and triggered (J), 216 cycles of waveform will be output. L1 (I/C)

- 15. Trigger Cycle, Monitor Count (K) This is an interrogating action which reads the value of the triggered waveform cycle counter. If continuous mode (B0) is selected, the value readout is always zero. If triggered mode (B1) is selected, the value readout is the number of complete blocks generated since the generator was last triggered. While the generator is running (not holding), the cycle counter is incremented when the last point in a block is being output. When holding, the counter is not incremented. Refer to paragraph 3.15 for more details.

- 16. Block, Full or Partial (U) Shows status:

- U0 A full 256 address block (or several blocks) forms one cycle of waveform (I/C).

- U1 A partial block forms one cycle. (Refer to items 17 and 18.)

Refer to paragraph 3.11 for operation.

Block, Start Address (V) — Shows block start address of waveform.

Example: V93 — One cycle of waveform starts at address 93 in 0 - 255 block. V0 (I/C)

Block, Stop Address (W) — Shows block stop address of waveform.

Example: W107 — One cycle of waveform stops at address 107 in 0 - 255 block. W255 (//C)

19. Function (C) — Shows which memory (or memories) will be used to generate the output waveform. Values 0 - 3 select standard waveforms:

C0 - Sine (I/C)

- C1 Triangle

- C2 Square

- C3 Ramp

Values 4 - 7 select the four user-supplied PROM blocks.

- C4 PROM block 1

- C5 PROM block 2

C6 – PROM block 3 C7 – PROM block 4

Values 8 - 11 select the four programmable RAM blocks.

C8 - RAM block 1

C9 - RAM block 2

C10 - RAM block 3

C11 - RAM block 4

Values 14 - 17 select joined together, user-supplied PROM blocks. The PROMs composing these are the same ones that are selected by function codes 4 - 7.

C14 - PROM block 1 (256 points maximum)

C15 - PROM blocks 1 & 2 (512 points maximum)

C16 - PROM blocks 1, 2 & 3 (768 points maximum)

C17 - PROM blocks 1, 2, 3& 4(1024 points maximum)

Values 18 - 21 select joined together, programmable RAM blocks. The RAMs composing these are the same ones that are selected by function codes 8 - 11.

C18 - RAM block 1 (256 points maximum)

C19 - RAM blocks 1 & 2 (512 points maximum)

C20 - RAM blocks 1, 2 & 3 (768 points maximum)

C21 - RAM blocks 1, 2, 3 & 4 (1024 points maximum)

Note that a set of joined together RAM blocks may not be programmed as a unit. Each block must first be separately selected (with function codes 8 - 11) and programmed. The start and stop addresses, if selected, will be applicable to each block of stacked PROMs or RAMs.

Memory Address (X) — Gives data (Y) value at the address (X) queried.

Example: X125 33Y – At address 125 in the 0 - 255 address block, the data value is 33 in a  $0 \pm 127$  range.

This parameter is used to select the address of the data point in the waveform memory which is read and programmed by the memory data (Y) parameter. This parameter also sets the cursor register (immediately, without Execute). This register is used to cause a pulse to occur on the rear panel CURSOR OUT BNC connector whenever the data point in the waveform memory at the address stored in the cursor register is being output.

This key has an automatic increment feature. If pressed (or "X" is programmed over the GPIB) twice without pressing any other key, then the second pres-

sing will increment the memory address and display it and the data at the new address. Additional pressings will continue to increment until the sequence is broken by pressing another key. Holding the key down will continuously increment to the next address and show the corresponding data.

21. **Memory, Data (Y)** — Provides access to the waveform memory data point located at the address specified by the memory address parameter (X) in the memory block specified by the function parameter (C).

Example: Y33 – At last address (X) queried in the 0 - 255 address block, the data value is 33 in a  $0 \pm 127$  range.

This key has an automatic increment feature. If pressed (or "Y" is programmed over the GPIB) twice without pressing any other alpha key, then the second pressing will increment the memory address parameter (X) value and display the Y data at the next address. Additional pressings will continue to increment the address until the sequence is broken by pressing another alpha key. Holding the key down will continuously increment the address and data displayed.

Refer to paragraph 3-7 for operation.

Output, Off or On (P) – Shows connection or no connection between the output amplifier and the BNC connector. This parameter makes the connection by a relay.

P0 — Output to ARB OUT (ATTEN) BNC disconnected (I/C)

P1 - Output to ARB OUT (ATTEN) BNC connected

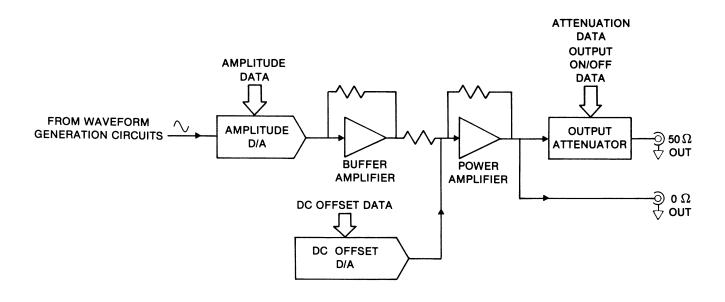

23. Output, Amplitude (A) — Shows status.

Example: A3.25V — The output voltage is 3.25V p-p into  $50\Omega$  in a range of 1 to 10V p-p. A1 (I/C)

Refer to paragraph 3.13 for operation.

24. Output, Offset (D) — Shows status.

Example: D2.05V — Output dc offset is 2.05V into  $50\Omega$  in a range of 0 ±5.00V. D0 (I/C)

Refer to paragraph 3.13 for operation.

25. Smoothing, Off or On (O) — Shows status:

O0 - Smoothing off (I/C)

O1 – Steps of data making up the waveform are smoothed for a more continuous waveform.

Refer to paragraph 3.8 for operation.

26. Manual, Hold (H) — In triggered mode (B1), pressing the key stops and holds the output at the instantaneous value. The address stopped on is shown on the readout. Trigger (J) the generator to continue output waveform. Refer to paragraph 3.15 for hold use.

Example: H102 – Holding at address 102.

- Manual, Trigger (J) Triggers the output when in trigger mode. Refer to item 13 and paragraph 3.15 for trigger use.

- 28. **Exponent (E)** Consider this key (E) as part of the numbered key group. The value keyed after E is the exponent of a X 10 multiplier.

Example:  $E6 = X \cdot 10^6$

- 29. Clear Entry Erases an incomplete numeric entry (indicated by a display with an asterisk on the right-hand side). The display is replaced by the previous value of the parameter that was being reprogrammed. This key is used to clear out a programming entry in case an incorrect key was pressed, or if the user changes his mind and decides not to change the parameter value. This key has no effect if there is no incomplete entry in progress (no asterisk on the right-hand side).

- 30. Execute (I) This key causes an execute cycle which transfers from the display memory to the waveform generator circuits the values of the following parameters:

Internal or External Clock (N)

Sample Time (T)/Block Rate (F)

Preset or Monitor Trigger Mode (M)

Preset Length of Burst (L)

Full or Partial Block (U)

Start Address (V)

Stop Address (W)

Function (C)

Output On or Off (P)

Amplitude (A)

Offset (D)

Smoothing On or Off (O)

Causing an execute cycle is the only way to update these parameters in the waveform generator circuits. An execute cycle also restores a ramp to zero (G) to the prior status. Note that the waveform memory data (Y) and cursor register (X) do not require an execute cycle; when either of them is programmed with a new value, that value is sent immediately to the waveform circuits.

Plus and Minus — Changes the sign on the displayed number. If the sign change is made after the exponent

(E) is programmed, the sign change affects the exponent only.

Example:

$$-1.25E-2 = 1.25-E-2 = -1.25E2-$$

=  $-0.0125 = -1.25 \times 10^{-2}$ .

### 3.3 POWER

Power is turned on and off with a front panel pushbutton. When power is turned on, wait approximately two seconds before programming. When the power is turned on, the Arb is ready to accept commands. At least two seconds must elapse between power off and power on for proper reinitialization of logic. When the power comes on, the Arb output is automatically disconnected to allow loading of a program; line transients on the output are avoided. The Arb must get an execute command to provide an output.

### 3.4 INPUTS AND OUTPUTS

Refer to figure 2-1 for connector locations.

**CURSOR OUT TTL Output** — This output is a positive going TTL pulse coincident and of the same width with each output of a particular data point. The data point is designated by storing its memory address in the cursor register. Refer to paragraph 3.2.2, item 20.