# PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL.

## 7S14

### DUAL TRACE DELAYED SWEEP SAMPLER

### INSTRUCTION MANUAL

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077

Serial Number \_

First Printing DEC 1973 Revised APR 1985

070-1410-00 Product Group 42

· \_-

Copyright © 1973 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and are registered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

#### INSTRUMENT SERIAL NUMBERS

Each instrument has a serial number on a panel insert, tag, or stamped on the chassis. The first number or letter designates the country of manufacture. The last five digits of the serial number are assigned sequentially and are unique to each instrument. Those manufactured in the United States have six unique digits. The country of manufacture is identified as follows:

| B000000 | Tektronix, Inc., Beaverton, Oregon, USA               |

|---------|-------------------------------------------------------|

| 100000  | Tektronix Guernsey, Ltd., Channel Islands             |

| 200000  | Tektronix United Kingdom, Ltd., London                |

| 300000  | Sony/Tektronix, Japan                                 |

| 700000  | Tektronix Holland, NV, Heerenveen,<br>The Netherlands |

## TABLE OF CONTENTS

| SECTION 1 | CHARACTERISTICS                             | Page |

|-----------|---------------------------------------------|------|

|           | General Information                         | 1-1  |

|           | Electrical Characteristics                  | 1-1  |

|           | Vertical System                             | 1-1  |

|           | Horizontal System                           | 1-2  |

|           | Environmental Characteristics               | 1-4  |

| SECTION 2 | BASIC SEQUENTIAL SAMPLING PRINCIPLES        |      |

|           | Introduction                                | 2-1  |

|           | Equivalent-Time Sequential Sampling         | 2-1  |

|           | Vertical Functions                          | 2-2  |

|           | Horizontal Functions                        | 2-4  |

|           | Glossary of Sampling Terms                  | 2-4  |

| SECTION 3 | OPERATING INSTRUCTIONS                      |      |

|           | General Information                         | 3-1  |

|           | Mainframe Controls                          | 3-1  |

|           | Getting A Trace On Screen                   | 3-1  |

|           | Front Panel Controls                        | 3-1  |

|           | Other Plug-Ins                              | 3-7  |

| SECTION 4 | APPLICATIONS                                |      |

|           | Introduction                                | 4-1  |

|           | Phase Difference Measurements               | 4-1  |

|           | X-Y Phase Measurements                      | 4-1  |

|           | Dual-Trace Phase Measurements               | 4-2  |

|           | Time Difference Measurements                | 4-2  |

|           | Two-Dot Measurements                        | 4-3  |

|           | Phase Measurements Using the Two-Dot System | 4-3  |

|           | Pulse Width Measurements                    | 4-3  |

|           | Time Between Pulses Using Dual Trace        | 4-4  |

| SECTION 5 | CIRCUIT DESCRIPTION                         |      |

|           | Vertical System                             |      |

|           | Compensation Network                        | 5-1  |

|           | Delay Line                                  | 5-1  |

|           | Sampling Gate                               | 5-1  |

|           | Sampling Gate Blow-by Compensation          | 5-1  |

|           | Strobe Generator                            | 5-1  |

|           | Preamplifier                                | 5-1  |

|           | DC Balance and DC Balance Amplifier         | 5-2  |

|           | Memory Gate                                 | 5-2  |

|           | Memory Gating Generator                     | 5-2  |

|           | Memory Gate Blow-by Compensation            | 5-2  |

|           | Memory                                      | 5-2  |

|           |                                             |      |

| SECTION 5 | CIRCUIT DESCRIPTION (cont)                                  | Page       |

|-----------|-------------------------------------------------------------|------------|

|           | Post Memory Amplifier                                       | 5-2        |

|           | Unity Gain Inverter (Channel 2 Only)                        | 5-2        |

|           | Output Amplifier                                            | 5-3        |

|           | Switching                                                   | 5-3        |

|           | Vertical Power Supplies                                     | 5-3        |

|           | Horizontal System                                           |            |

|           | Peak-To-Peak Signal Follower                                | 5-3        |

|           | HF Synchronizer Oscillator                                  | 5-3        |

|           | Trigger Amplifier                                           | 5-3        |

|           | Holdoff Ramp Generator                                      | 5-5        |

|           | Trigger Circuit                                             | 5-5        |

|           | Fast Ramps                                                  | 5.5        |

|           | Delta Delay Generator                                       | 5-6        |

|           | Buffer                                                      | 5-7        |

|           | Scan Ramp Gating Multivibrator                              | 5-7        |

|           | Interdot Blanking Pulse Generator                           | 5-7        |

|           | Inverter, Gating Generator, and Gated Current Generator     | 5-7        |

|           | Scan Ramp and Staircase Generator                           | 5-7        |

|           | Two Dot Circuit                                             | 5-7<br>5-8 |

|           | Intensity Blanking Mixer                                    | 5-8        |

|           | Position Voltage Follower & Horizontal Amplifier<br>Readout | 5-8        |

|           | Headout<br>Horizontal Power                                 | 5-8        |

|           | Horizontal Power                                            | 0-0        |

| SECTION 6 | MAINTENANCE                                                 |            |

|           | Preventive Maintenance                                      |            |

|           | General                                                     | 6-1        |

|           | Cleaning                                                    | 6-1        |

|           | Lubrication                                                 | 6-1        |

|           | Visual Inspection                                           | 6-1        |

|           | Semiconductor Checks                                        | 6-1        |

|           | Recalibration                                               | 6-1        |

|           | Troubleshooting                                             |            |

|           | Troubleshooting Aids                                        | 6-2        |

|           | Component Identification                                    | 6-2        |

|           | Troubleshooting Equipment                                   | 6-2        |

|           | Troubleshooting Techniques                                  | 6-3        |

|           | Troubleshooting Procedure                                   |            |

|           | General                                                     | 6-4        |

|           | Test Procedure                                              | 6-5        |

|           | Horizontal Checks                                           | 6-5        |

|           | Vertical Checks                                             | 6-9        |

|           | Corrective Maintenance                                      |            |

|           | Obtaining Replacement Parts                                 | 6-11       |

|           | Soldering Techniques                                        | 6-11       |

**Circuit Board Replacement**

Vertical Board Removal

Sampler Board Cover Removal

6-12

6-12

6-12

۲

| SECTION 6 | MAINTENANCE (cont)                                  | Page |

|-----------|-----------------------------------------------------|------|

|           | Sampler Board Removal                               | 6-12 |

|           | Vertical and Horizontal Interface Board Removal     | 6-12 |

|           | Delay Line Removal                                  | 6-13 |

|           | Compensation Board Removal                          | 6-13 |

|           | Trigger Board Removal                               | 6-14 |

|           | Horizontal Board Removal                            | 6-14 |

|           | Readout Board Removal                               | 6-14 |

|           | Vertical Mode Switch Board Removal                  | 6-14 |

|           | Component Replacement                               |      |

|           | Semiconductor Replacement                           | 6-15 |

|           | Connector Replacement                               | 6-15 |

|           | Push-button Switches                                | 6-16 |

|           | Rotary Switches                                     | 6-17 |

|           | Cam Switch                                          | 6-17 |

|           | Recalibration After Repair                          | 6-17 |

|           | Instrument Repackaging                              | 6-17 |

| SECTION 7 | PERFORMANCE CHECKS/CALIBRATION                      |      |

|           | Elementary Checks and Incoming Inspection           | 7-1  |

|           | Detailed Checks and Adjustments                     | 7-3  |

|           | Equipment Required                                  | 7-3  |

|           | Preliminary Connections and Set-up                  | 7-4  |

|           | Power Supply Checks                                 | 7-4  |

|           | Triggering Checks and Adjustments                   | 7.6  |

|           | Equipment Set-up                                    | 7.6  |

|           | Trigger Calibration Check                           | 7-6  |

|           | Adjustment of R212 (Trig Cal)                       | 7-8  |

|           | Sync Level Check                                    | 7-8  |

|           | Adjustment of R530 (Sync Level)                     | 7-9  |

|           | + Balance and – Balance Check                       | 7-9  |

|           | Adjustment of R524 and R521 (+ Bal and — Bal)       | 7-9  |

|           | Sync Bias Check                                     | 7-9  |

|           | Adjustment of R209 (Sync Bias)                      | 7-10 |

|           | Timing Checks and Adjustments                       | 7-10 |

|           | Equipment Set-up                                    | 7-10 |

|           | 2-Dot Cal Check                                     | 7-10 |

|           | Adjustment of R131 (2-Dot Cal)                      | 7-10 |

|           | Delay Stop Check                                    | 7-11 |

|           | Adjustment of R130 (Delay Stop)                     | 7-11 |

|           | 1 μs/Div Delaying Check                             | 7-11 |

|           | Adjustment of R132 (1 µs/Div Delaying)              | 7-11 |

|           | 1 μs/Div Delayed Check                              | 7-11 |

|           | Adjustment of R460 (1 μs/Div Delayed)               | 7-11 |

|           | Scan Rate Check                                     | 7.12 |

|           | Adjustment of R381 (Scan Rate)                      | 7-12 |

|           | Leadtime and Register Check                         | 7-12 |

|           | Adjustment of R472 and R230 (Leadtime and Register) | 7-12 |

|           | Delayed and Delaying Timing Checks                  | 7-12 |

|           | 10 ns/Div, Delaying Check                           | 7-13 |

|           | Adjustment of C350 (10 ns/Div, Delaying)            | 7-13 |

| SECTION 7 | CALIBRATION PROCEDURE (cont)                                          | Page              |

|-----------|-----------------------------------------------------------------------|-------------------|

|           | 10 ns/Div, Delayed Check                                              | 7-13              |

|           | Adjustment of C353 (10 ns/Div, Delayed)                               | 7-13              |

|           | Delayed and Delaying Timing Verification                              | 7.13              |

|           | 1 ns Linearity Check                                                  | 7-13              |

|           | Adjustment of R380 (1 ns Linearity)                                   | 7-14              |

|           | Vertical Checks and Adjustments                                       | 7-14              |

|           | Equipment Set-up                                                      | 7-14              |

|           | Channel 1 Avalanche Check                                             | 7-15              |

|           | Adjustment of R20 (Avalanche for both Channel 1 and Channel 2)        | 7.15              |

|           | Channel 2 Avalanche Check                                             | 7-16              |

|           | Delta t Center Check                                                  | 7-16              |

|           | Adjustment of R458 (Delta t Center)                                   | 7-16              |

|           | Channel 1 DC Balance, Loop Gain, and Memory Balance Checks            | 7-16              |

|           | Adjustment of R233, R232 and R242 (DC Bal, Loop Gain, and Memory Bal) | 7-17              |

|           | Channel 2 DC Balance, Loop Gain and Memory Balance Checks             | 7-17              |

|           | Adjustment of R330, R331 and R344 (DC Bal, Loop Gain, and Memory Bal) | 7-17              |

|           | Trigger Jitter Check                                                  | 7-18              |

|           | Avalanche Recheck                                                     | 7-18              |

|           | Channel 1 L.F. Comparator Check                                       | 7-19              |

|           | Adjustment of CH 1 R30 (L.F. Comp.)                                   | 7-19              |

|           | Channel 2 L.F. Comparator Check                                       | 7-19              |

|           | Adjustment of CH 2 R30 (L.F. Comp.)                                   | 7-19              |

|           | Channel 1 and Channel 2 Amplitude Attenuation Check                   | 7-19              |

|           | Channel 1 INPUT Connector Check                                       | 7-19              |

|           | Channel 2 INPUT Connector Check                                       | 7-20              |

|           | Channel 2 Amplitude Check                                             | 7-20              |

|           | Channel 1 Amplitude Check                                             | 7-20              |

|           | Readout Checks                                                        | 7-20              |

| SECTION 8 | ELECTRICAL PARTS LIST                                                 |                   |

|           | Parts Ordering Information                                            | 8-1               |

|           | Abbreviations                                                         | 8-1               |

|           | Cross Index, Mfr. Code Number to Mfr.                                 | 8-2               |

|           | Parts List                                                            | 8-3               |

| SECTION 9 | DIAGRAMS AND CIRCUIT BOARD ILLUSTRATIONS                              |                   |

|           | Block Diagrams                                                        | See Tabs          |

|           | Vertical Block Diagram                                                |                   |

|           | Horizontal Block Diagram                                              |                   |

|           | Electrical Schematics and Circuit Boards                              | See Tabs          |

|           | Compensation                                                          | $\langle \rangle$ |

|           | Samplers                                                              | $\dot{\langle}$   |

|           | Sampler Cover                                                         |                   |

|           | Trigger                                                               | ò                 |

|           |                                                                       | ~                 |

SECTION 10 MECHANICAL PARTS LIST AND MECHANICAL ILLUSTRATIONS

See Tabs

۷

• ...

.....

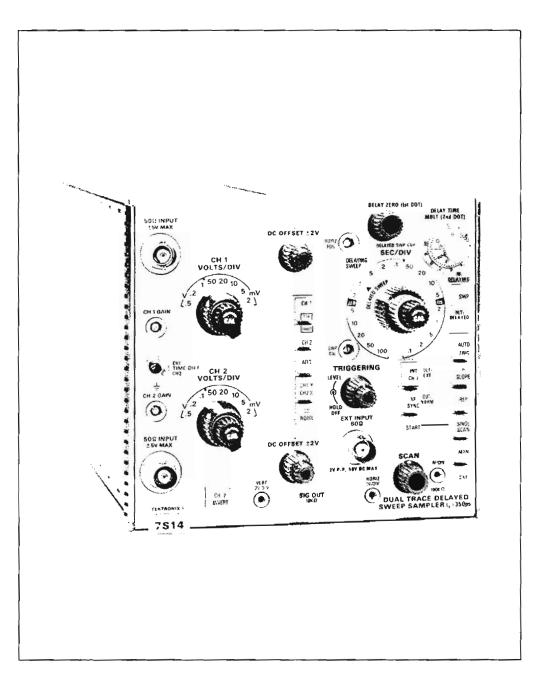

Fig. 1-1. 7S14 Dual Trace Delayed Sweep Sampler.

## CHARACTERISTICS

#### **General Information**

The Tektronix 7S14 Dual Trace Delayed Sweep Sampler is a general purpose sampling unit with a DC-to-1000 MHz bandwidth. It will operate in any Tektronix 7000 Series mainframe. The front panel terminology is similar to that of conventional oscilloscopes.

The 7S14 has two time bases to provide "delaying" and "delayed sweep" operation. The delayed sweep starts after the selected delay interval, giving the effect of a wide-range sweep operation. The delayed sweep starts after the selected delay interval, giving the effect of a wide-range sweep magnifier. The calibrated delay replaces the "time position" control found on most sampling time-base units.

The 7S14 has a two dot time-interval measurement method that provides a means of measuring the time between two points on the "normal" (delaying) display. A brightened dot on the trace can be positioned to the start of the event to be measured. A second brightened dot can be positioned to the end of the event by using the Delay Time Mult control. The time interval between the two points is the product of the reading on the Delay Time Mult dial times the Delaying Sweep Sec/Div setting.

Delay lines in the input signal channels permit display of the leading edge of the triggering waveform. The Auto Level mode provides a bright baseline in the absence of a triggering signal. Other features include 2 mV/div sensitivity, low tangential noise, versatile triggering capabilities, a broad range of sweep rates, and crt readout of both the attenuation and timing values.

The characteristics given in the following Table apply over an ambient temperature range from 0°C to +50°C after the instrument has been calibrated at +25°C  $\pm$ 5°C. Under these conditions, the 7S14 will perform to the requirements given in the Performance Check section of this manual.

The Supplemental Information column of the Table provides additional information about the operation of the 7S14. Characteristics given in the Supplemental Information column are not requirements in themselves and are not necessarily checked in the Performance Check procedure.

|                    | VERTICAL SYSTEM                                                                                                             |                                                                                         |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Characteristics    | Performance Requirements                                                                                                    | Supplemental Information                                                                |

| Rísetíme           | 350 ps or less, 10% to 90% of step pulse signal.                                                                            |                                                                                         |

| Step Aberrations   | +2%, -3%, total of 5% or less P-P within first 5 ns after step transition; +1%, $-1$ %, total of 2% or less P-P thereafter. | Check made with Tektronix 284 Pulse<br>Generator; includes aberrations from the<br>284. |

| Bandwidth (–3 dB)  | DC to 1 GHz or more.                                                                                                        | Calculated from risetime.                                                               |

| Input Resistance   | 50 $\Omega$ within 2%.                                                                                                      |                                                                                         |

| Deflection Factor  | 2 mV/Div to 0.5 V/Div.                                                                                                      | 8 steps, 1-2-5 sequence.                                                                |

| Accuracy           | Within ±3% (with VARIABLE at CAL).                                                                                          |                                                                                         |

| Variable           | At least 2.5:1.                                                                                                             | Extends uncalibrated deflection factor to approximately 800 $\mu$ V/Div.                |

| Input Signal Range |                                                                                                                             |                                                                                         |

| Maximum Operation  | $2 \vee P \cdot P$ (DC + Peak AC) within a +2 V to $-2 \vee$ window at any sensitivity.                                     |                                                                                         |

| Maximum Overload   | ±5 ∨.                                                                                                                       |                                                                                         |

#### **ELECTRICAL CHARACTERISTICS**

### ELECTRICAL CHARACTERISTICS (cont)

| Characteristics              | Performance Requirements                                                | Supplemental Information                        |

|------------------------------|-------------------------------------------------------------------------|-------------------------------------------------|

| DC Offset Range              | +2 V or more to $-2$ V or more.                                         |                                                 |

| Displayed Noise (tangential) | 2 mV or less, LOW NOISE switch "out".                                   |                                                 |

| Low Noise Operation          | Displayed noise reduced by at least five times.                         |                                                 |

| Vertical Signal Out          | 0.2 V/Div of deflection ±3%.                                            | Source resistance is 10 k $\Omega$ ±0.5%.       |

| Dot Slash                    | Less than 0.1 Div at 10 Hz and above.                                   |                                                 |

| Interchannel Crosstalk       | -60 dB or less.                                                         | When input signal is 0.5 GHz sine wave.         |

| ΔT Range                     | Shifts Channel 2 at least $+1$ ns to $-1$ ns with respect to Channel 1. | Range may be centered with internal adjustment. |

#### **VERTICAL SYSTEM** (cont)

#### HORIZONTAL SYSTEM

### Delaying Time Base

| Time Base Range       | 100 µs/Div to 10 ns/Div.                                                                                      | 13 steps, 1-2-5 sequence.                                                                                                                                          |

|-----------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Time Base Accuracy    | Within ±2%, excluding first ½ division of displayed sweep.                                                    | No time mark between 1st and 9th<br>divisions can be more than 0.2 divisions<br>from the major division line when the 1st<br>mark is set on the 1st division line. |

| Delay Zero Range      | 0-9 divisions or more.                                                                                        | When Delay Time Multiplier is set to<br>0.00, the 1st dot can be moved past the<br>9th graticule line.                                                             |

| Delay Time Multiplier | Each turn equal to 1 crt division.                                                                            | Delaying Time/Div X Delay Time Mult =<br>Time between dots.                                                                                                        |

| Delay Accuracy        | Within 1% of full screen (10 crt divisions)<br>when measurement is made between 1st<br>and 9th crt divisions. |                                                                                                                                                                    |

#### **Delayed Time Base**

| Time Base Range | 100 µs/Div to 100 ps/Div.                                  | 19 steps, 1-2-5 sequence.                                                                                                                                         |

|-----------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Accuracy        | Within ±3%, excluding first ½ division of displayed sweep. | No time mark between 1st and 9th<br>divisions can be more than 0.3 divisions<br>from the major divison line when the 1st<br>mark is set on the 1st division line. |

| Variable        | At least 2.5:1.                                            | Extends uncalibrated Time/Div to ap-<br>proximately 40 ps/Div.                                                                                                    |

### **ELECTRICAL CHARACTERISTICS (cont)**

#### HORIZONTAL SYSTEM (cont)

| Characteristics         | Performance Requirements                                          | Supplemental Information                                                                                                                                                                                                                                              |

|-------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fime Base Display Modes |                                                                   |                                                                                                                                                                                                                                                                       |

| Delaying Time Base      |                                                                   | Conventional display, maximum lead<br>time. Left intensified dot indicates Time<br>Zero (Multiplier Zero). Right intensified<br>dot indicates point at which Delayed<br>Sweep starts. Time between dots is read<br>from the crt or the Delay Time Multiplier<br>dial. |

| Delayed Time Base       |                                                                   | Delayed sweep display starts immediately<br>at end of delay time. Set by Delay Zerc<br>plus Delay Time Multiplier. Operates in<br>same manner as "run after delay" mode<br>in conventional oscilloscopes except Time<br>Zero is adjustable and identified.            |

| friggering              |                                                                   |                                                                                                                                                                                                                                                                       |

| Amplitude Range         |                                                                   |                                                                                                                                                                                                                                                                       |

| External                | 10 mV to 2 V, P-P.                                                | Rate of rise, 10 mV/ $\mu$ s or faster.                                                                                                                                                                                                                               |

| Internal                | 50 mV to 2 V, P-P.                                                | At Sampler Input (vertical input signal)<br>Rate of rise, 50 mV/μs or faster.                                                                                                                                                                                         |

| Input Resistance        | 51 $\Omega$ within ±10%, AC coupled.                              |                                                                                                                                                                                                                                                                       |

| Jitter                  | Less than 40 ps with 50 mV, 5 ns width trigger at external input. |                                                                                                                                                                                                                                                                       |

|                         | Less than 30 ps when internally triggered<br>from 284 pulse.      |                                                                                                                                                                                                                                                                       |

#### NORMAL Triggered Mode

| Sine waves        | 150 kHz to 100 MHz. |  |

|-------------------|---------------------|--|

| Pulse             | 10 Hz to 100 MHz.   |  |

| Minimum Rise Rate | 10 mV/µs.           |  |

#### AUTO TRIG Mode (Auto baseline when not triggered)

| Sine waves          | 150 kHz to 100 MHz.         |                             |

|---------------------|-----------------------------|-----------------------------|

| Minimum Amplitude   | 10 mV P-P at 100 MHz (Ext). |                             |

| Pulse               | 1 kHz to 100 MHz.           | Auto baseline below 800 Hz. |

| Minimum Pulse Width | 10 ns at 1 kHz.             |                             |

| Minimum Rise Rate   | 10 mV/µs.                   |                             |

### ELECTRICAL CHARACTERISTICS (cont)

| HORIZONTAL SYSTEM (cont)              |                                                                              |                                                                                                                                                                                                                                                                                                         |

|---------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristics                       | Performance Requirements                                                     | Supplemental Information                                                                                                                                                                                                                                                                                |

| HF SYNC Mode                          |                                                                              |                                                                                                                                                                                                                                                                                                         |

| Sine waves                            | 100 MHz to 1 GHz.                                                            | Free-Running Sync.                                                                                                                                                                                                                                                                                      |

| Scan Controls                         |                                                                              | <b>↓</b>                                                                                                                                                                                                                                                                                                |

| Repetitive                            | 25-40 Hz Repetition Rate.                                                    | Repetition rate barely into flicker rate.<br>Controls must be set as follows:<br>Low Noise Control, out;<br>HF SYNC Control, in;<br>Scan Control, fully CW;<br>Holdoff control, fully CCW;<br>Delaying sweep, 1 µs/Div or faster;<br>Approximately 20 samples per div at low<br>trigger or sweep rates. |

| Single Sweep                          | One sweep per Single Sweep Start button depression.                          | Scan Rate is the same as set in Repetitive mode.                                                                                                                                                                                                                                                        |

| Manual                                | Scan control moves the spot over a slightly greater range than 10 divisions. |                                                                                                                                                                                                                                                                                                         |

| Ext Scan                              |                                                                              |                                                                                                                                                                                                                                                                                                         |

| Maximum Sensitivity                   | 1 V/Div within ±5%.                                                          | Scan control serves as an attenuator, Full<br>scale scan signal must run from 0 V to<br>+10 V or more.                                                                                                                                                                                                  |

| Maximum Input Voltage                 | 150 V.                                                                       |                                                                                                                                                                                                                                                                                                         |

| Horizontal Output Signal<br>Amplitude | 1 V/Div ±5%.                                                                 | Source resistance is 10 k $\Omega$ within ±0.5%.                                                                                                                                                                                                                                                        |

#### ENVIRONMENTAL CHARACTERISTICS

| Characteristics                | Description                                                      |  |

|--------------------------------|------------------------------------------------------------------|--|

| Temperature                    |                                                                  |  |

| Operating Range                | 0°C to +50°C.                                                    |  |

| Non-operating Range            | $-40^{\circ}$ C to $+70^{\circ}$ C.                              |  |

| Altitude                       |                                                                  |  |

| Operating Range                | To 15,000 feet.                                                  |  |

| Non-operating Range            | To 50,000 feet.                                                  |  |

| Vibration Range                | To 0.025 inch peak-to-peak displacement at 55 cycles per second. |  |

| Shock Range                    | To 30 g, ½ sine, 11 milliseconds duration.                       |  |

| Transportation (Non-operating) | Meets National Safe Transit Test Requirements.                   |  |

### BASIC SEQUENTIAL SAMPLING PRINCIPLES

#### Introduction

Sampling provides the means to display fast-changing signals of low amplitude that cannot be displayed in any other way. Sampling overcomes the gain-bandpass limitation inherent with conventional amplifiers and oscilloscopes. It does so by displaying a real-time signal in "equivalent" time. Only the input stage of a sampler is subjected to the input signal; all subsequent signal amplification takes place through relatively low bandwidth amplifiers.

Sampling, however, does require repetitive input signals. Fortunately, most fractional-nanosecond risetime signals exist in low impedance environments; thus they may be delivered directly through 50 ohm cables to a 50 ohm load. They are generally low amplitude signals, so 50 ohm attenuators are used when the signal is more than one or two volts.

There are three types of sampling: sequential, random, and real-time. The 7S14 uses the sequential sampling method; this technique will be discussed in this section of the manual.

#### Equivalent-time Sequential Sampling

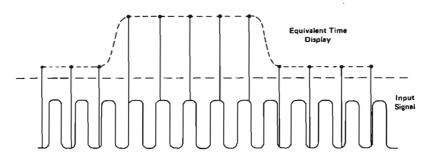

The sampling system looks at the instantaneous amplitude of a signal during a specific small time period, remembers the amplitude, and displays a single dot on the crt that corresponds to the amplitude. The horizontal position of the dot represents the equivalent time when the sample was taken. After a dot is displayed for a fixed amount of time, the system again looks at the instantaneous amplitude of a different cycle of the input signal. Each successive look, or sample, is at a slightly later time in relation to a fixed point of each sampled signal cycle. After many cycles of the input signal, the sampling system has reconstructed and displayed a single facsimile made up of many samples, each sample taken in sequence from a different cycle of the input signal; thus, the term "sequential sampling".

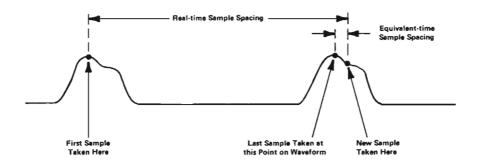

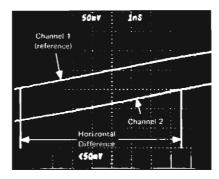

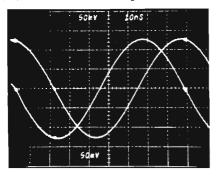

Because the reconstructed signal is not completed until long after the first signal cycle has occurred, it is not displayed in "real" time. The time displayed on the crt is termed "equivalent-time". Such a display is shown in Fig. 2-1. The equivalent time between dots is determined by the time delay between the fixed point on the signal at which sweep triggering occurs and the point at which the sample is taken. The real-time and equivalent-time relationship is depicted in Fig. 2-2. Since both time references (triggering and sampling) are taken from the same cycle of the signal, the signal repetitions do not have to be identical in amplitude, time duration, and shape. Periodic differences in individual cycles, however, will show as noise or jitter in the reconstructed display if the shape or amplitude changes from cycle to cycle.

The number of dots per horizontal division in one sweep is called dot density. Since only one sample is taken from any particular input cycle, the time needed to reconstruct a display depends on the dot density and the repetition rate of the signal. The greater the dot density and the slower the repetition rate, the longer the time to construct the equivalent-time display.

Sampling systems have maximum signal repetition rates at which samples can be taken and accurately displayed.

Fig. 2-1. Input pulse of a repetitive real-time signal is reconstructed in an equivalent-time display via sequencial sampling.

Fig. 2-2. Real-time and equivalent-time relationship.

The primary limit is the time needed for the vertical amplifiers to stabilize after a sample has been taken. For signals with a repetition rate higher than 30 kHz, the timing unit holds off retriggering for a maximum of approximately  $35 \,\mu$ s. This means that a sample will not be taken from every cycle of a high repetition rate signal; only those cycles are sampled that occur after the end of the trigger holdoff. If the signal is truly repetitive and each cycle is identical, these "missed" cycles are of little significance.

Signals below 30 kHz may have considerable repetitive rate jitter, but the sampling oscilloscope can still give a sample of each cycle without display jitter because triggering and sampling both occur on the same cycle.

#### Vertical Functions

The sampling oscilloscope's vertical stages perform the same basic functions as those in a nonsampling oscilloscope: i.e., signal amplification and attenuation. Vertical signal delay is also used to permit viewing a signal's leading edge.

All the amplification and signal processing in the sampling oscilloscope (except for the passive 50 ohm input) is done at relatively low frequencies. It is this feature that makes the sampling oscilloscope unique in performance and design.

Sampling begins with the input signal being changed to stored, long duration, low frequency voltages consisting of brief portions (samples) of the input. This change is not a frequency conversion; rather, it is a different way to represent the input signal. The sampled energy is stored in a memory circuit so that it stays constant between samples. Each time a new sample is taken, the memory is refreshed. The amount of sampled and stored energy represents the amplitude of the input signal when that sample is displayed on the crt.

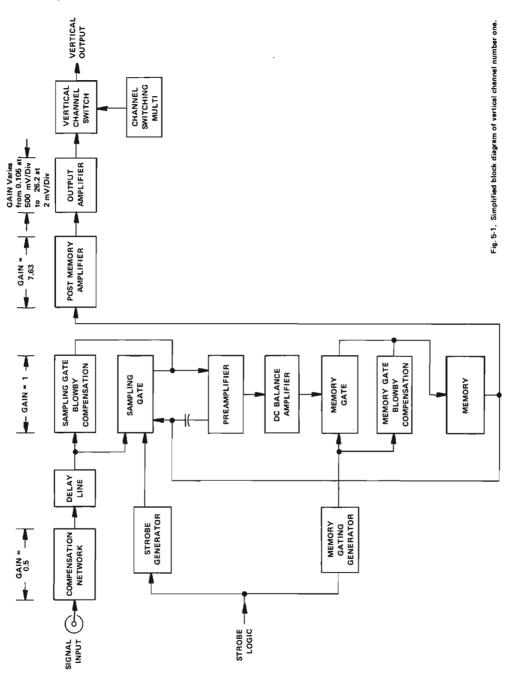

Vertical stages in a sampling oscilloscope include some not found in a nonsampling oscilloscope, such as a Sampling Gate, Blow-by Compensation, Preamplifier, Memory Gate, Memory Amplifier and Feedback, and Memory Gating Generator. Circuit descriptions for these stages appear in Section 5. In summary, stage purposes are: Sampling Gate samples brief portions of the input signal; Blow-by Compensation nullifies unwanted signal coupling; Preamplifier and Memory Amplifier and Feedback keep the Sampling Gate output and Memory constant between samples, making the Sampling Gate output proportional to its input; the Memory Gate passes the sampled signal to the Memory; and the Memory Gating Generator turns on the two gates.

An important part of the sampling process is a sampling loop. This loop provides in-phase feedback of the sampled and memory energy to the Sampling Gate output. The feedback forms a null-seeking servo loop that attempts to make a zero difference between the Sampling Gate input and output.

When the gain of the feedback loop is unity, it compensates for the attenuation across the Sampling Gate. In this case, the feedback voltage equals the value of the sampled input signal voltage. When the loop gain is less than unity, the feedback voltage is less than necessary to equalize the voltage across the gate. The Memory output and feedback will then approach the signal asymptotically after several samples have been taken. The Memory output is effectively a moving average of several preceding samples. When the loop gain is greater than unity, the feedback voltage is greater than the Sampling Gate input signal. The resulting crt display of a step signal input will alternately overshoot and undershoot for a few samples. For the least display distortion, the loop gain must be unity, allowing the system to track the input signal as closely as possible.

A loop gain of less than unity can be useful, if the resulting condition is understood and the system is operated properly. Random noise in the display is reduced when loop gain is less than unity, since several consecutive samples are averaged. The averaging, however, will slow the risetime of an abrupt step signal depending on the number of dots in the step transition and how much less than unity the loop gain may be. Averaging will also reduce the amplitude of a sine wave if there are not enough dots per cycle. When the memory gate is open, it passes the sampled signal and charges a capacitor in the memory gate output. This stored charge remains essentially constant until another sample is taken. The memory output is not reset to zero after a given sample, but is held at the level of the previous sample by the feedback signal.

In the memory gate output there is a LO NOISE control that reduces the random noise seen at high sensitivities. The function of this control is known as "smoothing," in that it smoothes or averages several consecutive samples. A check for whether smoothing is producing any distortion is accomplished by increasing the number of dots in the display with the SCAN control and observing whether there is any significant change in the waveform.

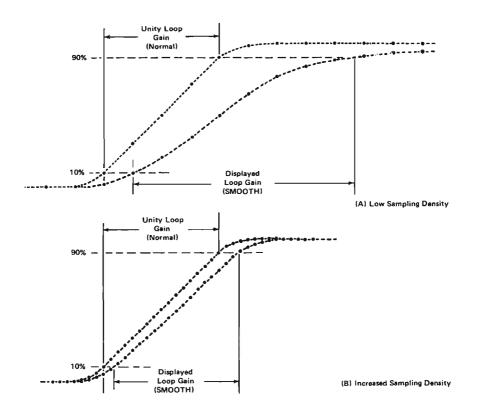

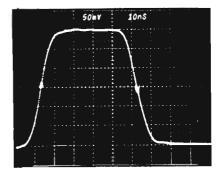

Fig. 2-3 shows the usual effects of smoothing for two different sampling densities (sampling density or dot density is the number of samples or dots per horizontal division).

Fig. 2-3. Equivalent-time display with and without smoothing for two different sampling densities.

#### **Basic Sequential Sampling Principles-7S14**

The signal out of the memory gate gets amplified by the memory circuit. Each change in voltage at the memory output is a step change proportional in amplitude to a step at the input to the preamplifier.

On sampling systems having two input channels, such as the 7S14, there are two sets of sampling-loop circuits. The output from each of the memories is fed to a channel switching multivibrator that selects which output each dot represents, so that either channel can be displayed, or so that both channels can be displayed, as two traces, by alternating outputs with each successive dot.

#### **Horizontal Functions**

The Horizontal system provides deflection voltage for the crt display and simultaneously controls the time at which the vertical system samples the input signal. The system uses (1) a 1 GHz trigger circuit, (2) two fast ramps for either Delaying sweep or Delayed sweep operation, (3) a combination scan ramp and staircase generator to provide horizontal deflection and a comparison level for the fast ramps, (4) two intensified positionable dots to provide an accurate dial read-out for time measurements and (5) a delay generator to provide strobe drive to the two vertical channels so that the signal at one input channel may be sampled consistently earlier than, later than, or coincident with the signal at the other input.

The sampling oscilloscopes's horizontal sweep is produced by a staircase voltage that advances one step each time a sample is taken. One cycle of the input signal causes the trigger circuit to initiate one cycle of the sampling process and produce one dot for the display.

The sampling cycle starts when the trigger circuit recognizes a point in a cycle of the triggering signal and unclamps the fast ramp generator. The fast ramp generator produces a linear rundown voltage that is compared to the slowly changing staircase voltage. The resulting pulse that occurs the instant the fast ramp voltage level equals the staircase voltage level is sent to the vertical circuit via the Delta Delay Generator as a strobe drive pulse. From there the store also goes to the Scan Ramp and Staircase Generator as a staircase-advance pulse.

The staircase generator advances one step just after the sampling circuit takes a sample of the input signal. The sampling memory output is applied to the vertical amplifier and the staircase output level is applied to the horizontal deflection system of the oscilloscope. As soon as the sample has been taken, a dot is displayed on the crt screen at a vertical position proportional to the input signal voltage level at the instant it was sampled. The dot then remains stationary on the screen until another sample is taken.

Each subsequent recognized triggering signal cycle initiates the same sequence of events. But since the staircase voltage moves down one step each time, the fast ramp has to run slightly farther each time before a comparison pulse is produced. In this way the sampling event is delayed by successively longer intervals and the samples are taken successively later along the waveform with respect to the triggering point. Each time a sample is taken, the crt is blanked momentarily while the dot on the crt moves horizontally by one increment.

The 7S14 contains a "two-dot circuit" that provides two bright dots for each trace. With the two dot circuit it is possible to position the dots to two specific points in the waveform and measure the time interval between the points directly from the 2nd dot positioning control.

#### **Glossary of Sampling Terms**

There are many terms used in the discussion of sampling systems whose definitions may not be universal. The following terms, used in this manual, have been compiled to help avoid confusion.

- Blow-by-A display aberration resulting from signal-induced displacement current through all capacitance shunting the Sampling Gate.

- **Display Window**—The particular time interval represented within the horizontal limits of the graticule.

- Dot-A displayed spot indicating the horizontal and vertical coordinates of a particular sample.

- Dot Density-The number of dots per horizontal division in any one scan.

- Equivalent Time-The time scale represented in the display of a sampling oscilloscope operating in the equivalenttime sampling mode.

- Equivalent-time Sampling—A sampling process in which a least one repetitive signal event is required for each sample taken. The time required for display construction is thus greater than the time represented in the display.

- Fast Ramp or Slewing Ramp-A linear ramp which acts with a slower staircase, ramp, or other changing voltage to cause slewing.

- Feedback-The effective intersample attenuation in the signal path between Memory output and Sampling Gate output in a sampling loop.

- Forward Gain-The effective gain between the Sampling Gate output and Memory output in a sampling loop.

- Loop Gain-The product of sampling efficiency, forward gain and feedback attenuation in a sampling loop. Loop gain is normally unity except in a smoothed display where it may be less than unity.

- Memory-A circuit which stores the vertical (or horizontal) coordinate value of a sample.

- Memory Gate-An electronic switch between a Memory and its driving amplifier.

- Pretrigger-A trigger signal which occurs before a related signal event.

- Real Time-The time scale associated with signal events.

- Sampling-A process of sensing and storing one or more instantaneous values of a signal for further processing or display.

Sampling Efficiency-The ratio of the voltage change between the instant before sampling, t<sup>-\*</sup>, and the instant after sampling, t<sup>+\*</sup>, at the output of a Sampling Gate to the difference between gate input voltage, E<sub>i</sub>, and gate output voltage, E<sub>a</sub>, at the instant before sampling.

$$E = \frac{E_{o}(t^{+}) - E_{o}(t^{-})}{E_{i}(t^{-}) - E_{o}(t^{-})}$$

- Sampling Gate-An electronic switch which conducts briefly upon command for the purpose of collecting and storing the instantaneous value of a signal.

- Sampling Loop-Those circuits providing the main signal path through the Sampling Gate, Preamplifier, Loop Gain attenuator, DC Balance Amplifier, Memory Gate, Memory, and the Feedback attenuator.

- Scanning-The process by which slewing is controlled.

- Sequential Sampling-A sampling process in which samples are taken at successively later times relative to a fixed point of each sampled signal cycle.

- Slewing-The process of causing successive samples to be taken at different instants relative to a fixed point of each sampled signal cycle.

- Smoothing-A process that reduces the effect of random noise or jitter in the display by averaging several consecutive samples.

- Strobe-A pulse of short duration which operates the Sampling Gate.

### OPERATING INSTRUCTIONS

#### General Information

The 7S14 is a double-width plug-in unit containing both vertical and horizontal deflection circuits. The 7S14 operates in any Tektronix 7000 Series mainframe when the unit is completely inserted into the proper two slots of the mainframe plug-in compartment. When inserted into mainframes that accommodate three single-width plug-ins, the two slots toward the operators right should be used. The middle two slots should be used in four-hole mainframes.

#### NOTE

When the 7S14 is used in the R7603, R7613, R7623, or R7903 rackmount instruments, the support posts between the rackmount plug-in compartments must be removed so that the dual width 7S14 can be inserted into the mainframe.

A blank plug-in panel may be used to cover the opening of any slot not occupied by a plug-in unit. Use panel 016-0155-00 for 7000 Series mainframes.

Assuming it is clean and dry, the plug-in unit is ready to operate as soon as it has been correctly installed in the mainframe. However, the mainframe power cord must first be plugged into a power outlet that supplies AC voltage of the correct frequency and amplitude and the mainframes power switch must be turned on. It should not be necessary to turn the power off before removing or inserting the plug-in unit.

#### **Mainframe Controls**

Besides the power switch, there are other switches and controls on the mainframe that must be set for the 7514 to operate correctly. If you are not already familiar with the functions of the mainframe controls you may need to refer to the instruction manual for that mainframe.

#### Getting A Trace On Screen

With power applied and the plug-in properly inserted, the next step is to get a trace on screen. The recommended procedure is to (1) temporarily disconnect any vertical input or trigger input signals, (2) select the repetitive scan mode by pushing the REP button, (3) select 1 $\mu$ s per division or faster for the DELAYING SWEEP (dark gray) control, (4) free-run the time base and sampling circuits by pushing the AUTO TRIG and HF SYNC buttons, (5) select Channel 1 Vertical input by pushing the CH 1 button, (6) set the Channel 1 VOLTS/DIV control to the least sensitive position, counterclockwise to .5 V, (7) center the Channel 1 DC OFFSET controls, and (8) adjust the mainframe crt intensity control for a medium bright trace. If a trace does not appear under these conditions, it is likely that either some mainframe control was incorrectly set, or that the mainframe or plug-in unit is not functioning properly.

#### **Front Panel Controls**

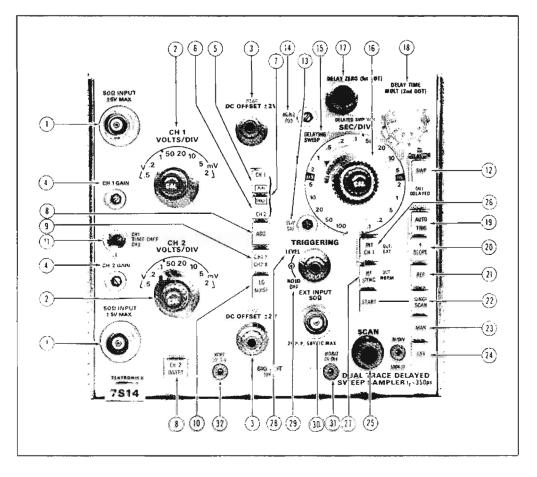

A brief description of the purpose and use of each front panel connector, pushbutton, control, and screwdriveradjustment on the 7S14 follows. If you have never operated a sampling oscilloscope, you should read the entire section before proceeding to display a signal waveform. You should refer to Fig. 3-1 as a guide to specific operating instructions relating to each front panel control or connector.

1. 50 Ω INPUT ±5 V MAX

These are input connectors to both Channel 1 and Channel 2 sampling gate circuits and vertical deflection amplifiers. Signals as large as 2 V P-P in amplitude may be handled, as long as no swing exceeds +4 volts or -4 volts. However, peak signal excursions that exceed +2 volts or -2 volts cannot be displayed at the more sensitive setting, even when using maximum DC OFFSET. Voltage greater than ±5 volts may alter the accuracy of precision delay line compensation resistors or cause input circuit components to fail. External probes or 50 ohm attenuators should be used to display signal voltages greater than 4 volts. The following probes are recommeded: P6056, 10X probe; P6057, 100X probe; P6201, 1X, 10X and 100X FET probe. You will need a 1101 Power Supply for the P6201 probe if the mainframe does not have a probe power output jack. The BNC 50 ohm attenuators recommended are: 011-0059-02 (10X), 011-0060-02 (5X), and 011-0069-02 (2X). Signals as great as ±20 volts peak or 14 volts RMS may be applied to these attenuators before exceeding the wattage rating, 50 ohm attenuators having connectors other than the BNC type may be used if adapters to BNC connectors are available.

Fig. 3-1. Key to Operating Instructions.

2. CH 1 VOLTS/DIV and CH 2 VOLTS/DIV The puter control selects the vertical deflection factor from .5 V/Div to 2 mV/Div. The red variable control (CAL) adjusts sensitivity over a range of at least 2.5 to 1. The two cortrols provide any sensitivity between .5 V per division and .8 mV per division. The CAL control must be set in the fully counterclockwise (detented) position before the indicated deflection factor can be expected to be accurate. 3. DC OFFSET ±2 V These two controls position the display up or down or position a signal on screen that otherwise may be off screen. A signal riding on a DC level as great as +2 volts or -2 volts may be positioned to center screen. The FINE control makes it easier to precisely position the display at high sensitivities.

4. CH 1 GAIN and CH 2 GAIN These screwdriver adjustments set the gain of the corresponding channels so that the chosen deflection factor corresponds to the deflection displayed on the crt by a signal voltage of known amplitude. For example, a signal of precisely 1 volt P-P amplitude should produce five divisions of deflection when the VOLTS/DIV is .2 V. Each adjustment should normally be checked each time a plug-in is placed in a different mainframe.

The applied signal voltage should be from a 50 ohm source so that the voltage arriving at the input may be precisely one half of the open circuit, unloaded voltage value.

9. CH 1 Y

CH 2 X

- 5. CH 1 Push this button to display a signal at Channel 1 input.

- 6. CH 2 Push this button to display a signal at Channel 2 input. There is no internal signal pickoff from Channel 2 input; internal triggering is from the signal picked off from Channel 1. Therefore, if you have only one input signal it should be connected to CH 1 input unless you use an external trigger input signal or using a power divider, first divide the signal so part may be applied to the external trigger input jack.

- 7. DUAL TRACE Dual trace operation is achieved by pushing both CH 1 and CH 2 buttons at the same time.

- 8. ADD Pushing the ADD button allows the signals at CH 1 INPUT and CH 2 and CH 2 INVERT INPUT to be, in effect, summed. Actually, the summing operation is performed on the sampled replicas of the two input signals following the vertical channel memories. This button should normally be pushed when two balanced, push-pull signals are applied to the CH 1 and CH 2 INPUTS. You may then also push the CH 2 INVERT button to achieve, in effect, differential input operation. Or, if you wish to see how similar the two halves of the

push-pull signal may be, any difference between them can be displayed by leaving the CH 2 IN-VERT button out.

To display the difference between two similar signals that have nearly the same polarity or phase and the same amplitude, the CH 2 INVERT button should be pushed.

#### NOTE

A front panel screwdriver adjustment (CH 1-TIME DIFF-CH 2) can be set for very precise phase or time comparisons. Refer to a later discussion of the purpose of that control.

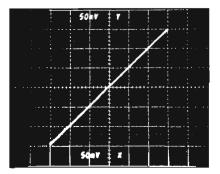

This button should be pushed for X-Y displays, such as Lissajous patterns. The signal applied to the Channel 1 input produces vertical deflection (Y) in the normal way and the signal applied to the Channel 2 input produces horizontal deflection (X). When using this mode, neither the DELAYING SWEEP nor DELAYED SWEEP controls affect the display in any way, except to change the maximum possible number of samples per second. Set the DELAYING SWEEP time per division to 10 ns and the triggering HOLDOFF control fully counterclockwise to ensure the greatest possible number of samples per second. The cleanest X-Y displays are achieved by triggering or synchronizing in the usual way before pushing the CH1 Y-CH 2 X pushbutton,

10. LO NOISE Push this button to reduce the amplitude of random noise in the display or, in some cases, to reduce horizontal time-jitter. It is normal for the horizontal scan rate to reduce greatly when this button is pushed.

11. CH 1 TIME DIFF CH 2 This screwdriver control should normally be set (and is set at the factory) so that identical signals applied to the two inputs will be displayed in precisely the same horizontal positions. For example, if a single signal is applied to the middle port of a coaxial tee and the output from each of the other two ports is applied through similar cables of precisely equal length to the two input channels, a dual trace display should show two nearly identical waveforms that can be made to coincide with the DC OFFSET controls. If a very fast step-signal is applied in this manner and displayed at 100 ps per division, the fast edge of either signal may be seen to be positionable horizontally with the CH 1-TIME DIFF-CH 2 control so as to occur before, after, or coincident with the fast edge of the other input signal.

13. SWP

CAL

Although this control should normally be left set so two such signals can be made to coincide, the control may also be deliberately set to other positions to (1) compensate for the delay difference in two input cables or (2) critically compare two similar repetitive signals that do not occur simultaneously. If you wish to use this control to critically compare two such signals that occur at widely separated instances, two similar cables of unequal length may be used at the proper inputs if the difference in length is chosen to introduce a propagation delay difference nearly equal to the time between the events. Most coaxial cables, i.e., those made with a dielectric of solid polyethylene, cause a signal delay of approximately 1.5 ns per foot (50 ps per cm). The delay through most other cables will be less; some nearly as little as 1 ns per foot

12. SWP Push this button to display a signal (MODE) when sweep delay is not needed, unless the time per division must be less than 10 ns. Pushing this button allows the Delaying Sweep to determine the ort time per division.

time per division. When the Delayed Sweep is selected to determine the crt time per division, the delaying sweep ramps are used in conjunction with the

Releasing the button allows the

Delayed Sweep to determine the crt

DELAY ZERO and DELAY TIME MULT controls to select the delay needed to display the signal of interest.

This screwdriver adjustment sets the amplitude of the horizontal output signal (to the mainframe) to produce the correct deflection on the crt to correspond with any time per division selected. Ideally, the adjustment should be checked using a time mark generator each time the 7S14 is placed in a different mainframe, However, if internal adjustments in the plug-in are set correctly, the SWP CAL adjustment may be set using the two intensified dots displayed in each trace when using the Delaying Sweep mode. There should be precisely 8 divisions of separation between corresponding parts of the two dots when (1) the Delaying Sweep is set to 1 us per division. (2) the DELAY TIME MULT dial is set to 8.00, and (3) the DELAY ZERO control is set to position the first dot one horizontal division from the left edge of the crt graticule.

14. HORIZ POS This screwdriver adjustment should be used to set the left edge of a trace even with the left edge of the crt graticule after the SWP CAL adjustment has been made.

15. DELAYING SWEEP The time indicated between the orange lines on the clear plastic skirt of the DELAYING SWEEP (dark gray) control is the crt time per division when the Delaying Sweep has been selected (SWP mode button pushed in).

16. DELAYED The time indicated at the point of the arrow on the clear plastic skirt SWEEP of the DELAYED SWEEP (light gray) control is the crt time per division when the Delayed Sweep has been selected (SWP mode button released). Be sure that the concentric, red CAL control is counterclockwise in the detented position: otherwise, the indicated time per division will not be correct. The CAL control varies the time per division over a range of at least 2.5 to 1.

SWEEP control multiplied by the

number indicated by the dial. Pre-

cise time interval tests of whether

the time between two particular

points in a waveform is greater than or less than a given amount may be

quickly made by first separating the

dots by the right amount, then

positioning them with the DELAY

ZERO control to see whether the

distance between dots is more than or less than the distance between

the two particular points in the

waveform.

To reduce delay time-jitter and to increase scan rate, the time per division of the Delaying Sweep should be as close as possible to the time per division of the Delayed Sweep. Ten divisions of delay is available when both sweep rates are the same. When more than ten divisions of delay is needed, the Delaying Sweep time per division must be set to be greater. If set to be 1,000 times longer, 10,000 divisions of delay is available, but delay time-jitter may be as much as ½ division.

When using the Delaying Sweep

mode, this control is used to set the

position of the first intensified dot

in the trace to a point in the displayed waveform suitable to be

called time-zero, a beginning refer-

ence point for a time interval

measurement. You will notice that

this control usually moves the

second dot as well. If, in some

cases, it appears that you cannot

position the first dot as far to the

right as you may wish, it is probably because the second dot is at

the right end of the trace. You may

17. DELAY ZERO (1st DOT) 19. AUTO TRIG

21. REP

22. SINGL

and

SCAN

START

AUTO Push this button for nearly every TRIG triggering signal or condition you may encounter, except when the triggering signal has a frequency or

may encounter, except when the triggering signal has a frequency or repetition rate less than about 800 hertz. When this button is pushed, strobe pulses are automatically generated (at about 800 hertz) when no triggering signal is being delivered or recognized. This keeps the sampling memories refreshed, produces a slow moving scan and keeps the crt beam positionable on screen even in the absence of a triggering signal.

20. + Push this button when you wish to SLOPE trigger on the positive-going portion of a signal. Release the button when you wish to trigger on a negative-going portion. The position of the button is immaterial when the HF SYNC button is pushed.

> The REP button should be pushed whenever repetitive scans (sweeps) are desired, which is the condition for most normal uses.

> > Push the SINGL SCAN button when you wish to produce only one scan at a time; this scan is displayed on command by the START button. This mode is useful when photographing waveforms where the scan repetition rate is low, or for stored displays when using an oscilloscope mainframe having a storage crt. It is also recommended when making chart recordings using the VERT and HORIZ output signals. Note that each scan starts when the spring loaded START button is released, not when it is

avoid this condition by running the DELAY TIME MULT dial completely counterclockwise first. 18. DELAY TIME MULT (2nd DOT) between the first and second bright

This dial controls the separation MULT (2nd DOT) between the first and second bright dots in a trace when the Delaying Sweep mode is selected. It controls the position of only the second dot until the second dot is positioned to the right end of the trace, at which time it continues to control the separation between dots by moving the first dot to the left. The point in a waveform identified by the second dot is the point corresponding to the left edge of the trace that you display when you switch from the Delaying Sweep mode to the Delayed Sweep mode (SWP mode button released).

> The number indicated on the dial is proportional to the separation between dots; one turn equals one division. The time between dots is equal to the time indicated between the orange colored lines on the skirt of the clear plastic DELAYING

pushed. The HORIZ output voltage returns to -5 volts when the START button is pressed and remains at about +5 volts at the completion of each scan. When driving a chart recorder, the START button should be held in while the recording apparatus is being set. The scan rate should be very slow when making chart recordings. Refer to the discussion about the SCAN control knob and the LO NOISE pushbutton, to set the scan rate as low as desired.

23. MAN

Push this button when you wish to scan the crt manually, instead of with the internally generated scanning ramp signal or with an externally supplied scanning signal. The scan control determines the point being sampled. This mode is particularly useful when you wish to repeatedly sample the same point in a signal for a period of time. High random noise may be separated from the signal this way by averaging the voltage at the VERT output jack.

- 24. EXT<sup>1</sup> Push this button when you wish to control the horizontal position of the crt beam with an externally supplied scanning signal. The input jack adjacent to the EXT pushbutton is for introducing such a signal. A zero to +10 volt (or higher) signal is needed to produce a full scale horizontal scan. A signal that goes from zero to more than +10 volts may be attenuated with the SCAN control to produce ten divisions of scan. This mode is useful when you wish to slave the scan operation to an external instrument such as a chart recorder.

- This control determines the hori-25. SCAN zontal velocity of the crt beam (scan rate) whenever the REP button or the SINGL SCAN button is pushed. (This rate is partly determined by some other factors also, like trigger repetition rate, holdoff. time per division, and whether the LO NOISE button is pushed or released.)

<sup>1</sup>Pin tip plugs of 0.08 inch diameter should be used with the pin jacks.

26. INT CH 1

27. HF SYNC

28. LEVEL

31. HORIZ

The LEVEL control is used to "lock" on to the triggering or synchronizing signal to reproduce a steady, coherent waveform on the crt. The triggering signal must have a steady, synchronous time relationship with the vertical signal for the display to be steady.

Push this button to trigger on the

internal signal introduced at the

Channel 1, 50 Ω INPUT connector.

Release this pushbutton to trigger

on the external triggering signal

introduced at the EXT INPUT

Push this button to synchronize on

signals above 100 MHz. Be sure to

release the pushbutton when trig-

gering on any signal below

connector.

100 MHz.

- 29. HOLDOFF The HOLDOFF control is normally left fully counterclockwise to allow a maximum scan rate. The HOLD-OFF control is used to help display complex waveforms and pulse trains, such as digital words, by varying the period of trigger holdoff. That inhibits recognition of early, unwanted triggering signal edges.

- 30. EXT INPUT This input connector is AC coupled **50** Ω into a nominal 50 ohm load. The blocking capacitor has a DC voltage rating of 50 volts and more than 1 megohm resistance. External triggering signals may be delivered to this input via a 50 ohm coaxial cable, unattenuated. For large signals the P6056 10X probe or P6057, 100X probe is recommended. When AC coupled, the DC load resistance imposed by these probes is essentially the same as that of the blocking capacitor, i.e., more than 1 megohm.

The signal voltage available at this 1 V/DIV<sup>1</sup> output pin jack is proportional to the horizontal position of the beam at any instant; zero volts corresponds to approximately center screen. The output waveform resembles that of a sawtooth or staircase when produced internally. using the REP or SINGL SCAN modes. The output voltage starts at

-5 volts and goes positive to +5 volts as the beam scans the ten crt divisions. The output waveform is most often used to drive chart recorders. Also refer to the discussion of the SINGL SCAN control.

32. VERT .2 V/DIV1 The signal available at this output pin jack is a replica of the signal that produces vertical deflection. This waveform is most often used to drive chart recorders. 7S14, and the time per division selected by the SEC/DIV switch does not set the horizontal velocity of the beam as with conventional oscilloscope time base plug-ins. The 7A13 Differential Comparator is a particular useful example, because it is often used to measure DC levels or peak signal levels when the signal waveform is of no importance. It may be placed alongside the 7S14 to produce a time-shared three-trace display when the 7S14 is used in the DUAL TRACE mode. The DISPLAY pushbutton on the other plug-in.

With the four-hole mainframe series, it is possible to use a horizontal plug-in and a vertical plug-in in conjunction with the 7S14. This is particularly useful in that the same mainframe can be used to troubleshoot the 7S14.

Other Plug-Ins

Most any vertical plug-in may be used in a limited way with the 7S14. However, you should remember that the horizontal scan rate of the beam is not calibrated in the

For a complete explanation of uses of the mainframe, refer to the operating manual for the particular mainframe.

### APPLICATIONS

#### Introduction

The display waveform on the crt screen propagated by a 7S14 is a plot of voltage per unit equivalent time. Since the 7S14 has calibrated deflection factors both vertically and horizontally, the sampling system can be used for making accurate voltage and time measurements of an input signal.

The 7S14 offers dual-trace capabilities that allow the user to simultaneously view two signals and determine the time and amplitude relationship between the two signals. In addition, dual trace operation allows interactive displays of the two signals; e.g., X-Y and added algebraically.

The 7S14 also provides a two-dot time-interval measurement that provides a means of measuring the time between two points of a display. The two dots represent two points in time on the delaying sweep of the 7S14.

The dual trace capabilities and the two-dot system provide a great versatility for measurements. Some of the applications will be discussed in the following paragraphs.

#### PHASE DIFFERENCE MEASUREMENTS

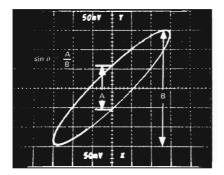

The time difference between two sine-wave signals of the same frequency may be measured by using one of the signals as the reference and observing the phase difference between the reference and the second signal. There are two convenient methods of measuring the phase difference using the 7S14. The main differences in the two methods are in terms of accuracy and convenience.