# THEORY OF OPERATION

This section describes the circuitry used in the 7104 Oscilloscope. The description begins with a discussion of the instrument, using the block diagram shown in Figure 3-1, and continues in detail, showing the relationships between the stages in each major circuit. Schematics of all major circuits are given in Section 8, Diagrams and Circuit Board Illustrations. Stages are outlined on the schematics with wide shaded lines. Stage names are in shaded boxes. Refer to these schematics throughout the following circuit description for specific electrical values and relationships.

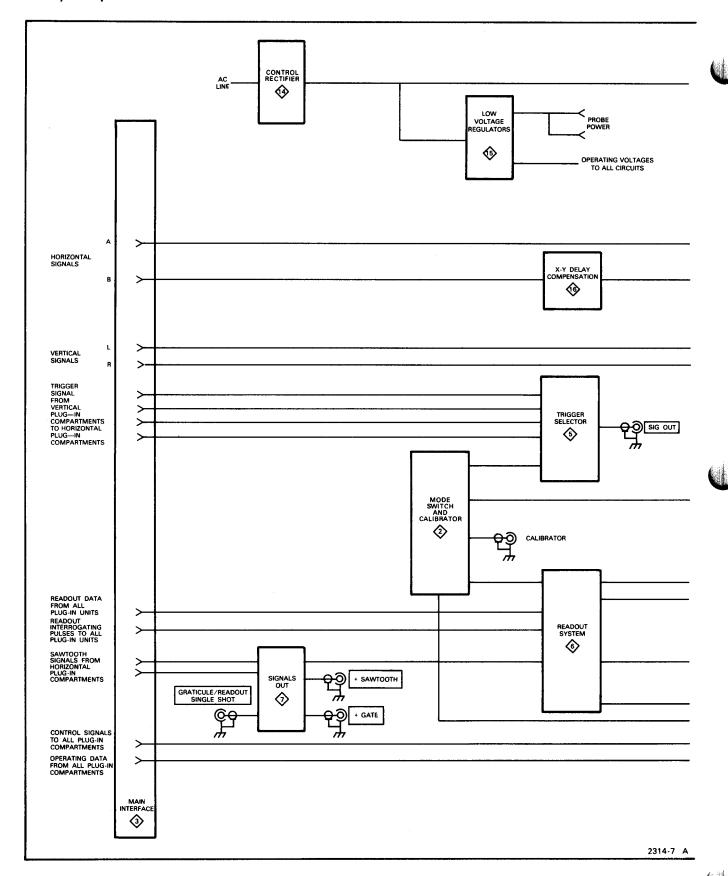

# **BLOCK DIAGRAM**

The following discussion is provided to assist in understanding the overall concept of the 7104 Oscilloscope mainframe before the individual circuits are discussed in detail. A basic block diagram of the 7104 is shown in Figure 3-1. Only the basic interconnections between the individual blocks are shown on this diagram. Each major circuit within the instrument is given a block. The number of each block refers to the complete circuit diagram located at the rear of this manual.

# **DESCRIPTION**

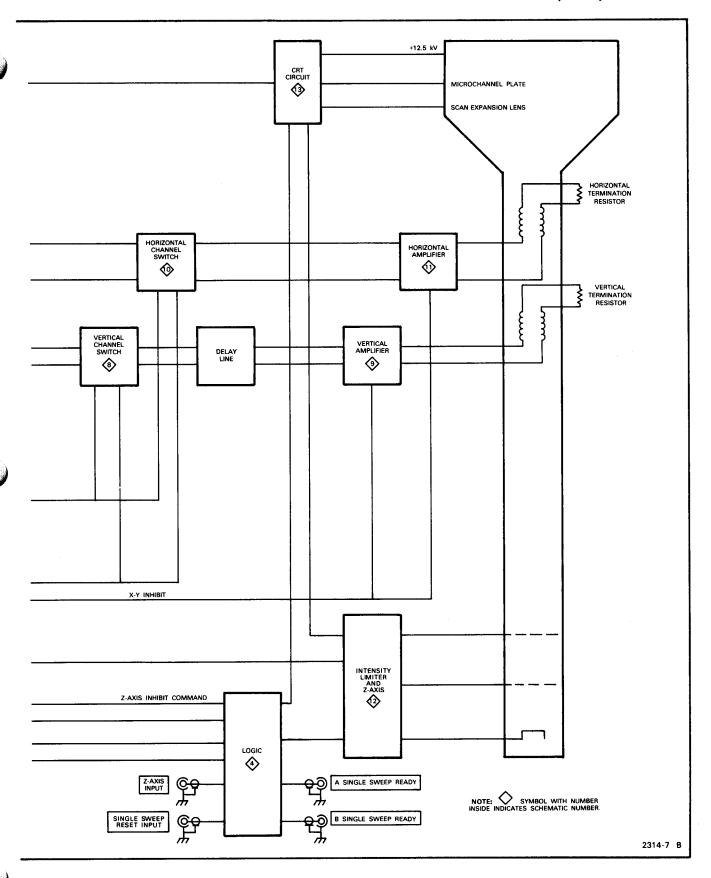

Vertical signals to be displayed on the crt are applied to the Vertical Channel Switch circuit from both vertical plug-in compartments. The VERTICAL MODE switch is connected to the logic circuit and determines whether the signal from the LEFT VERT or RIGHT VERT compartment is displayed on the crt. The Vertical Channel Switch receives an X-Y inhibit signal from the Readout System to provide the time sharing between the vertical and readout signals.

The selected vertical signal passes through the Delay Line and is amplified by the Vertical Amplifier circuit to drive the vertical deflection plates of the crt (cathode-ray tube). The Vertical Amplifier circuit includes an input from the Readout System to produce the vertical portion of the alpha-numeric readout display.

Horizontal signals for display on the crt are connected to the Horizontal Channel Switch from both horizontal plugin compartments. The signal from B HORIZ plugin compartment may pass through the optional X-Y delay compensation network (Option 2 instruments only). The HORIZONTAL MODE switch determines whether the signal from the A HORIZ or B HORIZ compartment is displayed by the crt. The Horizontal Channel Switch receives an X-Y inhibit signal from the Readout System to provide the time sharing between the vertical and readout signals.

The selected horizontal signal is amplified by the Horizontal Amplifier circuit to provide horizontal deflection of the crt. The Horizontal Amplifier circuit accepts an input signal from the Readout System to produce the horizontal portion of the alpha-numeric readout display.

The Readout System provides an alpha-numeric display of information encoded by the plug-in unit(s). The readout display is written on the crt on a time-shared basis with the analog waveform display. The VERTICAL and HORIZONTAL MODE switch circuits determine which plug-in unit(s) displays readout information. The Readout System sends inhibit commands to the Vertical Channel Switch, Horizontal Channel Switch and Z-Axis logic circuits. The Readout System provides signals to produce the alpha-numeric display to the Vertical, Horizontal and Z-Axis Amplifier circuits.

The Logic circuit develops control signals for use in other circuits within the instrument and the plug-in units. These control signals automatically determine the correct instrument operation in relation to the plug-in units, plug-in unit control settings, and 7104 front-panel control settings. The Logic circuit performs three functions:

#### (1) Receives

- a. The external Z-Axis Input signal.

- b. The Single Sweep Reset Input from the rear panel.

- c. The Z-Axis Inhibit Command from the Readout System.

- (2) Sends the A and B SINGLE SWEEP READY signals to the rear panel.

- (3) Develops the Z-Axis signal for use by the Z-Axis Amplifier.

Figure 3-1. Basic block diagram of the 7104 Oscilloscope.

Figure 3-1. Basic block diagram of the 7104 Oscilloscope (continued).

#### Theory of Operation-7104

In addition to control circuitry, the CRT Circuit supplies voltages necessary for operation of the crt by:

- (1) Developing the operating voltages for the crt Microchannel Plate and the Scan Expansion Lens.

- (2) Providing a signal proportional to the average screen current to the input of the intensity limiter level.

- (3) Receiving a signal proportional to the intensity level setting from the logic circuit to be used by the Microchannel Plate supply for biasing. The Z-Axis Amplifier provides the drive signal to control the intensity level of the crt display.

The Calibrator circuit produces a one kilohertz squarewave signal which can be used to check the calibration of this instrument and the compensation of probes. The calibrator signal is available as a voltage at the CALIBRATOR connector or as a current through a 40 milliampere optional current loop accessory.

The internal trigger signals from the vertical plug-in units are connected to the Trigger Selector circuit. The Trigger Selector circuit determines whether the trigger signal from the left or right vertical unit is connected to the A or B horizontal unit. The B Trigger Channel Switch also produces the drive signal for the SIG OUT circuit to provide an output that is a sample of the vertical signal.

The Signals Out circuit processes signals from the plugin units for the front-panel +GATE and +SAWTOOTH outputs.

The Control/Rectifier and Low-Voltage Regulator circuits provide the power necessary to operate the instrument. These voltages are connected to all circuits within the instrument.

# **DETAILED CIRCUIT OPERATION**

A detailed description of the electrical operation and relationship of the circuits in the 7104 Oscilloscope mainframe is provided in this section. The theory of operation for circuits unique to this instrument is described in detail in the discussion. Circuits commonly used in the electronics industry are not described in detail. If more information is desired on these commonly used circuits, refer to the following textbooks:

Gordon V. Deboo, Integrated circuits and Semiconductor Devices, McGraw-Hill, New York, 1971.

Albert Paul Malvino, Transistor Circuit Approximations, McGraw-Hill, New York, 1973.

Joseph Milman and Herbert Taub, Pulse, Digital and Switching Waveforms, McGraw-Hill, New York, 1965.

#### LOGIC FUNDAMENTALS

Digital logic techniques are used to perform many functions within the instrument. The function and operation of the logic circuits are described using logic symbology and terminology, aiding in the understanding of these symbols and logic concepts, not a comprehensive discussion of the subject. For further information on binary number systems and the associated Boolean algebra concepts, the derivation of logic functions, or a more detailed analysis of digital logic, refer to the following textbooks:

Robert C. Baron and Albert T. Piccirilli, *Digital Logic and Computer Operation*, McGraw-Hill, New York, 1967.

Thomas C. Bartee, *Digital Computer Fundamentals,* McGraw-Hill, New York, 1966.

Yaohan Chu, *Digital Computer Design Fundamentals*, McGraw-Hill, New York, 1962.

Joseph Milman and Herbert Taub, *Pulse, Digital and Switching Waveforms,* McGraw-Hill, New York, Chapters 9-11, 1965.

#### **SYMBOLS**

The operation of circuits in this instrument which use digital techniques is described using the graphic symbols set forth in military standard MIL-STD-806B. Table 3-1 provides a basic logic reference for the logic devices used within this instrument. Any deviations from the standard symbology, or devices not defined by the standard are described in the circuit description for the applicable device.

#### NOTE

Logic Symbols used on the diagrams depict the logic function as used in this instrument and may differ from the manufacturer's data.

#### LOGIC POLARITY

All logic functions are described using the positive logic convention. Positive logic is a system of notation where the more positive of two levels (HI) is called the true or 1-state; the more negative level (LO) is called the false or 0-state. The HI-LO method of notation is used in this logic description. The specific voltages that constitute a HI or LO state vary between individual devices. Whenever possible, the input and output lines are named to indicate the function that they perform when at the HI (true) state.

TABLE 3-1

Basic Logic Reference

| Device    | Symbol | Description                                                            | Input    | /Output | Table         |

|-----------|--------|------------------------------------------------------------------------|----------|---------|---------------|

| AND gate  |        | A device with two or more inputs                                       | in       | out     | /Output       |

|           | A      | and one output. The output of the AND gate is HI if and only if all of | Α        | В       | X             |

|           | В х    | the inputs are at the HI state.                                        | LO       | LO      | LO            |

|           | 8 —    |                                                                        | LO       | HI      | LO            |

|           |        |                                                                        | HI       | LO      | LO            |

|           |        |                                                                        | LHI      | HI      | Н             |

| NAND gate |        | A device with two or more inputs                                       | In       | put     | /Output       |

|           |        | and one output. The output of the                                      | Α        | В       | X             |

|           | A —    | NAND gate is LO if and only if all of the inputs are at the HI state.  | LO       | LO      | HI            |

|           | )— X   | or the inputs are at the fire state.                                   | LO       | HI      | ні            |

|           |        |                                                                        | ні       | LO      | НІ            |

|           |        |                                                                        | н        | НІ      | LO            |

| OR gate   |        | A device with two or more inputs                                       | In       | put     | /Output       |

| O gato    |        | and one output. The output of the                                      | A        | В       | X             |

|           | A      | OR gate is HI if one or more of the                                    | LO       | LO      | LO            |

|           | В X    | inputs are at the HI state.                                            | LO       | HI      | HI            |

|           |        |                                                                        | HI       | LO      | HI            |

|           |        |                                                                        | HI       | НІ      | н             |

|           |        |                                                                        | <b>L</b> |         |               |

| NOR gate  |        | A device with two or more inputs                                       | In       | put     | /Output       |

| _         |        | and one output. The output of the                                      | A        | В       | $\frac{1}{x}$ |

|           | A      | NOR gate is LO if one or more of                                       | LO       | LO      | HI            |

|           | вх     | the inputs are at the HI state.                                        | LO       | HI      | LO            |

|           |        |                                                                        | HI       | LO      | LO            |

|           |        |                                                                        | НІ       | ні      | LO            |

| Inverter  |        | A device with one input and one                                        | Inpu     | t /     | Output        |

|           |        | output. The output state is always                                     | A        |         | X             |

|           | A — X  | opposite to the input state.                                           | Lo       |         | HI            |

|           |        |                                                                        | HI       |         | LO            |

|           |        |                                                                        |          |         |               |

TABLE 3-1 (CONT.) Basic Logic Reference

| Device                             | Symbol  | Description                                                                                                                                                                                                                                                | Inpi                   | ut/Outp             | ut Table                                    |

|------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------|---------------------------------------------|

| LO-state<br>indicator              |         | A small circle at the input or output of a symbol indicates that the LO state is the significant state. Absence of the circle indicates that the HI state is the significant state. Two examples follow:  AND gate with LO-state indicator at the A input. | A<br>LO<br>LO<br>HI    | B<br>LO<br>HI<br>LO | /Output X LO HI LO LO                       |

|                                    | A — O X | The output of this gate is HI if and only if the A input is LO and the B input is HI.                                                                                                                                                                      | ı                      | <b>anut</b>         | Outnut                                      |

|                                    | A — X   | OR gate with LO-state indicator at the A input:  The output of this gate is HI if either the A input is LO or the B input is HI.                                                                                                                           | A<br>LO<br>LO<br>HI    | B LO HI LO HI       | /Output X HI HI LO HI                       |

| Edge symbol                        | 4       | Normally superimposed on an input line to a logic symbol. Indicates that this input (usually the trigger input of a flip-flop) responds to the indicated transition of the applied signal.                                                                 |                        |                     |                                             |

|                                    | 7       |                                                                                                                                                                                                                                                            |                        |                     |                                             |

| Triggered<br>(toggle)<br>Flip-Flop | 1 x     | A bistable device with one input and two outputs (either or both outputs may be used). When triggered, the outputs change from one stable state to the other stable state                                                                                  | Condit before to pulse | tion (<br>rigger at | Output<br>Condition<br>ter trigger<br>pulse |

|                                    | 0 ▼     | with each trigger. The outputs are complementary (i.e., when one output is HI the other is LO). The edge symbol on the trigger (T) input may be of either polarity depending on the device.                                                                | l <del></del>          | ні і                | X X<br>HI LO<br>.O HI                       |

TABLE 3-1 (CONT.)

Basic Logic Reference

| Device                                                                                | Symbol                                                | Description                                                                                                                                                                                                                                                                                                                                                                       | In                                        | put/Ou                    | tput T                        | able                          |

|---------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------|-------------------------------|-------------------------------|

| Set-Clear<br>(J-K)<br>Flip-Flop                                                       | A X FF K 0 \ \textbf{X}                               | A bistable device with two inputs and two outputs (either or both outputs may be used). The outputs change state in response to the states at the inputs. The outputs are complementary (i.e., when one output is HI the other is LO).                                                                                                                                            | A<br>LO<br>LO<br>HI                       | B<br>LO<br>HI<br>LO       | X<br>No cl<br>LO<br>HI<br>Cha | tput  X hange HI LO nges ate  |

| D (data) Type<br>Flip-Flop                                                            | A — D 1 — X FF T 0 — X                                | A bistable device with two inputs and two outputs (either or both outputs may be used). When triggered the state of the "1" output changes to the state at the data (D) input prior to the trigger. The outputs are complementary (i.e., when one output is HI the other is LO). The edge symbol on the trigger (T) input may be of either polarity, depending on the device.     | A LO HI Output trigger                    | )<br>L                    | 11                            | X<br>HI<br>LO                 |

| Triggered Set-Clear (J-K) Flip-Flop                                                   | A — J 1 — X FF T K 0 — X                              | A bistable device with three or more inputs and two outputs (either or both outputs may be used). When triggered, the outputs change state in response to the states at the inputs prior to the trigger. The outputs are complementary (i.e., when one output is HI the other is LO). The edge symbol on the trigger (T) input may be of either polarity depending on the device. | LO<br>LO<br>HI                            | B<br>LO<br>HI<br>LO<br>HI | X<br>No c<br>LO<br>HI<br>Cha  | tput  X hange HI LO inges ate |

| Flip-Flop with<br>Direct Inputs<br>(may be applied<br>to all triggered<br>flip-flops) | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | For devices with direct-set (S <sub>D</sub> ) or direct-clear (C <sub>D</sub> ) inputs, the indicated state at either of these inputs over-rides all other inputs (including trigger) to set the outputs to the states shown in the input/output table.                                                                                                                           | А 1 Ф 6 Ф 6 Ф 6 Ф 6 Ф 6 Ф 6 Ф 6 Ф 6 Ф 6 Ф |                           | D C                           | ined by                       |

#### INPUT/OUTPUT TABLES

Input/Output (truth) tables show the input combinations important to a particular function, along with the resultant output conditions. This table may be given either for an individual device or for a complete logic stage. Examples of input/output tables for individual devices can be seen in Table 3-1.

#### **NON-DIGITAL DEVICES**

Not all of the integrated circuit devices in this instrument are digital logic devices. The function of non-digital devices is described individually, using operating waveforms or other techniques to illustrate their function.

# **CABLE DISTRIBUTION**

Diagram 1, shows the cable inter-connections between circuit boards within the 7104.

# MODE SWITCH AND CALIBRATOR

A schematic diagram of the Mode Switch and Calibrator circuits is given on diagram 2, in section 8 of this manual (Diagrams and Circuit Board Illustrations). The schematic is divided by gray shaded lines separating the circuitry into major stages. These stages aid in locating components mentioned here. Sub-headings use the stage names to further identify portions of the circuitry on diagram 2.

#### **CALIBRATOR**

The Calibrator circuit provides voltage outputs of 40 millivolts, 0.4 volt and 4 volts at the CALIBRATOR output connector. A current output of 40 milliamperes is available from the Calibrator circuit with an optional current loop adapter. When using the current loop adapter the Calibrator must be operated only in the 4 V switch position, for stated output.

Transistors Q376 and Q382 form a 1 kilohertz, square-wave oscillator. Oscillation occurs as follows: Initially assume that Q376 is conducting and Q382 is not conducting. The voltage at the emitter of Q382 becomes more negative as C376 discharges through R381. Capacitor C376 discharges until the emitter-base junction of Q382 becomes forward biased. As Q382 begins conducting the oscillator changes states. Regeneration starts when Q382 conducts and C376 stops discharging; this reduces the collector current of Q376. Thus, the collector voltage of Q376 rises positive

which causes the base and emitter of Q382 to rise positive. The positive going voltage is coupled by C376 to the emitter of Q376, turning it off.

At this time, Q382 is conducting and Q376 is not conducting. The voltage at the emitter of Q376 goes negative as C376 charges through R376. When the emitter-base junction of Q376 becomes forward biased the oscillator will again change states to complete the cycle.

The square-wave signal produced at the collector of Q382 switches Q384 on and off. When Q384 is on, the current from R383 and R384 flows to ground. When Q384 is off, this current flows through CR386 and R386 into the voltage divider network of R387, R392, R393, R394, R395, R396, and R397 to produce the 4 volt, 0.4 volt and 40 millivolt Calibrator output voltages. The accuracy of the Calibrator is set by the 0.4 Volts DC adjustment, R385. Both the 4V and 0.4V calibrator switches must be engaged when adjusting R385. The Calibrator frequency is set by the 1 kHz adjustment, R375.

#### MODE SWITCHING

The Mode Switching circuit includes front-panel switching and provides the logic for selection of the vertical and horizontal compartments to provide deflection for the crt. The Mode Switching circuit operates in conjunction with the Logic circuit (diagram 4) to develop control signals for use in other circuits within this instrument and plug-in units installed in the plug-in compartments. Table 3-2 shows the outputs produced with all combinations of the front-panel switch positions.

#### MAIN INTERFACE

Diagram 3 shows the plug-in interface and the interconnections between the plug-in compartments, circuit boards, etc. of this instrument. The signal and voltage connections of each interface connector are also identified in diagram 3.

#### LOGIC

A schematic diagram of the Logic circuit is given on diagram 4, in section 8 of this manual (Diagrams and Circuit Board Illustrations). The schematic is divided by gray shaded lines separating the circuitry into major stages. These stages aid in locating components mentioned here. Sub-headings in the following discussion use these stage names to further identify portions of the circuitry on diagram 4.

TABLE 3-2 Mode Switching Inputs/Outputs

-

|                                       |                                     | RIGHT         |        | N |    | NO |      | NO | N<br>O | NO  | NO  | NO     |     |     | NO  |

|---------------------------------------|-------------------------------------|---------------|--------|---|----|----|------|----|--------|-----|-----|--------|-----|-----|-----|

|                                       | D B<br>ER<br>JGHTS                  | <del></del>   |        | 0 |    | -  |      | 0  | -      | 0   | 0   |        |     |     | 0   |

| TS .                                  | A AND B<br>TRIGGER<br>SWITCH LIGHTS | LEFT<br>VERT  | N<br>O |   | NO | NO | O    |    | ON     | NO  |     |        | O   | NO  | O   |

| OUTPU                                 | NS                                  | VERT<br>MODE  |        |   | NO | NO | NO   | NO | NO     | NO  | ON  | N<br>O | ON  | NO  | NO  |

| CHING                                 | ADD                                 |               | Ŧ      | Ī | Ī  | ОП | Ī    | Ī  | Ξ      | H   | Ī   | Ī      | Ī   | Ī   | Ī   |

| MODE SWITCHING OUTPUTS                | RIGHT                               |               | ΓO     | Ī | ГО | го | ro   | Ī  | ALT    | ALT | Ī   | Ŧ      | LO  | 07  | ALT |

| MOD                                   | HORIZ                               | ENABLE        |        |   | OJ | ГО | ГО   | ГО | ГО     | ГО  | Ξ   | Ī      | 王   | Ī   | ГО  |

|                                       | VERT                                | SIG           |        |   | Ħ  | Ī  | сноР | 70 | ALT    | ALT | ALT | ALT    | ALT | ALT | ALT |

|                                       | A TIME-<br>BASE<br>UNIT             | MODE          |        |   |    |    |      |    |        |     |     |        |     |     | •   |

|                                       | ١٢                                  | 8             |        |   |    |    |      |    |        | •   |     |        |     |     |     |

|                                       | HORIZONTAL<br>MODE<br>SWITCH        | СНОР          |        |   |    |    |      |    |        |     |     | •      |     | •   |     |

|                                       | HORI<br>M(<br>SW                    | ALT           |        |   |    |    |      |    |        |     | •   |        | •   |     |     |

|                                       |                                     | ∢ .           |        |   |    |    |      |    |        |     |     |        |     |     |     |

| ITS)                                  | тсн                                 | RIGHT         |        |   |    |    |      | •  |        |     |     |        |     |     |     |

| S (INPL                               | VERTICAL MODE SWITCH                | снор          |        |   |    |    | •    |    |        |     |     |        |     |     |     |

| NOITIS                                | IL MO                               | ADD           |        |   |    | •  |      |    |        |     |     |        |     |     |     |

| 4 POS                                 | TIC/                                | ALT           |        |   |    |    |      |    | •      | •   | •   | •      | •   | •   | •   |

| SWITC                                 | VEF                                 | LEFT          |        |   | •  |    |      |    |        |     |     |        |     |     |     |

| FRONT-PANEL SWITCH POSITIONS (INPUTS) | R                                   | RIGHT<br>VERT |        | • |    |    |      |    |        |     |     |        |     |     |     |

| FRON                                  | B TRIGGER<br>SOURCE<br>SWITCH       | LEFT<br>VERT  | •      |   |    |    |      |    |        |     |     |        |     |     |     |

|                                       | 8 8                                 | VERT          |        |   | •  | •  | •    | •  | •      | •   |     |        | •   | •   | •   |

|                                       | æ                                   | RIGHT<br>VERT |        | • |    |    |      |    |        |     |     |        |     |     |     |

|                                       | A TRIGGER<br>SOURCE<br>SWITCH       | LEFT<br>VERT  | •      |   |    |    |      |    |        |     |     |        |     |     |     |

|                                       | Α"                                  | VERT          |        |   | •  | •  | •,   | •  | •      | •   | •   | •      |     |     |     |

#### Theory of Operation-7104

The Logic circuit develops control signals for use in other circuits within this instrument and any plug-in units installed in the vertical and horizontal compartments. These control signals automatically determine the correct instrument operation in relation to the plug-in units installed or selected, plug-in control settings, and 7104 control settings.

### **HORIZONTAL LOGIC**

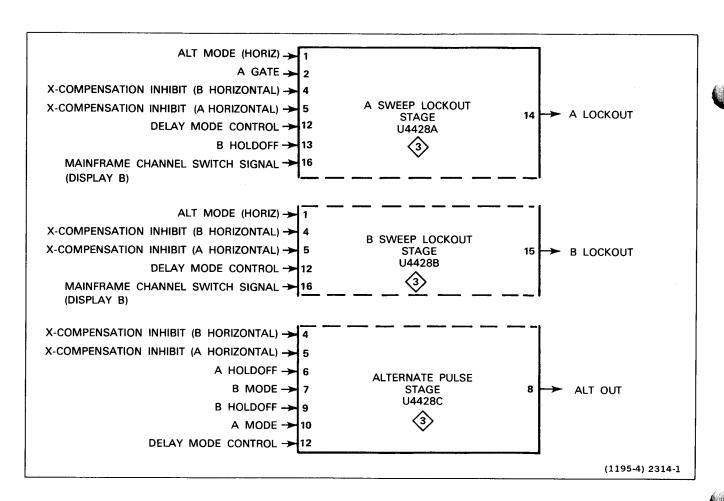

The Horizontal Logic stage performs three separate logic functions: A Sweep Lockout, B Sweep Lockout, and Alternate Pulse Generation. The majority of the Logic for these functions are contained within the Horizontal Logic IC, U4428. Figure 3-2 identifies the three individual stages of U4428 and the input and output terminals associated with each. Note that some of the input levels are connected internally to more than one of the individual stages.

#### A Sweep Lockout

The A Sweep Lockout portion of the Horizontal Logic IC (U4428) produces an output level at the collector of Q4462 (A Sweep Inhibit) that determines when the A HORIZ time-base unit can produce a sweep. If this output is HI, the A HORIZ unit is locked out (disabled) not

producing a sweep. If the level is LO, the A HORIZ unit is enabled and produces a sweep when triggered.

Only two combinations of input conditions to U4428 will produce a HI A Sweep Inhibit level, as shown by Table 3-3. If non-delayed operation is being used, the first combination disables the A sweep while the B sweep is being displayed in the ALT horizontal mode (both units must be in time-base mode). The second combination disables the A sweep during delayed-sweep operation enabling the B sweep to complete its holdoff before the next A sweep begins.

## **B Sweep Lockout**

The B Sweep Lockout stage produces an output level at the collector of Q4468 determining whether the B HORIZ time-base unit can produce a sweep. A HI output level locks out (inhibits) the B HORIZ unit and a LO level enables the B HORIZ unit to produce a sweep.

The output of this stage is HI only under one set of input conditions to U4428, as shown by Table 3-4. (This set of conditions disables the B sweep while the A sweep is being displayed in the ALT, HORIZONTAL MODE switch position, if both time-base units are in a sweep mode and

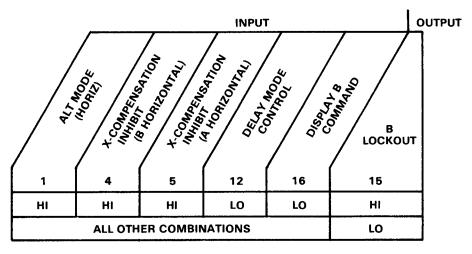

Figure 3-2. Breakdown of separate stages within Horizontal Logic IC (4428).

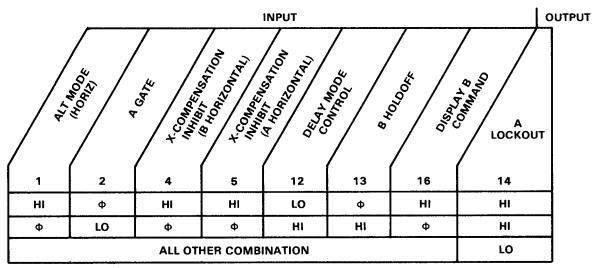

TABLE 3-3

Input/Output Combinations for A Lockout (U4428 Pin 14)

Φ = HAS NO EFFECT IN THIS CASE

TABLE 3-4

Input/Output Combinations for B Lockout (U4428 Pin 15)

non-delayed sweep is used.) For any other combination of input conditions, the B Sweep Lockout level is determined by the Delay Gate (from A time-base unit); see Main Interface, diagram 3.

#### Alternate Pulse Generator

The third function performed by the Horizontal Logic stage is the production of an Alternate Pulse signal for use by the Plug-In Binary and Vertical Binary stages. The holdoff gate produced at the end of the sweep by the respective time-base unit is differentiated by either C4335 or C4423, providing a positive-going pulse to pin 6 or 9 of U4428. The differentiated A or B holdoff gate may produce the alternate pulse depending upon the operating conditions as shown in Table 3-5.

#### (1) A (Only) Mode

An Alternate Pulse is produced at the end of each A sweep when the HORIZONTAL MODE switch is set to the A position.

#### (2) B (Only) Mode

In the B position of the HORIZONTAL MODE switch, an Alternate Pulse is produced at the end of each B sweep. (The A time-base must be in independent, non-delayed mode.)

TABLE 3-5

Input/Output Combinations for Alternate Pulse (U4428 Pin 8)

| _          |               |                 |           | INPUT           |       |            | /               | ОUТРИТ                                 |

|------------|---------------|-----------------|-----------|-----------------|-------|------------|-----------------|----------------------------------------|

| *COMPENSAT | *COMPENSATION | A HOLDS         | 8 MODE    | 8 40100         | A MOS | DELAY MODE | TIME BASE WHICH | TE SE PULSE                            |

| 4          | 5             | 6               | 7         | 9               | 10    | 12         | 8 <sup>2</sup>  | HORIZONTAL CONDITIONS                  |

| HI         | Φ             | HI1             | LO        | Φ               | ні    | Φ          | Α               | A ONLY                                 |

| Φ          | HI            | Φ               | н         | HI <sup>1</sup> | LO    | LO         | В               | BONLY                                  |

| н          | HI            | HI <sup>1</sup> | LO        | HI <sup>1</sup> | LO    | LO         | A AND B         | ALT OR CHOP                            |

| HI         | н             | HI <sup>1</sup> | Φ         | Φ               | Φ     | ні         | Α               | A DELAYS B                             |

| ні         | LO            | HI <sup>1</sup> | LO        | LO              | Φ     | Φ          | A               | A WITH VERTICAL UNIT IN B COMPARTMENT. |

| LO         | ні            | LO              | Φ         | HI1             | LO    | LO         | В               | B WITH VERTICAL UNIT IN A COMPARTMENT. |

|            |               | ALL OTH         | IER COMBI | NATIONS         |       |            | NO OUT          | PUT PULSE (LO AT OUTPUT)               |

$<sup>\</sup>Phi$  = Has no effect in this case.

### (3) Alt or Chop Mode

When the HORIZONTAL MODE switch is set to ALT or CHOP (the A time-base unit must be in independent, non-delayed mode), an Alternate Pulse is produced at the end of each sweep. For example, an Alternate Pulse is produced at the end of the A sweep, then at the end of the B sweep, again at the end of the A sweep, etc. Although Alternate Pulses are produced in the CHOP horizontal mode, they are not used in this instrument.

#### (4) Delayed Sweep (A Delays B)

When the A time-base unit is set for delayed operation, the operation of the Alternate Pulse Generator is changed producing an Alternate Pulse only at the end of the A sweep, even when the HORIZONTAL MODE switch is set to B. This is necessary since the A time-base establishes the amount of delay time for the B time-base unit whenever it is displayed.

# (5) Amplifier Unit in Horizontal Compartment

When an amplifier unit is installed in either of the horizontal plug-in compartments, the Alternate Pulse can be produced only from the remaining time-base unit. If amplifier units are installed in both horizontal compartments, an Alternate Pulse is not produced since there are no time-base units to produce a holdoff pulse.

#### **Z-AXIS LOGIC**

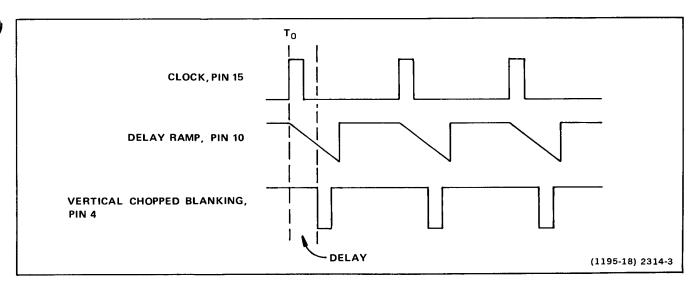

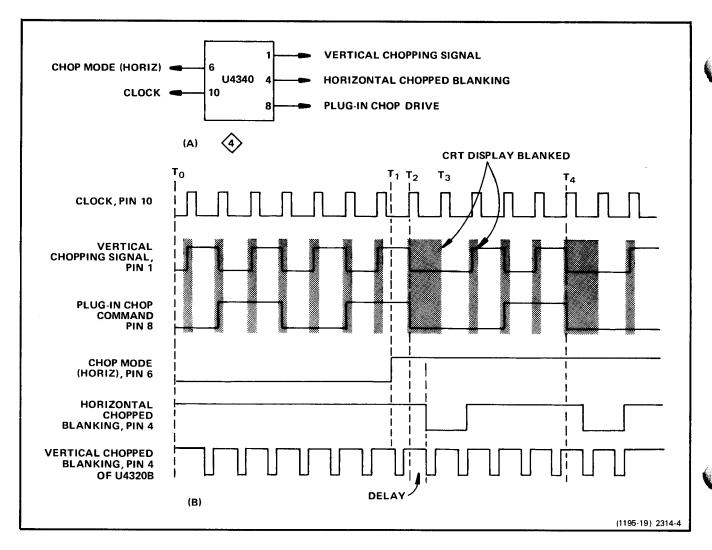

The Z-Axis Logic stage produces an output current signal at pin 8 of U4485 which sets the intensity of the crt display except for the readout display which is controlled by the Readout System. The output current at pin 8 is determined by the setting of the A or B INTENSITY controls, and the Auxiliary Z-Axis input. The Auxiliary Z-Axis input is produced by either the External Z-Axis input or by an input from any of the plug-in units; see Main Interface, diagram 3. The input current from the A and B INTENSITY controls is switched matching the output current to the horizontal display. The Vertical Chopped Blanking, Horizontal Chopped Blanking, and readout blanking signals are applied to this stage to block the output current and blank the crt display for vertical chopping, horizontal chopping, or during a readout display.

The inputs to the Z-Axis Logic stage (U4485) pins 1, 2, 9, and 16 are current-driven and are variable from zero to four milliamperes.

The Vertical Chopped Blanking signal, the Horizontal Chopped Blanking and the Z-Axis Inhibit signal enables or disables this stage to control all output current. Quiescently, the level at pins 6 and 7 is HI so that the intensity current from pins 1, 2, 9, and 16 can pass to the output. However, both pins 6 and 7 go LO during Vertical Chopped Blanking, during Horizontal Chopped Blanking or during a readout display. This blocks the output

<sup>&</sup>lt;sup>1</sup>Positive-going pulse. Where both A and B Holdoff are required to be HI, a HI at either input produces an alternate pulse.

<sup>&</sup>lt;sup>2</sup>Negative-going pulse.

current and the crt is blanked. The Vertical Chopped Blanking signal is connected to pins 6 and 7 of U4485 directly from pin 4 of U4320. The Horizontal Chopped Blanking Inhibit signal is connected to U4485 from pin 4 of U4340 through LR4338, Q4336 and CR4471. Notice that this signal is connected to the collector of Q4336. This transistor is normally operating in the saturated condition, and the HI Horizontal Chopped Blanking Inhibit level from U4340 is the collector source voltage. When the Horizontal Chopped Blanking Inhibit level goes LO, the current through Q4336 drops producing a corresponding LO level at its emitter. This level is connected to pins 6 and 7 of U4485 through CR4471.

Transistor Q4336 also controls the levels at pins 6 and 7 for readout displays. The Z-Axis Inhibit from the Readout System is connected to the base of Q4336 through VR4334 and R4335. This level is normally HI, so Q4336 operates as controlled by the Horizontal Chopped Blanking Inhibit level at its collector. When a readout display is to be presented, the Z-Axis Inhibit level drops LO and is coupled to the base of Q4336 through VR4334. Transistor Q4336 is then reverse biased producing a LO level at its emitter. This level is coupled to pins 6 and 7 of U4485 through CR4471 to block the Z-Axis Logic output current during the readout display. (The intensity of the readout display is determined by a separate Readout intensity level connected directly to the Z-Axis Amplifier; see CRT Circuit description.) Diode CR4472 clamps the emitter of Q4336 at about -0.6 volt when the transistor is off.

The A INTENSITY control sets the output current level when the A Gate at pin 14 is HI and the Display B Command connected to pin 15 through Q4488 and Q4492 is LO. The A Intensity current is blocked whenever the A Gate level goes LO indicating that the A sweep is complete or the Display B Command goes HI indicating that the B sweep is being displayed. The current from the A INTENSITY control is connected to pin 16 through R4482.

In the delayed mode, current is added to the A INTENSITY current during the A-sweep time to intensify a portion of the trace. This intensified portion is coincident with the B-sweep time providing an indication of which portion of the A sweep is displayed in the delayed mode. The A Intensified current is supplied to pin 2 of U4485 from the INTENSITY control through R4481. With this configuration, the intensified current increases as the A INTENSITY control setting is advanced to provide a proportional intensity increase in the intensified zone as the overall A-sweep intensity increases. Therefore, the intensified zone is more readily visible at high intensity levels. A front-panel screwdriver adjustment (B CONTRAST, R2015) allows for optimum contrast between the intensified portion and the overall sweep. The intensified current is added to the A INTENSITY current to produce an intensified zone on the A sweep under the following conditions: HI A Gate level at pin 14, LO Display B Command at pin 15, HI B Gate level at pin 4, and HI Delay Mode Control Out level at pin 5.

The B INTENSITY control determines the output current when the B Gate level at pin 4 and the Display B Command at pin 15 are both HI. The current from the B INTENSITY control is connected to the Z-Axis Logic stage through R4483.

The current level established by the intensity controls can be altered by the Auxiliary Z-Axis current level at pin 9. The current at this pin can come from the Z-AXIS INPUT connector on the rear panel (see diagram 3) or from any of the plug-in compartments. This current either increases or decreases (depending on polarity) the output current to modulate the intensity of the display. Input from the Z-AXIS INPUT connector allows the trace to be modulated by external signals. The Auxiliary Z-Axis inputs from the plug-in compartments allow specialpurpose plug-in units to modulate the display intensity. Diodes CR4473 and CR4474 limit the maximum voltage change at pin 9 to about + and -0.6 volt to protect the Z-Axis Logic stage if an excessive voltage is applied to the Z AXIS INPUT connector. Table 3-6 shows Input/Output combinations of the Z-Axis Logic stage.

#### HORIZONTAL BINARY

The Horizontal Binary stage develops the Display B Command to determine which horizontal plug-in unit provides the sweep displayed on the crt. When the level is HI, the B horizontal unit is displayed; when it is LO, the A horizontal unit is displayed.

The Display B Command is used in the following stages within the Logic circuit: Horizontal Logic (A and B Sweep Inhibit), Z-Axis Logic, Vertical Binary, and Trace Separation. In addition, it is connected to the following circuits elsewhere in the instrument to indicate which horizontal unit is to be displayed: Main Interface (A and B HORIZ plug-in compartments), Horizontal Interface (for horizontal channel selection).

The levels on pins 3, 4, 7, and 10 of U4358 are determined by the HORIZONTAL MODE switch (see diagram 2) which indicates which horizontal mode has been selected by providing a HI output level on only one of four output lines. The remaining lines are LO.

The Horizontal Binary stage operates as follows for each 4 positions of the HORIZONTAL MODE switch (refer to Table 3-7 for input/output conditions):

- 1. A MODE. By setting the HORIZONTAL MODE switch to A, the Display B Command is LO indicating to all circuits that the A horizontal unit is to be displayed.

- 2. B MODE. Selecting the B horizontal mode provides a HI Display B Command to all circuits.

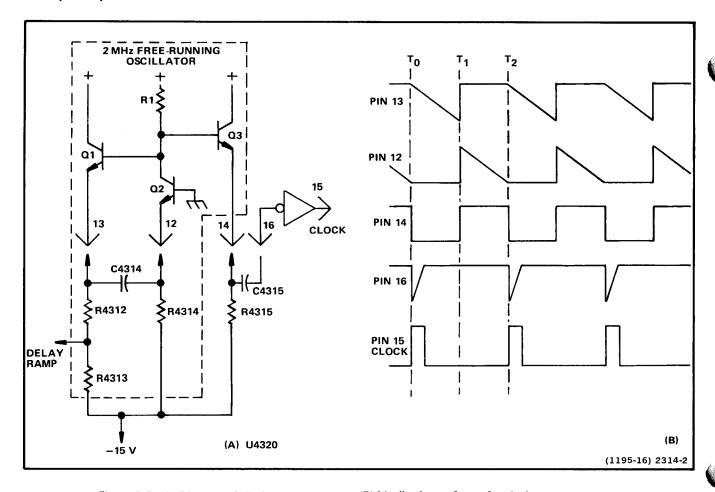

- **3. CHOP MODE.** In the CHOP position of the HORIZONTAL MODE switch, the Display B Command switches between the HI and LO levels to produce a display that switches between the A and B horizontal

TABLE 3-6 Input/Output Combinations for the Z-Axis Logic Stage

| 16  | Tuesday of the second of the s | August 2 | 14        | \$ \\ \delta \\ \ | 5  | 30 00 00 00 00 00 00 00 00 00 00 00 00 0 | 8 Annual S | 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------------------------------|------------|---------------------------------------|

| VAR | Φ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Φ        | HI        | Φ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LO | LO                                       | VAR        | A INTENSITY                           |

| VAR | Φ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Φ        | HI        | LO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | HI | LO                                       | VAR        | A INTENSITY                           |

| VAR | Ф                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VAR      | ні        | HI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | HI | LO                                       | VAR        | A INTENSITY PLUS INTENSIFIED          |

| Φ   | VAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Φ        | Ф         | HI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Φ  | н                                        | VAR        | B INTENSITY                           |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OTHE     | R COMBINA | TIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |                                          | LO         | NO OUTPUT                             |

HI = MAX VOLTAGE OR CURRENT LO = MIN VOLTAGE OR CURRENT VAR = VARIABLE CURRENT, 0 to 4 mA  $\Phi$  = HAS NO EFFECT

TABLE 3-7

Input/Output Combinations of the Horizontal Binary Stage

| _                       |       |       | INP     | UT                 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ОИТРИТ                                |

|-------------------------|-------|-------|---------|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

|                         |       |       |         |                    | , /      | " /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       |

| × 4                     |       | y / 5 | y / 6   |                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | N N N N N N N N N N N N N N N N N N N |