First Printing MAR 1978

PRODUCED BY SPS DOCUMENTATION GROUP

070-2151-00

### WARRANTY

Unless otherwise provided, Tektronix warrants that this instrument shall be free from defects in materials and workmanship under normal use and service for a period of one year from the date of installation. If this instrument fails during the warranty period under normal use and service because of a covered defect, Tektronix will repair or replace this instrument, provided that it is shipped freight prepaid to a designated service center. Tektronix will ship the repaired instrument or its replacement freight collect to the buyer. The risk of loss or damage and the duty to insure instruments in transit to or from Tektronix under this warranty shall be with the buyer.

## LIMITATION OF WARRANTY

Any attempt by any person other than an authorized representative of Tektronix to repair this instrument or to make any modifications to the hardware or software, without the express prior written consent of Tektronix, will void all warranties. Tektronix makes no other warranties, express or implied and specifically disclaims all warranties of merchantability or fitness for a particular purpose. Tektronix further disclaims any warranty that use of this instrument in conjunction with instruments supplied by buyer does not infringe any patent. Tektronix specifically excludes all special incidental and consequential damages for breach of any warranty. Tektronix' sole obligation for breach of any warranty shall be to repair or replace as set forth above.

For fastest possible service, direct all requests for repairs and replacement parts to the Tektronix Field Office or representative in your area. Please include the instrument Type Number or Part Number and Serial Number with all requests for parts or service.

Specifications and price change privileges reserved.

Copyright © 1978 by Tektronix, Inc. Beaverton, Oregon. Printed in the United States of America. All rights reserved.

U.S.A. and foreign TEKTRONIX products covered by U.S. and foreign patents and/or patents pending.

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

### TABLE OF CONTENTS

| SECTION 1 - INTRODUCTION                              | 1-1  |

|-------------------------------------------------------|------|

| Manual Organization                                   | 1-1  |

| Interface Description (General)                       | 1-1  |

| IEEE 488 Interface Function Subsets                   | 1-4  |

| Related Information                                   | 1-5  |

| Specifications                                        | 1-5  |

|                                                       |      |

|                                                       |      |

| SECTION 2 - IEEE 488 BUS DESCRIPTION                  | 2-1  |

| Introduction                                          | 2-1  |

| Bus Signal Lines                                      | 2-1  |

| The Data Bus                                          | 2-3  |

| The Management Bus                                    | 2-3  |

| The Transfer Bus (Handshake)                          | 2-5  |

| Bus Messages                                          | 2-5  |

| Control Commands                                      | 2-7  |

|                                                       |      |

|                                                       |      |

| SECTION 3 - INTERFACE REGISTERS AND INTERRUPT VECTORS | 3-1  |

|                                                       |      |

| Introduction                                          | 3-1  |

| Programmable Registers                                | 3-1  |

| Register Addresses                                    | 3-3  |

| Interrupt Vector Addresses                            | 3-4  |

| Register Descriptions                                 | 3-5  |

| Talker Data Buffer                                    | 3-6  |

| Listener Data Buffer                                  | 3-8  |

| Interrupt Control Register                            | 3-10 |

| Bus Status Register                                   | 3-14 |

| Bus Control Register                                  | 3-17 |

| Interface Status Register                             | 3-21 |

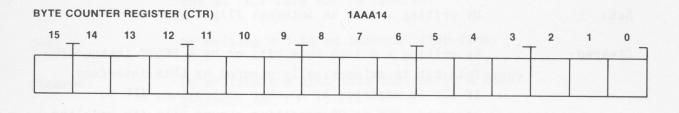

| Byte Counter Register                                 | 3-28 |

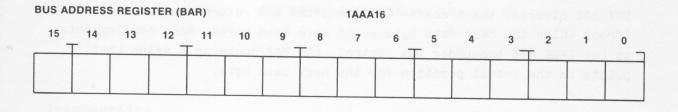

| Bus Address Register                                  | 3-29 |

| Local Reset and Interface Clear                       | 3-30 |

i

.

ł

| SECTION 4 - SOFTWARE PROTOCOLS                     | 4-1  |

|----------------------------------------------------|------|

| Introduction                                       | 4-1  |

| Programming Considerations                         | 4-2  |

| Addressing                                         | 4-2  |

| Local Reset                                        | 4-2  |

| The EOI Function                                   | 4-2  |

| The Listen Enable Functions                        | 4-3  |

| Errors Detected and Reported                       | 4-3  |

| Implementation of the IEEE 488 Interface Functions | 4-4  |

| Controller Function                                | 4-4  |

| Usage of IFC and REN                               | 4-5  |

| Usage of ATN and TCS                               | 4-5  |

| Performing a Serial Poll                           | 4-7  |

| Performing a Parallel Poll                         | 4-7  |

| Passing Control                                    | 4-8  |

| Interface Commands                                 | 4-8  |

| Source Handshake Function                          | 4-9  |

| Acceptor Handshake Function                        | 4-11 |

| Talker Function                                    | 4-13 |

| Listener Function                                  | 4-14 |

| Service Request Function                           | 4-17 |

| Remote/Local Function                              | 4-18 |

| Parallel Poll Function                             | 4-20 |

| Device Clear Function                              | 4-20 |

| Device Trigger Function                            | 4-21 |

|                                                    |      |

| OPERATION IN DMA MODE                              | 4-22 |

| Introduction                                       | 4-22 |

| Setting Up a DMA Transfer                          | 4-23 |

| Interface Status Register                          | 4-23 |

| Bus Status Register                                | 4-27 |

| Byte Counter Register                              | 4-28 |

| Bus Address Register                               | 4-28 |

### WARNING

The following servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing other than that contained in operating instructions unless you are qualified to do so.

### SECTION 5 - SERVICING

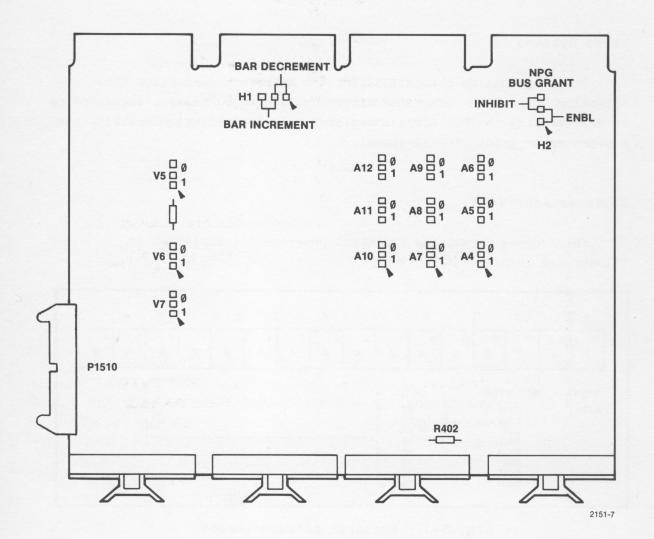

| Strap Options                                | 5-1 |

|----------------------------------------------|-----|

| Register Addresses                           | 5-1 |

| Interrupt Vector Addresses                   | 5-3 |

| Operating Mode Jumpers (H1 and H2)           | 5-5 |

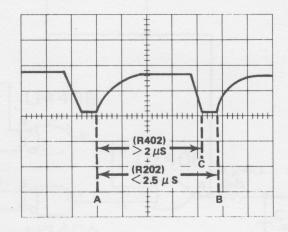

| Calibration for DMA Transmission Rate (R402) | 5-5 |

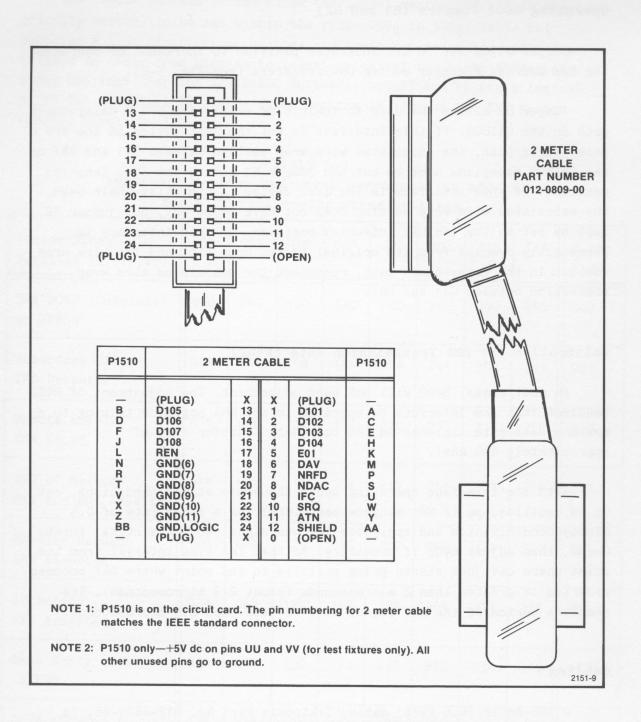

| Cabling                                      | 5-5 |

| Installation                                 | 5-7 |

| General Maintenance                          | 5-7 |

| Static-Sensitive Parts                       | 5-8 |

### SECTION 6 - CIRCUIT DESCRIPTION

6-1

5-1

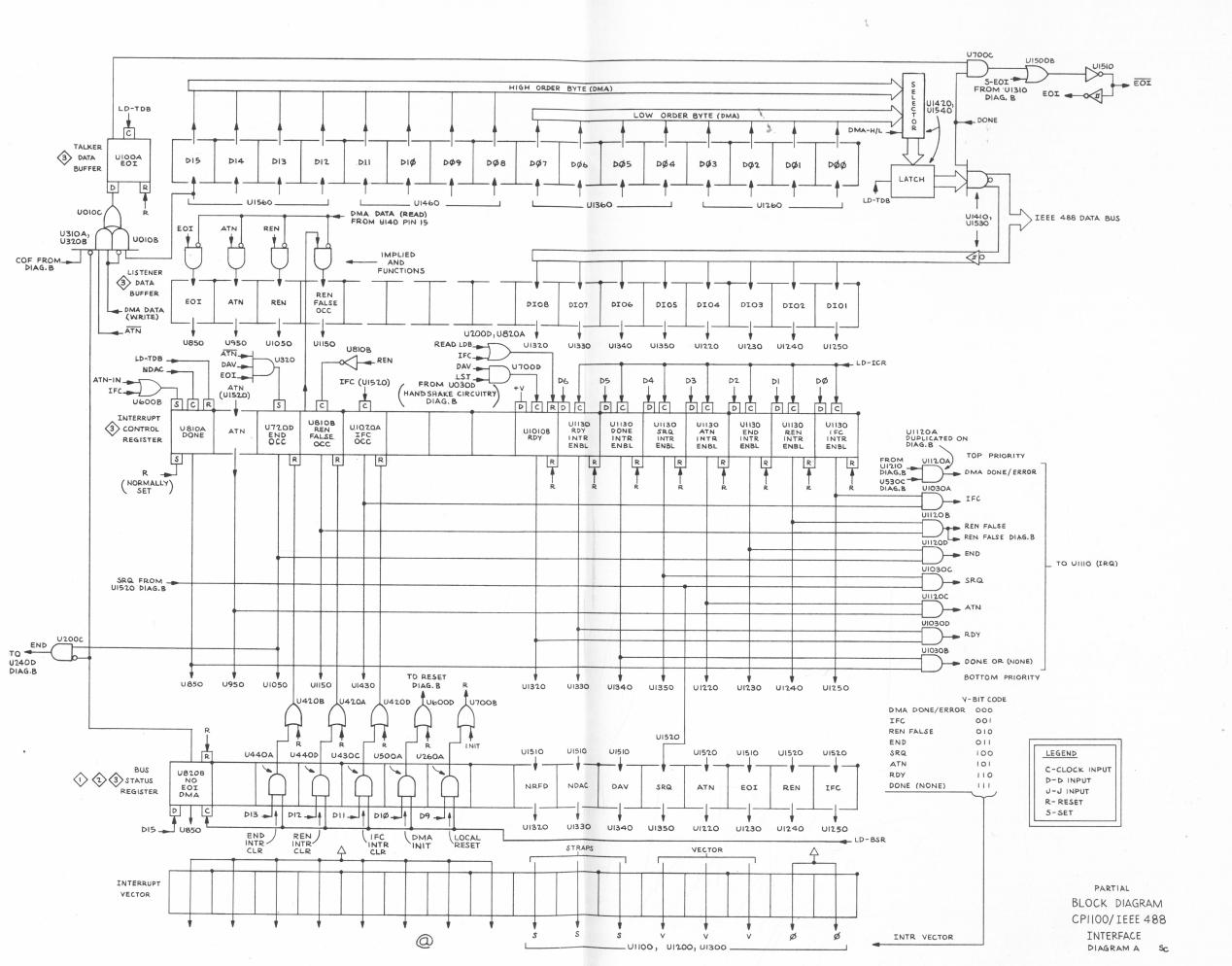

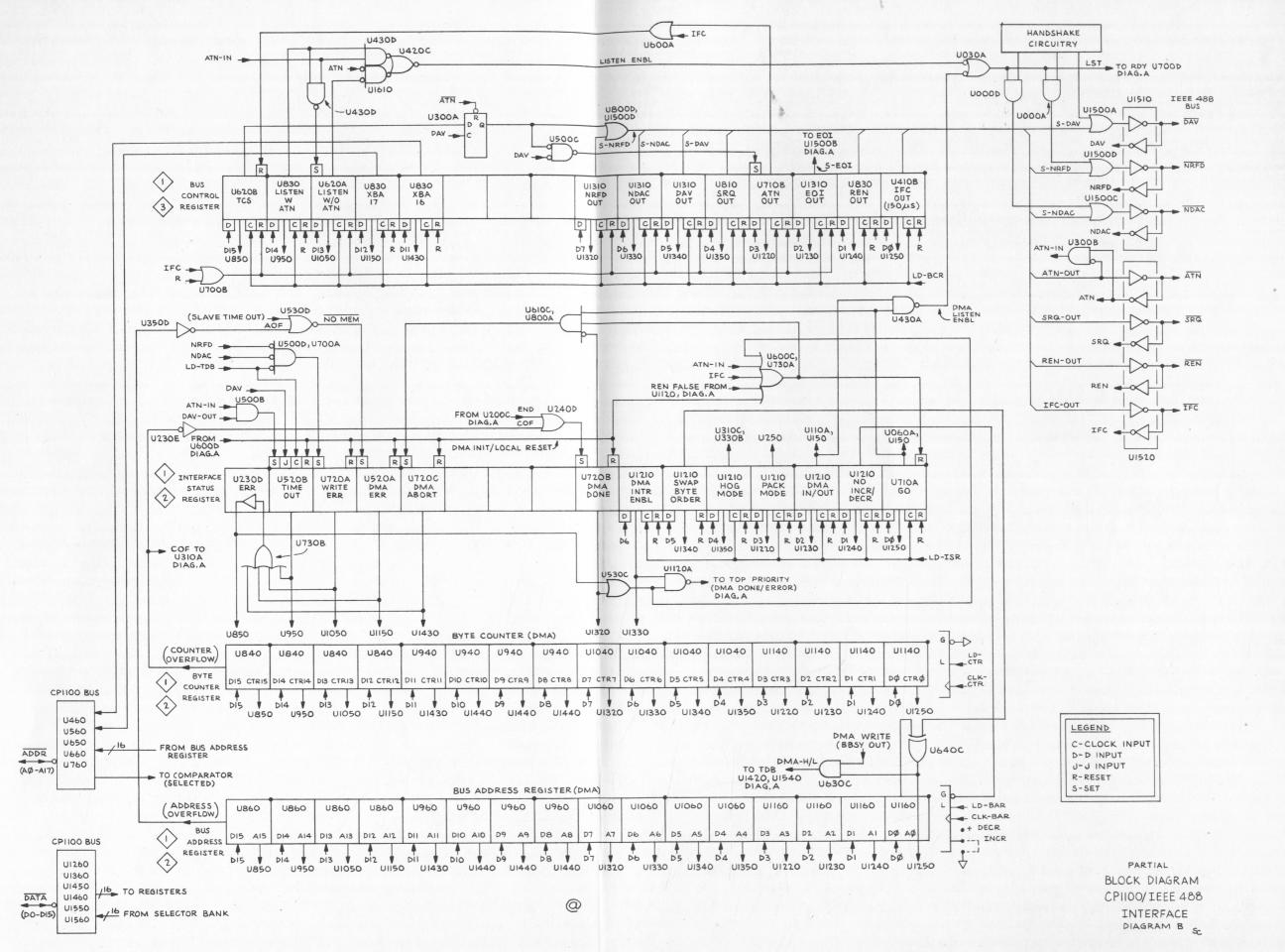

| Introduction (Block Diagram)    | 6-1  |

|---------------------------------|------|

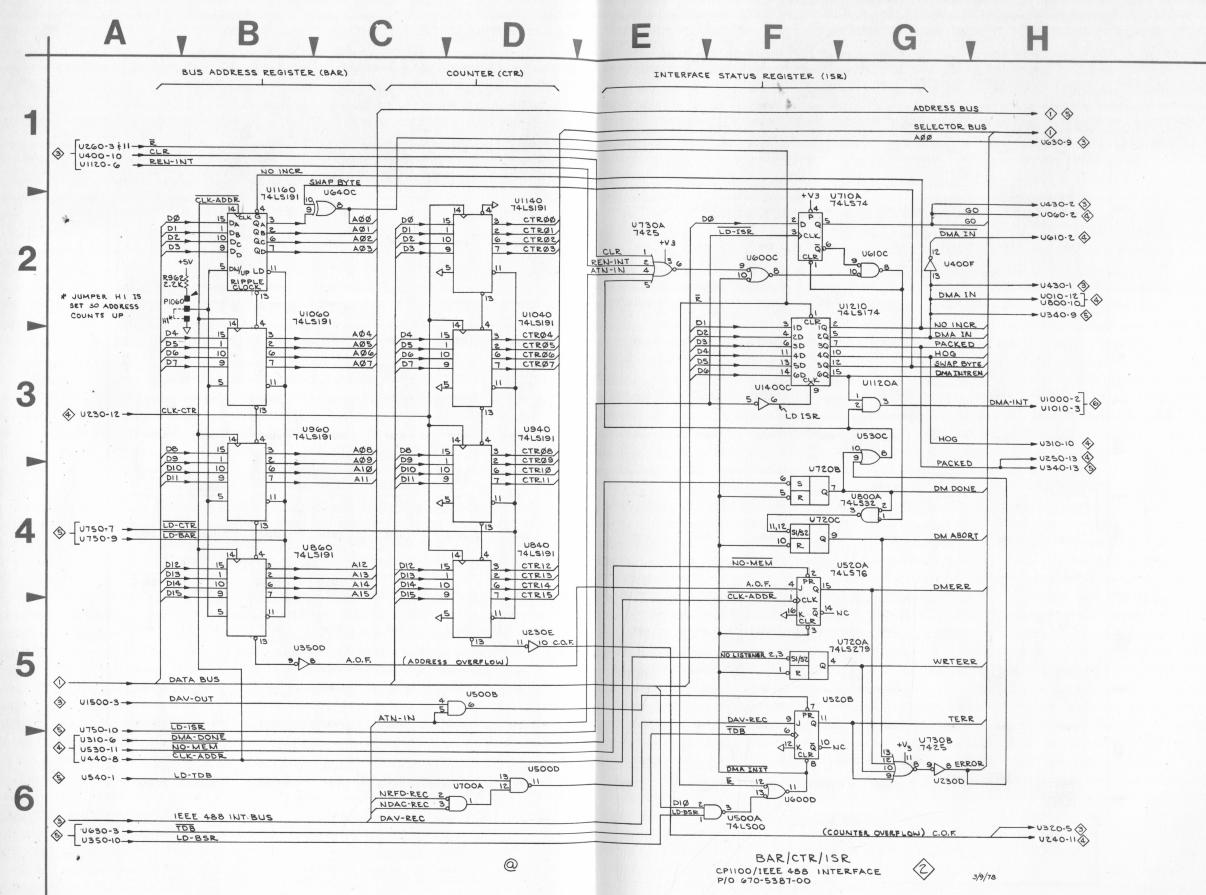

| Schematic Diagrams              | 6-1  |

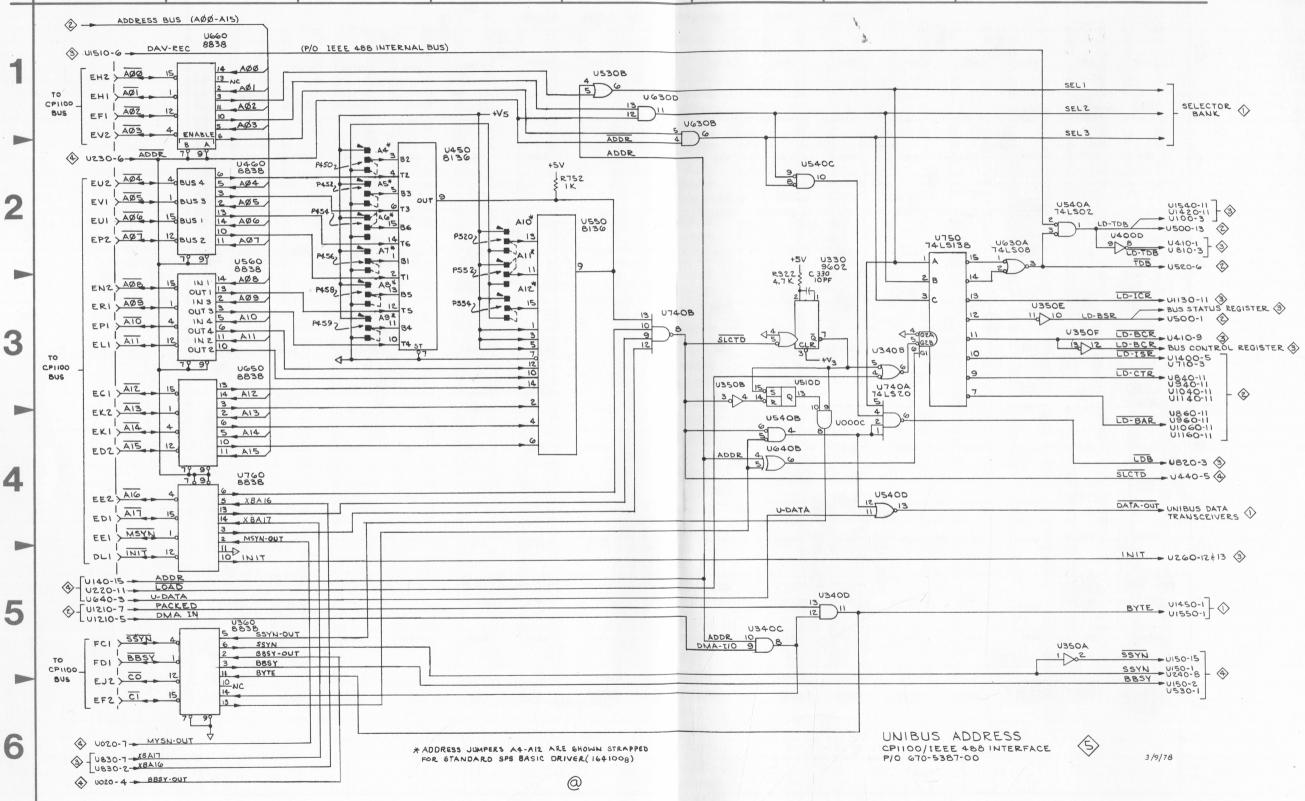

| Bus Address and Control         | 6-2  |

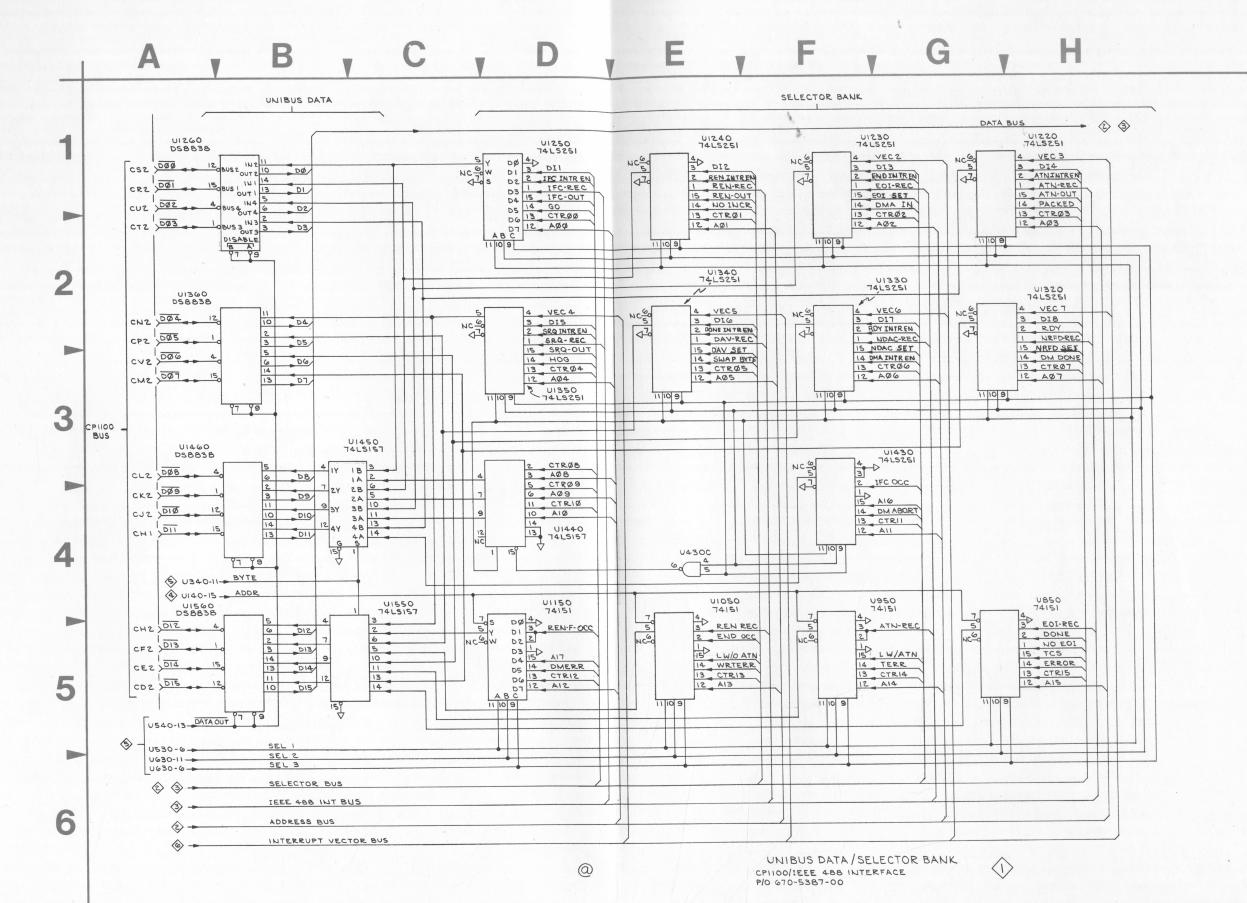

| Data/Selector Bank              | 6-5  |

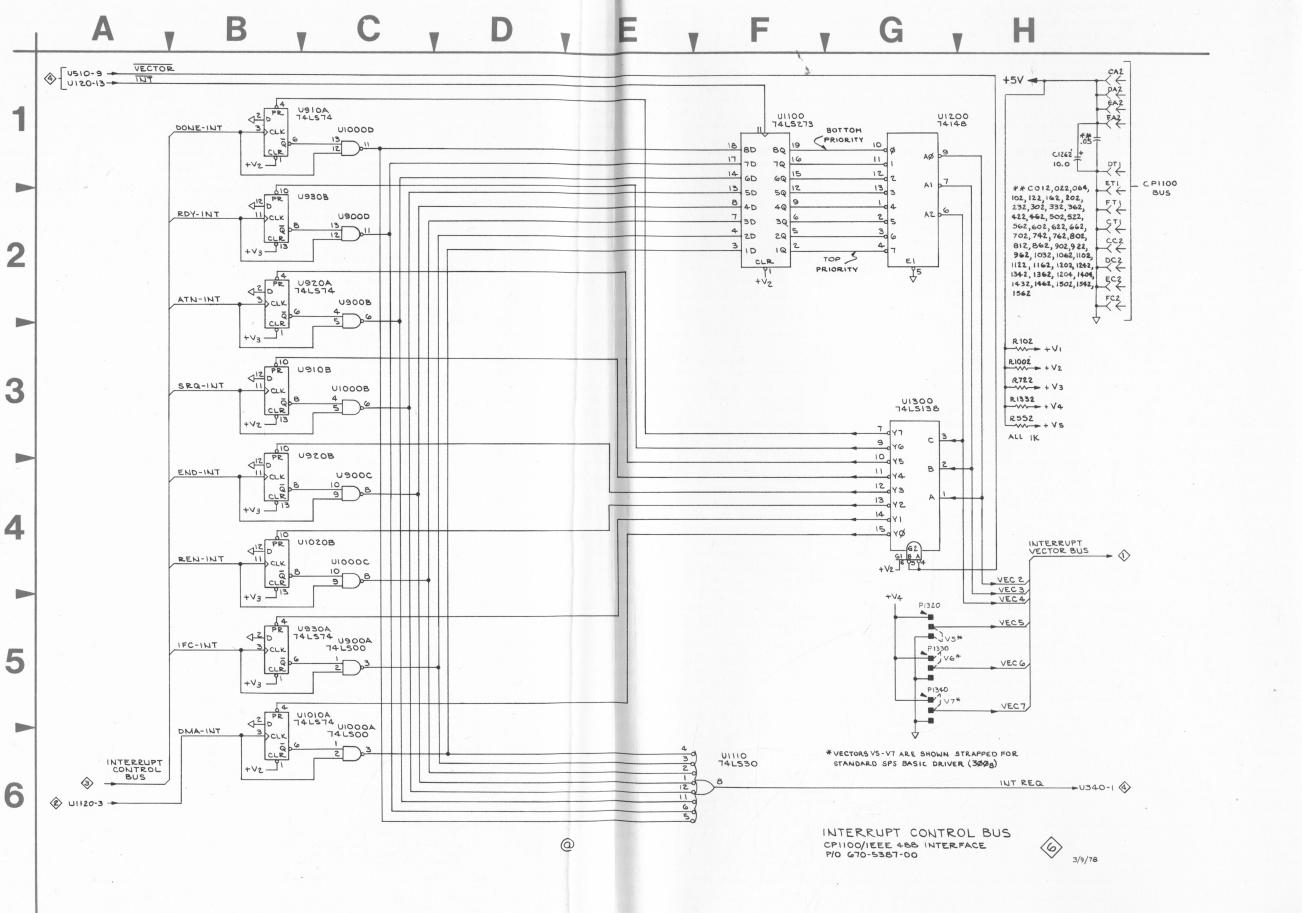

| Interrupt Control Bus           | 6-6  |

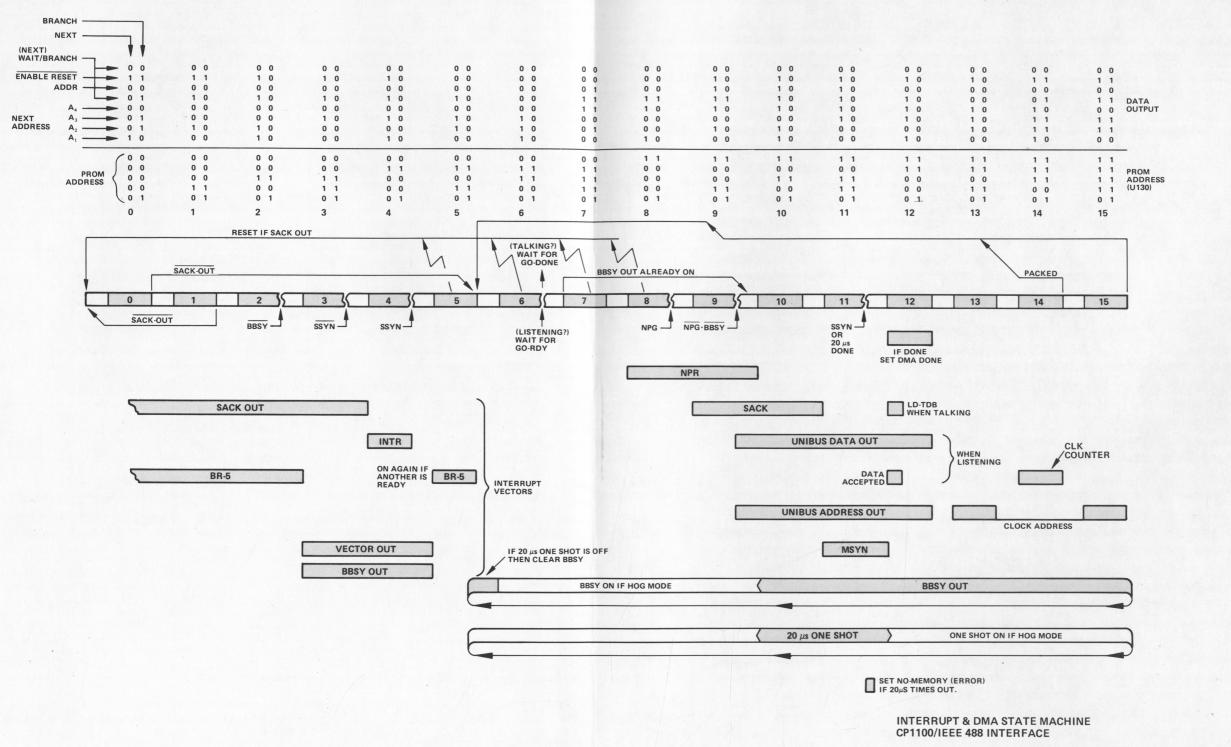

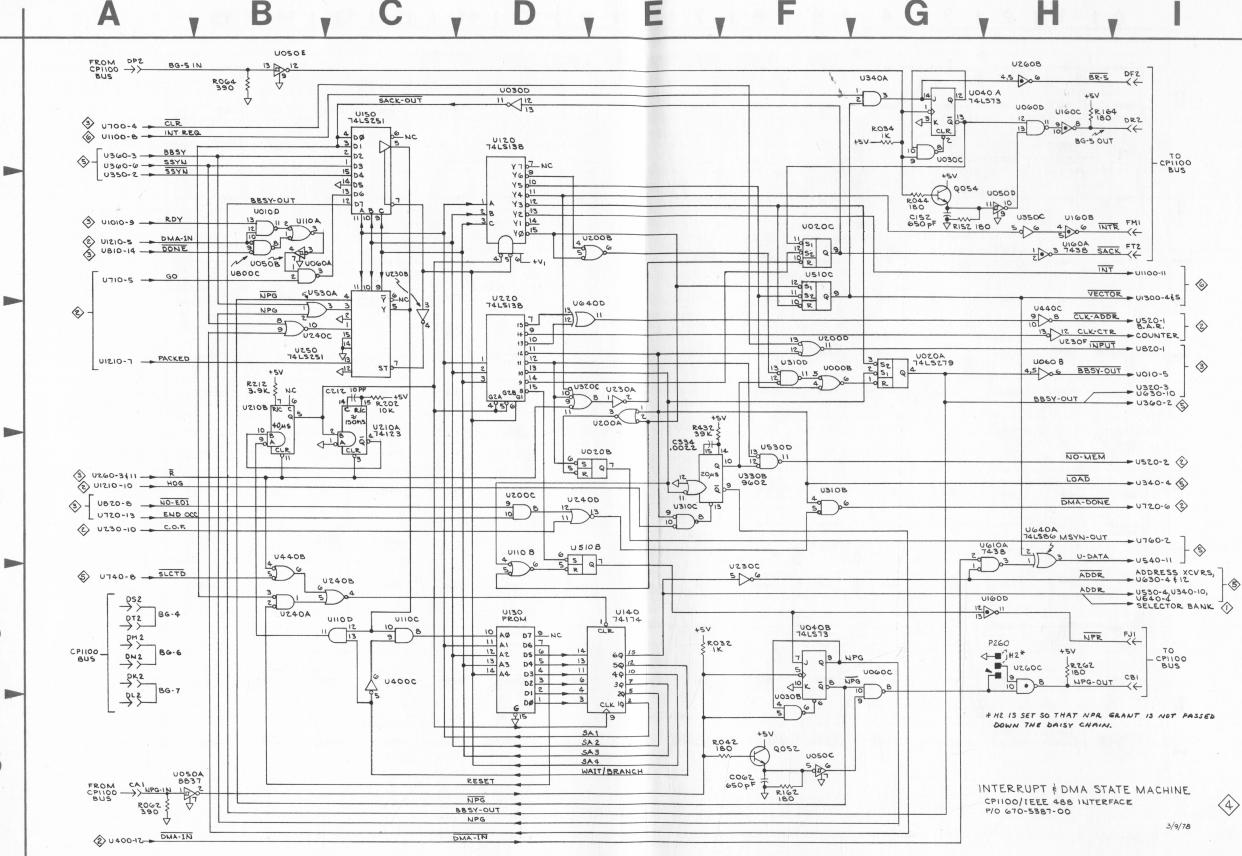

| Interrupt and DMA State Machine | 6-7  |

| Introduction                    | 6-7  |

| Machine Operation               | 6-8  |

| Source Handshake                | 6-15 |

| Acceptor Handshake              | 6-18 |

| Interface Registers             | 6-19 |

| General                         | 6-19 |

| Attention Received              | 6-20 |

| Attention Sent                  | 6-20 |

| Interface Clear                 | 6-21 |

|                                 |      |

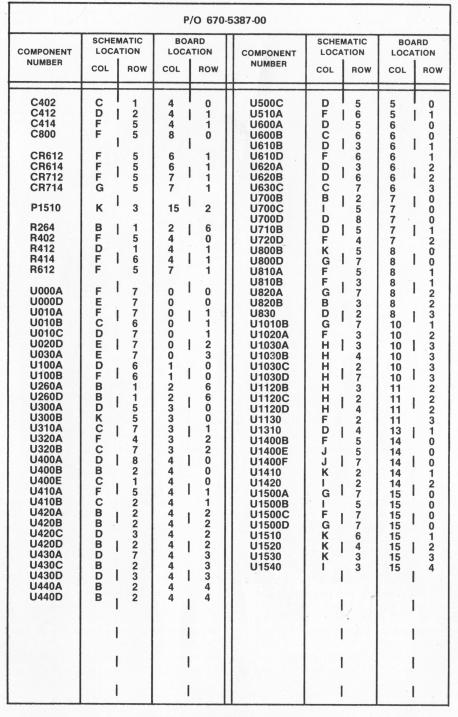

# SECTION 7 - REPLACEABLE PARTS LIST 7-1 Electrical 7-1 Mechanical 7-7

### SECTION 8 - DIAGRAMS

Block Diagram A Block Diagram B State Machine (DMA)

### SCHEMATIC DIAGRAMS

| UNIBUS Data/Selector Bank     | 1 |

|-------------------------------|---|

| BAR/CTR/ISR                   | 2 |

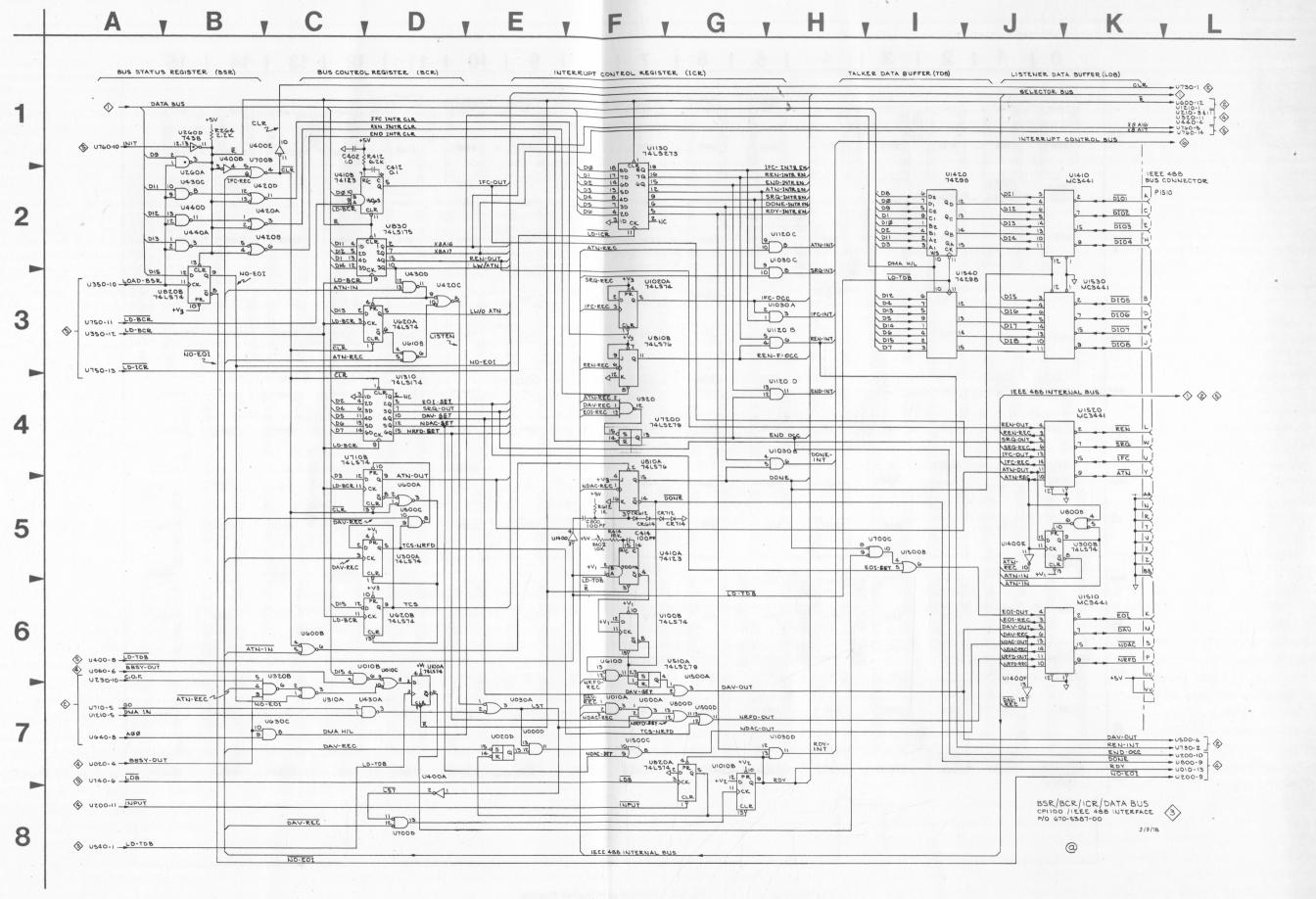

| BSR/BCR/ICR/Data Bus          | 3 |

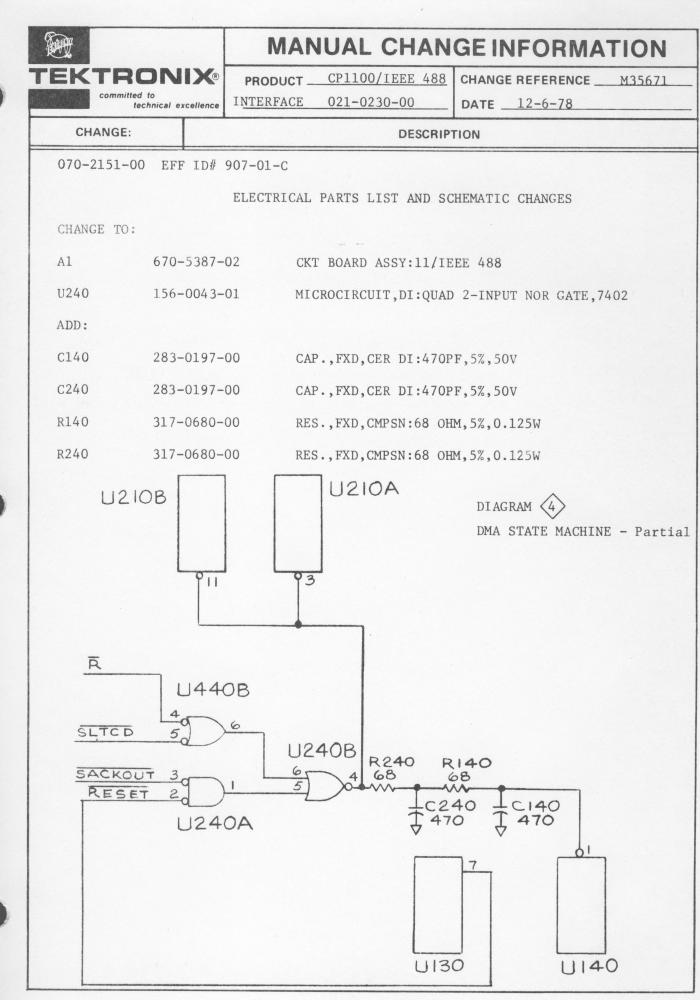

| Interrupt & DMA State Machine | 4 |

| UNIBUS Address                | 5 |

| Interrupt Control Bus         | 6 |

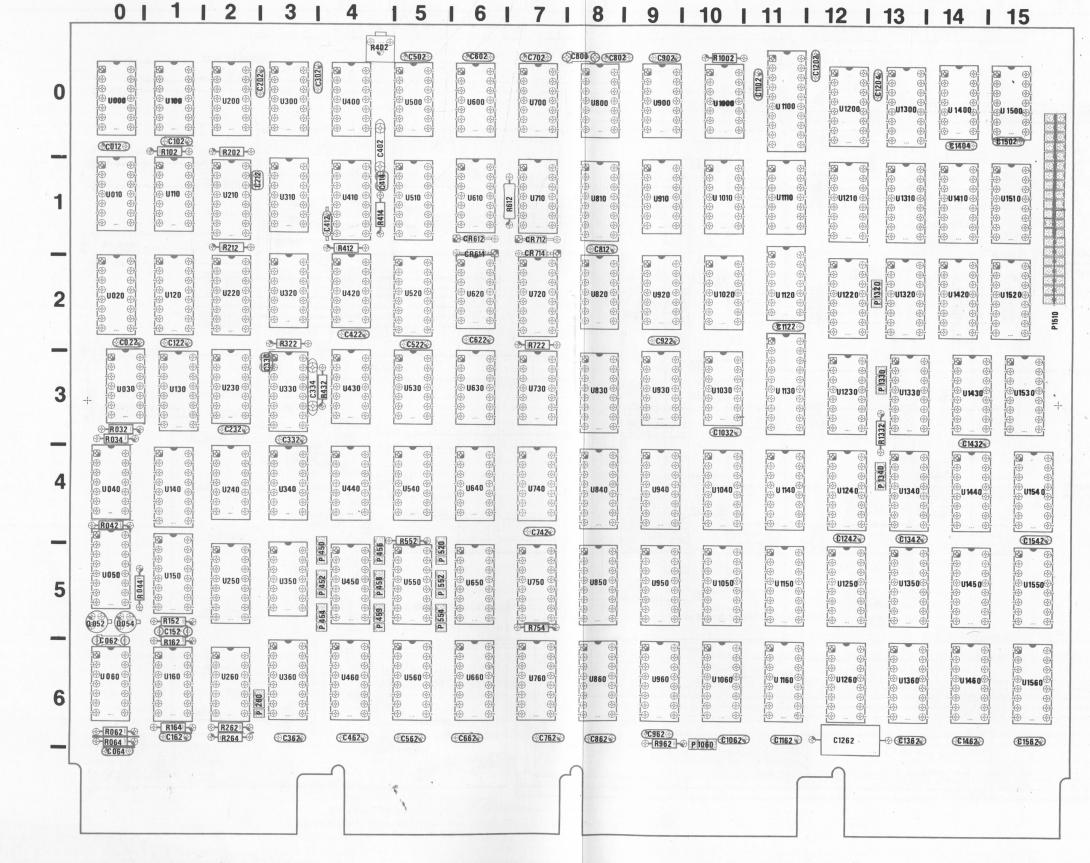

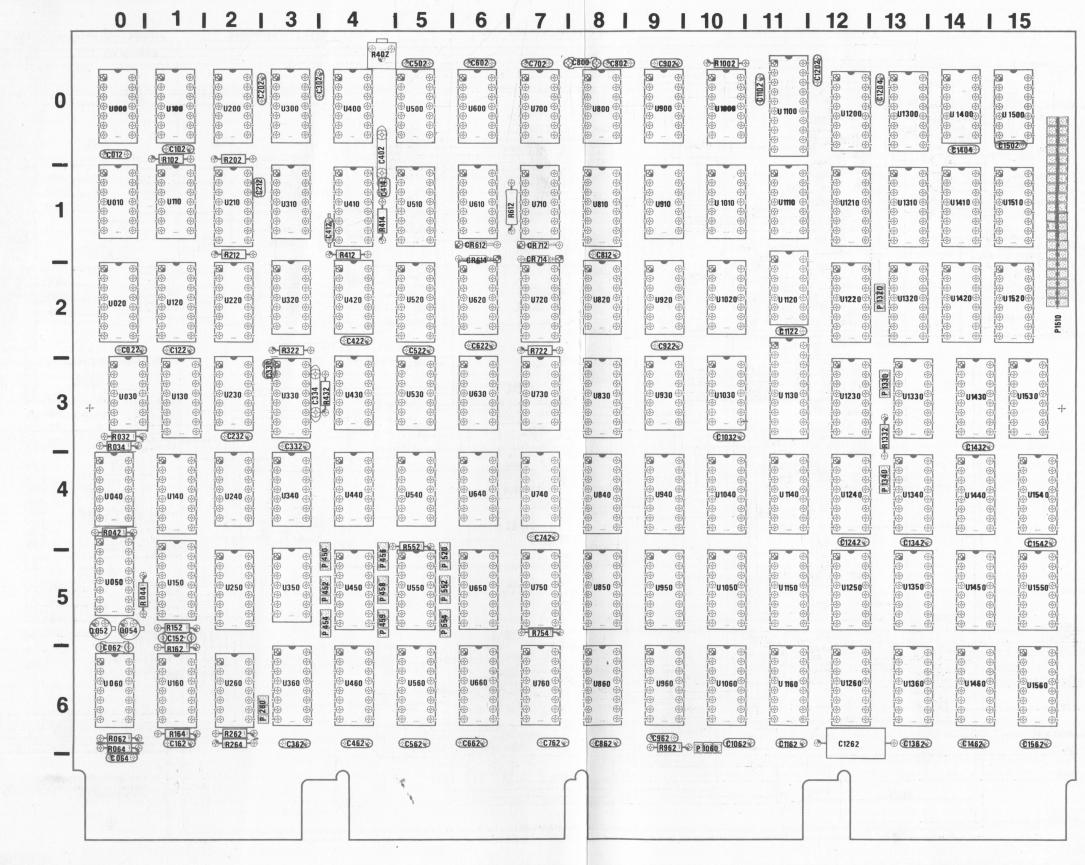

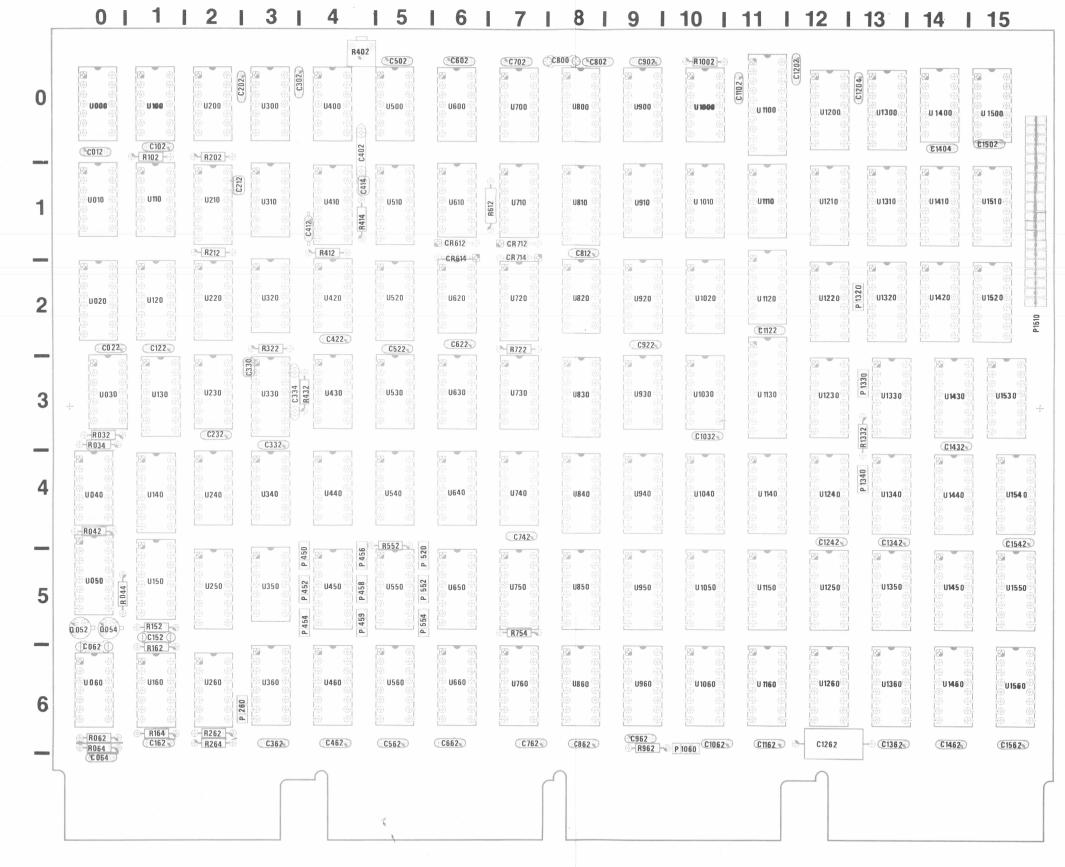

### COMPONENT LOCATORS

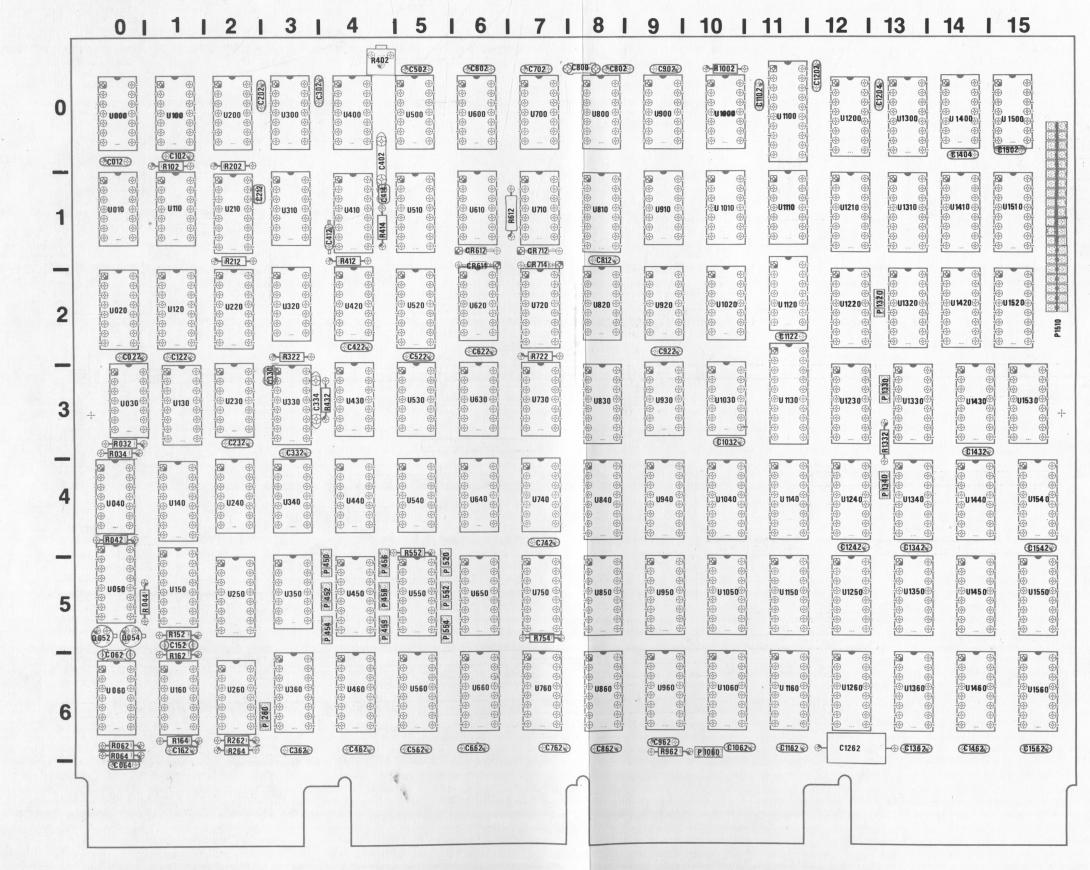

Located on reverse side of foldouts

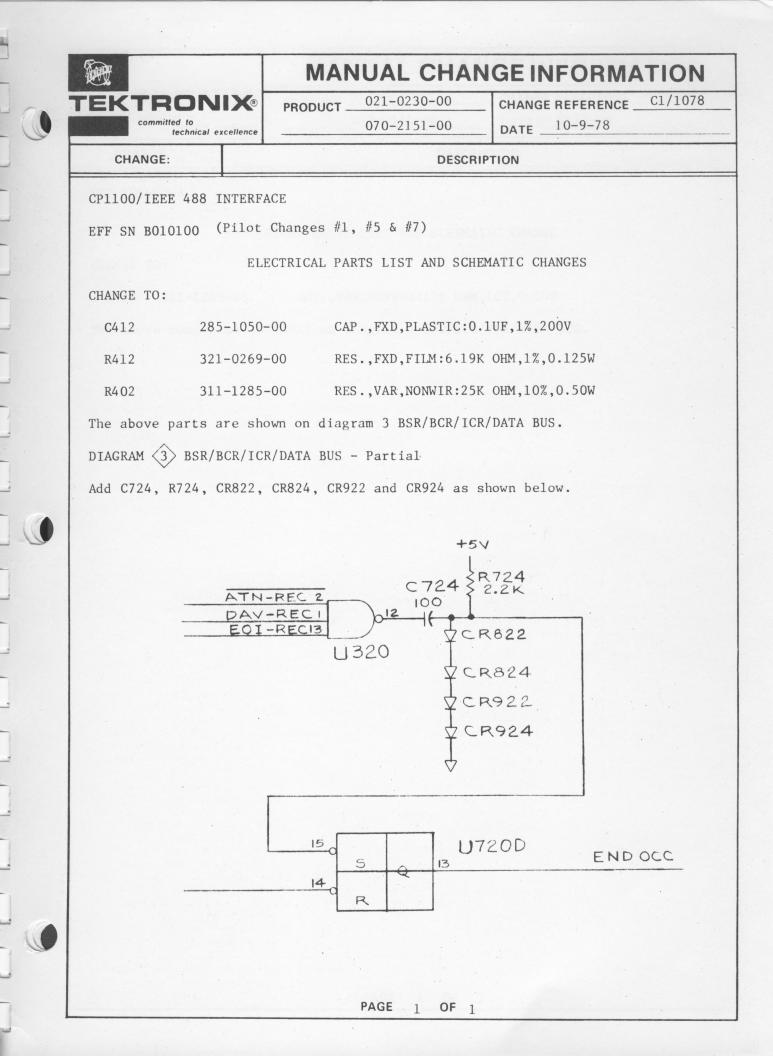

### CHANGE INFORMATION

#### SECTION 1

#### INTRODUCTION

### Manual Organization

This manual contains two main divisions: programming and service.

When used with Tektronix software that includes a driver for this interface, the interface appears transparent to the operator and programmer. The first main division of this manual introduces the CP1100/ IEEE 488 Interface and the IEEE 488 general purpose bus. Register addresses, register formats, interrupt handling, interrupt vector addresses, DMA transfers, and interface protocol are discussed to aid an assembly language programmer.

A warning page separates the second main division of this manual. Information following the warning page is intended for qualified service personnel only. The servicing instructions cover address and vector strap options, installation, cabling, and maintenance. Circuit description, parts lists, component locator, and schematic diagrams follow.

### Interface Description (General)

The TEKTRONIX CP1100/IEEE 488 Interface is an assembly designed for use in TEKTRONIX CP1100-series controllers such as the TEKTRONIX CP1164. The interface includes the circuit card, a 2 meter cable (Tektronix Part Number 012-0809-00) to connect the interface to the IEEE 488 bus, and the instruction manual.

The interface can be used in other controllers that utilize the Digital Equipment Corporation UNIBUS, such as the PDP-11/04, PDP-11/05, PDP-11/10, PDP-11/34, PDP-11/35, PDP-11/40, and PDP-11/45; generally all of the PDP-11 models except the PDP-11/03 and other PDP-11 controllers based on the LSI-11 processor.

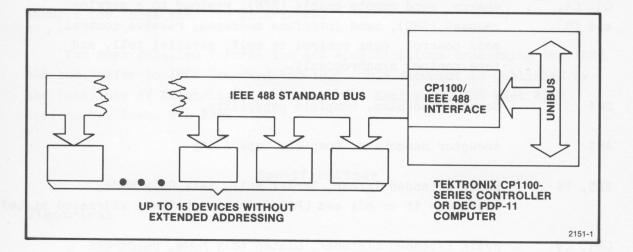

When this interface circuit card is properly installed, the controller can exchange data with and control instruments connected to a general purpose bus (see Fig. 1-1) as specified by IEEE Standard 488-1975.

The CP1100/IEEE 488 Interface provides both direct memory access (DMA) and processor controlled data transfers (program) to or from the IEEE 488 bus. DMA transfer rates up to 400 K bytes/sec can be achieved by this interface. To reduce the load on the processor, the source and acceptor handshakes are implemented in hardware. Other DMA features of the interface include:

1. Capability to pack two bytes into a word. This is useful for acquiring data from digitizers which have more than eight bits per word, or for transferring command text strings.

2. Capability to swap the order in which bytes are sent or received when data is packed. This assures compatibility with both high byte first or low byte first 16-bit word transfers.

3. Capability to address memory space in either direction by incrementing or decrementing a Bus Address Register.

4. Operation in the burst (hog) or non burst (non hog) mode, allowing the user to make best use of DMA cycle stealing. For either mode, protection is built in to allow the processor to take control if the IEEE 488 bus should hang (or cycles too slowly).

Eight addressable registers and eight interrupt vectors are provided by the interface. The interface register addresses and the vector address range are user-set by selecting the desired jumper (strap) positions on the interface card. Strap selection, register addresses, register formats, and interrupt vectors are discussed in other sections of this manual.

With appropriate software, the controller can implement the full capabilities allowed by the interface functions specified by IEEE Standard 488-1975, except for responding to a parallel poll conducted by another controller on the bus. The CP1100/IEEE 488 Interface can perform a parallel or serial poll of instruments on the IEEE 488 bus when the CP1164 controller is acting as the controller-in-charge. See Fig. 1-1 for a system block diagram using this interface.

## Fig. 1-1. Block diagram of an IEEE 488-compatible system using the CP1100/IEEE 488 Interface.

Up to 15 devices (including this interface) can be electrically connected to the IEEE 488 bus. The total bus length allowed by the standard is 20 meters. Normally, the devices are separated by cables no more than 2 meters in length. If this is not the case, a bus termination network must be provided for each 2 meters of cable length. If the required terminations are lumped, performance of the bus may be degraded.

IEEE Standard 488-1975 designates 31 primary address codes and 31 secondary address codes for talkers and listeners using the bus to communicate; this addressing scheme provides a total of 961 addresses.

1-3

### **IEEE 488 Interface Function Subsets**

The IEEE 488 interface function subsets (defined by the standard) that can be implemented by a controller using this interface and the appropriate software are:

C1, C2, System controller, send interface clear (IFC) and take C3, C4, charge, send remote enable (REN), respond to a service and C5 request (SRQ), send interface messages, receive control, pass control, pass control to self, parallel poll, and take control synchronously.

SH1 Source Handshake, complete capability.

AH1 Acceptor Handshake, complete capability.

- TE5, T5 Basic Extended Talker, Serial Poll, Talk Only Mode, Unaddress if or MSA and LPAS (listener primary addressed state).

- LE3, L3 Basic Extended Listener, Listen only Mode, Unaddress if MSA and TPAS (Talker primary addressed state).

- SR1 Service Request, complete capability.

- RL1 Remote-Local, complete capability.

- PPO Parallel Poll, no capability (does not respond).

- DC1 Device Clear, complete capability.

DT1 Device Trigger, complete capability.

My Listen Address (MLA), My Talk Address (MTA), and My Secondary address (MSA) are all established by software.

### Related Information

Tektronix, Inc. provides manuals for the CP1100-series controllers. Digital Equipment Corporation publishes manuals and handbooks for its line of PDP-11 computers. Examples are the PDP-11 Processor Handbook and PDP-11 Peripherals Handbook. Information on device interfaces for TEKTRONIX IEEE 488-compatible instruments is available in Tektronix manuals for those specific interfaces.

For more detailed information and specifications concerning the IEEE 488 bus, refer to IEEE Standard 488-1975. This document is published by the Institute of Electrical and Electronics Engineers, 345 East 47th Street, New York, New York, 10017.

### Specifications

### Electrical

#### Power Requirement:

This interface requires 1.5 amperes at +5 Vdc (typical) from the controller mainframe.

#### Signal Levels:

All signal levels are TTL compatible. Refer to controller mainframe specifications for Unibus signal levels and IEEE Standard 488-1975 for signal levels on the IEEE 488 bus.

### Environmental

The interface operates within the same environmental limits as the controller. Refer to specifications in the controller manual.

### Mechanical

0

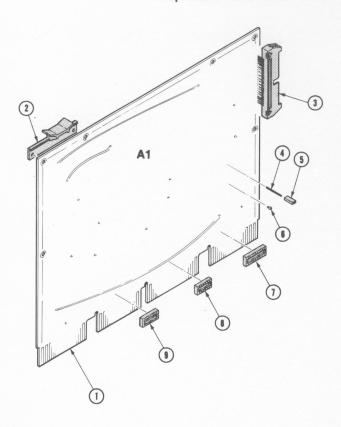

The interface is contained on a quad-height, extended length card and requires a full slot in the peripheral backplane of the controller (see Fig. 9.2, PDP-11 Peripherals Handbook).

#### **SECTION 2**

### **IEEE 488 BUS DESCRIPTION**

### Introduction

All instruments (devices) designed for use with the IEEE 488 bus must conform to IEEE Standard 488-1975 (ANSI MC1.1-1975), Standard Digital Interface for Programmable Instrumentation. IEEE Standard 488-1975 specifies the mechanical, electrical, and functional elements of the digital interface system.

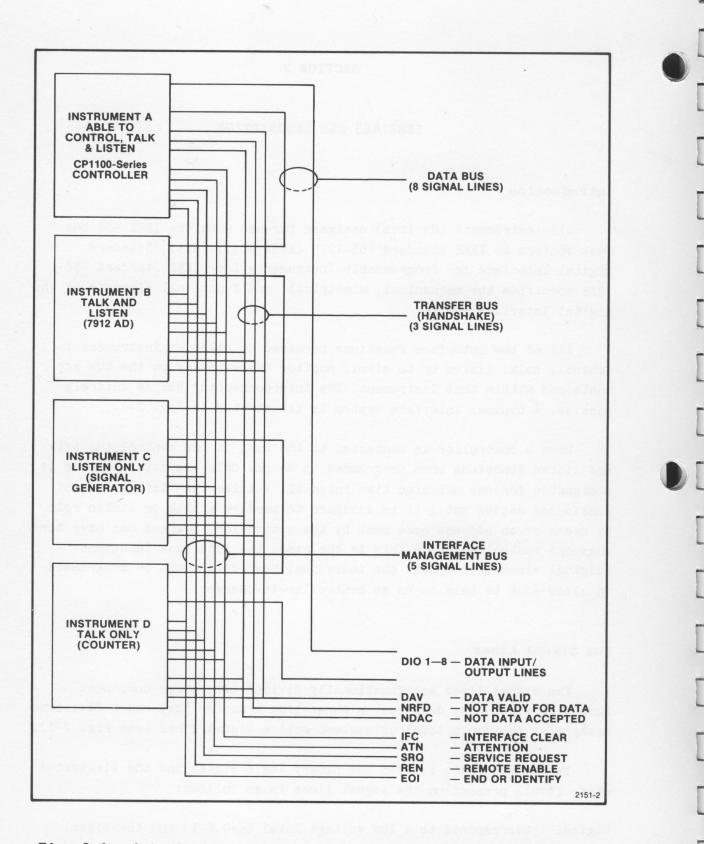

All of the interface functions required to allow an instrument to control, talk, listen or to simply monitor the activity on the bus are contained within that instrument. The interconnecting bus is entirely passive. A typical interface system is illustrated in Fig. 2-1.

When a controller is connected to the bus, it can control the talk and listen functions when programmed to do so. Only one active talker is designated for any selected time interval. A talker or listener is not considered active until it is assigned to perform a talk or listen role by means of an address code sent by the controller. Systems can have more than one controller; when this is the case, the interface functions (digital circuitry) within the individual controllers can be programmed to allow each to take turns as controller-in-charge.

### **Bus Signal Lines**

0

The signal lines are functionally divided into three component buses: an eight-line data bus, a three-line transfer bus, and a five-line management bus for a total of sixteen active signal lines (see Fig. 2-1).

The relationship between the binary logic states and the electrical state levels present on the signal lines is as follows:

2-1

Logical 1 corresponds to a low voltage level ( $\leq$ +0.8 V) and the signal line is asserted.

Fig. 2-1. A typical system showing the IEEE 488 bus organization.

Logical 0 corresponds to a high voltage level ( $\geq$ +2.0 V) and the signal line is not asserted.

The electrical states are based on standard TTL levels where the power source does not exceed +5.25 Vdc (referenced to logic ground).

#### The Data Bus

The data bus contains eight bidirectional signal lines, DIO1 through DIO8. One byte of information (eight bits) is transferred over the bus at a time. DIO1 represents the least significant bit in the byte and DIO8 represents the most significant bit in the byte. Data is transmitted in a byte-serial, bit-parallel format over the data bus.

Since the bus operates asynchronously, the transfer rate over the data bus is a function of the slowest instrument taking part in a data transfer at any one time. Data bytes can be formatted in ASCII (ISO 7-bit) code representation with or without parity, or they can be formatted in machine dependent binary code. The term "machine dependent binary code" refers to an internal binary format used by a device to store certain programs and data.

#### The Management Bus

The management bus is a group of five signal lines which are used to control data transfers over the data bus. The basic signal definitions for the management bus are as follows:

Interface Clear (IFC). The IFC signal line is asserted by the system controller to place all interface circuitry in a predetermined quiescent (power on) state.

The system controller is the only source for this signal. IEEE 488-1975 designates only three interface messages (universal commands) to be recognized during the time that IFC is asserted, device clear (DCL), local lockout (LLO), or parallel poll unconfigure (PPU).

Attention (ATN). The ATN signal line is asserted by a controller when peripheral instruments connected to the bus are being assigned as

talkers or listeners and for other interface control traffic. As long as the ATN signal line is asserted (ATN = 1), only instrument address codes and control messages are transferred over the data bus. When the ATN signal line becomes unasserted only those instruments designated as talkers and listeners can take part in the data transfer. The controller is the only source of the ATN signal.

Service Request (SRQ). Any peripheral instrument connected to the bus can request the attention of the controller by asserting the SRQ line.

The controller responds by asserting ATN and executing a serial poll to determine which instrument is requesting service. After the peripheral instrument requesting service is found (an instrument requesting service identifies itself by asserting its DIO7 line after being addressed) program control can be transferred to a service routine for that instrument. When the service routine is completed, program control returns to the main program. The SRQ signal line is released (unasserted) when the instrument requesting service is polled.

**Remote Enable (REN).** The REN signal line is asserted by the system controller whenever the interface system is operating under remote program control. The REN signal is used (in conjunction with other control messages) to cause an instrument on the bus to select between two alternate sources of programming data. A remote-local interface function is used to indicate to an instrument that either input information from the front-panel controls (local) or corresponding input information from the interface (remote) is to be used. Some instruments are designed so that specifically designated front-panel controls are enabled during a remote programming sequence.

End or Identify (EOI). The EOI signal can be used by a talker to indicate the end of a data transfer sequence. The talker asserts the EOI signal line as the last byte of data is transmitted. In this case, EOI is essentially a ninth data line and must observe the same setup times as the DIO lines. When the controller is programmed to listen, it assumes that a data byte received is the last byte in the transmission (if the EOI signal line has been asserted). When the controller is talking, it may assert the EOI signal line as the last byte is transferred. The EOI signal is also used in conjunction with the ATN signal if a parallel polling sequence is conducted by the controller. EOI is not used during

serial polls.

### The Transfer Bus (Handshake)

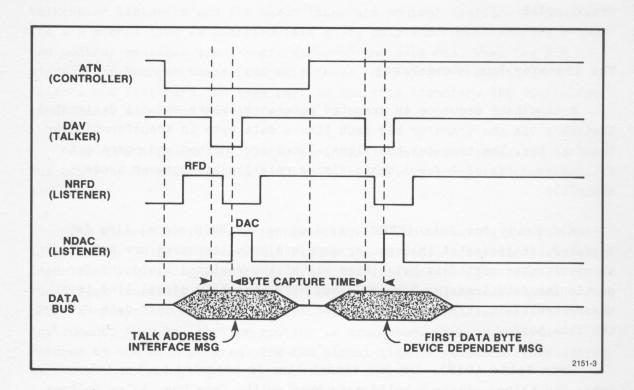

A handshake sequence is executed between a talker and all designated listeners via the transfer bus each time a data byte is transferred over the data bus. The transfer bus signal lines are defined and operate as follows (see Fig. 2-2 for a basic timing relationship between these signals):

Not Ready for Data (NRFD). As long as the NRFD signal line is asserted, it indicates that one or more assigned listeners are not ready to receive the next data byte. When all of the assigned listeners for a particular data transfer have released NRFD, the NRFD signal line is unasserted. This tells the talker that it may place the next data byte on the data bus.

Data Valid (DAV). The DAV signal line is asserted by the talker after the talker places a valid data byte on the data bus. A low voltage level for the asserted DAV signal tells each assigned listener to accept the byte presently on the data bus. The talker is inhibited from asserting the DAV signal line as long as the NRFD signal line is asserted.

Not Data Accepted (NDAC). The NDAC signal line is asserted (held low true) by each assigned listener until the listener accepts the data byte currently on the data bus. When all assigned listeners have accepted the data byte, the NDAC signal line is released (unasserted). This tells the talker to remove the data byte from the data bus. The DAV signal line is unasserted when all assigned listeners have accepted the data byte.

#### **Bus Messages**

Messages on the bus are either interface messages or device dependent messages and are coded according to the ASCII (ISO 7-bit) code. Interface messages are used to manage the interface functions of the instruments; for example, they are sent with attention (ATN) asserted and designate a specific instrument to talk and others to listen. Device dependent messages are sent over the bus with ATN unasserted and are not

### Fig. 2-2. A typical handshake timing sequence (idealized). Byte capture time is dependent on the slowest instrument involved in the handshake.

used by the instrument interfaces to change their state or configuration. Device dependent messages are passed on to the device functions of the instruments and can be considered to be data, such as a voltage reading by a digital multimeter or the functional setting of a front panel control.

### Control Commands

| Octal Code | Command | Meaning                          |

|------------|---------|----------------------------------|

|            |         |                                  |

| 024        | DCL     | Device Clear                     |

| 010        | GET     | Group Execute Trigger            |

| 001        | GTL     | Go To Local                      |

| 021        | LLO     | Local Lock Out                   |

| 005        | PPC     | Parallel Poll Configure          |

| 16X        | PPD     | Parallel Poll Disable (see note) |

| 14X        | PPE     | Parallel Poll Enable (see note)  |

| 025        | PPU     | Parallel Poll Unconfigure        |

| 004        | SDC     | Selected Device Clear            |

| 031        | SPD     | Serial Poll Disable              |

| 030        | SPE     | Serial Poll Enable               |

| 011        | TCT     | Take Control                     |

| 077        | UNL     | UNListen                         |

| 137        | UNT     | UNTalk                           |

|            |         |                                  |

2-7

### NOTE

The exact binary format for the PPE command is: 110SNNN where "NNN" is a number in the range 0 to 7 designating which data line to send the parallel poll response on, and "S" is the sense returned on data line NNN for a true response.

The exact binary format for the PPD command is 111DDDD, where D specifies a don't care bit that must be sent as a 0 but does not need to be decoded by the receiving device.

GET, GTL, PPC, and SDC, are sent to an instrument or group of instruments that have been addressed to listen. The TCT command is sent to a controller that has been addressed to talk.

DCL, LLO, SPE, SPD, and PPU are universal commands and affect all instruments on the bus.

The UNT command disables the talk mode of a previously selected talker, while the UNL command disables the listen mode of all previously selected listeners.

### SECTION 3

#### INTERFACE REGISTERS AND INTERRUPT VECTORS

#### Introduction

This interface has eight addressable (programmable) registers and eight interrupt vectors that allow the programmer to control a system of instruments interfaced according to IEEE Standard 488-1975. Through the interface, the program can act as the system controller or it can pass control back and forth with another device that can act as controller-incharge. The program can also act as a talker only or as a listener only (to monitor activity on the bus). When the program is acting as the controller in charge it can address devices, send universal and addressed commands, and transfer device-dependent messages. This interface can conduct a serial or parallel poll of instruments on the bus, but will not respond to a parallel poll conducted by another device. It can, if so programmed, respond to a serial poll.

#### Programmable Registers

Table 3-1 illustrates the data format and bus addresses (octal) for the eight interface registers. The Talker Data Buffer (TDB) and the Listener Data Buffer (LDB) are data ports to and from the IEEE 488 bus. The Interrupt Control Register (ICR) provides interrupt management bits. The Bus Status Register (BSR) and the Bus Control Register (BCR) provide a way to monitor and set the IEEE 488 bus control lines; these two registers also include interrupt clearing and interface mode control bits. The Interface Status Register (ISR) supplies information about direct memory access (DMA) operation. The Byte Counter Register (CTR) and the Bus Address Register (BAR) are used when DMA transfers are implemented between the controller bus and the IEEE 488 bus.

3-1

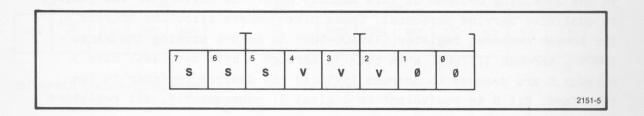

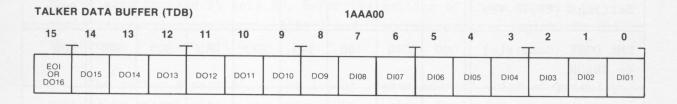

#### TALKER DATA BUFFER (TDB) **1AAA00** 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 EOI OR DO15 DO14 DO13 DO12 DO11 DO10 DO9 D108 D107 DI01 D106 D105 D104 D103 D102 DO16 LISTENER DATA BUFFER (LDB) **1AAA02** 12 11 10 9 8 7 6 15 14 13 5 4 3 2 1 0 REN EOI ATN REN FALSE D108 D107 D106 D105 D104 D103 D102 DI01 INTERRUPT CONTROL REGISTER (ICR) **1AAA04** 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 REN RDY INTR DONE SRQ ATN END IFC ATN END OCC REN DONE FALSE OCC INTR RDY INTR INTR INTR ENBL ENBL ENBL ENBL ENBL **BUS STATUS REGISTER (BSR) 1AAA06** 15 14 13 12 11 10 9 8 7 6 5 4 3 2 0 1 END IFC INTR REN NO EOI DMA INTR DMA LOCAL NRFD NDAC DAV SRQ ATN EOI REN IFC CLR CLR CLR BUS CONTROL REGISTER (BCR) **1AAA10** 15 14 13 12 11 10 9 8 7 6 5 4 3 2 0 1 LIST W/O ATN LIST XBA XBA NRFD OUT NDAC OUT SRQ DAV EOI IFC OUT TCS ATN REN ATN 17 16 INTERFACE STATUS REGISTER (ISR) **1AAA12** 15 14 13 12 11 10 9 7 8 6 5 2 4 3 1 0 DMA INTR ENBL DMA IN/ OUT NO INCR/ DECR SWAP TIME WRITE DMA DMA HOG ERR DMA PACK BYTE GO ERR ABORT DONE BYTE COUNTER REGISTER (CTR) 1AAA14 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 BUS ADDRESS REGISTER (BAR) **1AAA16** 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TABLE 3-1 CP1100/IEEE 488 Interface Registers

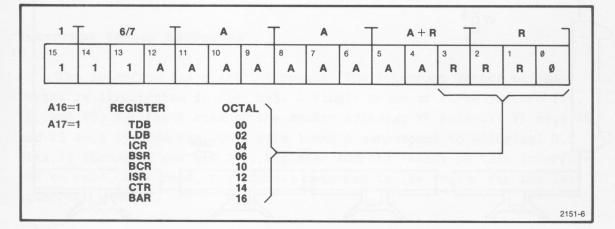

#### Register Addresses

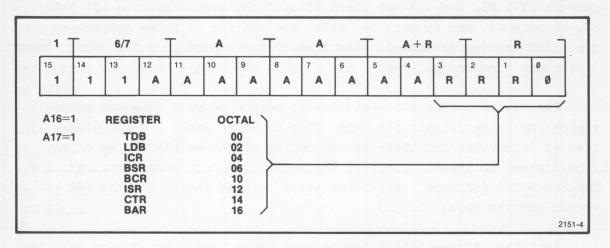

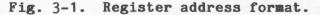

The address format for the eight interface registers is illustrated in Fig. 3-1.

Address bits 15 through 13 are hardwired for a logical 1. Bits 12 through 4 are set to a logical 1 or 0 by a group of nine jumpers as shown in the Servicing Section of this manual. Refer the setting of the jumpers to qualified service personnel. These nine jumpers allow the address of the lowest numbered register (1AAA00-TDB) to be set withing the range  $160000_8$  through  $177760_8$ . When bits 12 through 4 have been set, bits 3 through 0 are decoded to address (select) the desired register in the interface. Bit 0 is equivalent to logical 0; consequently, all registers have an even address.

For TEK SPS BASIC Software, the upper bits of the register address decoding logic are set for  $164100_8$ . TEK SPS BASIC Software allows the use of more than one interface. The address straps of each interface can be set to create successively numbered addresses. For example:

| Interface | 0 | 1641008 | through | 1641168 |

|-----------|---|---------|---------|---------|

| Interface | 1 | 1641208 | through | 1641368 |

| Interface | 2 | 1641408 | through | 1641568 |

### **Interrupt Vector Addresses**

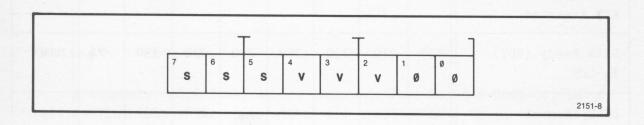

The CP1100/IEEE 488 interface has eight interrupts. The vector address format is illustrated in Fig. 3-2. A single group of three jumpers (V7, V6, and V5) set the S bits of the vector address. V7 sets S7, V6 sets S6, and V5 sets S5. Refer the setting of these jumpers to qualified service personnel. Bits 1 and 0 correspond to a logical 0. Bits 15 through 8 return all 0's.

The vector straps allow the lowest vector address (highest priority vector) to be set within the range 0008 to 3408. Table 3-2 contains a list of interrupts and their corresponding addresses (listed in order from highest to lowest priority) for eight different strap settings. For TEK SPS BASIC Software, the vector strap setting is 110 and the SRQ vector address should be 320.

Register address 1AAA00 can be read. When read, the address returned is the vector for the last interrupt granted.

Fig. 3-2. Interrupt vector address format.

| TABLE 3-2 |         |      |       |       |          |           |  |  |  |  |  |

|-----------|---------|------|-------|-------|----------|-----------|--|--|--|--|--|

| Interrupt | vectors | and  | their | corre | sponding | addresses |  |  |  |  |  |

| for       | differe | nt v | ector | strap | settings |           |  |  |  |  |  |

| Vector Strap<br>Settings (V7,V6,V5)    | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 | V-bit<br>Code |

|----------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|---------------|

| DMA DONE (Complete)<br>or ERROR        | 000 | 040 | 100 | 140 | 200 | 240 | 300 | 340 | 000           |

| Interface Clear<br>IFC Detected        | 004 | 044 | 104 | 144 | 204 | 244 | 304 | 344 | 001           |

| Remote Enable<br>REN FALSE             | 010 | 050 | 110 | 150 | 210 | 250 | 310 | 350 | 010           |

| END of Message<br>DAV and EOI Asserted | 014 | 054 | 114 | 154 | 214 | 254 | 314 | 354 | 011           |

| Service Request<br>SRQ Asserted        | 020 | 060 | 120 | 160 | 220 | 260 | 320 | 360 | 100           |

| Attention<br>ATN Asserted              | 024 | 064 | 124 | 164 | 224 | 264 | 324 | 364 | 101           |

| Data Ready (RDY)<br>in LDB             | 030 | 070 | 130 | 170 | 230 | 270 | 330 | 370 | 110           |

| DONE (Source<br>Handshake Completed)   | 034 | 074 | 134 | 174 | 234 | 274 | 334 | 374 | 111<br>(NONE) |

### **Register Descriptions**

This part of the manual contains a functional description for the valid bits in each register to aid the programmer and service person. It describes the bit functions and their relationships to each other and discusses how and under what circumstances each bit is set or cleared (reset). In this section a RESET instruction refers to a LOCAL RESET function, a controller RESET, or whenever INIT is asserted on the controller's internal bus.

Talker Data Buffer (TDB). The Talker Data Buffer is used to write to the IEEE 488 bus in any of the formats described below. The TDB is a write-only register. However, performing a read operation on register address 1AAA00 returns the vector address for the last interrupt granted. Reading register address 1AAA00 at system initialization time allows the programmer to determine how the vector address straps are set.

1. For a non-DMA transfer from the controller to a device on the IEEE 488 bus, data is written into this register. The low byte is latched and output under control of the interface source handshake logic. The MSB (D016) is also latched; if set, the interface asserts the EOI message. Bits 14 through 8 are ignored (not latched or output on the bus).

2. For a DMA transfer to the IEEE 488 bus in the "unpacked" mode, the DMA IN/OUT and PACK MODE bits in the Interface Status Register must be cleared. The interface DMA control logic places a word in this register. The low byte is latched and output on the bus by the interface source handshake logic; the high byte is ignored.

3. For a DMA transfer to the IEEE 888 bus in the "packed" mode, the DMA IN/OUT bit must be cleared and the PACK MODE bit set. The interface DMA control logic places a word in this register. Either the high byte or the low byte is latched first, depending on the condition of the SWAP BYTE ORDER and NO INCR/DECR bits in the Interface Status Register (ISR), the setting of jumper H1, and the value of the least significant bit in the Bus Address Register (BAR). The byte that is latched is output on the bus by the interface source handshake logic. The

DMA control logic then performs another read cycle to latch and output the other byte. The user should not write to or read from register 1AAA00 while a DMA transfer is taking place.

The data written to the bus in any mode is removed from the bus before the source handshake cycle is completed if a RESET instruction is executed, if ATN is asserted by another controller on the bus, or if IFC is asserted. If an error condition (bits 15 through 11 in the ISR) occurs before the handshake is completed, toggling the NDAC OUT bit in the Bus Control Reigster (BCR) is the preferred method of clearing the handshake and removing data from the bus (see Section 4, Software Protocol). The DONE bit in the Interrupt Control Register (ICR) is set automatically when the handshake cycle is completed.

#### Bits 15 - 8: D016-D09 (write only).

Function:

High byte data for the DMA "packed" mode. Bit 15 can be programmed (if desired) for the EOI function in the non-DMA mode only. When set for EOI, it causes the EOI message to be sent at the same time as the last data byte.

Set:

0

By writing a 1 into the desired bit. These bits are cleared when outgoing data is accepted by all assigned listeners or otherwise removed from the bus (see above).

### Bits 7 - 0: DIO8-DIO1 (write only).

Function: Low byte data for the DMA "packed" mode. Normal data output for the other modes.

Set: By writing a 1 into the desired bit. These bits are cleared when outgoing data is accepted by all the assigned listeners, by a RESET instruction, when IFC is asserted, or if another controller asserts ATN before the handshake is completed.

Listener Data Buffer (LDB). The Listener Data Buffer is a read only register and receives data sent by other devices on the IEEE 488 bus. This register is normally read in the non-DMA mode. However, when using the DMA control logic to send data on the IEEE 488 bus (DMA IN/OUT bit in the ISR must be cleared), the LDB can be used to read data as transmitted by this interface. The LISTEN control bits (bits 14 and 13 in the ISR) must be set if the acceptor handshake is to be controlled. Reading the LDB while the DMA control logic is sending allows for self-check procedures.

To accept data (listen to devices on the IEEE 488 bus) in a DMA mode, the interface acceptor handshake logic is enabled as soon as the DMA IN/OUT and GO bits in the ISR are set. For non-DMA listening, the LISTEN bits in the ISR control the enabling of the acceptor handshake function. The interface performs the acceptor handshake cycle and sets the RDY bit in the Interrupt Control Register (ICR) to indicate that valid data can be read from the LDB.

When the LDB is read, it returns the current value of the IEEE 488 data bus lines, the status of the EOI, ATN, and REN control lines, and the condition of the REN FALSE OCC bit. Reading the LDB also clears the RDY bit in the Interrupt Control Register.

### Bits 15 - 12:

## EOI, ATN, REN, REN FALSE OCC, respectively (read only).

Function:

EOI, ATN, and REN are read directly from the bus and indicate the asserted or unasserted states for these control lines. EOI asserted indicates the last data byte sent or received. ATN asserted indicates an interface message (control command) was sent by this interface or by another controller. REN asserted indicates that the system is under remote control. REN FALSE OCC, when read as a 1, indicates that all messages should be interpreted as data sent or received under local mode control (not remote). The REN FALSE OCC bit can be used for non-DMA listening programs if the REN INTR ENBL bit (1) in the ICR is not set. Bits 15 through 12 are ignored when this register is read by the DMA control logic. See Section 4 for more information concerning the REN FALSE OCC bit.

### Bit 12: REN FALSE OCC (read only).

Set:

0

By an internal flip-flop when the REN control line goes from its asserted to unasserted state.

Cleared:

By a RESET instruction, or by writing a 1 into the REN INTR CLR bit (12) in the Bus Status Register (BSR). This bit is set and cleared at the same time as the REN FALSE OCC bit in the Interrupt Control Register.

### Bits 7 - 0: DIO8 - DIO1 (read only).

Function: Read directly from the IEEE 488 data bus in any mode. When read, indicates the current values of the data lines; a 1 indicates that the corresponding bus line is asserted. A talker sending data to this interface does not normally remove the input data until the acceptor handshake cycle is completed.

| INTERF | RUPT C | ONTRO      | DL REGI             | STER (     | ICR)           | 1AAA04 |              |     |                     |                      |                     |                     |                     |                     |                     |  |

|--------|--------|------------|---------------------|------------|----------------|--------|--------------|-----|---------------------|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--|

| 15     | 14     | 13         | 12                  | 11         | 10             | 9      | 8            | 7   | 6 _                 | 5                    | 4                   | 3 _                 | 2                   | 1                   | 0                   |  |

| DONE   | ATN    | END<br>OCC | REN<br>FALSE<br>OCC | IFC<br>OCC | erao<br>1955-1 |        | asa<br>Secto | RDY | RDY<br>INTR<br>ENBL | DONE<br>INTR<br>ENBL | SRQ<br>INTR<br>ENBL | ATN<br>INTR<br>ENBL | END<br>INTR<br>ENBL | REN<br>INTR<br>ENBL | IFC<br>INTR<br>ENBL |  |

Interrupt Control Register (ICR). The Interrupt Control Register provides the interrupt management functions. Two bits are used to indicate completion of the source and acceptor handshake functions.

Bits in this register operate in pairs to generate interrupts related to conditions on the IEEE 488 bus control lines. Low order bits (0-6) enable the interrupts. High order bits (7, 11-15) indicate that interrupt conditions occurred. An interrupt occurs if an enable bit and its associated condition bit are both 1, regardless of which was set first. Once an interrupt occurs, another interrupt for the same condition cannot occur until one of the two bits is cleared and set to 1 again. If more than one interrupt condition is pending when the interrupt request was recognized, the interrupt with the lowest numbered vector address (highest priority interrupt) will be the one sent to the controller program. Refer to the Servicing Section of this manual for additional information concerning the interrupt vectors.

### Bit 15: DONE (read only).

Function:

Data byte transfer complete. Set true when powered up. After data is written into the TDB, the interface performs the source handshake cycle and sets this bit when data has been accepted by all of the assigned listeners (NDAC line is released). The next data byte can then be loaded into the TDB. The DONE interrupt is generated if this bit is set and its associated enabling bit has been set.

Set:

By the NDAC bus line going from an asserted to an unasserted state at the end of a handshake cycle, by a RESET instruction, when IFC is asserted, or when another controller on the bus asserts ATN.

Cleared: By a correct write to the TDB. This bit will not clear if the DAV bus line is already asserted or remains asserted when NDAC is released.

Bit 14: ATN (read only).

Function: This bit is read directly from the bus and generates the ATN interrupt if its associated enabling bit has been set. A 1 indicates that the ATN line is asserted.

Bit 13: END OCC (read only).

Function: Essentially indicates the END of a device dependent message. Generates the END interrupt if its associated enabling bit has been set.

Set:

By an internal latch when a talker on the IEEE 488 bus asserts the DAV and EOI lines simultaneously with the last data byte (ATN unasserted).

Cleared: By a RESET instruction or by writing a 1 into the END INTR CLR bit (13) in the BSR.

Bit 12: REN FALSE OCC (read only).

Function: For interrupt driven program. Detects when the IEEE 488 bus leaves the remote control mode and generates the Remote Enable (REN) Cleared interrupt vector if its associated enabling bit has been set.

Set:

By an internal flip-flop when the REN bus line goes from its asserted to its unasserted state.

Cleared: By a RESET instruction or by writing a 1 into the REN INTR CLR bit (12) in the BSR.

### Bit 11: IFC OCC (read only).

Function: Detects when the IFC bus line becomes asserted and generates the IFC interrupt if its associated enabling bit has been set.

Set: By an internal flip-flop when the IFC bus line goes from its unasserted state to its asserted state.

Cleared: By a RESET instruction or by writing a 1 into the IFC INTR CLR bit (11) in the BSR.

### Bit 7: RDY (read only).

- Function: When set at the end of an acceptor handshake cycle, this bit indicates that a valid data byte is available in the LDB. Interface must be in a listen mode (LIST W ATN or LIST W/O ATN). For a DMA listen mode, the DMA IN/OUT bit (2) in the ISR must be set. When this bit is set it generates the RDY interrupt if its enabling bit has been set. NOTE: Do not set the DONE or RDY interrupt enabling bits for a DMA transfer.

- Set: By an internal flip-flop when DAV assumes its asserted state at the beginning of a handshake cycle. Data is normally placed on the bus by a talker before DAV is asserted.

Cleared: When the LDB is read, by a RESET instruction, or when the IFC line is asserted.

Bits 6-0:

INTR ENBL (Interrupt Enable) bits; RDY, DONE, SRQ, ATN, END, REN, and IFC, respectively (write or read).

Function:

When written, these bits are stored in a common octal flip-flop circuit with a common clear input. Each bit can be set (interrupt unmasked) or cleared (interrupt masked) by writing a 1 or 0 into the desired bit (1 equals set, 0 equals clear). The SRQ interrupt vector is generated if bit 4 is set and the SRQ bus line is asserted. The RDY INTR ENBL and the DONE INTR ENBL bits must not be set for a DMA transfer. All of these bits are cleared by a RESET instruction. The assertion of the IFC bus line does not clear these bits.

#### **BUS STATUS REGISTER (BSR) 1AAA06** 15 14 13 12 11 10 9 8 7 6 2 0 5 3 1 END INTR CLR REN INTR CLR IFC INTR CLR NO EOI DMA DMA LOCAL NRFD DAV SRO FOI IFC NDAC ATN REN

**Bus Status Register (BSR).** The Bus Status Register essentially monitors the IEEE 488 bus management and handshake control lines. Bits included in this register are two DMA functions, three interrupt clearing bits, and a local reset function.

Bit 15: NO EOI DMA (write or read).

Function: This bit is provided for DMA transfers: 1) If bit 15 is set for a DMA transfer from the IEEE 488 bus to the controller memory or to another peripheral, the transfer is not terminated by the EOI message being received with a data byte. The DMA control logic continues to accept data until the Byte Counter Register (BCR) overflows or the DMA transfer is aborted. 2) If bit 15 is set for a DMA transfer from the controller memory or another peripheral to the IEEE 488 bus, the interface will not assert the EOI bus line at the same time as the last data byte. If this bit is clear, EOI will be asserted with the last data byte. 3) If the ATN OUT bit (3) in the BCR is set and a DMA transfer to the IEEE 488 bus is initialized, the assertion of the EOI bus line is automatically inhibited (bit 15 does not have to be set).

Set:

By writing a 1 to the bit location.

Cleared: By writing a 0 into this bit or by a RESET instruction.

# Bits 13 - 11: END INTR CLR, REN INTR CLR, and IFC INTR CLR, respectively (gated write pulse only).

Function: When written these bits are not stored or latched. When a 1 is written to the desired bit, it clears its corresponding interrupt condition bit (13, 12, or 11) in the ICR. Write pulse duration is about 50 nanoseconds.

### Bit 10: DMA INIT (gated write pulse only).

Function:

To be set before a DMA operation. This bit is not stored or latched. When a 1 is written to this bit it clears the ERR, TIME ERR, WRITE ERR, DMA ERR, DMA ABORT, DMA DONE, and GO bits (15, 14, 13, 12, 11, 7, and 0) in the ISR. Write pulse duration is about 50 nanoseconds.

### Bit 9: LOCAL RESET (gated write pulse only).

Function:

0

This bit is not stored or latched. When a 1 is written to this bit, it performs the same operation as occurs when a controller RESET instruction is executed. It is used to re-initialize this interface without affecting other interfaces (peripherals) within the system. Write pulse duration is about 50 nanoseconds. Asserting this bit affects the eight programmable (addressable) registers as follows (see Table 3-3):

- TDB: Resets (clears) the EOI function associated with bit 15 and removes output data from the IEEE 488 bus.

- LDB: Clears the REN FALSE OCC bit (12).

- ICR: Sets the DONE bit (15). Clears the following bits: END bit (13), REN FALSE OCC bit (12), IFC OCC bit (11), RDY bit (7), and the INTR ENBL (interrupt enabling) bits (6 through 0).

BSR: Clears the NO EOI DMA bit (15).

- BCR: Clears TCS (15), LIST W ATN (14), LIST W/O ATN (13), XBA17 (12), XBA16 (11), and resets the IEEE 488 control lines to their idle state.

- ISR: Resets (clears) all the bits in this register.

CLR: Does not affect this register.

BAR: Does not affect this register.

## Bits 7 - 0: NRFD, NDAC, DAV, SRQ, ATN, EOI, REN, and IFC, respectively (read only).

Function:

Not Ready for Data, Not Data Accepted, Data Valid, Service Request, Attention, End or Identify, Remote Enable, and Interface Clear, respectively. These bits monitor the IEEE 488 control lines and are read directly from the bus. They are not stored or latched. When read, a 1 indicates that a control signal is received and that the corresponding bus line is asserted.

| BUS CONTROL REGISTER (BCR) |                  |                    |           |           |    |     |   | 1AAA10      |             |            |            |            |            |            |            |

|----------------------------|------------------|--------------------|-----------|-----------|----|-----|---|-------------|-------------|------------|------------|------------|------------|------------|------------|

| 15                         | 14               | 13                 | 12        | 11        | 10 | 9   | 8 | 7           | 6           | 5          | 4          | 3          | 2          | 1          | 0          |

| TCS                        | LIST<br>W<br>ATN | LIST<br>W/O<br>ATN | XBA<br>17 | XBA<br>16 |    | 533 |   | NRFD<br>OUT | NDAC<br>OUT | DAV<br>OUT | SRQ<br>OUT | ATN<br>OUT | EOI<br>OUT | REN<br>OUT | IFC<br>OUT |

**Bus Control Register (BCR).** The Bus Control Register provides a way to set and monitor the IEEE 488 management and handshake control lines. This register also includes interface mode control bits.

## Bit 15: TCS (write or read).

Function:

Take control synchronously. This bit is used to take synchronous control of the bus in order to prevent the possible loss of data. Bit 15 sets up the interface hardware so that if a data transfer is taking place across the bus while ATN is unasserted, the NRFD line is asserted at the same time as DAV to inhibit the next handshake cycle; the ATN OUT bit (3) is then set automatically when DAV clears. As soon as the ATN OUT bit becomes set, it resets (clears) the TCS bit. It is possible for the ATN OUT bit to not be set within the expected time interval if the data transfer has slowed or stopped (talker has not yet received the DAC message).

Set:

6

By writing a 1 into two internal flip-flops, with the second flip-flop clocked by the DAV signal.

Cleared:

By writing a 0 into this bit, when the ATN OUT bit becomes set, by a RESET instruction, or when the IFC bus line is asserted.

## Bits 14 and 13: LIST W ATN and LIST W/O ATN, respectively (write or read).

Function:

Either, or both, of these bits enable the interface acceptor handshake logic for the non-DMA mode. See description of the LDB for information relative to enabling the acceptor handshake logic while this interface is outputting data (talking) on the bus during a DMA transfer. For the non-DMA mode, the logic is enabled under the following conditions:

When LIST W ATN is set and another controller on the bus asserts the ATN line.

If LIST W/O ATN is set and the ATN line is

released (unasserted) by another controller on the bus.

The LIST W ATN bit (14) should be set to a 1 whenever another device on the bus is acting as controller-in-charge. The LIST W/O ATN bit (13) is automatically set if the LIST W ATN bit is set and another controller asserts the ATN line. This immediately sets the acceptor handshake function as soon as the ATN line is unasserted. If the program does not require the interface to accept data (it is not a listener) when ATN becomes unasserted, bit 13 should be cleared.

Set:

Each, or both, of these bits are set by writing a 1 to internal flip-flops. LIST W/O ATN is automatically set by this interface if LIST W ATN is set and another controller asserts the ATN line.

Cleared:

By writing a 0 into the desired bit. Bit 14 is cleared by a RESET instruction. Bit 13 is cleared either by a RESET instruction or the assertion of the IFC line.

Bits 12 and 11: XBA17 and XBA16, respectively (write or read).

Function:

Extended address bits. Provided for DMA transfers in Memory Management systems. XBA17 and XBA16 assert the extended address lines on the controller bus. For Memory Management systems set XBA17 and XBA16 according to the following guide: 00 for transfers in the area of 00-32 K. 01 for transfers in the area of 32-64 K. 10 for transfers in the area of 64-96 K. 11 for transfers in the area of 96-128 K.

Set:

Either, or both, bits are set by writing a 1 to internal flip-flops.

Cleared:

By writing a 0 to the desired bit. Both bits are cleared by a RESET instruction.

Bits 7 - 0:

NRFD OUT, NDAC OUT, DAV OUT, SRQ OUT, ATN OUT, EOI OUT, REN OUT, IFC OUT, respectively (write or read).

Function:

0

The following bits are latched by writing a 1 into the desired bit: bits 7, 6, 5, 4, 2, and 1. Bit 3 is set by writing a 1 to a flip-flop. Bit 0 (IFC OUT) is a triggered "one-shot" multivibrator; the IFC bus line is asserted for approximately 150 microseconds when this bit is loaded and then clears itself. The output of the latches drive the IEEE 488 bus in a corresponding manner; if the output of a latch is a 1, the corresponding bus line is asserted. Note that the ATN OUT bit (3) is also set automatically as described for the TCS bit (15). All of these bits, except REN OUT and IFC OUT, are cleared by either a RESET instruction or when IFC is asserted on the bus. REN OUT and IFC OUT can be cleared by RESET instruction. The status of the IEEE 488 bus lines associated with

## CP1100/IEEE 488 INTERFACE

these bits can also be read from the Bus Status Register (BSR). When the IFC bus line is asserted by this interface or another controller, the eight programmable registers are affected in the following manner (see Table 3-3):

TDB: Clears the EOI function associated with bit 15 and removes output data to the IEEE 488 bus.

LDB: Configured to receive new data.

- ICR: Sets the DONE bit. Sets IFC OCC and generates an interrupt if IFC INTR ENBL is set. Clears the RDY bit.

- BSR: A positive transition occurs at bit 0.

- BCR: Clears TCS, LIST W/O ATN, NRFD OUT, NDAC OUT, DAV OUT, SRQ OUT, ATN OUT, and EOI OUT.

ISR: Sets DMA ABORT and clears the GO bit.

CTR: Does not affect this register.

BAR: Does not affect this register.

Note that the ATN OUT and SRQ OUT bits, when set, will generate interrupts through the ICR if their enabling bits have been set. The REN OUT bit generates a REN FALSE interrupt if it is cleared after being set and the enabling bit has been set. The status of the ATN, REN, and EOI bus lines can also be read from the LDB. In most cases, the LDB should not be read during a DMA transfer since it could cycle the acceptor handshake logic.

| INTERFACE STATUS REGISTER (ISR) |             |              |            |              |    |   | 1AAA12 |             |                     |                       |             |              |                   |                     |    |

|---------------------------------|-------------|--------------|------------|--------------|----|---|--------|-------------|---------------------|-----------------------|-------------|--------------|-------------------|---------------------|----|

| 15 _                            | 14          | 13           | 12 _       | - 11         | 10 | 9 | 8      | 7           | 6                   | 5                     | 4           | 3 _          | 2                 | 1                   | 0  |

| ERR                             | TIME<br>ERR | WRITE<br>ERR | DMA<br>ERR | DMA<br>ABORT |    |   |        | DMA<br>DONE | DMA<br>INTR<br>ENBL | SWAP<br>BYTE<br>ORDER | HOG<br>MODE | PACK<br>MODE | DMA<br>IN/<br>OUT | NO<br>INCR/<br>DECR | GO |

Interface Status Register (ISR). The primary function of the Interface Status Register allows the user to control and monitor the operation of this interface in the DMA modes. Other DMA primary control bits are found in the Bus Status Register. The Byte Counter Register and the Bus Address Register are also used for DMA operations.

Bit 15: ERR (read only).

Function:

For DMA or non DMA modes. This bit is the inclusive-OR of the following four errors: 1) TIME ERR, 2) WRITE ERR, 3) DMA ERR, and 4) DMA ABORT. If any of the four error flags or the DMA DONE bit (7) becomes set, the GO bit is automatically cleared. If the DMA INTR ENBL bit is set and an error occurs during a DMA transfer, or the transfer is completed (DMA DONE set), the interface generates the highest priority interrupt and returns a vector address determined by the vector address straps. Bits 15 through 7 of this register are read by the program to determine the type of error or if the DMA transfer is complete.

Set:

0

Automatically by this interface if bit 14, bit 13, bit 12, or bit 11 of this register become set.

Cleared:

By writing a 1 into the DMA INIT bit (10) of the BSR, or by a RESET instruction.

## Bit 14: TIME ERR (read only).

Function: For DMA or non DMA modes. When set, indicates that one of two possible timing errors has occurred:

1) Another controller asserting ATN while this interface is handshaking data.

2) An attempt to load the TDB before a previous byte was accepted by all listeners.

Set: By this interface if another controller asserts ATN during the time that DAV is asserted by this interface or, if the program tries to load the TDB before DAV assumes its unasserted state.

Cleared: By writing a 1 to the DMA INIT bit (10) in the BSR, or by a RESET instruction.

## Bit 13: WRITE ERR (read only).

- Function: For DMA or non DMA modes. When set, indicates that an attempt was made to load the TDB when no device on the IEEE 488 bus was listening.

- Set: By this interface if an attempt is made to load the TDB while the NRFD and NDAC bus lines are in their unasserted states.

Cleared: By writing a 1 into the DMA INIT bit (10) of the BSR, or by a RESET instruction.

Bit 12: DMA ERR (read only).

Function: When set, indicates one of two possible error conditions occurred during a DMA transfer: 1) the Bus Address overflowed, or 2) no response from a designated slave device; for example, a non-existent memory location.

Set: By this interface if the BAR overflows or if the slave device does not reply when addressed.

Cleared:

By writing a 1 into the DMA INIT bit (10) in the BSR or by a RESET instruction.

## Bit 11: DMA ABORT (read only).

Function: When set, indicates one of four possible reasons for the DMA transfer to halt before completion: 1) IFC asserted, 2) ATN asserted by another controller,

3) A TIME ERR, WRITE ERR, or DMA ERR occurred,

4) The REN FALSE condition occurred with its enabling bit set. An error interrupt vector is generated if the DMA INTR ENBL bit (7) has been set and the DMA aborts; see ERR bit (15).

Set:

By this interface during a DMA transfer under any of the following conditions; IFC asserted, ATN asserted by another controller, the ERR bit becomes set, or if REN goes from its asserted to unasserted state with the REN INTR ENBL bit (10) in the ICR set. The DMA DONE bit (7), if set, inhibits the setting of DMA ABORT.

Cleared:

By writing a 1 into the DMA INIT bit (10) in the BSR, or by a RESET instruction.

## Bit 7: DMA DONE (read only).

Function: When set, indicates the normal end of a DMA transfer when transmitting data in either direction across this interface.

Set:

Automatically by this interface when the END bit (13) in the ICR becomes set and the NO EOI DMA bit has been cleared; if the NO EOI DMA bit has been set, the DMA DONE bit is set by Byte Counter Register overflow (all 1's to all 0's).

Cleared:

0

By writing a 1 into the DMA INIT bit (10) in the BSR, or by a RESET instruction.

| Bit | 6: | DMA | INTR | ENBL | (write | or | read) | ). |

|-----|----|-----|------|------|--------|----|-------|----|

|     |    |     |      |      |        |    |       |    |

Function: When set, enables the interrupt condition for DMA DONE or for one of the error flags associated with bits 15 through 11 of this register.

Set: By writing a 1 to an internal flip-flop.

Cleared: By writing a 0 into this bit, or by a RESET instruction.

Bit 5: SWAP BYTE ORDER (write or read).

Function: This bit is used to control the manner in which memory is addressed when operating in the DMA "packed" mode (bit 3 of this register set). If this bit (5) is clear, memory is addressed in the standard fashion (16-bit memory word assumed): 1) Low order bytes first when incrementing the Bus Address Register. 2) High order bytes first when decrementing the Bus Address Register.

> If the SWAP BYTE ORDER bit is set, memory is addressed in the following manner (16-bit memory word assumed): 1) High order bytes first when incrementing the Bus Address Register. 2) Low order bytes first when decrementing the Bus Address Register.

Refer to the Servicing Section of this manual for information on how to increment or decrement the BAR.

0

Set:

By writing a 1 to an internal flip-flop.

Cleared:

By writing a 0 into this bit, or by a RESET instruction.

## Bit 4: HOG MODE (write or read).

Function:

This bit defines how the controller bus is used during a DMA transfer; it can be set or cleared while the DMA is running. If this bit is clear, the interface gets control of the bus, transfers one byte, and then releases the bus before the next byte transfer. If this bit is set, the interface gets control of the bus and does not release it until the DMA transfer is completed. This interface will release the controller bus if a device on the IEEE 488 bus does not respond within 20 microseconds; this is not an "error" (an error flag is not set). The device was slow to respond and as soon as it does respond, the interface will proceed with the remainder of the DMA transfer.

Set: E

By writing a 1 to an internal flip-flop.

Cleared: By writing a 0 into this bit, or by a RESET instruction.

## Bit 3: PACK MODE (write or read).

Function:

0

This bit specifies how the data is stored in (or retrieved from) memory. If set, the 16-bit memory word is byte addressed. The order of byte transfer is dependent on the setting of the SWAP BYTE ORDER bit and whether the BAR is incremented or decremented. See discussion under SWAP BYTE ORDER bit and the BAR. In the PACK MODE, the BAR is incremented or decremented by one (1) after each byte transfer. The transfer may start at an even or odd address. When this bit is clear, the interface is operating in an "unpacked" mode and the data is assumed to appear in the low order byte defined by the current value in the BAR. When transferring data from the IEEE 488 bus to memory in the "unpacked" mode, the high byte of a word will be ignored during the time that the low byte is written; the BAR is incremented or

## CP1100/IEEE 488 INTERFACE

decremented by two (2) after each byte transfer if the NO INCR/DECR bit is cleared.

Set: By writing a 1 to an internal flip-flop.

Cleared: By writing a 0 into this bit, or by a RESET instruction.

Bit 2: DMA IN/OUT (write or read).

Function: Specifies the direction of the DMA transfer. When set, the data is transferred from the IEEE 488 bus to the controller bus (DMA IN). When clear, the data is transferred from the controller bus to the IEEE 488 bus (DMA OUT).

Set: By writing a 1 to an internal flip-flop.

Cleared: By writing a 0 into this bit, or by a RESET instruction.

Bit 1: NO INCR/DECR (write or read).

Function: When set, indicates that the same address should be used for the entire DMA transfer; the BAR will not be incremented or decremented during the transfer.

Set: By writing a 1 to an internal flip-flop.

Cleared: By writing a 0 into this bit, or by a RESET instruction.

Bit 0: GO (write or read).

Function: When set, initiates a DMA controlled data transfer. This bit can be set simultaneously with bits 1 through 6 of this register, or set last in a sequence. Before setting the GO bit, the Bus Status Register (BSR)

should be programmed properly for a DMA transfer.

Set:

By writing a 1 to an internal flip-flop.

Cleared:

By writing a 0 into this bit, or by a RESET instruction. This bit is automatically cleared by this interface if ATN is asserted by another controller, IFC is asserted, REN FALSE condition occurs with its enabling bit set, or if any of bits 15 through 7 of this register becomes set.

## CP1100/IEEE 488 INTERFACE

Byte Counter Register (CTR). The Byte Counter Register is a write or read register and used by the programmer for DMA operations. Initially, the CTR is loaded with the 2's complement of the number of bytes to be transferred. For each byte transferred, this register increments toward zero. When the Byte Counter Register overflows (all 1's to all 0's), the DMA DONE bit in the Interface Status Register is set and the DMA transfer is complete. If an EOI message is received and the NO EOI DMA bit is set, the transfer halts with the DMA DONE bit set. The Byte Counter Register contains the 2's complement of the initial byte count minus the number of bytes transferred. Each bit is set/cleared by writing a 1/0 into the desired bit. See NOTE under the description for the Bus Address Register.

3-28

**Bus Address Register (BAR).** The Bus Address Register is a write or read register and is used for DMA operations. This register (along with the extended address bits, XBA17 and XBA16 in the Bus Control Register) is used to specify the controller bus address of the location to (or from) which data is to be transfer during DMA cycles. The BAR is incremented or decremented according to how a strap (jumper) on this interface is set by the user. If the NO INCR/DECR bit in the Interface Status Register is set after the BAR is loaded, the same address can be used for the entire DMA transfer. If the PACK MODE bit in the ISR is set, the BAR is incremented (decremented) once for each byte transfer; if it is cleared, the BAR is incremented (decremented) twice for each byte transferred. If the BAR overflows during a DMA transfer, the DMA ERR bit in the ISR is automatically set. Since BAR overflow does not increment (decrement) the extended address bits, the maximum block of data that can be transferred in one operation is 64 K bytes.

The SWAP BYTE ORDER bit in the ISR does not affect the actual contents of the BAR; if the SWAP BYTE ORDER bit is set, the least significant bit in the BAR will appear complemented when read or when it is used as an address on the controller bus. Each bit of the BAR is set or cleared by writing a 1 (set) or 0 (clear) into the desired bit.

#### NOTE

If this interface is performing a DMA transfer from the controller bus to the IEEE 488 bus (a talk mode) and another controller performs a "take control synchronously" operation (TCS), the CTR and the BAR should be backed up one cycle before continuing.

If an EOI message is received during a DMA transfer with the NO EOI DMA bit cleared, the transfer halts and the BAR returns the address into (from) which the next data byte would have been moved. When sending data to the IEEE 488 bus under DMA control, the BAR contains a value that points to the actual position for the next data byte.

## Local Reset and Interface Clear

Table 3-3 illustrates the bits in each register that is cleared (or set) by issuing a LOCAL RESET instruction or when IFC is asserted on the IEEE 488 bus.

### TABLE 3-3

## Local Reset/Interface Clear Functions. Bits cleared by R (LOCAL RESET) and I (Interface Clear)

| Bit ( | 15<br>EOI) | 14                     | 13 | 12 | 11 | 10  | 09 | 08   | 07           | 06   | 05 | 04  | 03            | 02 | 01 | 00 |

|-------|------------|------------------------|----|----|----|-----|----|------|--------------|------|----|-----|---------------|----|----|----|

| TDB   | IR         | - 1                    | -  | -  | -  | -   | -  |      | IR           | IR   | IR | IR  | IR            | IR | IR | IR |

| LDB   | -          | ( <b>-</b> 3)<br>80181 | -  | R  | -  | -   | -  | -    | -            | -100 | -  | -   | -             | -  | -  | -  |

| ICR ( | SET)       | -                      | R  | R  | R  | -   | -  | -    | IR           | R    | R  | R   | R             | R  | R  | R  |

| BSR   | R          |                        | -  | -  | -  | -00 | -  | - 22 | -911<br>1791 | - 11 | -  | -30 | - 33<br>59.42 | -  | -  | -  |

| BCR   | IR         | R                      | IR | R  | R  | -   | -  | -    | IR           | IR   | IR | IR  | IR            | IR | R  | IR |

| ISR   | R          | R                      | R  | R  | R  | -   | -  | -    | R            | R    | R  | R   | R             | R  | R  | IR |

NOTE: The DONE bit (15) in the Interrupt Control Register (ICR) is set by either LOCAL RESET (R) or Interface Clear (I). The DMA ABORT bit (11) in the Interface Status Register (ISR) will be set by Interface Clear if a DMA transfer has not been completed.

3-30

## SECTION 4

## SOFTWARE PROTOCOLS

## Introduction

Programming protocol for the IEEE 488 interface is discussed in this section of the manual. The program may act as a system controller or control may be passed back and forth between this interface and another controller on the IEEE 488 bus.

The basic concept of the IEEE 488 system is described in Section 2 of this manual. For more specific details and state diagrams relative to the IEEE 488 interface functions, refer to IEEE Standard 488-1975.

This interface has eight addressable registers and eight interrupt vectors. The registers and interrupts are specifically discussed in Section 3 of this manual.

The IEEE 488 system usually requires that one device be designated as the system controller. It is possible, however, to have a system configured where more than one device has the controller function; when that is the case, only one device may be the controller-in-charge at any given time. To get control of the bus, any controller may request transfer of control from the current controller-in-charge. A system controller can take control from the current controller-in-charge by requesting that control be returned or by simply asserting the Interface Clear (IFC) message. Interface Clear can only be performed by a system controller and it causes the Talker and Listener functions, as well as the Controller functions in other devices, to go to their power on state. The other interface (IEEE 488) functions are not directly affected by the IFC message.

## Programming Considerations

Addressing. This interface can be strapped to respond to addresses within the range of  $160000_8$  through  $177776_8$ .

The extended address bits (XBA16 and XBA17) in the Bus Control Register are used when the controller has provision for Memory Management. In order to perform a DMA operation with this interface to, or from, another device in the peripheral space, the user must set XBA16 and XBA17 for data transfers to the desired memory area (see Section 3 -Bus Control Register).

The addressable registers on this interface do not support write byte operations. If the user performs a write byte operation on one of the interface registers, the byte will be loaded into both the high and low order bits of the register. Read byte operations are handled in the standard fashion.

The Talker Data Buffer is typically thought of as a write only register. However, register address 1AAA00 can be read and has the added feature that it returns the vector address for the last interrupt granted. This feature can be used by system software to determine how the interface interrupt vectors have been set (strapped).

Local Reset. The LOCAL RESET bit in the Bus Status Register provides a means of initializing the controller side of this interface. Writing a 1 into this bit performs the same function on this interface as occurs when a controller RESET (INIT) instruction is executed. The LOCAL RESET bit can be used to reinitialize this interface without affecting the other interfaces (peripherals) in the system. Refer to Table 3-3 (Section 3) for information concerning the bits in each register that are cleared by the LOCAL RESET and Interface Clear (IFC) functions.

The EOI function. The EOI line of the IEEE 488 bus is used to indicate the end of data transmission (or Identify for a Parallel Poll, covered later). The EOI line can be asserted by setting the EOI bit in the Bus Control Register; however, since it is normally sent only with the last data byte in a message, the EOI message may be sent by setting

4-2

CP1100/IEEE 488 INTERFACE

bit 15 in the Talker Data Buffer when sending data in a non DMA mode. The programmer must take care when using the internal registers of the controller (RO-R5) that an automatic sign extension does not inadvertently set bit 15 and assert the EOI line. For DMA transfers, the EOI message is automatically sent along with the last byte of data unless the programmer sets the NO EOI DMA bit in the Bus Status Register before the DMA transfer is initiated. The EOI bus line can be monitored directly by reading the Bus Status Register; it is also available as the most significant bit (15) in the Listener Data Buffer.

The END condition (EOI and DAV asserted, ATN unasserted) is detected by this interface and indicated in the Interrupt Control Register as the END OCC bit. The END condition can also be monitored by enabling its interrupt. Once the interrupt is detected, either the END OCC bit or its interrupt enabling bit (2) must be reset and set again for another interrupt to occur. The END OCC bit is cleared by writing a 1 to the END INTR CLR bit in the Bus Status Register.

The Listen Enable Functions. The source and acceptor handshake functions for this interface are totally independent. If the LIST W/O ATN bit in the Bus Control Register is set and the user writes data to the Talker Data Buffer, the interface will listen to itself because the acceptor handshake logic has been enabled. This feature can be used by the programmer for system checkout, but the programer must take care not to inadvertently "hang" the IEEE 488 bus with the interface listening to itself.

The LIST W ATN bit in the Bus Control Register is implemented such that if it is set, the interface will automatically start listening when ATN is asserted by another controller, yet will not handshake data sent if the ATN OUT bit in the Bus Control Register is set. This feature allows this interface to respond properly to the system controller asserting the IFC and ATN lines, and allows this interface to send data as a controller-in-charge (ATN asserted) without listening to itself.

**Errors Detected and Reported.** This interface detects and reports four errors to the program, they are:

- 1. TIMING ERROR caused by:

- a) Writing to the Talker Data Buffer before the previous byte was accepted by all assigned listeners.

4-3

#### CP1100/IEEE 488 INTERFACE

- b) Another controller asserting ATN while this interface is sending data.

- 2. WRITE ERROR caused by:

- a) Writing to the Talker Data Buffer when no device on the IEEE 488 bus is listening.

- 3. DMA ERROR caused by:

- a) Overflow of the Bus Address Register.

- b) No response from an addressed "slave" device in a DMA transfer.

- 4. DMA ABORT caused by:

- a) Interface Clear (IFC) being issued during a DMA transfer.

- b) ATN being asserted by another controller during a DMA transfer.

- c) Remote Enable (REN) going from the asserted state to the unasserted state with the REN INTR ENBL bit set during a DMA transfer (a REN FALSE condition).

- d) A TIMING ERROR, WRITE ERROR, or DMA ERROR occurrence during a DMA transfer.

## Implementation of the IEEE 488 Interface Functions

The IEEE 488 interface functions provide a wide variety of capabilities and options, making the implementation of all of them in hardware unrealistic. For this reason only the most generally used functions (Source and Acceptor Handshake functions) are implemented completely in hardware. The other functions must be implemented in software, though in most cases the interface has features which make the task easier.

Program examples are provided, in some cases, to illustrate and guide the user in implementing the interface functions. However, they may not be complete and are not guaranteed to execute correctly as written.

## **Controller Function**

If this interface is to act as controller of the IEEE 488 bus, the programmer must implement the Controller Functions in software. The Controller Function provides a device with the capability to send device addresses, universal commands, addressed commands, secondary addresses, and secondary commands to other devices in the system. A controller function also provides the capability to conduct serial and parallel polls to determine which device requires service.

A controller function can exercise its capabilities, except for IFC and REN, only when it is asserting ATN on the bus. If more than one device on the bus has a Controller Function, then all but one of them must be in the Controller Idle State (CIDS) at any given time. The device containing the Controller Function which is not in CIDS is called the controller-in-charge.