**H 52380 - 900E** Vol. 2

# Spectrum Analyzer Display Unit

2380

Code No. 52380-900E

#### AMENDMENT RECORD

The following amendments are incorporated in this manual.

| Amendment<br>No. | Date    | Issued at Serial number prefix |

|------------------|---------|--------------------------------|

|                  | June 86 | 152027                         |

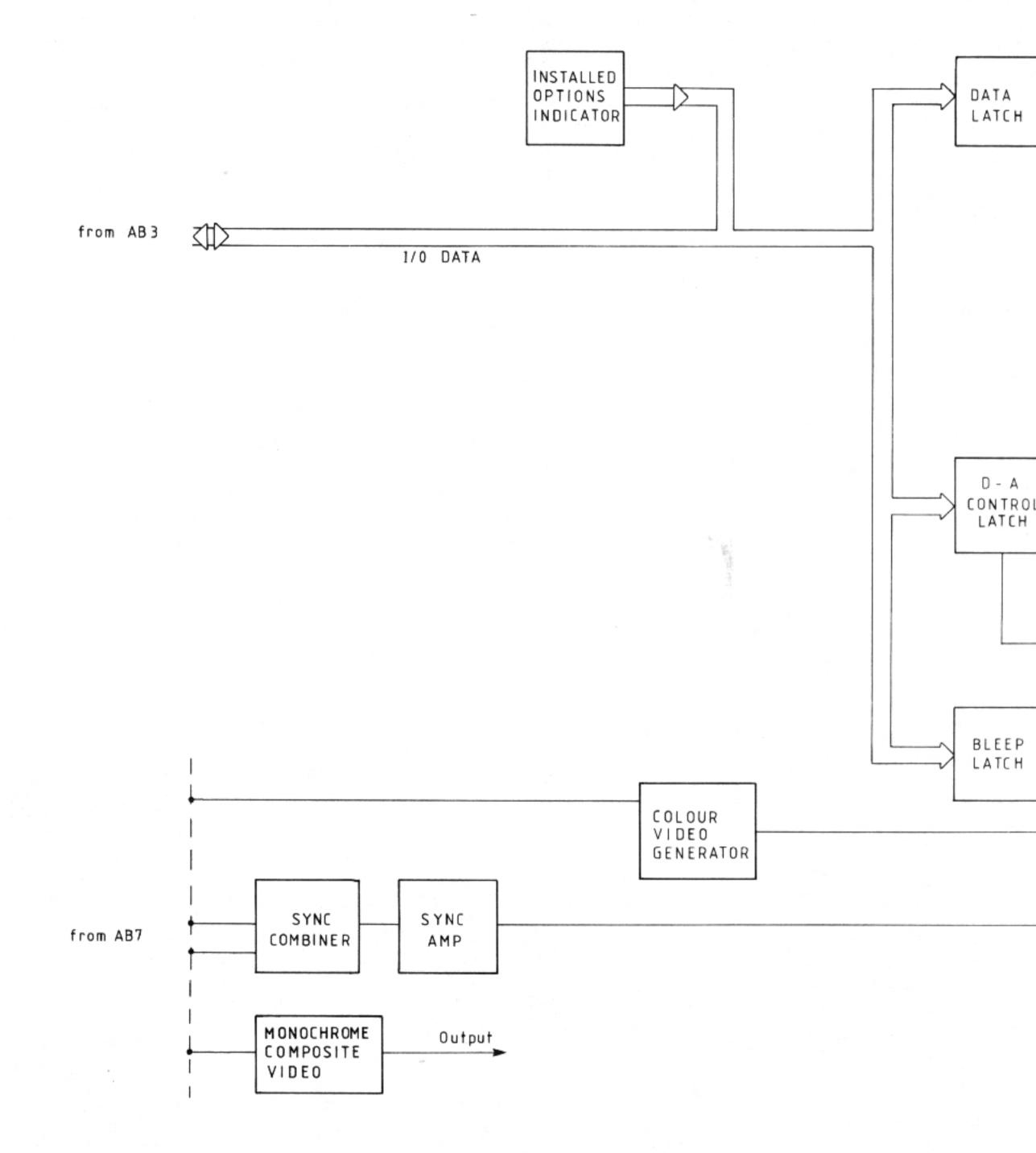

|                  |         |                                |

|                  |         |                                |

|                  |         |                                |

|                  |         |                                |

|                  |         |                                |

|                  |         |                                |

|                  |         |                                |

© Marconi Instruments Ltd. 1985 Printed in the UK

> Part No. 46881-488S Print code: A - 6/86, 2c

#### CONTENTS

#### **PRELIMINA**RIES

Title page Contents Notes and Cautions Logic mnemonics

#### **CHAPTERS**

General information Installation These chapters are contained Operation in Vol. 1: Operating Manual. Brief technical description 4-2 Technical description Maintenance 5-0 Not assigned 5-2 Adjustment and cal 5-3 Fault diagnosis 6 Replaceable parts Servicing diagrams 8 Modifications and supplements

#### HAZARD WARNING SYMBOLS

The following symbols appear on the equipment:

| Symbo1   | Type of hazard                               | Reference               |

|----------|----------------------------------------------|-------------------------|

| <b>⚠</b> | Static sensitive device                      | Page (iv)<br>Page (iii) |

| <u>A</u> | Dangerous voltages present<br>Supply voltage | Page (iii)              |

#### Note ...

Each page bears the date of the original issue or the code number and date of the latest amendment (Am. 1, Am. 2 etc.). New or amended material of technical importance introduced by the latest amendment is indicated by triangles positioned thus  $\triangleright$  ....  $\triangleleft$  to show the extent of the change. When a chapter is reissued the triangles do not appear.

Any changes subsequent to the latest amendment state of the manual are included on inserted sheets coded Cl, C2 etc.

#### NOTES AND CAUTIONS

#### ELECTRICAL SAFETY PRECAUTIONS

This equipment is protected in accordance with IEC Safety Class 1. It has been designed and tested according to IEC Publication 348, 'Safety Requirements for Electronic Measuring Apparatus', and has been supplied in a safe condition. The following precautions must be observed by the user to ensure safe operation and to retain the equipment in a safe condition.

#### Defects and abnormal stresses

Whenever it is likely that protection has been impaired, for example as a result of damage caused by severe conditions of transport or storage, the equipment shall be made inoperative and be secured against any unintended operation.

#### Removal of covers A

Removal of the covers is likely to expose live parts although reasonable precautions have been taken in the design of the equipment to shield such parts. The equipment shall be disconnected from the supply before carrying out any adjustment, replacement or maintenance and repair during which the equipment shall be opened. If any adjustment, maintenance or repair under voltage is inevitable it shall only be carried out by a skilled person who is aware of the hazard involved.

Note that capacitors inside the equipment may still be charged when the equipment has been disconnected from the supply. Before carrying out any work inside the equipment, capacitors connected to high voltage points should be allowed to discharge through the bleed resistors fitted for the purpose; do not attempt to remove the safety covers from the power supply until the lamp under the top cover stops blinking. Should the unit be reconnected to the supply with the safety covers removed then disconnected, do not attempt to discharge the power supply unit's main reservoir capacitors using a shorting link as the equipment may be damaged. Discharge should always be allowed to occur gradually.

Note also that the 12 kV e.h.t. circuit for the cathode ray tube retains its charge for a considerable time after switch off. Therefore before any handling is carried out in the vicinity of the cathode ray tube or e.h.t. unit it is essential that the supply is disconnected from the instrument and the final anode lead is shorted to the chassis several times immediately after unplugging. The residual charge on the c.r.t. itself must also be removed by shorting the anode connection to ground.

# AC supply plug A

The supply plug shall only be inserted in a socket outlet provided with a protective ground contact. The protective action shall not be negated by the use of an extension lead without protective conductor. Any interruption of the protective conductor inside or outside the equipment is likely to make the equipment dangerous.

#### Fuses - primary and secondary

Note that there is a supply fuse in both the live and neutral wires of the supply lead. If only one of these fuses should rupture, certain parts of the equipment could remain at supply potential.

To provide protection against breakdown of the supply lead, its connectors, and filter where fitted, an external supply fuse (e.g. fitted in the connecting plug) should be used in the live lead. The fuse should have a continuous rating not exceeding 6 A.

Make sure that only fuses with the required rated current and of the specified type are used for replacement. The use of mended fuses and the short-circuiting of fuse holders shall be avoided. A number of secondary fuses are fitted to boards in the upper and lower units. For details of both primary and secondary fuses, refer to Performance data in the Operating Manual.

#### CAUTION: STATIC SENSITIVE COMPONENTS

Components identified with the symbol  $\Delta$  on the circuit diagrams and/or parts lists are static sensitive devices. The presence of such devices is also indicated in the equipment by orange disks, flags or labels bearing the same symbol. Certain handling precautions must be observed to prevent these components being permanently damaged by static charges or fast surges.

- (1) If a printed board containing static sensitive components (as indicated by a warning disk or flag) is removed, it must be temporarily stored in a conductive plastic bag.

- (2) If a static sensitive component is to be removed or replaced the following anti-static equipment must be used.

A work bench with a grounded conductive surface.

Metallic tools grounded either permanently or by repeated discharges.

A low-voltage grounded soldering iron.

A grounded wrist strap and a conductive grounded seat cover for the operator, whose outer clothing must not be of man-made fibre.

- (3) As a general precaution, avoid touching the leads of a static sensitive component. When handling a new one, leave it in its conducting mount until it is required for use.

- (4) If using a freezer aerosol in fault finding, take care not to spray programmable ICs as this may affect their contents.

#### WARNING: HANDLING HAZARDS

This equipment is formed from metal pressings and although every endeavour has been made to remove sharp points and edges care should be taken, particularly when servicing the equipment, to avoid minor cuts.

Page iv May 86

Cathode ray tube. When exposing or handling the tube take care to prevent implosion and possible scattering of glass fragments. Handling should only be carried out by experienced personnel and the use of a safety mask and gloves is recommended. A defective tube should be disposed of in a safe manner by an authorized waste contractor.

#### WARNING: TOXIC HAZARD

Many of the electronic components used in this instrument employ resins and other chemicals which give off toxic fumes on incineration. Appropriate precautions should therefore be taken in the disposal of these items.

#### RADIO FREQUENCY INTERFERENCE

This equipment conforms with the requirements of IEC Directive 76/889 as to limits of r.f. interference.

May 86

#### LOGIC MNEMONICS USED IN THE LOGIC SECTION

A OR A-B SEL A OR A-B trace SEL

ADSR A channel Display Shift Register

AVG A Video Generator

B SEL

BDC

B Data Comparator

BDML

B DeMultiplex Latch

BDSR B channel Display Shift Register

BVG B Video Generator

COL Current Ordinate Latch

DACK1 Direct memory access ACKnowledge 1

DDM Data Display Mask

DIV H DIVIDE Higher bit

DIV L DIVide Lower bit

DMA Direct Memory Access

DMARL

DREQ 1

Direct Memory Access Request Latch

DREQ 1

Direct memory access ReQuest 1

DRQ Direct memory access ReQuest

DRQ 1

Direct memory access ReQuest 1

DSR Display Shift Registers

EOC End Of Conversation ERSD Even Row Start Detector

ESPG Extra line Sync Pulse Generator

ESTB Extra Sync Trigger Bistable

GCHM Gated Clock & Horizontal Mask generator

GDSR Graticule Display Shift Register

HRTC Horizontal ReTraCe

HRTCS Horizontal RetraCe Sync

HSTB Horizontal Sync Trigger Bistable

HSYNC Horizontal SYNC

IOW Input/Output Write

LCVM Line Count & Vertical Mask generator

MPY Multiply

SDA Spectrum Display Area

VML Vertical Mask Latch

VRTC Vertical ReTraCe

VRTCS Vertical ReTraCe Sync

VSYNC Vertical SYNC

WD Write Display

WE Write Even

WO Write Odd

WPG Write Pulse Generator

XV1DEN Y VIDeo ENable

YVIDEN Y VIDeo ENable

# Chapter 4-2

## TECHNICAL DESCRIPTION

### CONTENTS

| Para  | •                                                      |         |         |       |

|-------|--------------------------------------------------------|---------|---------|-------|

| 1     | Introduction                                           |         |         |       |

| 3     | Circuit summary                                        |         |         |       |

| 3     | Signal path, display, pen plot & RGB video             |         |         |       |

| 10    | Processor and control                                  |         |         |       |

| 11    | Power supply                                           |         |         |       |

| 12    | Signal path                                            |         |         |       |

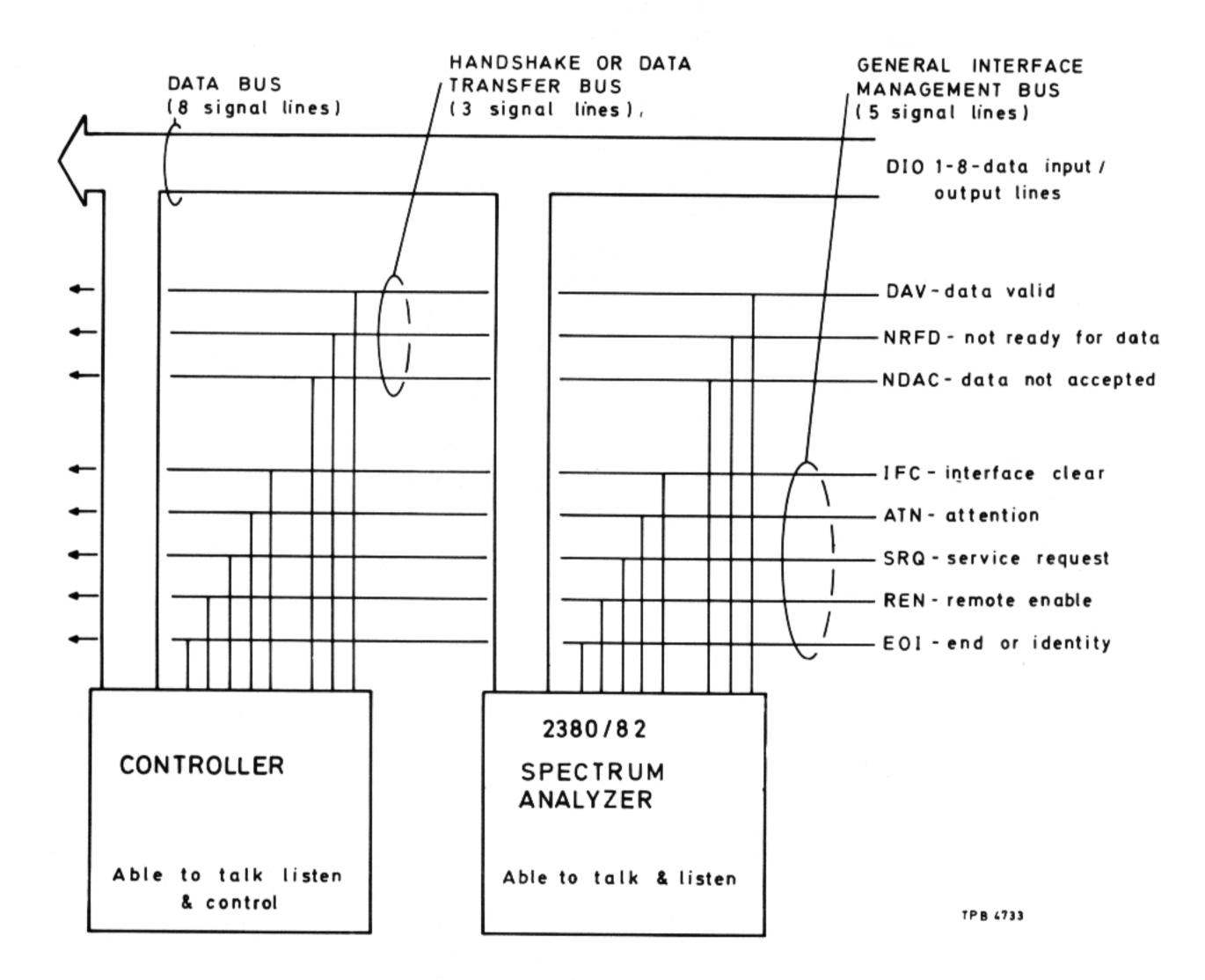

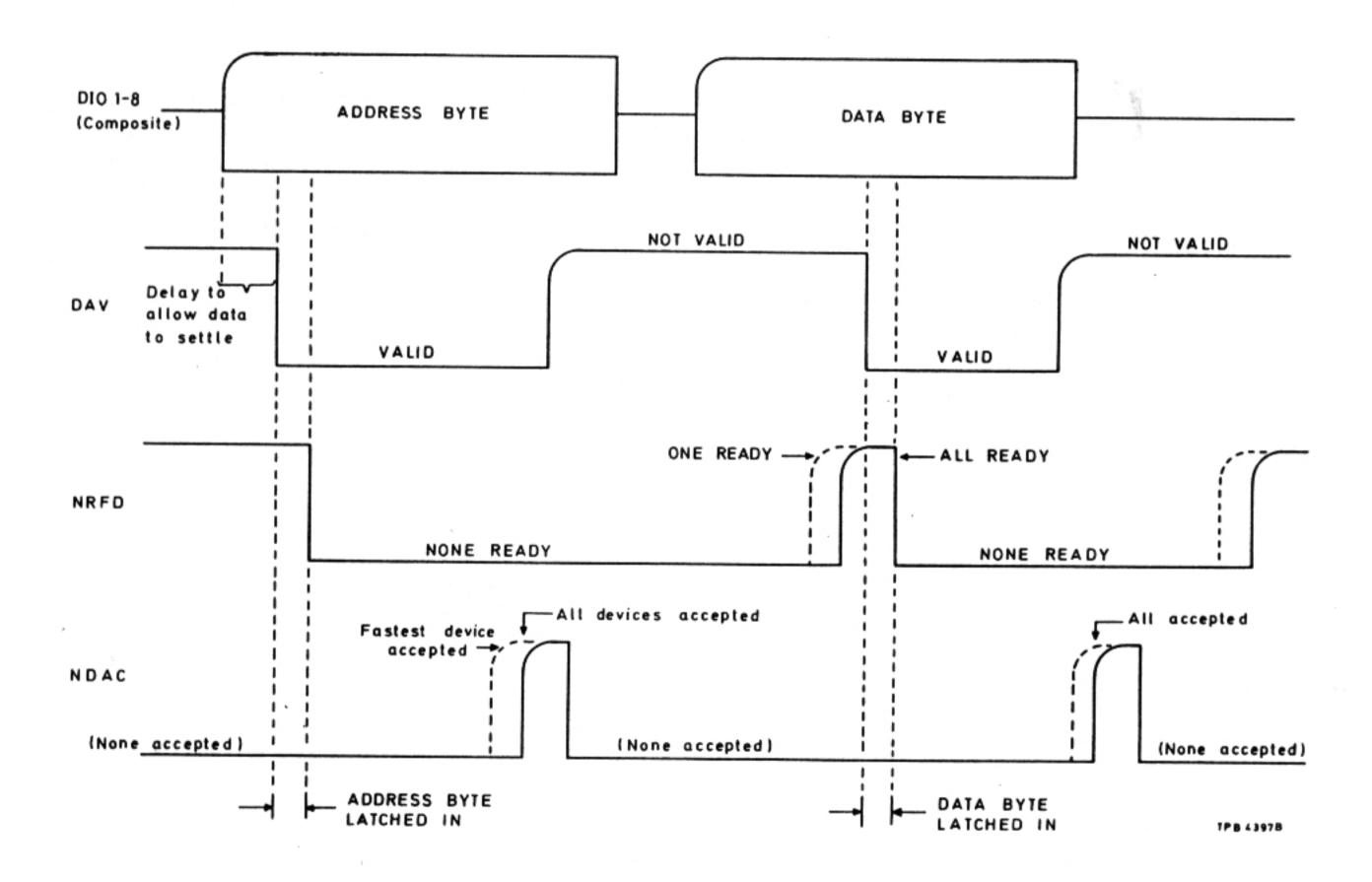

| 16    | Board AAl - Mother board &                             |         |         |       |

|       | Board AA2 - Auxiliary connector                        |         |         |       |

| 19    | Board AB2 - Input signal data processing               |         |         |       |

| 50    | Board AB4 - Mathematics operations                     |         |         |       |

| 64    | Board AB5 - Timing & B display dynamic store           |         |         |       |

| 83    | Board AB6 - Graticule & A display dynamic store        |         |         |       |

| 88    | Display                                                |         |         |       |

| 92    | Board AB7 - CRT control, clock and video mixer         | *       |         |       |

| 115   | Board AD1/1 - Display drive &                          |         |         |       |

|       | Board AT2 - CRT base                                   |         |         |       |

|       | Assembly ADO - CRT                                     |         |         |       |

| 123   | Processor and control                                  |         |         |       |

| 126   | Board AB1 - I/O and keyboard communication &           |         |         |       |

|       | Board AR1 - GPIB connector                             |         |         |       |

| 148   | Board AB3/1 - Processor, memory and chip select        |         |         |       |

| 163   | Board AF1 - Keyboard matrix and encoding               |         |         |       |

| 165   | Board AZ1 - Shaft encoder                              |         |         |       |

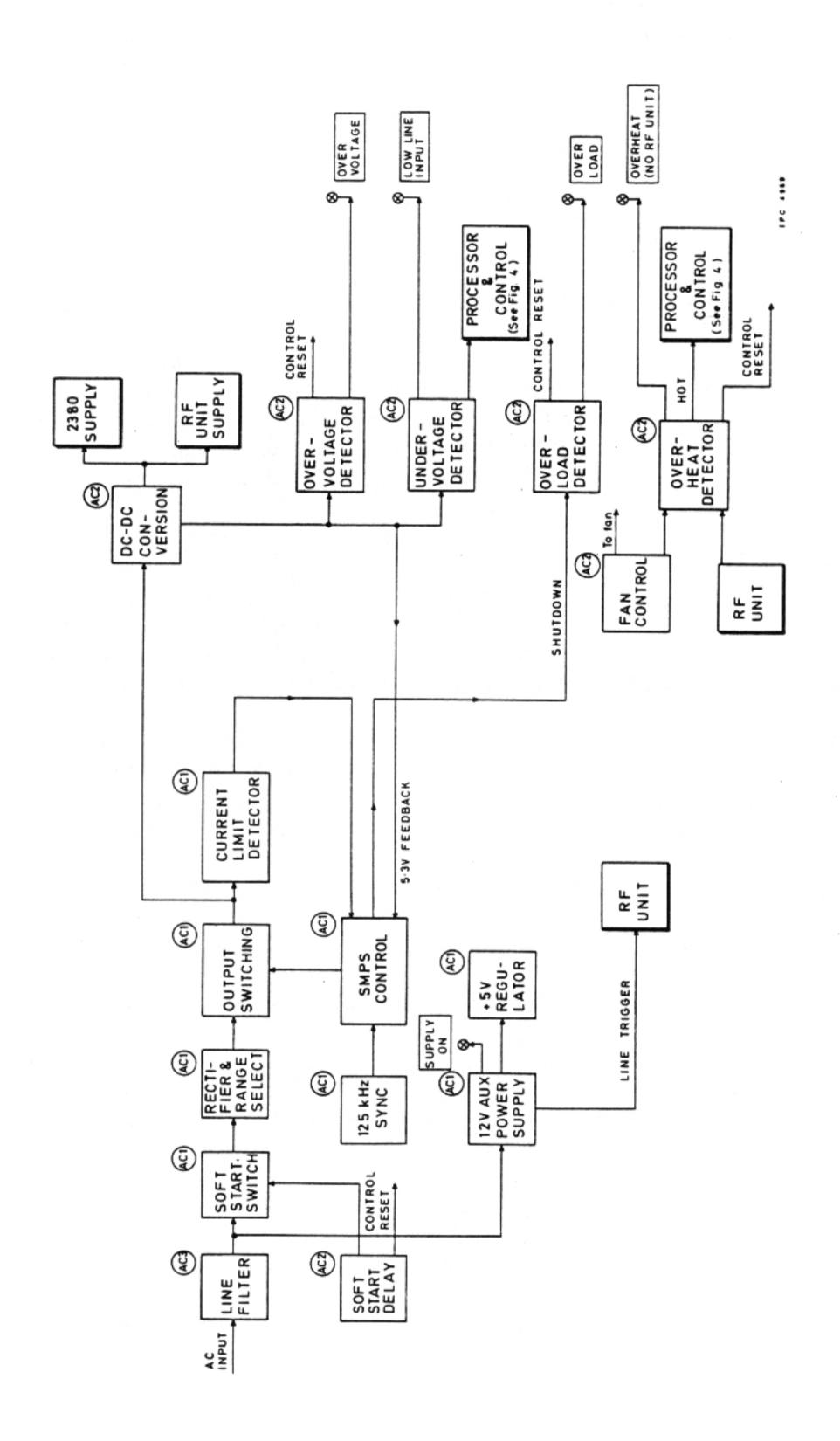

| 166   | Power supply                                           |         |         |       |

| 168   | Board AC1/1 - Input and control of SMPS &              |         |         |       |

|       | Board AC3/1 - Line filter                              |         |         |       |

| 180   | Board AC2/1 - Output and monitors of SMPS              |         |         |       |

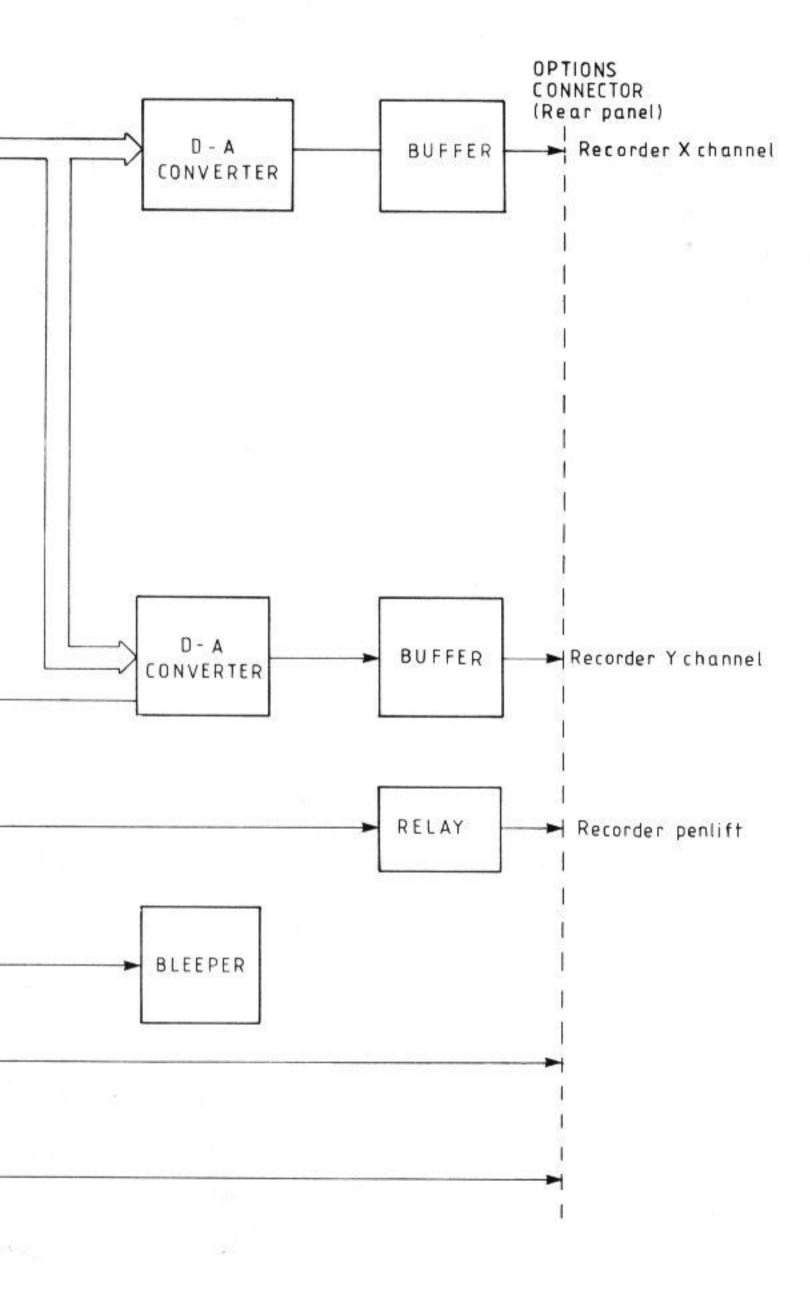

| 190   | Penplot and RGB video (optional)                       |         |         |       |

| 191   | Board AB8 - Penplot & RGB video                        |         |         |       |

|       | Total Control (102 (100)                               |         |         |       |

|       |                                                        |         |         |       |

| Table | e                                                      |         |         | Page  |

| 1     | Overrange detector operation - AB4                     | •••     |         | 16    |

| 2     | Display algorithms - AB5                               | •••     |         | 21    |

| 3     | Vertical graticule decoding - AB6                      | •••     |         | 22    |

| 4     | IC5 marker decoding - AB6                              |         | •••     | 22    |

| ,     |                                                        | •••     | •••     | 22    |

|       |                                                        |         |         |       |

| Fig.  |                                                        |         |         |       |

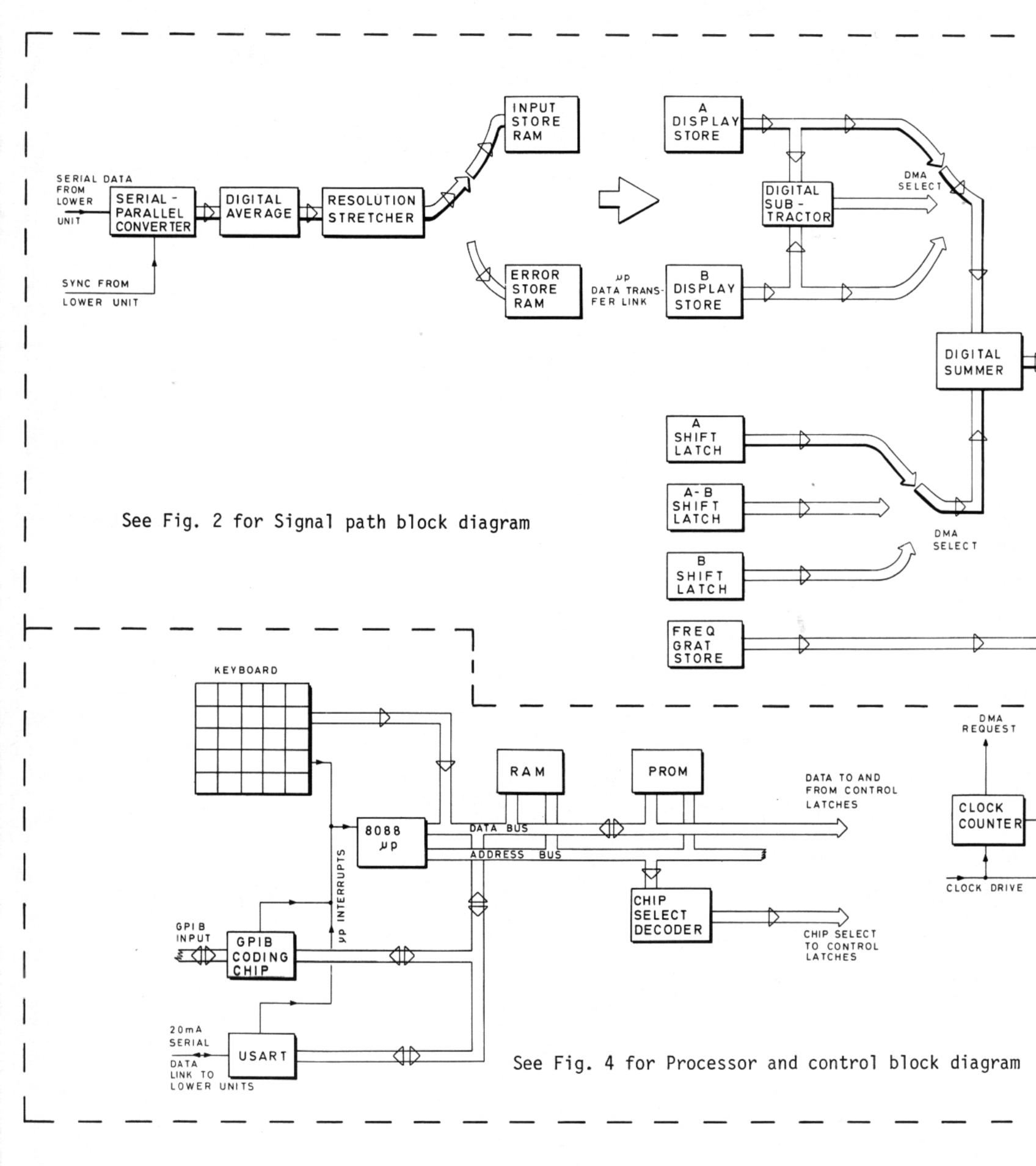

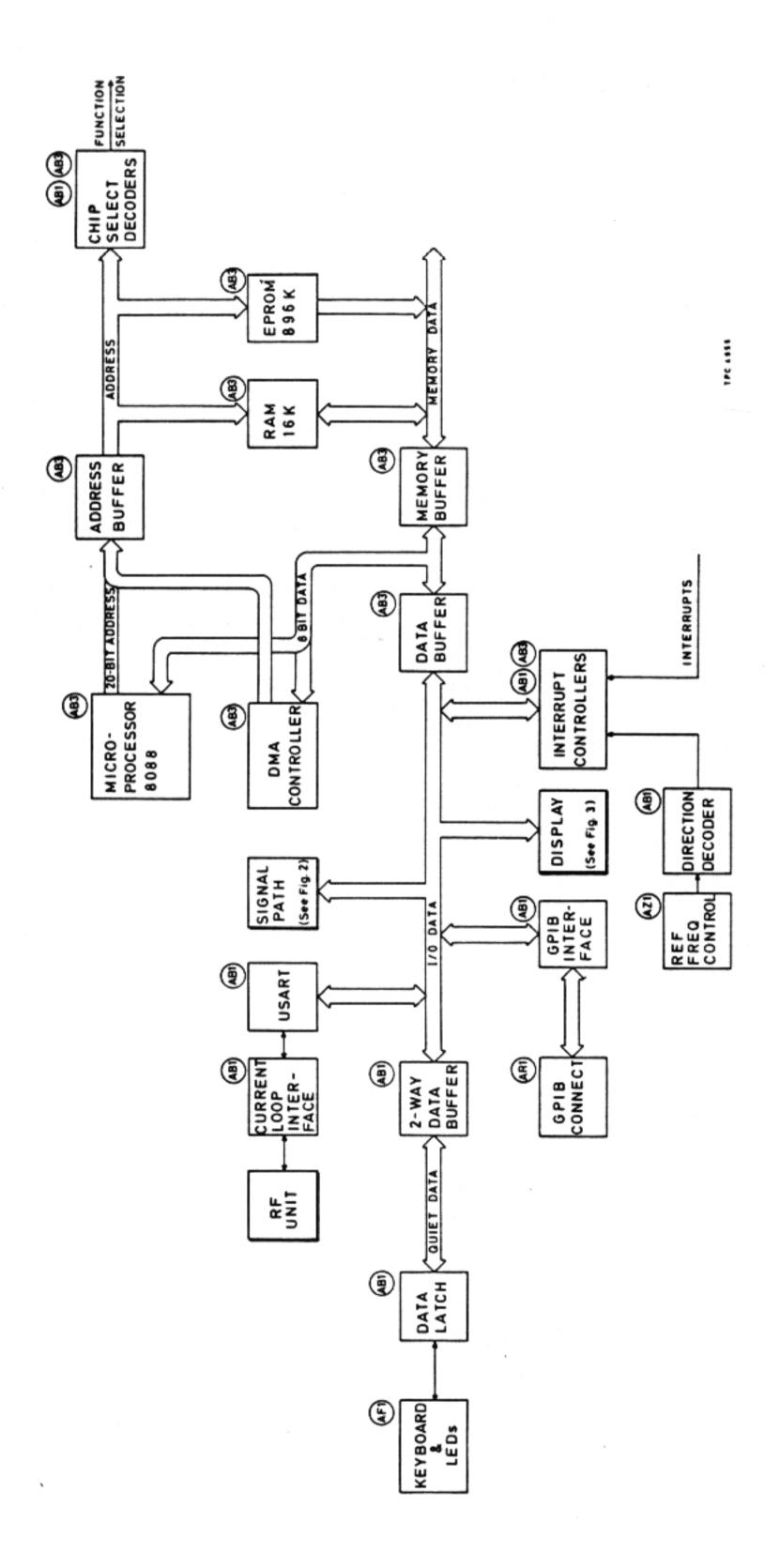

| 1     | Block schematic of 2380 System                         |         |         | 3/4   |

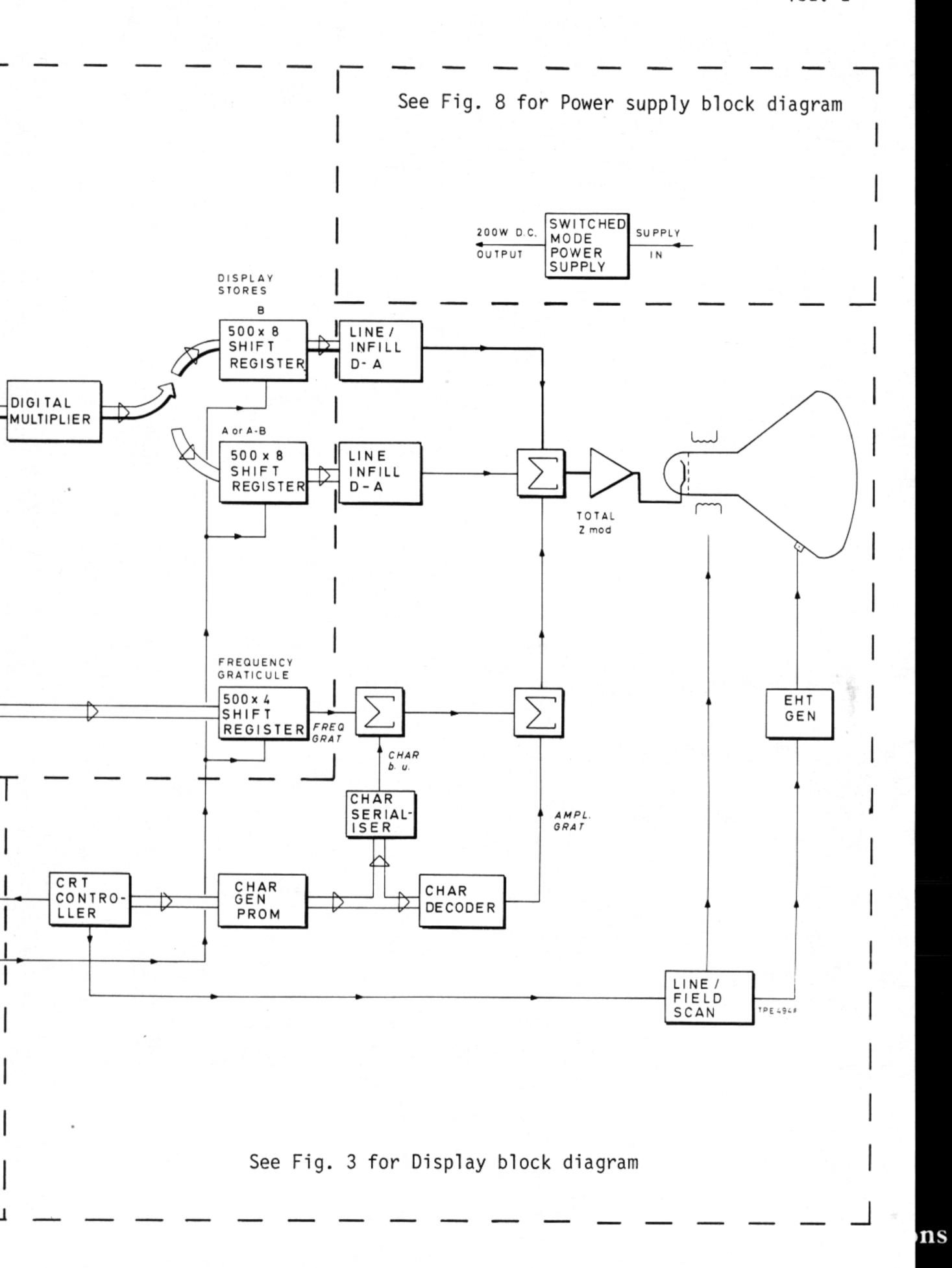

| 2     | Signal path block diagram                              | •••     | • • • • | 6     |

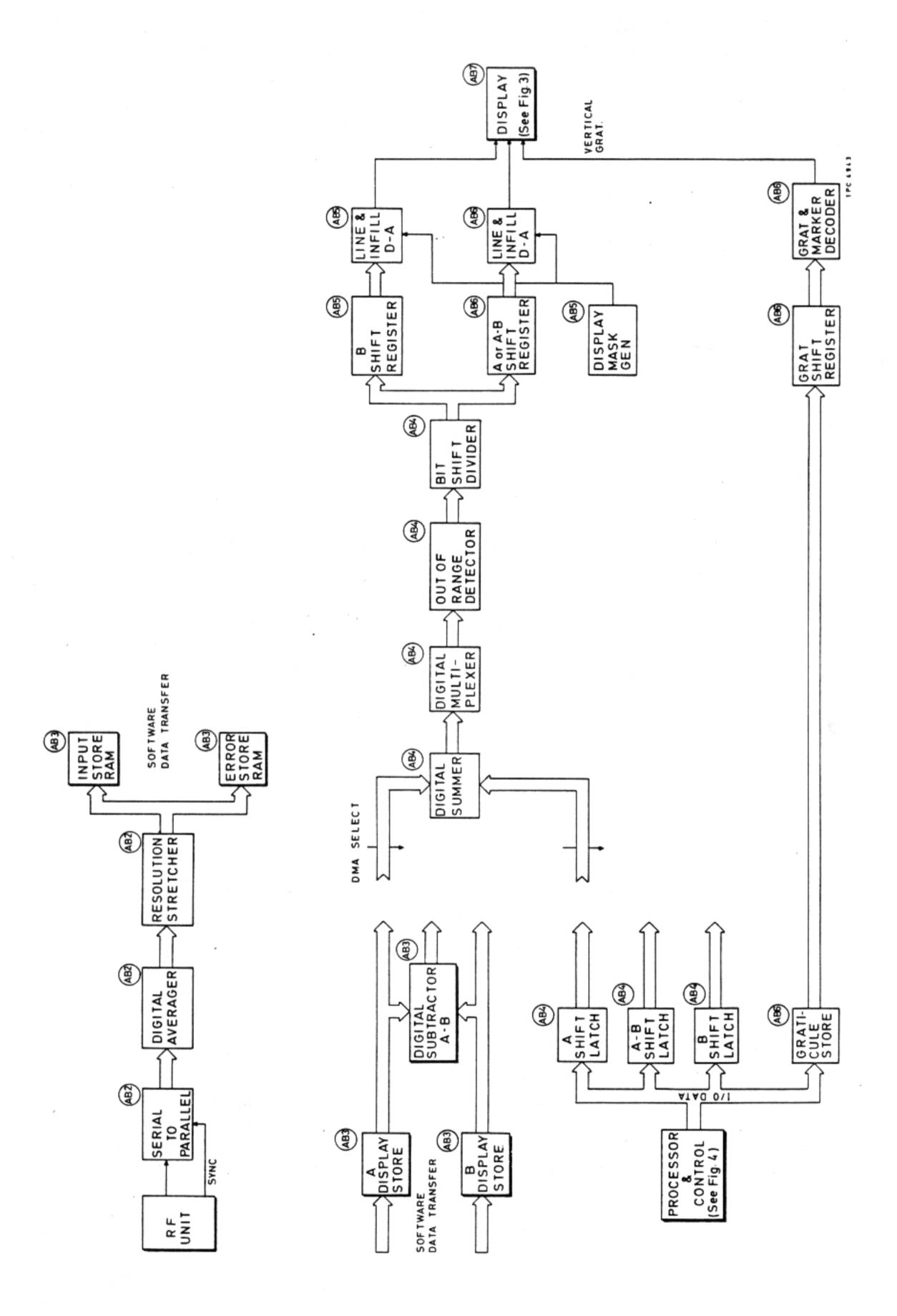

| 3     | Display block diagram                                  | •••     | •••     | 0.1   |

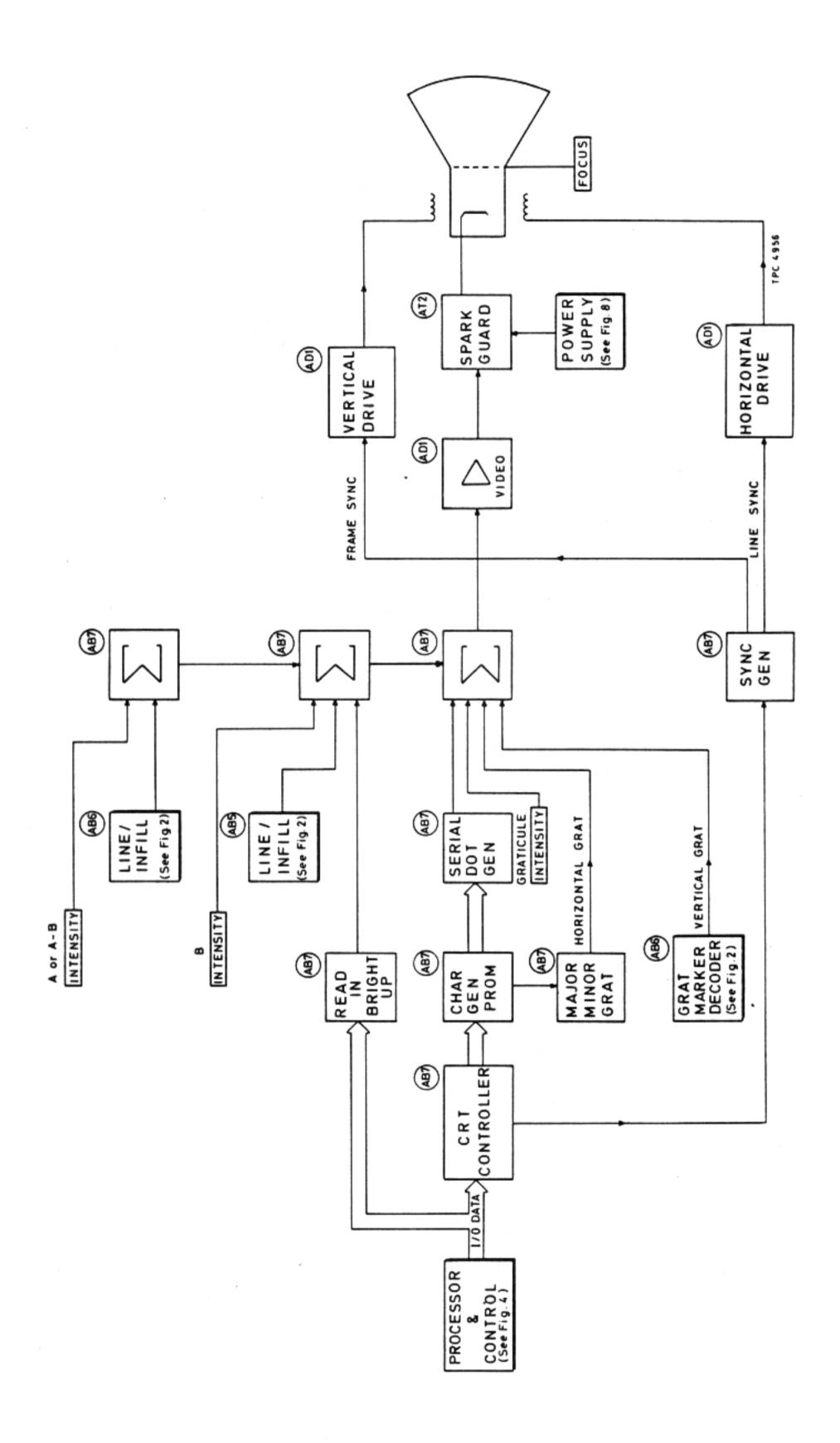

| 4     | Processor and control block diagram                    | •••     | •••     | 32    |

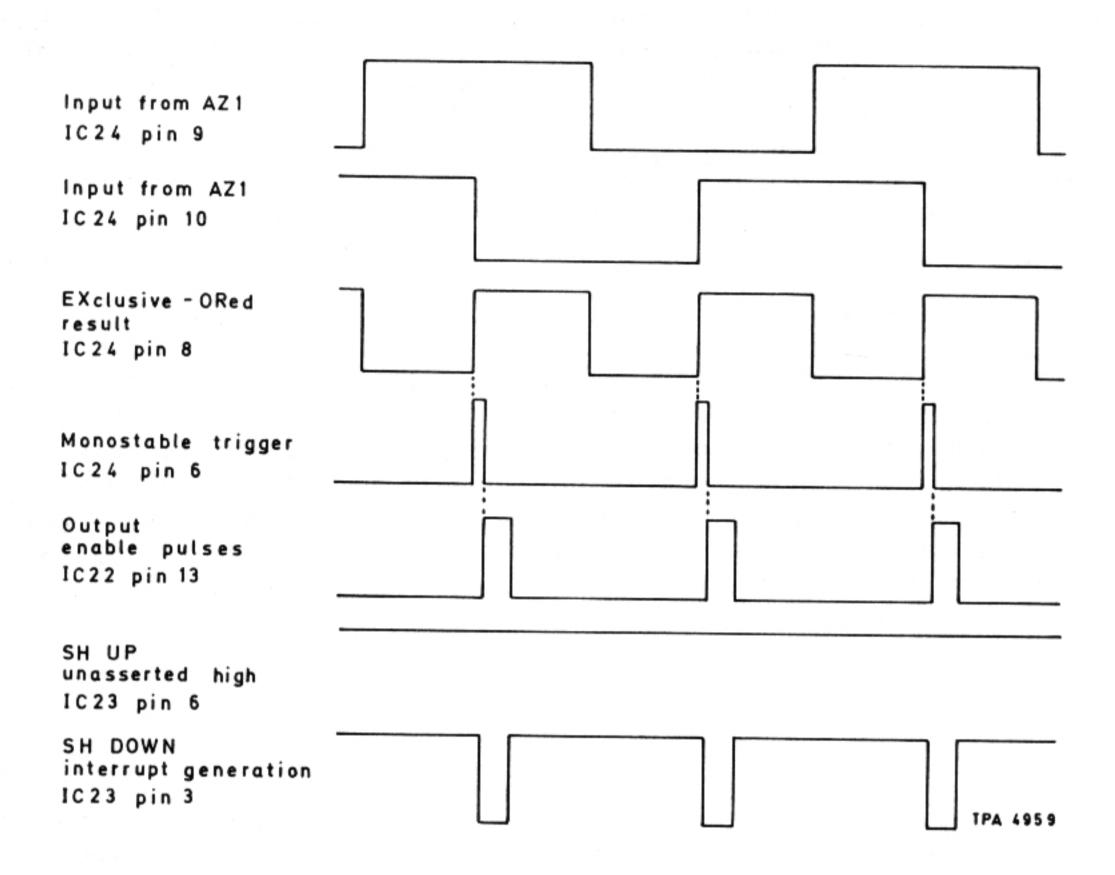

| 5     | SET REF LEVEL control direction detector example - AB1 | •••     | •••     | 35    |

| 6     | General Purpose Interface Bus (GPIB) structure - AB1 . | • • • • | • • •   | 00    |

| 7     | Handshake procedure - AB1                              | •••     | •••     | 39    |

| 8     | Power supply block diagram                             | •••     | •••     | 44    |

| 9     | Pen plot and RGB video block diagram                   |         |         | 53/54 |

|       |                                                        | •••     | •••     | JJ/ J |

|       |                                                        |         |         |       |

#### INTRODUCTION

- 1. The following description should be read in conjunction with the appropriate diagrams in this chapter and with the circuit diagrams in Chap. 7. The circuits are summarized in paras. 3 to 8 and then described in detail in the paras. that follow.

- 2. The spectrum analyzer comprises one or more lower units containing the frequency synthesizer plus a common upper unit described in this volume containing the display and power supply. Communication is via a two-way serial 9600 baud 20 mA current loop for housekeeping data whilst a one-way high speed serial link is used for the display data. The upper unit's power supply will power up to two lower units with only one selected at any one time. The lower units are internally wired to be self-addressing, therefore any configuration of units may be controlled via the front panel or remotely via a single GPIB socket as if it were a single instrument.

#### CIRCUIT SUMMARY

#### Signal path, display, pen plot & RGB video

- 3. The serial data input from the selected lower unit at the 2.5 MHz bit rate (see Fig. 1) is converted to 16-bit parallel data and is subjected to a running digital averaging process to simulate the customary video filter. A normal analogue RC network is inappropriate since, due to the inclusion of the high resolution switched gain logarithmic amplifier, no full range detected analogue signal exists anywhere in the system.

- 4. Since the final stored picture has a resolution of 500 slots across the displayed frequency span, it is necessary to ensure that any spectral responses less than one slot wide do not get missed or attenuated. The Resolution Stretcher is designed to do this whilst at the same time not exaggerating the noise level, as a simple peak hold circuit would do.

- 5. The processed data word is now transferred under Direct Memory Access (DMA) control to RAM space dedicated as Input Store or Error Store depending on whether the current sweep is a measurement scan or a calibration scan. The data in these two stores is now selectively subtracted (the data space in the Error Store permits correction over the range 100 Hz to 400 MHz) and loaded into the appropriate dedicated RAM spaces known as A Store and B Store under microprocessor control.

- Each Display Store shift register contains 500 bytes representing the 6. data for the currently displayed image. These data can be used to produce an infilled display or an outlined display depending on the option selected. the completion of each horizontal scanning line (one complete recirculation of data in the shift register), the Clock Counter generates a DMA request. results in a DMA transfer of a single display slot of data from the appropriate Display Store to the appropriate shift register. transfer the 16-bit word in the Display Store is added to the 16-bit word in the Shift Latch to arrive at the correct vertical display value and is then subject to the correct hardware multiplication to give the selected scaling factor before the 8 bits appropriate to the selected display range are loaded into the recirculating shift register. The output from the shift register is used to produce a solid (infilled) display or is subjected to further line draw processing to produce an outlined display. The resulting signal is then mixed with the graticule and character symbol data before being applied to the video amplifier and thence to the c.r.t.

- 7. The frequency graticule data and marker data are similarly refreshed, two bits being used for Graticule brightness information and two bits being used for Steady or Flashing Markers.

- 8. The c.r.t. controller chip organizes the display drive waveforms and also drives the character generator EPROM to annotate the graticule and display mode status information. The first character of each line is used as a control character and is suppressed, decoded and used to generate the amplitude graticule. Thus the graticule for both axes is under microprocessor control and may draw in any type of ruling to suit the needs of the display.

- 9. An optional board supplies the drives for the x and y axes of a pen recorder, as well as RGB outputs for use with a colour monitor and a composite video output for a monochrome monitor.

#### Processor and control

10. Front panel controls are serviced via microprocessor interrupt procedures. Additionally, the processor shares the data and address buses with a DMA controller to allow direct memory access to selected peripherals. All system switching, control and flag reads are done via a two-way buffer on the microprocessor bus. In this way, bus wiring is free from the continuous data train of pulses on the normal microprocessor bus thus reducing the possibility of interference to the analogue circuits. Housekeeping data between the processor and the r.f. units is conveyed by 20 mA current loop. The GPIB interface housed in the display unit allows the spectrum analyzer to form part of a system acting under the direction of a controller.

#### Power supply

11. Besides powering the display unit, the power supply supplies one r.f. unit on full power and a second on standby power. The switched mode power supply controller operates in synchronism with the associated r.f. unit's frequency standard. The controller shorts down to provide protection against overload, overvoltage or overheat conditions while rear panel l.e.d's illuminate to warn of overvoltage, undervoltage and overload as well as to indicate when no r.f. unit is connected.

#### SIGNAL PATH

12. The signal path block diagram is shown in Fig. 2. Serial data for display from the r.f. unit at a 2.5 MHz bit rate and accompanied by a synchronizing pulse is applied for processing by board AB2. Only the least significant 13 bits of the 23-bit word are used by the r.f. unit. is serial to parallel converted and simultaneously averaged in a shift register. Here, up to the full 23 bits may be used for addition during the averaging process used to simulate a video filter. Synchronizing pulses are counted on AB2 to indicate to the processor when data for the next ordinate (out of the 500 displayed) is to be written into the data store, as well as indicating end of sweep, according to display mode. Maximum and minimum data latches on AB2 implement the resolution stretcher used to ensure that spectral responses less than one slot wide do not get missed. The data is next transferred under direct memory access to either the input store or the error store in RAM depending upon whether the current sweep is for data or measurement purposes. After selective subtraction, the now calibrated data is loaded into the A or B display store in RAM.

Fig. 2 Signal path block diagram showing main functions of boards

- 13. Data from the A store, the B store or the result of A-B is summed on AB4 with the A,B or A-B shift latch respectively to determine the vertical display position. A xl or x5 multiplier on AB4 provides the required scaling factor. The following bit shift divider, responding to controls such as for reference level, operates in conjunction with out of range detectors. The B data is fed to AB5 while the A or A-B data together with the graticule data is fed to AB6.

- 14. 8-bit data for each of 502 ordinates is held in Display Shift Registers (DSR) on boards AB5 and AB6. The A store DSR on AB6 holds either A or A-B data, while the graticule DSR on the same board holds 4-bit data for the vertical graticule lines (horizontal line data is processed on AB7). All shift registers are recirculating to enable the data to be read non-destructively in byte serial form. Each circulation represents one horizontal display scan. At each ordinate position, the 8-bit display data is decoded to determine which picture elements are to be lit up to provide the selected infilled or outlined display. In the case of the graticule, the elements are lit up to form the vertical line when the scan reaches the appropriate position. The 4-bit graticule data in fact contains both graticule and marker information, 2 bits are decoded to define a major, minor, dashed or no graticule line, while the remaining 2 bits are used for steady or flashing marker selection.

- 15. Clock generators on AB5 control the operation of the shift registers on both AB5 and AB6, as well as providing the horizontal and vertical masks used for screen blanking to prevent spurious data from appearing outside the  $502 \times 250$  element display area. Outputs for the different displays are taken to the video mixer on AB7.

# Board AA1 - Mother board & Board AA2 - Auxiliary connector

Circuit diagrams: Chap. 7, Figs. 4,5 & 14

- 16. Mother board AAl connects together eight 60-way 2-side edge connectors and five smaller connectors. The eight hold the main logic boards, ABl to AB8. The backplane behind them consists of two sets of bused signal lines and an area of daisy-chained lines. The bused signals are common to many of the boards, e.g. power rails, data bus, processor read and write signals and clock signals. The daisy chain area is used to connect 'private' signals between adjacent boards. Included in the bused signals are some which will allow expansion at a later date, mainly on the options board AB8. Examples of this are colour video output and the addition of a second interrupt controller.

- 17. The small connectors on AAl are as follows: PLA is used to transfer signals from the backplane to the lower unit via the data connector on the rear panel. PLB connects the backplane to the INTENSITY controls and the SUPPLY ON l.e.d. on the front panel. PLC connects the main power rails from the power supply to the backplane. PLD connects some signals and the minor power rails from the power supply to the backplane. SKJ connects the TV unit to the backplane.

- 18. Auxiliary connector AA2 transfers some 'private' signals between AB5 and AB6, there being too many to fit in the daisy-chain area of the mother board alone.

#### Board AB2 - Input signal data processing

Circuit diagrams: Chap. 7, Figs. 8 & 9

- 19. The circuit of AB2 can be split into two major blocks, following roughly the same break line as the two sheets of the circuit diagrams. The first section deals with the gathering of the data from the lower unit, which is in serial form, and producing a parallel data word. In this section of the circuit the data is averaged. There is also a number of ICs employed in the synchronization of the serial to parallel conversion, and the calculation of the Ordinate Rate, which is the rate at which data is input to the data stores of the analyzer.

- 20. The second section of the circuit includes a maximum and a minimum detector which acts on the parallel data word produced by the averaging process in the first part of the circuit. An algorithm is used to determine which of the two detectors is used as the source of data which will be stored in the data stores.

## Parallel to serial conversion and averaging

- 21. The data from the lower unit is sent in a serial format and is packaged as a 23-bit word every 10 ms at a 2.5 MHz bit rate. Only 13 of the bits are used by the lower, r.f. unit, and occupy the least significant 13 bits of the 23-bit word. The least significant bit is sent first. To enable the data to be synchronized as it arrives from the lower unit, an END OF CONVERSION pulse is provided by the r.f. unit. This negative-going pulse arrives on a separate line. The positive-going edge marks the beginning of the first data bit.

- 22. The circuit based on IC30 serves to provide clock pulses that have edges about half way through each data bit period. This part of the circuit (a divide by 5) has a 2:3 mark space ratio. The divider is held in the reset state during the END OF CONVERSION synchronizing pulse, and it is clocked at a clock rate 5 times faster than the required clock frequency. In this way, the divider produces on its output a clock frequency at 2.5 MHz which is used to clock the data into the shift registers. The active edge is 2/3 of the way through the data periods.

- 23. As with standard serial to parallel practice, the two clock frequencies (the one clocking the data out of the lower unit, and the one clocking the data into the upper unit) need not be exactly the same, so long as the difference in frequency does not cause the clocking edges to drift outside the data bit periods. In this case, since the clock pulses may start within 1/3 of the clock period from the edges of the data periods, and there are 23 such data periods, the accuracy of the clock should be better than 1 part in 69. It is for this reason, that the difference in the master clocks of the two units (about 1 part in 400) is of no consequence since both master clocks are crystal controlled and phase locked together.

- 24. The actual serial to parallel conversion takes place using three 8-bit shift registers, ICs 15 to 17. The data is input via a one bit full adder. The action of this adder is to add together the incoming data with the data which is being shifted through the shift registers. By selecting the correct tap on the shift registers (the 23rd tap, since the data words are 23-bits long), the recirculated data bits will have the same bit value as the bits to which they are to be added. After two data words have been added, the value in the shift register will be twice the value of the two individual data words

(assuming both data words had the same numerical value). Hence the correct value can be obtained from the shift register by performing a one bit shift in the correct direction (a one bit shift to the right is a divide by two). If the two data words were different, then the value obtained would be the average of the two words.

- 25. By taking four words at a time, adding them in the same manner as above, and then performing a two bit shift, the average of four words can be obtained. Averages over other numbers of data words can also be done, but to enable simple division by the application of bit shifts, these are restricted to simple binary numbers. Since the total of the additions must be stored in the shift register until the time when the final shift/division takes place, there is a maximum number of additions that can take place before the 23 bit capability of the shift register is exceeded.

- 26. The controlling of the shift register, the adder and the final shift/division is achieved by the Average Clock Counter, IC20. This counter is programmed with the total number of clock pulses to be applied to the shift register. To clock in one complete word, 23 clock pulses are required. To add two words together, 46 clock pulses would be required etc. These numbers are modified by two factors: the final shift/division, and the positions of the 13-bit parallel taps. Since the taps are on the first thirteen bits of the shift register, the number of clock pulses required for the first word to appear at the output taps is only 13. However it still takes 23 pulses before it reaches the end of the shift register and is ready to be added to the next data word should this be required.

- 27. To allow for the final shift/division, extra pulses must be applied to the shift register to move the data through by the correct number of bits. The final division ratio becomes  $23 \times N 10 + 2LOG(N)$ , where LOG is to the base 2. This formula is derived from; 23 bits  $\times N$ , where N is the number of averages of 23-bit words; -10 for the offset due to the position of the taps; and LOG(N) for the number of bits of shift to perform the correct division.

- 28. After the correct number of clock pulses, the output of the Average Clock Counter causes the data appearing on the shift register taps to be latched into ICs 32 and 33. At the same time the shift register is reset ready for the next average, and the pulse is passed to the second block of the circuit on the ENABLE line to signal that data is available.

- 29. The one bit full adder, mentioned earlier is made from separate gates. The CARRY OUT is latched from one data bit period, and applied to the carry input during the next data bit period.

- 30. Some very slow sweep rates using narrow filters require that the averaging be done over a period of greater than 210 data input words. This is not possible, as stated earlier, because the shift register cannot contain the total of that number of data words. However, the data words produced by such a sweep are necessarily varying at a very slow rate due to the band limiting effect of the i.f. filters, and thus two or more consecutive words cannot differ by any significant amount. Under these circumstances a proportion of the input words is lost, without any fear of losing required data. The programmable Input Word Rate Divider and the latch IC18a provide a gating signal to the STROBED 2.5 MHz clock used to clock the shift register. In this way, a gating signal is provided to extend the data averaging period by up to 216 times greater than the basic 10 microsecond sampling rate.

#### Clock generation

- 31. The Ordinate Clock Generator and the Sweep Terminator Generator are two closely related parts of the circuit. During normal (swept linear frequency) scans, the incoming END OF CONVERSION pulses are counted, and a pulse is produced which signals to the processor that it is time for the next data ordinate to be written into the data stores. The END OF SWEEP pulse produced by the Sweep Terminator Generator is, on these 'normal' sweeps, a pulse produced by a division by 502 (by IC20) on the ORDINATES pulse. The division is by 502 because there are 50 ordinates in each of the 10 frequency segments across the display, and 2 more are on the last graticule line.

- 32. It should be noted that, although the averaging and the ordinate clocks are both derived from the same END OF CONVERSION pulses, they are not locked together; the averaging clock is a 1 2 4 8 16... division on the END OF CONVERSION pulses, and the ORDINATES clock is a 1 2 5 10 20... division on the END OF CONVERSION pulses.

- 33. For the Zero Span modes, the r.f. unit defines the ordinate rate and therefore the Ordinate Clock Generator division ratio must be set to one. Since this is an inadmissible division ratio for this programmable section, the divider has to be bypassed. This is done by programming its output to be high impedance, pulled to a logic 1 by the pull-up resistor, and using only monostable pulse generator IC34 to produce the 1:1 END OF CONVERSION to ORDINATES pulse ratio. The Sweep Terminator Generator still produces its pulses every 502 ordinates.

- 34. In the Log Scan mode, each decade is swept separately by the lower unit. Each decade sweep is used to fill 1/nth of the data stores, where n is the number of decades requested for the display. The total number of ordinates in n decades is not exactly 502 (or 500 for that matter) for all values of n, since there must be the same number of ordinates in each decade, and 500 is not divisible by 3, 6, 7 etc.

- 35. During these Log sweeps, the Sweep Terminator Generator is used in a different manner. It is used to create the log shaping to the frequency scale of each decade. The linear decade frequency scan produced by the lower unit is divided into ten segments. Each segment will have the same number of ordinates, but will represent a different amount of the frequency scan, the proportions being in a logarithmic ratio. The Sweep Terminator Generator is used to signal the end of each of these segments. It is programmed to interrupt the processor after the (fixed) number of ordinates in each segment. The Ordinate Clock Generator is programmed with a different number for each segment, and by using the facilities of the programmable counter, viz preselecting the next count ratio before the last count has been completed, the interrupt from the Sweep Terminator Generator need not be very high priority.

- 36. On Logarithmic sweeps, where the number of decades is low, the number of END OF CONVERSION pulses per ordinate is small. It is not possible to produce a good approximation to a logarithmic scan by using the same number of END OF CONVERSION pulses for each ordinate in any one segment. Since the overhead of programming the Ordinate Clock Counter differently for each ordinate is too great, a much faster clock is used so that the gradation from one segment to the next can be much finer and more exact. The clock chosen is a 2.5 MHz output from the CLOCK TICK generator prescaler IC31. It is

gated (in the programmable divider) by a signal from IC25a which starts with the first END OF CONVERSION pulse, and stops when the Sweep Terminator Generator produces its END OF SWEEP pulse.

37. Divider IC29 in this section of the circuit provides a glitch-free 6.25 MHz clock for the microprocessor and the UART; the clock produced by the 6.25 MHz phased clock generator may have glitches until the CRT generator is set up. Another divider, IC20 and IC31 produces the CLOCK TICK signal for the real time executive. The clock rate is 10 ms.

#### Maximum and minimum detectors

- 38. The maximum detector consists of the 16-bit comparator formed by ICs 9 to 12 which compares the incoming PARALLEL AVERAGED DATA with the data already stored in the Max Data Latches, IC23 and IC24. The presence of new data is signalled by the ENABLE pulse from the Averager Clock Counter. Should the new data be smaller, no action is taken, but should it be larger it is transferred to the Max Data Latches and becomes the new maximum data value. IC12 pin 5 'greater than' output is ANDed with ENABLE by IC13a and used to set max latch IC14a to show that a new maximum value has been found. If the data value did not rise above that stored in the Max Data Latches during an ordinate period, the max latch IC14a will not be set.

- 39. The minimum detector formed by ICs 5 to 8 works in a similar way to the maximum detector. The comparator finds the minimum values of the data, and stores them in the Min Data Latches ICs 21 and 22, setting min latch ICl4b at the same time. If the data value did not fall during an ordinate period, the min latch ICl4b will not be set.

#### Max/min select logic

- 40. At the end of each ordinate period, signalled by the ORDINATES pulse from the Ordinate Clock Generator, the Max/Min Latch Select Logic circuit (IC29a pin 1) and the DMA controller (DRQ Latch IC41 pin 13) are strobed. The Max/Min Select Logic operates using the algorithm described below.

- 41. Two of the several requirements of the spectrum analyzer display are that it should show the maximum value of any signals, and should at the same time show a reasonable representation of noise, and not just its peak and minimum values.

- 42. In a display where the IF filter bandwidth used is relatively wide compared with the scan width, the signal appears as a wide, rounded topped, display. Noise on the other hand would appear more ragged, and may well appear as 'grass', having a very fine amplitude v time display. During any one ordinate time period, when the analyzer is scanning through the signal part of the display, the max and min detectors, and their associated max and min latches would be detecting either a rise or a fall, but not both, since the signal amplitude is changing smoothly from one value to the next. When the scan is in the noise part of the display, it is likely that during any one ordinate period, new maximum and minimum values will be found, and both the max and the min latches will be set.

- 43. To form an acceptable display for this type of scan a very simple algorithm is used. When the signal amplitude is rising only, the peak detector is used. When the signal amplitude is falling only, the minimum detector is used. When the signal amplitude both rises and falls, then the state of the max and the min latches during the previous ordinate is checked. Should

this previous state be rise only, then the max latch is read for this ordinate; should the state be fall only, then the min latch is read for this ordinate; should the state be both rise and fall, then the opposite latch to that last read, is read for this ordinate. In this way, during periods of noise, the detector latches will be set during each of the ordinates, and the max and min data latches will be read alternately. However at a signal peak, the max latch will be read even though the signal both rises and falls, since the detector latches would have been showing 'rise only' during the previous ordinate.

- 44. To satisfy the algorithm, the outputs of max latch ICl4a and min latch ICl4b are ANDed by IC27a to produce a change-over signal to the following gates. These gates select either the state of the max latch if max.min='0', or the J-K bistable IC29a if max.min = '1'. When the signal does not both rise and fall, i.e. max.min = '0', then the max or min data latches are read depending on the state of the max latch when max.min = '1' then the J-K bistable performs the needed algorithm. It is clocked on the falling edge of the ordinates pulse, and therefore at the start of the next ordinate pulse the history of what happened at the last ordinate is available. Should the detector latches both be set, the J-K will toggle ready to select the opposite latch to that used on the current ordinate in the event of the next ordinate having max.min = '1'. If the detector latches have differing outputs (max.min = '0') then the outputs of the J-K will reflect the input state after the clocking pulse. Hence the output will select the same latch as the previous ordinate if max.min = '0'.

- 45. The data enters the max output latches IC37 and IC39 and the min output latches IC35 and IC36 as a 16-bit word under DMA transfer. Since the DMA process transfers 8 bits at a time, two transfers per word have to take place, with the least significant byte being sent first. The ORDINATES pulse from the Ordinate Clock Generator sets the cross-coupled NAND R-S bistable IC41a, IC41d, causing DRQ 0 to become active. The High/Low Byte Select Generator then selects which of the two data bytes must be sent first. This m.s.b./l.s.b. signal is further gated with the max/min latch select signal so that the correct byte from the correct data latch is selected. When the second byte is selected, the R-S bistable is reset which removes the DRQ 0 signal.

- 46. It is possible, since the ordinate rate and the rate at which averaged data words are produced are not synchronized, that new averaged data will arrive during the data transfer process, and a change in the detector latch outputs could occur. This would cause corruption of the data levels since half of the data word would be read from one latch and half from the other. To stop this happening, the output of the change-over gate, selecting either the max or min data, is latched so that it remains constant during the time that the data is read into the input store of the display.

- 47. The rules about resetting the max and the min data latches are quite simple. Each time data is output to the data stores, the min data latches and the min latch are reset. The min data latches are reset to the current value of the data from the averager. The resetting of the max data latches occurs whenever they are read, and also whenever the min data latches are read as a result of a min only signal (max.min = 0). It too is reset to the current value of the data from the averager. The max latch is reset each time data is read, at the same time as the min latch and the min data latches.

Bypass of the display detector, (for use during Sampled Zero Span displays), is provided via IC38 (CS1E). The detector circuit is enabled whenever IC38 pin 2 is at a logical 'l' state. It will be seen that under these conditions the three most significant bits of the new data being compared in the max and in the min data identify logic comparators will be set, and will match exactly the three m.s. bits applied to the other inputs. The comparison will then ignore these identical bits, and compare the bits of lesser significance. When IC38 pin 2 is at a logical '0' state, the m.s. bit of the max comparator new data input is at a '0' and hence the new data input must always be judged 'less' by this comparator, and hence the max latch will not be set, and no data will be transferred to the max data latches. The minimum detector has its inputs controlled in the same way, and will therefore set the min latch and transfer the data to the min data latches. The detector circuit is hence disabled since its output is always set to give the 'min' signal (i.e. no max and min stitching), and the data transferred to the input data stores is always that applied to the min latch immediately before the data transfer.

#### Sweep flyback

49. When a new sweep is started, data from the previous sweep will still be held on the board and would, incorrectly, both be averaged with the new data and displayed as the first ordinate of the new sweep. The DISPLAY DETECTOR FORCE MAX, FORCE EOC and MISS FIRST ORDINATE signals from octal latch IC38 prevent this from occurring. The sequence is as follows: DISPLAY DETECTOR FORCE MAX is asserted low to IC12 pin 1 in preparation for the next data byte. Averager Clock Counter IC20 then generates a pulse during flyback which resets the Serial to Parallel Converter ICl5,16,17 to zero and latches the zero into the paralled averaged data latch IC32,33 while also providing the ENABLE pulse to the next stage. With its most significant bit pin 1 set low, IC12 recognizes the applied zero data as a new maximum so that, at the end of the ENABLE pulse, the zero data is latched into max data latches IC23,24 and max latch ICl4a is set. At this point the DMA controller on AB3 causes extra DMA cycles to be made to dump the unwanted data in the output latches to spare memory locations. FORCE EOC is next asserted high to IC42 pin 10. ZERO SPAN MODE is asserted low to IC19 pin 4 and when FORCE EOC is removed, the falling edge causes IC34 to generate an ORDINATES pulse to High/low Byte Select Gen IC43b and latches the zero data into max output latches IC37,39. But to prevent this data from being accepted into the data store, IC38 asserts MISS FIRST ORDINATE high to prevent a DMA request from being made. this, the signal is inverted to reset IC25b causing IC41b to gate off the ORDINATES pulse from DRQ latch IC4la,b so preventing DRQ being asserted high to the DMA controller on AB3. When the data for the new sweep arrives it is recognized as a new maximum (since the previous data was zero) and thus replaces the zero data in the max output latches.

#### Board AB4 - Mathematics operations

Circuit diagrams: Chap. 7, Figs. 12-14

#### DMA control and input data selection

50. Board AB4 receives two sets of data, A and B, and from these generates a third, A-B. Data enters the A latches IC38, IC40 and the B latches IC39, IC23 under DMA (Direct Memory Access) control. DMA request latch IC19 output pin 5 goes high at the trailing edge of the WD signal to pin 3. WD goes low when data is to be written to the display shift registers. Since the WD

pulses occur at the line refresh rate, AB4 has about 64  $\mu s$  in which to process new data before it is required for display.

- 51. The A and B latch sets each accept 16-bit data (although only the lower 15 bits are actually used), which are presented in the byte sequence; B low, B high, A low, A high. The DMA controller, in fact, follows these with a byte of graticule data, but this is not used on AB4, being latched on AB6 instead. The input latches are controlled by the DMA byte counter IC35 and the associated B, A, graticule demultiplexer IC18. The DMA byte counter counts 5 DACK1 + IOWR clock pulses before resetting DMA request latch IC19 on pin 1.

- 52. The WD pulse when active low to pin 1 IC35, resets the DMA byte counter to point at the B low latch IC39, ready for the first byte in the sequence. When the DACK1 + IOWR signal becomes active it clocks DMA byte counter IC35 which causes demultiplexer IC18 Yl output to go active low and the YO output to go inactive high. Thus the B low latch IC39 receives a positive-going clock edge on its pin 11 and the first byte enters that latch. As succeeding DACK1 + IOWR pulses arrive, so Yl, Y2, Y3 and Y4 each in turn supply a positive-going edge to their associated latches IC23, IC38, IC40 and that on AB6 respectively. When the fifth pulse arrives, IC35 pin 12 goes high and, via IC24d, IC37c and IC36a, resets DMA request latch IC19a. The whole sequence repeats when the next WD pulse arrives, with the exception of the period when FRAME is active low to IC36 pin 2; the signal prevents DMA channel 1 getting out of step with the display.

- 53. Once both bytes of B data have been latched, the data can be processed by the rest of AB4. That the B data is available is signalled by the B SEL pulse on IC18 Y2 output which clocks the A low byte latch IC38. Similarly, when both bytes of A data have been latched, the fact is signalled by the A OR A-B SEL pulse on the Y4 output which clocks the graticule byte latch on AB6. The trailing edge (positive-going) of B SEL is used to clock the processed data from AB4 into the latch on AB5, and A OR A-B SEL does the same on AB6.

- 54. A OR B SEL is gated with the outputs of the A/A-B select latch IC19 to give A SEL from IC37 pin 11 and A-B SEL from IC37 pin 3. These together with B SEL are used to decide which pair of tristate buffers, ICs 20 and 25, ICs 2 and 4 or ICs 1 and 3, will be enabled so as to send data forward for processing. The signals also control the outputs of the shift latches. The processor writes to the A/A-B select latch IC19b using CS36.

- 55. The A-B data is produced by adding the two's complement of the B data to the A data. This is done by ICs 21, 22 and 24 and ICs 14 to 17. The A-B data is then buffered by ICs 2 and 4 ready for selection if required.

#### Multiplier

- 56. In order that the displayed spectra can be moved up and down the screen, it is necessary to add a variable offset to the data. This is achieved by part of the circuit on sheet 2.

- 57. The 16-bit offset values for the three sets of data are loaded by the processor into the three pairs of shift latches ICs 41 and 44, ICs 42 and 45, and ICs 43 and 46. The processor addresses the latches individually via the local chip select decoder IC49. Maths function latch IC47 controls the multiply and divide circuits. This latch and the A/A-B select latch IC19b are addressed simultaneously using CS36; the latter accepts bit 0 of the byte

which the processor writes, while the former accepts bits 1 to 6. The multiply and divide circuits may need to operate differently for the B data and the A OR B-A data, so the maths function latch contains two sets of control bits at any time. The appropriate set is selected by the maths function multiplexer IC48 according to the states of the B SEL and the A OR A-B SEL signals.

- 58. When the outputs of the appropriate data buffers and shift latches are enabled the combined data appears at the outputs of the shift adder formed by ICs 26 to 29. Since the data is in two's complement form, the m.s.b. of the combined data on IC29 pin 13 represents the sign bit. And since no data is displayed whose value is less than zero this bit provides the UNDERRANGE signal used to limit the display to bottom of screen (i.e. any data which has a value less than zero is presented as zero on the display). The rest of the combined data is passed to the multiplier circuit formed by ICs 5 to 9, 30, 13a and 36b.

- 59. The multiplier can multiply by 5 or by 1, according to the state of the MPY signal from IC48 pins 5 and 16. To multiply by 5 (when MPY = 0), a copy of the data is moved 2 bits left (equivalent to multiplying by 4), and then added to the original. The original data is applied to the A inputs of the multiplicant adders, ICs 5,7,8 and 9. The x4 data is applied, via multiplier drive buffer IC6 and IC30, to the B inputs, with the exceptions that the two least significant B inputs and the least significant carry input, are all set to zero by the MPY signal. Thus the output of the multiplicand adders represents the input data x5. Because a 16-bit number is added to a 14-bit number, the m.s.b. of the multiplicand adders is output by IC36 pin 6.

- 60. To multiply by 1, the multiplier drive buffer (IC6 and IC30) outputs are disabled by MPY being high, and are pulled high by R3 and R4, so that the B inputs of the multiplicand adders and the input to inverter IC13 are all high. Thus the effect of the B inputs is negated; firstly by making all the B inputs logical '1', then adding 1 to the carry input pin 7 of IC5 so that an overflow occurs from IC9 pin 9, and finally by disabling IC36 so as to gate off the overflow.

#### Overrange detector and divider

- 61. The bit shift divider selects the appropriate set of 8 bits from the 17 available at the output of the multiplier circuit, but since the smallest division ratio is 2, the 1.s.b. of the multiplier output is simply ignored. The bit shift divider formed by ICs 51, 31, 32 and 50 selects sets of 8 bits which give effective ratios of 2,4,8 or 16 under the control of the division select decoder, which is, in turn, controlled by the maths function latch.

- 62. Even after the data has been passed through the divider circuit, it is possible for its value to exceed that which can be represented on the display (maximum is 250). Therefore, the overrange detector formed by ICs 10,11,12 and 34a, and controlled by the logic on the DIV L and DIV H lines checks the data for illegal values before it is finally sent to the output. For example, when the division ratio is set to 8, bits 2 to 9 are sent via IC32 to the display, while bits 10 to 15 are checked. If any of the latter are on then the data is overrange. The higher the division ratio, the fewer are the bits checked by the overrange circuits. Table 1 shows which bits are checked for the various division ratios.

63. Normally, division select decoder IC33 will enable one of the bit shift divider buffers by taking one of its Y outputs low. However, if the overrange detector finds that the value of the input data is too large, it disables the decoder via IC12c thus preventing any of the Y outputs from going low. The tristated output of the divider buffer will be pulled to all ones by the action of pull-up resistors R5. Similarly, if the UNDERRANGE signal is active, decoder IC33 outputs are disabled via IC12d while the underrange clamp IC52 is enabled thus pulling the output data to all zeros. The resulting processed display data is passed out to AB5.

TABLE 1 OVERRANGE DETECTOR OPERATION - AB4

| Division ratio             | 16  | 8        | 4        | 2 |

|----------------------------|-----|----------|----------|---|

|                            |     |          |          |   |

| Control signals:-<br>DIV L | L   | Н        | L        | Н |

| DIV H                      | L   | L        | Н        | н |

| Bits checked:-             |     |          |          |   |

| 8                          |     |          |          | ✓ |

| 9                          |     |          | √        | ✓ |

| 10                         |     | ✓        | ✓        | ✓ |

| 11                         | ✓   | ✓        | ✓        | ✓ |

| 12                         | √ √ | <b>√</b> | ✓        | ✓ |

| 13                         | ✓   | ✓        | ✓        | ✓ |

| 14                         | ✓   | ✓        | <b>√</b> | ✓ |

| 15                         | ✓   | ✓        | ✓        | √ |

Example: For :16 DIV L and DIV H are both low and bits 11 to 15 are checked for overrange.

#### Board AB5 - Timing & B display dynamic store

Circuit diagrams: Chap. 7, Figs. 15 & 16

#### Circuit Sheet 1

64. The method of displaying frequency spectra on the TV screen and the operation of the A channel, B channel, and Graticule Channel Display Shift Registers (ADSR, BDSR, GDSR) are very closely related. Note that the ADSR and GDSR circuits are on AB6, but all three DSR's are considered here, since they are governed by common timing circuits which appear on this board. The Spectrum Display Area (SDA) on the TV screen is essentially a histogram, nominally 500 ordinates along the X, or Frequency, axis, and 250 levels along

- the Y, or Amplitude, axis. The histogram can be overlain by a graticule, and, depending on the contents of the GDSR, the SDA can be made to represent graphs which are lin/lin, lin/log, log/lin, or log/log. Since it is desirable, for linear graphs, that the graticule should encompass an even number of ordinates, the DSRs are actually designed to hold data representing 502 ordinates on the X axis. In the A and B DSR's, one byte (8 bits, using 250 of 256 possible levels) is used for each ordinate.

- 65. The GDSR is used to hold data which represents the frequency (vertical) graticule lines only: the display of amplitude (horizontal) graticule lines is due to circuits on AB7. Also, the graticule is displayed at half the resolution of the spectra, and thus the GDSR is only half the length of the A and B DSRs. The GDSR holds just two bits of data for each graticule line position since it is only necessary to define a major, minor, dashed or no graticule line. The remaining two bits of the GDSR are used to hold marker data, and are discussed in the description for AB6.

- 66. The DSRs are provided with data feedback paths, so that the data may be read non-destructively in byte-serial form. The method and rates of clocking the DSRs are such that the data makes one complete rotation in the time the TV scan takes to pass across the SDA. On a given SDA scan line, the spectrum data for each ordinate is compared with the scan line number, and the result passes to logic which decides whether or not to light up the pixel (picture element) corresponding to the ordinate on that line. The graticule data is used directly to light pixels as the scan reaches the appropriate positions.

- 67. In order that new data may be written into the DSRs from time to time, they have multiplexers at their inputs. These select either data fed back from the DSR outputs, or new data which has been processed by AB4. They are under the control of the even/odd Write Pulse Generator (WPG), which allows one new byte to be written into each DSR during each SDA scan line period.

- 68. Each 8-bit DSR is formed by running 4-bit banks in parallel; the LSB bank which holds bits 0 to 3, and the MSB bank for bits 4 to 7. Each bank is comprised of two physical SRs, EVEN and ODD. New data is written to the EVEN registers of each bank simultaneously; similarly, the ODD registers. The EVEN and ODD pairs are written alternately. The register output multiplexers select, in parallel, the outputs of the EVEN pair alternately with the ODD pair, and the overall effect is thus of an 8-bit DSR whose length and clocking rate are each twice that of the physical SRs.

- 69. Each shift register is formed from three ICs, and since all four registers are similar, a description of the operation of the EVEN register of the LSB BANK can serve for all. The heart of the register is ICl3 which is a 4-bit by 256 word device. This m.o.s. IC is driven by a high level bi-phase non-overlapping clock derived from the 6.25 MHz SHIFT REGISTER GATED CLOCK. The signal, with a pulse width of 70 ns, is applied to pin 4 ( $\phi$ 1) and pin  $11(\phi$ 2). ICl3's clock-to-data-output delay is such that it cannot directly recirculate data and therefore an extra register stage, ICl4a follows whose output delay is very much shorter. ICl4a consists of 4 D-type bistables and is clocked by 6.25 MHz SHIFT REGISTER GATED CLOCK. ICl3 outputs are open drain and are made t.t.1. compatible by pull-down resistors R7a to d. Output is to multiplexer IC30.

- 70. Output multiplexers IC25 and IC30 are driven by the 6.25 MHz SHIFT REGISTER CLOCK signal and thus produce two streams of 4-bit data in parallel at a rate of 12.5 MHz. Input multiplexers ICs 26, 27, 28 and 29 are normally set to select recirculated data from the extra register stages of IC9 and IC14.

However, once every alternate TV horizontal scan (see above), the input multiplexers for the EVEN register pair, ICs 27 and 29, are made to select new data under control of the WE output from the Write Pulse Generator (WPG) to pins 1. Similarly, the ODD pair, ICs 26 and 28, are written due to WO once every other scan. Since data is written into the registers at a much slower rate than it is read, the WPG must keep track of where next to write data: the way it does this is described in a succeeding paragraph.

- 71. The high-level bi-phase clock for the shift registers is derived from the 6.25 MHz SHIFT REGISTER CLOCK signal by ICs 41, 42, 43 and 45. IC41 acts as a phase splitter, producing  $\phi$ 1 from pin 5 and  $\phi$ 2 from pin 6. The positive-going leading edges of  $\phi$ 1 trigger monostable IC42a which emits 70 ns positive-going pulses. These are a.c. coupled to clock drivers IC43 and IC45 which convert the pulses to high level (+5 V, -12 V) to supply  $\phi$ 1a and  $\phi$ 1b for the shift registers. Similarly,  $\phi$ 2 triggers monostable IC42b, and the 70 ns pulses which this emits are converted to  $\phi$ 2a and  $\phi$ 2b. The width of the  $\phi$ 1a,b pulses is set by R4,  $\phi$ 2a, b by R3.

- 72. Because the data in the DSRs must complete just one rotation during each TV horizontal scan, it is necessary to stop the DSR clocks periodically. This is done by the Gated Clock and Horizontal Mask Generator (GCHM). Although the A and B DSRs each hold 502 bytes of data to be sent to the display, they are actually 514 stages long. Hence, after allowing the DSRs to receive 502 clocks, the GCHM sets a mask which prevents the display of further "data", while the DSRs are given another 12 clocks. The GCHM then stops the DSR clocks completely, and awaits the next horizontal scan before resetting the mask, and re-enabling the DSR clocks. It should be noted that the DSRs operate over the whole vertical scanning cycle; in particular, the DSR clocks are NOT gated by any vertical retrace signals. The SDA, however, is defined with reference to vertical retrace (see below).

- 73. In order to maintain alignment between displayed data and displayed characters, the GCHM synchronizes its activities to the leading edge of HRTC (L) to pin 13 of IC40. Before HRTC goes low, the counter formed by ICs 16, 31 and 48 is held in the load state by IC40 pin 8, and START from IC16 pin 12 therefore is low. When HRTC goes low (beginning of horizontal retrace), it resets IC40 whose Q(L) output goes high. The counter is released from the load state and begins to count PHASED 12.5 MHz CLOCKS. Since the data display appears within an annotated border on the screen (i.e. the SDA), the counter is preloaded with a value such that when IC16 pin 12 goes high to assert START, an interval corresponding to the horizontal retrace period plus the chosen width of the border has elapsed. The rising edge of START clocks IC15b taking CLOCK EN low, which, via IC47b and IC46b produces the 6.25 MHz SHIFT REGISTER GATED CLOCK signal. Thus the DSR clock is started and data contained in the registers begins to appear at the output of multiplexers IC25 and IC30.

- 74. The same edge of START also clocks IC15a whose Q output supplies the X-direction video enable signal, XVIDEN. This is combined with other signals (see below) to enable the display of data within the SDA and so prevent spurious data appearing outside the SDA. When the counter has counted 502 clocks after START, all of the data in the DSRs will have been presented in the SDA. This state is detected by AND-gate IC32, and used to reset IC15a restoring XVIDEN low.

- 75. At this stage however, data byte 1 has not yet returned to register position 1 which it occupied before clocking began. This is because the data occupies only 502 of the available 514 positions. Therefore, the counter continues counting up to 514 clocks after START. This stage is detected by IC47a and used to reset IC15b. CLOCK EN therefore, goes high which stops the 6.25 MHz SHIFT REGISTER GATED CLOCK to the DSRs. Consequently, the shift registers stop with data byte 1 in position 1 again. At the same time, the rising edge of CLOCK EN clocks IC40a whose Q(L) output goes low, forcing the counter into the load state. This completes the horizontal scan cycle, and the whole circuit waits for the next HRTC falling edge.

- 76. A new data byte on the MULTIPLEXED PROCESSED DISPLAY DATA bus which is destined for the BDSR is first placed in B demultiplexing latch IC44, under control of B SEL to pin 11. IC44 outputs present the data to the NEW data inputs of the DSR input multiplexers. These normally select their recirculating inputs. However, once during every other SDA scan line period, the EVEN input multiplexers select their NEW inputs, so that the new data enters the EVEN register pair. On the alternate scans, the ODD input multiplexers select their NEW inputs, and the new data enters the ODD register pair. The signals controlling the input multiplexers are called Write Even (WE) and Write Odd (WO) and they are generated by the WPG.

- 77. The heart of the WPG is a 10-bit counter formed by ICs 1,17 and 33. counter is clocked by the 6.25 MHz SHIFT REGISTER GATED CLOCK and thus receives 257 clocking edges per horizontal scan. Bit 9 output from IC33 pin 13 to the inputs of bit 9 (IC33 pin 4) and bit 0 (IC1 pin 3) allows the counter to divide by 257 and 258 alternately. Hence, on every other scan, the counter's transition to a given state will move one clock pulse later, relative to the immediately previous scan. This is used as a pointer to successive locations in the register pairs. The counter is configured to derive WD(L) from IC34 pin 6 which determines where data should be written in a register pair, and the odd/even output from IC33 pin 13 which points alternately to the ODD and EVEN register pairs. Since there are only about 320 horizontal scans per TV field, it takes the WPG the best part of two fields to put new data into all 502 DSR locations. However, if the WPG writes to a DSR location on every scan in both fields, it will cause To prevent this, for every two fields the WPG is resynchronized to the trailing edge of FRAME(L) to IC2 pins 2 and 4, and after 502 bytes have been written into the DSR, DREQ1 is used, which remains high to pin 5 IC34, to prevent any further WD pulses reaching the DSR. WD(L) from IC34 pin 6 is inverted and combined with odd/even output from IC33 pin 13 to form WO or WE which control the DSR input multiplexers.

- 78. What happens between the end of one TV frame and the start of the next, is explained from a point near the end of a frame when WD goes low for the 502nd time. Just after WD's falling edge, the 501st data byte is written into the DSR. On AB4, WD's rising edge clocks the DMA Request Latch (DMARL) making DRQl go high. The DMA controller on AB3 sends some data bytes, and eventually resets the DMARL so that DRQl goes low again with byte 502 placed in B Demux Latch (BDML), IC44. The DMA controller has now reached the end of process on channel 1 and will not send further data until reset during the next FRAME period. As WD goes low for the 503rd time, data byte 503 enters the DSR, and DRQl goes high. It will remain so for the rest of the frame when the DMA controller becomes inactive. DRQl high to pin 5 of IC34 prevents any further WD pulses from reaching the DSR, and also means that data byte 502 is left undisturbed in BDML IC44.

79. When FRAME goes low, the DMARL on AB4 is reset and held so until the end of FRAME and so DRQl goes, and is held, low. This does not affect the DSR, however, because the WPG is also reset by FRAME to IC2 pins 2 and 4, and so no WD pulses are produced in this period. Sometime during FRAME, the DMA controller is re-initialized by part of the processor's frame interrupt Eventually, FRAME goes high again and the WPG is able to begin its routine. first count cycle during the first horizontal scan of the new TV frame. first cycle is of 258 states, and obviously the WPG will stop in its terminal count state as it receives only 257 6.25 MHz SHIFT REGISTER GATED CLOCKS during the scan. Thus WD is asserted and remains low, and WE holds the EVEN bank input multiplexers open, until the first clock edge of the second scan. At this point, data byte 502 is deposited in the final position of the EVEN bank, and since the WPG's first cycle is complete, WD goes high, thus setting the DMARL on AB4. The DMA controller now sends data byte 1 (for this frame) The WPG's next cycle has 257 states, but it has already to wait in the BDML. used one of the clocks of this (second) scan to complete the previous cycle. Therefore, another elongated WD pulse occurs, which, this time, results in the transfer of data byte No. 1 to the last position in the ODD bank on the first clock edge of the third scan. Simultaneously, DRQl goes high and the DMA controller soon sends data byte 2 to the BDML. The WPG now has a 258 state cycle again, with only 256 clocks of the present (third) scan left. Hence, terminal count does NOT coincide with the last clock edge of the scan, and a Orshort WD pulse occurs between the first and second clock edges of the fourth Data byte 2 is thus written into the first position of the EVEN bank. scan. Similarly, data byte 3 is written into position 1 of the ODD bank. This process continues until data byte 502 which concludes the sequence.

#### Circuit Sheet 2

80. On sheet 2 are seen the B channel Video Generator (BVG), which consists principally of the line draw and infill bright up operator, and the Line Count and Vertical Mask generator (LCVM). The vertical display mask, YVIDEN from IC40 pin 5 defines the top and bottom of the SDA. The LCVM consists mainly of a 9-bit ripple down counter formed by ICs 36 to 38 which is clocked by When VRTC is asserted low to IC37 pin 11, the counter is parallel-loaded with 273. After the trailing (rising) edge of VRTC, which coincides with the start of the TV picture, the counter first counts down to 250. This state is detected and LINE 250 goes low from IC39 pin 11 which sets Vertical Mask Latch (VML) IC40b. This causes YVIDEN to go high, and the top of the SDA is defined. The counter continues down to zero, at which point LINE 0 from IC38 pin 13 goes low resetting VML IC40, and so defining the bottom of the SDA, YVIDEN and XVIDEN are combined with Box by AND-gates IC3a and b to produce the Data Display Mask signal TOTAL DDM. The latter has two functions: to define the SDA Window within the TV picture, and to provide blank boxes around characters which appear within the SDA.

81. The current SDA scan line number (250...0) is extracted from the LCVM as the lower 8 output bits of the counter and passed to the B Data Comparator (BDC), ICs 7 and 8 on the HIGH SPEED B CHANNEL DATA lines. The rising edge of the 12.5 MHz PHASED CLOCK is taken to the clock inputs of ICs 23a and b forming the Current Ordinate Latches (COL), and used to latch in the greater than (>) and less than (<) decision signals from IC8 pins 5 and 7 respectively. Use of the clock ensures that the BDC has enough time to reach its decision, resynchronizes the less than and greater than decision signals and results in every data byte being displaced right by one ordinate position on the display. Compensation for this is made near the beginning of each horizontal scan across the SDA. While XVIDEN from IC15 pin 5 (see Sheet 1) is low and CLOCK EN from pin 8 is high, the DSR waits with display data byte 1

present at its output. Since the 12.5 MHz PHASED CLOCK does not stop, the BDSL is repeatedly loaded with data byte 1, and the COL receives the same decision from the BDC on every clock edge. Then, as soon as XVIDEN goes high, and CLOCK EN goes low, the BVG paints up data byte 1 in the first ordinate position. However, data byte 1 will now be clocked into the BDSL once in the normal way, and will, therefore, also appear in the second ordinate position (see above). After this, operation returns to normal, leaving data byte 1 as the only double ordinate.

82. The BVG uses the BDC decisions stored in the COL and Previous Ordinate Latches (POL), IC22, to create either line draw or infill type display video. However, line 250 (top line of the SDA) is a special case since this line must be lighted over those sections where data amplitude is greater than top of SDA. B display amplitude limiter IC21 ensures that this happens for line draw displays. The algorithms for the two types of display are shown in Table 2.

| Algorithm | COL                                                                    | POL                                    | 250(L) | video |

|-----------|------------------------------------------------------------------------|----------------------------------------|--------|-------|

| TMETT     | D / T                                                                  |                                        |        |       |

| INFILL    | D <l< td=""><td>X</td><td>X</td><td>off</td></l<>                      | X                                      | X      | off   |

|           | D>L                                                                    | x                                      | x      | on    |

|           | D=L                                                                    | x                                      | x      | on    |

|           |                                                                        |                                        |        |       |

| LINE DRAW | D <l< td=""><td><math>D \le = L</math></td><td>x</td><td>off</td></l<> | $D \le = L$                            | x      | off   |

|           | D>L                                                                    | D>=L                                   | 1      | off   |

|           | D>L                                                                    | D>=L                                   | 0      | on    |

|           | D <l< td=""><td>D&gt;L</td><td>x</td><td>on</td></l<>                  | D>L                                    | x      | on    |

|           | D>L                                                                    | D <l< td=""><td>x</td><td>on</td></l<> | x      | on    |

|           | D=L                                                                    | x                                      | x      | on    |

TABLE 2 DISPLAY ALGORITHMS - AB5

Where D is data, L is line number and X is don't care

#### Board AB6 - Graticule & A display dynamic store

Circuit diagrams: Chap. 7, Figs. 17 & 18

#### Shift registers and video generator

- 83. For a description of the A channel Display Shift Register (ADSR) on sheet 1, and the A channel Video Generator (AVG) on sheet 2, refer to the description of the identical circuits on AB5. Note that the shift register clocks,  $\Phi$ 1 and  $\Phi$ 2, have their pulse widths set locally (IC35a,b), so as to avoid sending these critical signals across motherboard AA1.

- 84. The Graticule Display Shift Register (GDSR), on sheet 1, is also very similar to the A and B DSR's, but is only half the length (257 locations instead of 514) and half the width (4-bit words instead of 8-bit) of the former. Its output data rate is half that of the larger DSR's too, which means that vertical graticule lines are always two ordinate positions wide on the TV screen. Graticule information destined for the GDSR is placed in the Grat Input Latch, IC37, under control of circuits on AB4, but the data itself comes directly from memory (by means of the DMA controller) without passing through AB4. Since the GDSR works at half the speed of the other two DSRs, it needs to have new data written in only half as frequently. For this

reason its input multiplexer, IC23, is controlled on pin 1 by Write Odd (WO) only.

#### Vertical graticule and marker generation

85. On sheet 2 the GDSR output is synchronized with that of the ADSR and BDSR by latching it in IC21, using the PHASED 12.5 MHz CLOCK as the latch control The latched 4-bit data is then split into marker and graticule to pin 9. information, and each is decoded to generate various effects on the TV screen. The 2-bit graticule data from pins 10 and 15 is decoded by IC20 so as to give one of four possible effects in any vertical graticule line position (see Dashed major lines are produced by combining the inverted output Table 3). of the decoder with a suitable line count bit. Dashed and normal major graticule lines are combined into MAJOR VERT GRAT by IC4a before being sent to The minor line output is inverted to form MINOR VERT GRAT to AB7. On AB7. AB7 these vertical graticule lines are combined with the horizontal graticule lines, and then sent to the video mixer.

| In  | put IC | 20   | IC2 | Out | put p | ins | 1                           |

|-----|--------|------|-----|-----|-------|-----|-----------------------------|

| Pin |        | in 3 | 4   | 5   | 6     | 7   | Effect selected             |

|     | L      | L    | Н   | Н   | Н     | L   | No graticule line (default) |

|     | L      | Н    | Н   | Н   | L     | Н   | Minor graticule line        |

|     | Н      | L    | Н   | L   | Н     | Н   | Major graticule line        |

|     | Н      | Н    | L   | Н   | Н     | Н   | Dashed major graticule line |

TABLE 3 VERTICAL GRATICULE DECODING - AB6

TABLE 4 IC7 MARKER DECODING - AB6

| I  | nput | pins |   | Ac | tive | out | put | pi | ns  |   | Effect and and a               |

|----|------|------|---|----|------|-----|-----|----|-----|---|--------------------------------|

| 13 | 3    | 1,15 | 9 | 10 | 11   | 12  | 7   | 6  | 5   | 4 | Effect selected                |

| L  | Х    | L    | L |    | L    |     |     |    |     |   | No marker                      |

| Н  | X    | Н    |   |    |      |     |     | L  |     | L | Steady marker, odd ordinate    |

| L  | X    | Н    |   |    |      |     | L   |    | L   |   | Steady marker, even ordinate   |

| Н  | Н    | L    |   |    | • 17 | L   |     |    |     |   | Flashing marker, odd ordinate  |

| H  | L    | L    |   | L  |      |     |     |    | , . |   | Flashing marker, even ordinate |

86. Three bit data is decoded by 3 to 8 line decoder IC7 which selects the required marker effect. A marker can appear in any ordinate position and sits at the data value for that ordinate. Markers however, are available on only one channel at a time. The five possible effects decoded by IC7 are shown in Table 4. To supply the flashing marker, IC8 is configured to divide the VRTC signal by 4 to produce a square wave of about 12 Hz from pin 9 to set

the FLASH RATE for the flashing marker signal. The odd/even flashing ordinate markers are produced by a combination of the logic on the ODD/EVEN FLASHING MARKERS line (low to select even coordinates) and the level on the GATED 6.25 MHz line (i.e. half the ordinate rate). By this means selected alternate markers are flashed at a 12 Hz rate. The MARKER signal from IC5 pin 8 is gated with A/B MKRS which selects the channel to which the markers refer, and with A= and B= which determine the vertical positioning of the markers on the TV screen. Marker data is then clocked out from D-latch IC40a synchronized to the PHASED 12.5 MHz CLOCK to provide the MKR VIDEO signal for the summer on AB7.