# HEWLETT-PACKARD

OCTOBER 1989

October 1989 Volume 40 . Number 5

#### Articles

- 6 40 Years of Chronicling Technical Achievement, by Charles L. Leath

- 4 A Modular Family of High-Performance Signal Generators, by Michael D. McNamee and David L. Platt

- Firmware Development for Modular Instrumentation, by Kerwin D. Kanago, Mark A. Stambaugh, and Brian D. Watkins

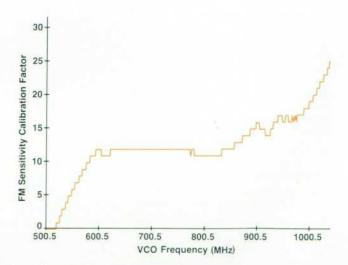

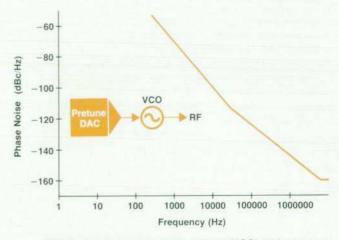

- 27 RF Signal Generator Single-Loop Frequency Synthesis, Phase Noise Reduction, and Frequency Modulation, by Brad E. Andersen and Earl C. Herleikson

- 28 Fractional-N Synthesis Module

- 30 Delay Line Discriminators and Frequency-Locked Loops

- 34 Design Considerations in a Fast Hopping Voltage-Controlled Oscillator, by Barton L. McJunkin and David M. Hoover

- 37 High-Spectral-Purity Frequency Synthesis in a Microwave Signal Generator, by James B. Summers and Douglas R. Snook

- 42 Microwave Signal Generator Output System Design, by Steve R. Fried, Keith L. Fries, and John M. Sims

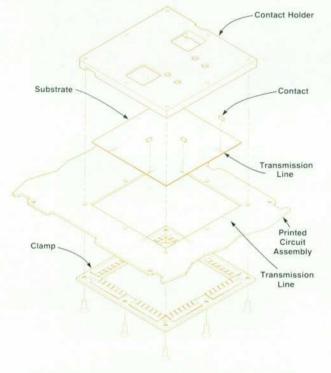

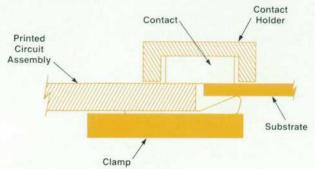

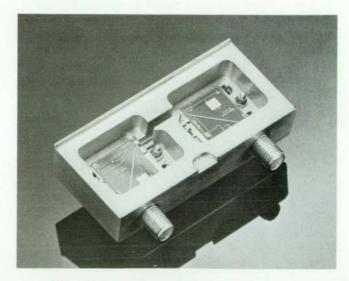

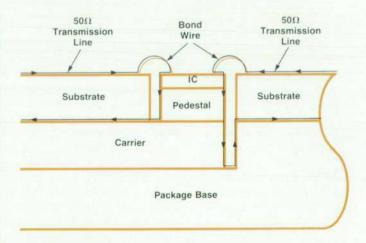

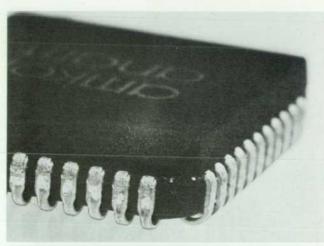

- 44 "Packageless Microcircuits"

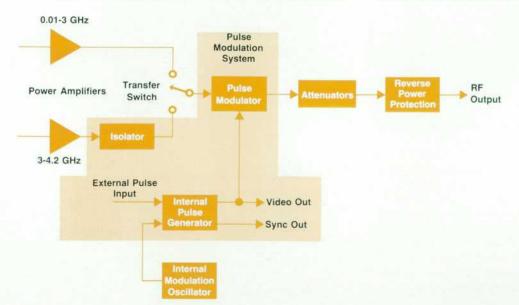

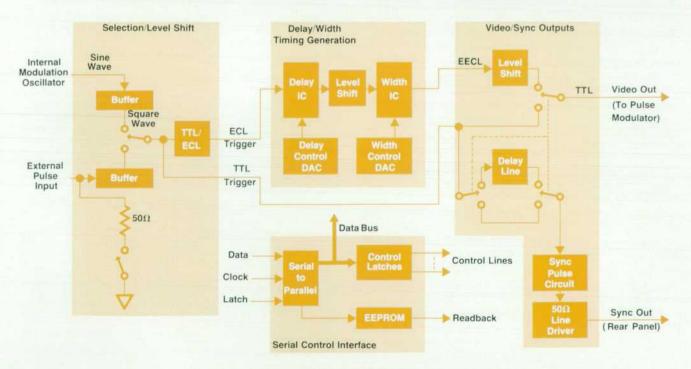

- Design of a High-Performance Pulse Modulation System, by Douglas R. Snook and G. Stephen Curtis

- Feducing Radiated Emissions in the Performance Signal Generator Family, by Larry R. Wright and Donald T. Borowski

Editor, Richard P. Dolan • Associate Editor, Charles L. Leath • Assistant Editor, Hans A. Toepfer • Art Director, Photographer, Arvid A. Danielson Support Supervisor, Susan E. Wright • Administrative Services, Typography, Anne S. LoPresti • European Production Supervisor, Sonja Wirth

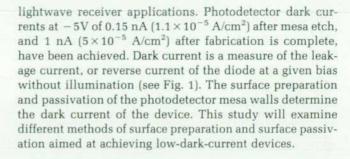

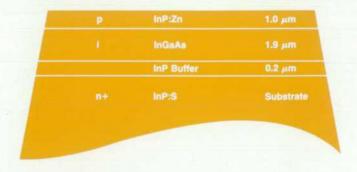

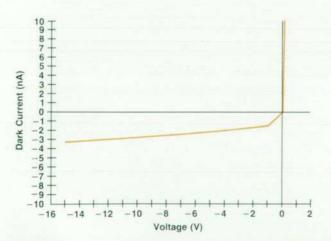

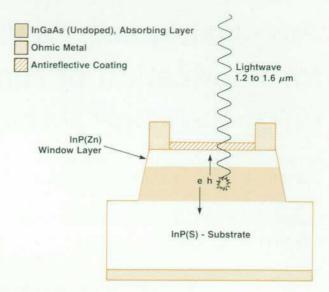

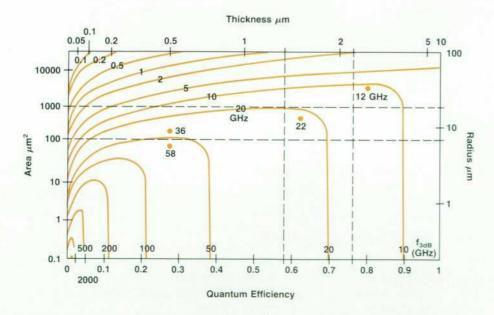

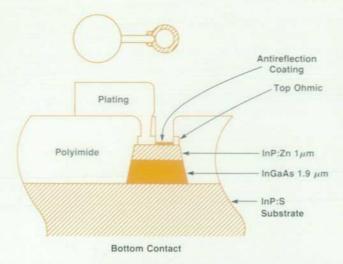

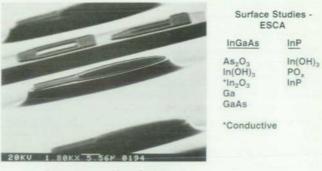

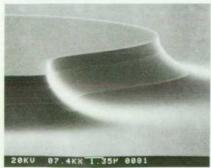

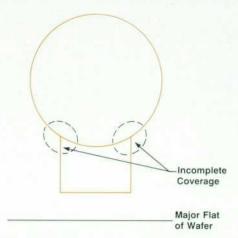

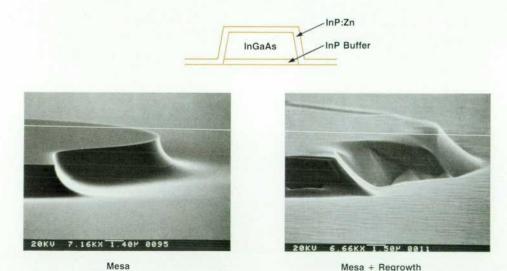

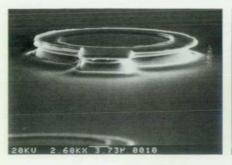

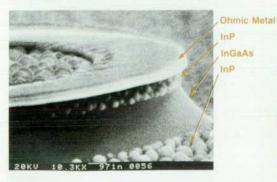

- Processing and Passivation Techniques for Fabrication of High-Speed InP/InGaAs/InP Mesa Photodetectors, by Susan R. Sloan

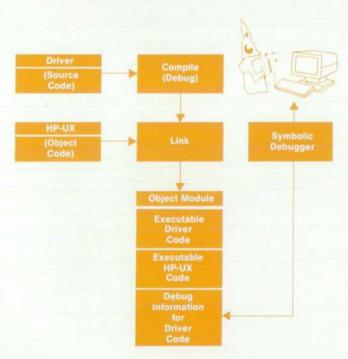

- 76 Providing Programmers with a Driver Debug Technique, by Eve M. Tanner

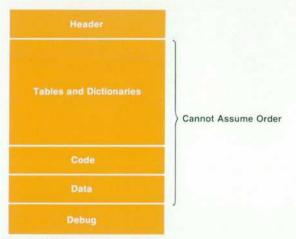

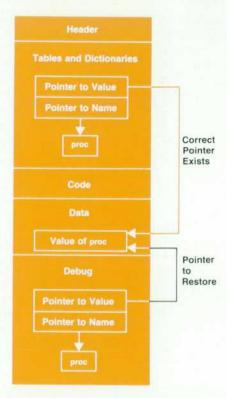

- 78 HP-UX Object Module Structure

- 79 Identifying Useful HP-UX Debug Records

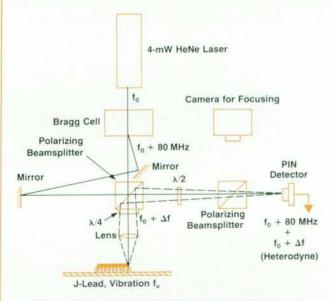

- Solder Joint Inspection Using Laser Doppler Vibrometry, by Catherine A. Keely

- 82 Laser Doppler Vibrometry

- 86 A Model for HP-UX Shared Libraries Using Shared Memory on HP Precision Architecture Computers, by Anastasia M. Martelli

- 90 User-Centered Application Definition: A Methodology and Case Study, by Lucy M. Berlin

- 92 Interviewing Techniques

- 95 Storyboarding Techniques

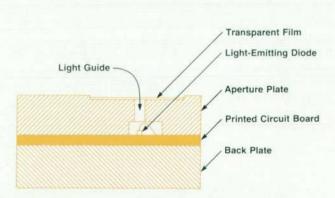

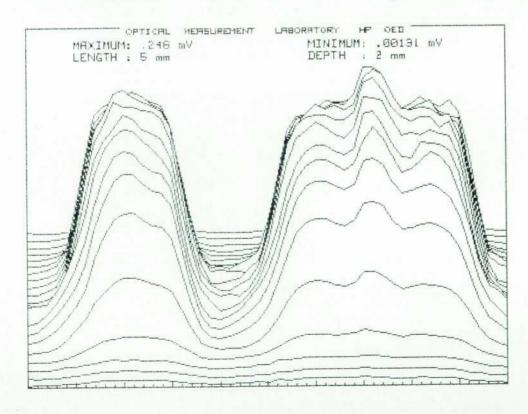

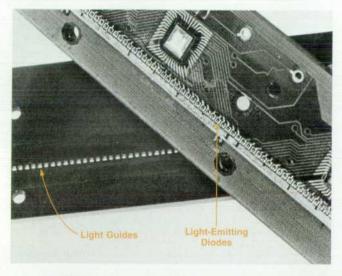

- 98 Partially Reflective Light Guides for Optoelectronics Applications, by Carolyn F. Jones

#### Departments

- 4 In this Issue

- 5 Cover

- 5 What's Ahead

- 66 Authors

- 85 Correction

#### In this Issue

The first issue of the *HP Journal* was published in September 1949, so this issue, October 1989, is the first of the *HP Journal*'s forty-first year of publication. (However, because of a 1978 change, Volume 41 doesn't begin until February 1990.) Coincidentally, the Hewlett-Packard Company is celebrating its fiftieth anniversary this year. To Associate Editor Chuck Leath, this double milestone—40 years of the *HP Journal* and 50 years of HP—fairly cried out for recognition, so he has assembled a special commemorative article to mark the occasion. The article, which begins on page 6, traces the development of HP technology as reported in the pages of the *HP Journal*.

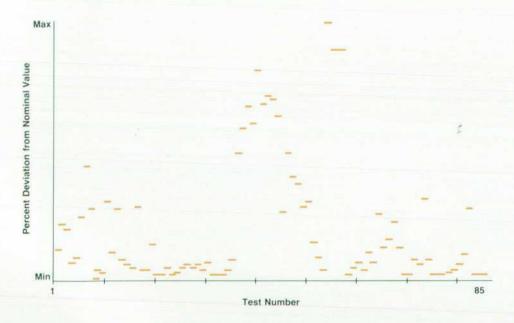

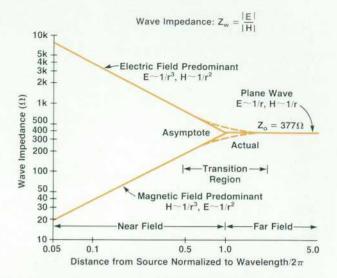

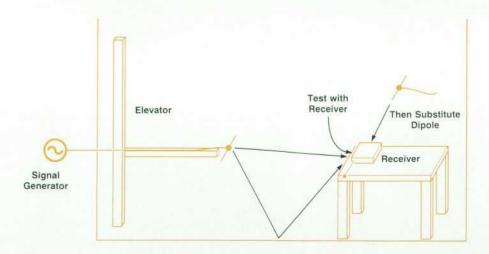

As signal generator designers at HP's Spokane Division saw things, general-purpose signal generators were delivering a lot of capability to the customer—so much, in fact, that few users needed all of it and were therefore paying for features they never used. On the other hand, offering a different product for each application could mean the loss of manufacturing economies and therefore higher prices. Their solution is a new family of internally modular signal generators. While options allow customers to buy only as much capability as they need, production economies are retained by using a lot of the same hardware and firmware in all of the members of the family. Called the Performance Signal Generators (PSG), the family includes the HP 8644A 1-GHz or 2-GHz Synthesized Signal Generator, the HP 8645A 1-GHz or 2-GHz Agile Signal Generator, and the HP 8665A 4.2-GHz Synthesized Signal Generator. The HP 8644A is designed with traditional out-of-channel transceiver test applications in mind, and the HP 8645A is focused on frequency agile transceiver testing. The HP 8665A is designed for radar, telemetry, spurious testing of UHF transceivers, and similar applications. On page 14, two PSG R&D project managers give an overview of the family and the basic design, which differs from previous microwave synthesized signal generators in that it uses only a single phase-locked loop instead of the multiple loops common in earlier designs. An advanced fractional divider makes the simplification possible. Supplementing the single-loop design are a new method of introducing frequency modulation and one or two optional frequency-locked loops for additional phase noise reduction. Details of the synthesis, FM, and noise reduction techniques are in the article on page 27. How fast frequency hopping, a capability of the HP 8645A, influenced its design is explained in the article on page 34. The articles on pages 37, 42, and 51 cover the design of the HP 8665A synthesis, output, and pulse modulation systems. Firmware design for the three instruments is treated in the article on page 20, and RFI (radio frequency interference) reduction is the subject of the article on page 59. A particularly simple and quick RFI test turns out to be one of the most difficult to pass—it consists of placing a pager next to the signal generator and noting whether it detects anything.

The **Hewlett-Packard Journal** is published bimonthly by the Hewlett-Packard Company to recognize technical contributions made by Hewlett-Packard (HP) personnel. While the information found in this publication is believed to be accurate, the Hewlett-Packard Company makes no warranties, express or implied, as to the accuracy or reliability of such information. The Hewlett-Packard Company disclaims all warranties of merchantability and fitness for a particular purpose and all obligations and liabilities for damages, including but not limited to indirect, special, or consequential damages, attorney's and expert's fees, and court costs, arising out of or in connection with this publication.

Subscriptions: The Hewlett-Packard Journal is distributed free of charge to HP research, design, and manufacturing engineering personnel, as well as to qualified non-HP individuals, libraries, and educational institutions. Please address subscription or change of address requests on printed letterhead (or include a business card) to the HP address on the back cover that is closest to you. When submitting a change of address, please include your zip or postal code and a copy of your old label.

Submissions: Although articles in the Hewlett-Packard Journal are primarily authored by HP employees, articles from non-HP authors dealing with HP-related research or solutions to technical problems made possible by using HP equipment are also considered for publication. Please contact the Editor before submitting such articles. Also, the Hewlett-Packard Journal encourages technical discussions of the topics presented in recent articles and may publish letters expected to be of interest to readers. Letters should be brief, and are subject to editing by HP.

Copyright © 1989 Hewlett-Packard Company. All rights reserved. Permission to copy without fee all or part of this publication is hereby granted provided that 1) the copies are not made, used, displayed, or distributed for commercial advantage; 2) the Hewlett-Packard Company copyright notice and the title of the publication and date appear on the copies; and 3) a notice stating that the copying is by permission of the Hewlett-Packard Company appears on the copies. Otherwise, no portion of this publication may be produced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage retrieval system without written permission of the Hewlett-Packard Company.

Please address inquiries, submissions, and requests to: Editor, Hewlett-Packard Journal, 3200 Hillview Avenue, Palo Alto, CA 94304, U.S.A.

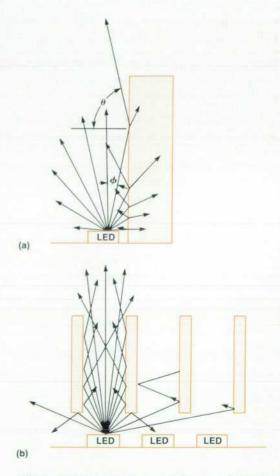

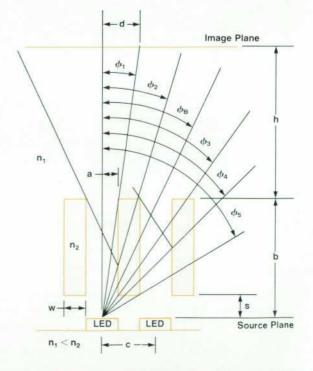

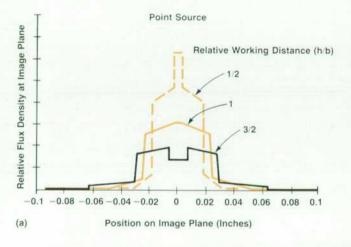

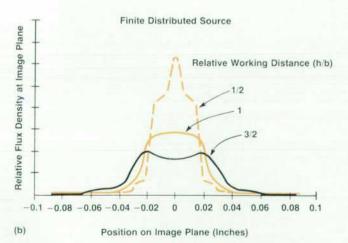

Hewlett-Packard's first Technical Women's Conference was held in October 1988. The conference was organized to showcase the achievements and contributions of technical women at HP and to promote their professional development into leadership roles. Approximately 400 HP women engineers and scientists and their managers attended the conference. Many section and Division managers participated as speakers and panel discussion leaders. Topics of the technical presentations included hardware, software, computers, instruments, manufacturing, components, and other subjects. Papers based on six of the presentations appear in this issue. On page 69, Susan Sloan of the Microwave Technology Division reports on work done to determine the best method of surface preparation and passivation for low-dark-current photodetectors for use in HP lightwave receivers. Among the requirements for these photodiodes are maximum dark currents of a few nanoamperes and good response to modulation frequencies beyond 22 GHz. On page 76, Eve Tanner of the Personal Computer group tells how a useful symbolic debugging capability can be given to programmers developing drivers to run under the HP-UX operating system when the HP-UX source code is not available. The technique takes advantage of available compiler information to insert HP-UX global data records into the user's file. On page 81, Cathy Keely of HP Laboratories describes an experimental laser-based method of finding bad solder joints on surface mount components. Vibrations induced in the leads by an air jet are detected and analyzed by laser Doppler vibrometry. On page 86, Stacy Martelli of the General Systems Division discusses a model for HP-UX shared libraries that was developed to provide shared library capability to users of a particular software package in the absence of operating system support for them. The model required only minor changes to the HP-UX linker. On page 90, Lucy Berlin of HP Laboratories describes a methodology for systematically acquiring and applying user information in the definition of software applications. Interviewing, task analysis, and storyboarding are key elements. On page 98, Carolyn Jones of the Optoelectronics Division discusses the design of light guides for an array of light-emitting diodes used for selective erasing in electrophotographic copiers. Well-defined spots of light have to be formed some distance away from the LEDs, which are one millimeter apart and emit light in all directions.

> R.P. Dolan Editor

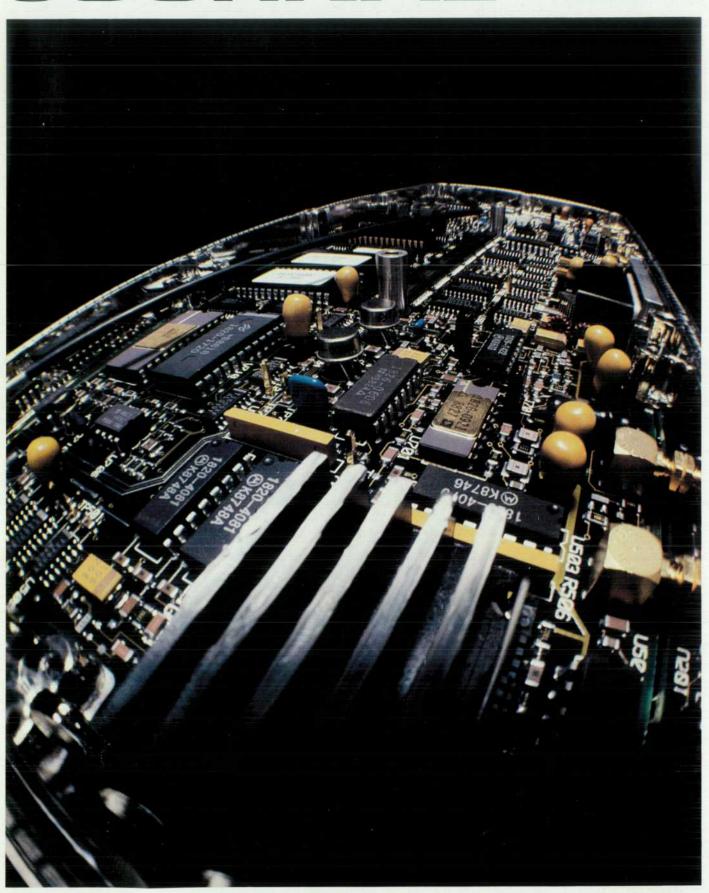

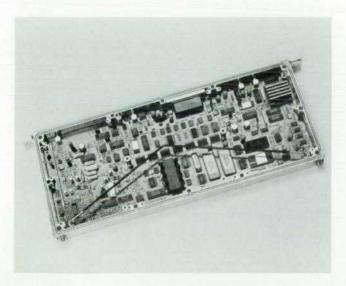

#### Cover

Not a space station from a science fiction film, but the fractional-N module from HP's Performance Signal Generator family. For a more conventional view, see Fig. 8 on page 19.

#### What's Ahead

The HP Starbase Graphics Library is a high-performance 2D and 3D graphics library that runs on HP 9000 Computers under the HP-UX operating system. In the December issue, six articles will describe the Starbase/X11 Merge System, which enables Starbase applications and X Window System applications to coexist in the same window system. There will be two papers on aspects of the HP 9000 Series 300/800 Turbo SRX graphics subsystem—one on the radiosity method of global illumination modeling and one on the custom VLSI chips used in the graphics pipeline. HP Source Reader, a CD-ROM system that gives HP support engineers fast access to HP 3000 Computer operating system source code, will be described. The December issue will also contain the 1989 Index.

### 40 Years of Chronicling Technical Achievement

Over the last 40 years the HP Journal has created a record of HP's technical achievements by communicating technical information to professional people in all fields served by HP. With Hewlett-Packard celebrating its 50th anniversary it seems appropriate to take a look at the HP Journal, past and present, and some of the technological history of Hewlett-Packard it has chronicled.

by Charles L. Leath

Associate Editor

HIS YEAR HEWLETT-PACKARD is celebrating its first fifty years as a company and coincidentally the HP Journal is in its 40th year of publication.

In September 1949, when the first issue of the HP Journal was published, HP had 150 employees, 70 electronic measurement instruments in the product catalog, and 2¼ million dollars in sales. Other significant technological events during this period were the invention of the transistor at Bell Laboratories in 1947 and the operation of the first supercomputer, the ENIAC, in 1946. Today HP has over 90,000 employees, over 10 billion dollars in sales, and over 10,000 products that appear or are alluded to in the HP product catalog. The HP product line today includes not only electronic measuring instruments, but also computer hardware and software systems, peripherals, medical electronic equipment, analytic instruments for chemical analysis, electronic components, and a host of other services and products.

The initial idea for the HP Journal came from a periodical called the General Radio Experimenter. General Radio, now known as GenRad, produced primarily electronic measurement instrumentation, and the Experimenter was a monthly publication devoted to supplying "unbiased information pertaining to radio apparatus design and application."1 The Experimenter started publishing in 1926 (11 years after the founding of General Radio) and was the first periodical of its type in the radio industry. It was distributed free of charge to qualified experimenters and it was a popular periodical in the industry. Many HP engineers were devoted readers of the Experimenter. One of those readers, David Packard, was impressed with the quality of the articles and thought that HP should have something similar. This idea turned into reality when Frank Burkhard, the first HP Journal editor, was assigned the task of creating HP's version of the Experimenter. There was some consideration given to calling the Journal the HP Experimenter. However, after examining periodicals from other companies (e.g., the Bell System Technical Journal) the name HP Journal stuck.

Although one of the initial objectives for the Journal was to produce a periodical similar to the General Radio Experimenter, other objectives included telling customers about HP products and their applications, showing the quality and workmanship that went into each product, and giving credit to the product designers. The Experimenter also included information about the product designers. Like HP's corporate objectives, the Journal's original objectives have been expanded and clarified. Today the HP Journal is a periodical for the communication of technical information from all of HP's R&D, manufacturing, and quality organizations

to professional people in all fields served by HP.

When this issue (Volume 40 Number 5) is printed there will have been 466 issues of the HP Journal. Since the late 1950s the HP Journal has been a monthly publication, and in December 1987 it became bimonthly. When the HP Journal started, it was circulated only in the continental U.S.A. Today the HP Journal's circulation includes subscribers all over the world. Up until the late 1950s the HP Journal averaged four to six pages per issue, and today it averages around 90 pages per issue.

#### First Journal

The first HP Journal featured the HP 460A, a wideband noninverting amplifier whose main features included distortionless pulse amplification with a very short rise time (3 ns) and almost zero overshoot, a frequency range of 3 kHz to 140 kHz, a gain of 20 dB into a 200 $\Omega$  load, and a weight of 10 pounds. The rise time was pretty good even by today's standards. The HP 460A was used in situations where it was necessary to amplify pulses faster than 0.01  $\mu s$ . Application areas included nuclear research and television, VHF, UHF, and SHF (superhigh-frequency or microwave) research. It was also used as a preamplifier for oscilloscopes and to increase the sensitivity of voltmeters. The original cost of the HP 460A was \$185.00, and when it was discontinued in 1967 it cost \$285.00. Fig. 1 shows a reduced reprint of this first HP Journal issue.

In 1964, the year HP celebrated its 25th anniversary and the HP Journal was up to eight pages per issue, two broadband, solid-state versions of the HP 460A were introduced, the HP 461A and HP 462A (March 1964).\* The HP 461A was optimized for a flat frequency response over a wide bandwidth, and the HP 462A was similar to the HP 461A, but had a smaller bandwidth and was optimized for a fast rise time (less than 4 ns) with an overshoot of less than 5%. These amplifiers could be cascaded with the HP 460 Series broadband amplifiers for high-voltage applications by using a  $50\Omega\text{-to-}200\Omega$  matching transformer. The HP 461A had a frequency range of 1 kHz to 150 kHz, a maximum gain of 40 dB operating into a  $50\Omega$  load, and a weight of four pounds. It cost \$325.00.

Today the performance characteristics of the HP 460 and 461 Series amplifiers are achieved and exceeded in thick-film hybrid circuits and HP amplifiers. For example, the HP 8449A Preamplifier, which is used in RF and microwave applications, is programmable and has up to 28 dB of gain at 22 GHz. There are also pulse

\*The month and year in parentheses indicate the Journal issue in which the referenced article or topic appears.

Generator, which can produce pulses with widths less than 0.5 ns, rise and fall times less than 200 ps, and frequencies to 500 MHz.

#### After Vol. 1 No. 1

HP Journal articles have covered everything from products and applications to tutorials and research topics. Many of the application articles showed the practical and diverse uses of HP products. For example, the October 1957 issue included a supplement that described the use of an HP counter and digital recorder to capture transmissions from the Russian earth satellite Sputnik. One of the more international applications appeared in the July 1964 issue which described the "Flying Clock" experiment, in which the HP

5060A Cesium-Beam Frequency Standard was used to compare time standards in the U.S.A. and Europe and the results were used by the official agencies of the two continents to improve their time synchronization. This same product was later used in a test of Einstein's relativity theory. Although applications, tutorials, and other items populated the Journal pages, new product designs dominated the Journal articles.

In 1983 reprints of articles from 32 HP Journal issues were bound together in a book called *Inventions of Opportunity*. The articles included in the book were chosen because they described products or innovations that represented important milestones in the technological history of the Hewlett-Packard Company. The selec-

Fig. 1. The first issue of the HP Journal.

Fig. 2. (a) Nov. 1949. This issue is the first of a two-part series describing design issues related to the resistance-capacity oscillator. (b) June 1951. The Journal issue describing the HP 202A Low-Frequency Function Generator. This instrument had a frequency range of 0.01 Hz to 1 kHz. (c) Nov. 1965. This issue describes a successor to the HP 202A, the HP 3300A Low-Frequency Function Generator. The basic instrument provided sine, square, and triangular waves

throughout a frequency range of 0.01 Hz to 100 kHz. The Journal cover shows some of the waveforms that could be generated with this instrument.

tion committee consisted of 20 or more individuals who had been with HP for a long time and who had a broad perspective on the technological history of HP. The collection begins with the resistance-capacity oscillator (November 1949) and ends with an article on a new plotting technology (October 1981). Bill Hewlett wrote the introduction, describing the history behind each of the products included in the book.

What follows is a synopsis of some of the Journal issues and technical areas covered in *Inventions of Opportunity*, and of some significant *Journal* issues published since October 1981. The discussion also shows what has happened to a particular product line since it first appeared in the pages of the *Journal*. Because of space limitations we can only show the front covers of the *Journal* issues being discussed, but these covers are interesting in themselves, because in addition to showing the product or something about it, they also show the changes in the style of the *Journal* over the years.

#### Signal Sources

Many of the HP Journal issues in 1949 described products that had been developed years earlier. The most famous of these products was the resistance-capacity oscillator, HP's first product. The RC oscillator had been introduced ten years before the Journal article. These two issues discussed the problems that had to be overcome in designing these instruments, such as extending the low and high frequency ranges with the components available at the time. Fig. 2a shows the first of these two issues.

Although HP had oscillators that operated as low as 1 Hz, there were needs for much lower-frequency sources. A technical paper from a student contest sponsored by the the San Francisco section of the IRE (predecessor to the IEEE) in 1950 described a technique for extending the range of an oscillator to very low frequencies. The rights to the technique were acquired from the student and his professor and very shortly HP developed the HP 202A Low Frequency Function Generator. This generator also had the ability to produce triangular and square waveform shapes—a big deal at the time. See Fig. 2b.

Today, signal sources are usually frequency synthesizers. The first synthesizer produced by HP, the HP 5100A/5110A Frequency Synthesizer (see Fig. 3), could generate high-stability signals from 0.01 Hz to 50 MHz. It used a direct synthesis approach. Direct synthesis involves performing a series of arithmetic operations on a signal from a frequency standard to achieve the desired output frequency. In today's synthesizers, indirect synthesis, which involves deriving the signal from one or more oscillators phaselocked to a reference source, is used. The development of the HP 5100A/5110A instrument was the first time HP had made such a

major commitment to a new technology—the project required almost 40-engineer-years of development effort spread over a period of about three years.<sup>3</sup>

#### Microwave Equipment

During World War II, development of microwave systems was quite intensive. However, after the war many companies dropped much of their microwave work. HP continued to develop microwave equipment including such items as detectors, standing-wave indicators, directional couplers, waveguides, and so on, "all with the aim of simplifying measurement in this very difficult field." Microwave products were so pervasive in the early days that out of 24 HP Journal articles between September 1950 and September 1952, half were devoted to microwave equipment. The Journal cover shown in Fig. 4a does not represent a significant product, but it is representative of the type of Journal issues published at the time that covered microwave equipment.

Today with new technologies, HP continues to develop microwave components, signal sources, and measurement instruments.

Fig. 3. (a) May 1964. This issue described the HP 5100Al 5110A Frequency Synthesizer. The unit with all the buttons (top unit) is the HP 5100A Synthesizer and the unit on the bottom is the HP 5110A Synthesizer Driver. The driver unit contains the frequency standard. (b) May 1983. This issue describes a product that shows where we were in 1983 with regard to frequency synthesis techniques. The HP 8673A Synthesized Signal Generator, which has a frequency range of 2 to 26.6 GHz, is featured.

Fig. 4. (a) Feb. 1951. This issue explained HP's program in 1951 regarding microwave waveguide equipment, and it is typical of the many Journal issues at the time that featured microwave equipment. Among the waveguides discussed in this issue, the one with highest range went to 18 GHz, or 18 kilomegacycles in the vernacular of the time. (b) Nov. 1986. This Journal cover shows four HP 11970 Series waveguide harmonic mixers. Three of them have their own horn antennas which come in different sizes for operation in different frequency bands.

One of the best examples of these efforts is the HP 11970 Series of waveguide harmonic mixers described in the HP Journal issue shown Fig. 4b. This issue describes the efforts by HP Laboratories and the HP Microwave Technology Division to develop small-scale integrated and hybrid circuits that operate at 100 GHz and beyond. Electromagnetic energy in the frequency range of 26 to 300 gigahertz is called millimeter waves.

#### Counters

The first high-speed frequency counter, the HP 524A, was developed in 1951. It revolutionized the measurement of unknown frequencies. At the time, frequency measurement required three separate pieces of equipment—a frequency standard, an interpolating system, and a detector. The technology for the HP 524A came from an instrument called a scaler, a frequency-dividing instru-

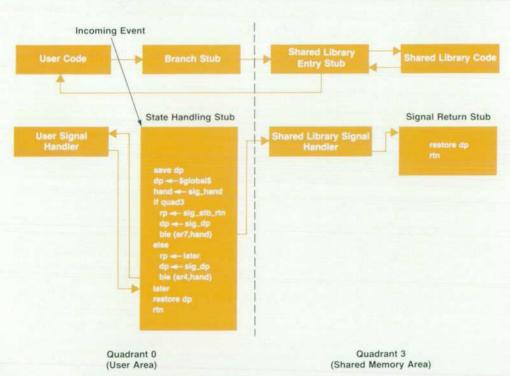

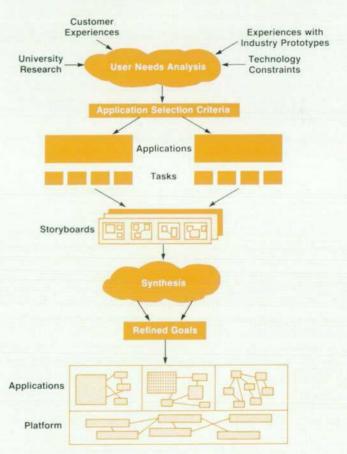

ment capable of dividing quantities of pulses by an arbitrary factor, usually 10° or 2°. The HP 520A, a 10-MHz scaler that provided the technology for the HP 524A, consisted of two decades, giving a scaling factor of one hundred, so that for every 100 pulses applied to the scaler a single output pulse was generated. This scaler was intended for the nuclear instrumentation market. Conventional scalers at the time operated to about 100,000 counts per second. The HP 520A could be used as a prescaler that could accept count rates as high as 10 million counts per second and scale them down by a factor of 100 to be fed into conventional scalers. The HP 520A was successfully developed, but the need for it never materialized. 5

The technology of the HP 520A was combined with a very accurate time gate circuit to produce the HP 524A. The complete counting circuit for the HP 524A consisted of eight cascaded scalers. All the scalers generated one output pulse for every ten counts. The first two scalers produced their counts on a panel meter and the remaining six displayed their counts in neon lights.

With more functionality and greater capabilities provided by firmware and new circuit technologies, counter technology has come a long way since the HP 524A as evidenced by the descendants described in the HP Journal issues shown in Fig. 5.

#### Oscilloscopes

Technical innovation is not always the result of a major technological breakthrough. Sometimes it is simply the application of old or existing concepts in different ways and possibly with new technologies. The HP 185A/187A Sampling Oscilloscope was just such an example of using an existing concept. The concept was waveform sampling, a technique that had been used earlier in the power generation field to measure the waveform of an alternator. The technique had proven to be applicable to very highspeed signals, and the HP 185A/187A was the first practical application of this concept to measuring periodically recurring waveforms. In the instrument, the sampling technique used a stroboscopic approach to reconstruct the input waveform. In reconstructing the waveform, the sampling circuit was turned on for a very short interval. The waveform voltage at that instant was measured and the CRT spot was positioned to correspond to the sampled amplitude. This process was repeated on the next cycle of the waveform except at a later point than the first sample. Continuing in this way the sampling scope reconstructed the entire

Fig. 5. (a) Jan. 1951. This issue describes the HP 524A High-Speed Frequency Counter. The counter provided frequency measurement up to 10 MHz and five selectable sampling periods: 0.001, 0.01, 0.1, 1.0, and 10.0 seconds. (b) July 1975. The HP 5328A Universal Counter has a direct count frequency range of 100 MHz (512 MHz with a special option), a period resolution of 100 ns (10 ns with a special module), and other functions such as time inter-

val averaging, totalize, ratio, and so on. The HP Journal cover shows the counter's optional modules superimposed on a background showing the counter's interior. (c) Feb. 1989. The latest contribution to frequency and time measurement, the HP 5371A Frequency and Time Interval Analyzer. The cover shows a sculpture in plastic of the circuit diagram of a zero-dead-time counter, a key component in the HP 5371A. The HP 5371A uses a method known as continuous measurement technology. The zero-dead-time counters implemented with high-speed integrated circuits make one measurement after another without stopping. Like the HP 524A, this instrument has also made it easier to make certain frequency and timing measurements that were formerly difficult or impossible.

Fig. 6. (a) March 1960. This Journal issue describes the HP 185A/187A Oscilloscope. Also in this issue is an article describing the phenomenon of reverse conducting diodes and how the new sampling scope was used to observe this phenomenon. (b) April 1986. This Journal issue describes the HP 54100A/D and HP 54111D Digitizing Oscilloscopes. The cover shows the display of the HP 54110D, and in front of the display are the seven hybrid circuits used in each instrument.

input waveform.

At the time the sampling scope was produced, most scopes had a top frequency of 50 to 100 MHz. The sampling technology enabled the HP 185A/187A to provide a 500-MHz upper limit. Sampling technology was also applied to other instruments such as the HP 8405A RF Vector Voltmeter (May 1966), the HP 3406A Voltmeter (July 1966), and the sampling plug-ins for the HP 140A and 141A oscilloscopes (October 1966). The latter had a range of dc to 12.4 GHz.

Today we have digitizing oscilloscopes that still employ the waveform sampling concept but use more advanced technologies and digital techniques to operate on the signal as opposed to pure analog signal processing in the older scopes. The HP 54100A and 54110D Digitizing Oscilloscopes (Fig. 6b) are the best examples of these new oscilloscopes. These scopes have capabilities such as a 1-GHz range and a 350-picosecond rise time (4 nanoseconds for the the HP 185A/187A oscilloscopes). These digitizing scopes use a sampling technique that reconstructs the input signal from a series of samples taken at random points on the waveform.

#### Computation

It is probably a gross understatement to say that the field of computation, which includes calculators, computers, peripherals, and associated technologies, has gone through some dramatic changes since the days of the ENIAC. The ENIAC computer, which began operation in 1946, weighed 30 tons, consumed 150 kW, contained 18,000 vacuum tubes, and could perform 400 multiplications or 5,000 additions per second. Contrast this with one HP Precision Architecture NMOS-III single-chip CPU, which contains 115,000 transistors packed onto a square die measuring 8.4 mm on a side, weighing just a few ounces and consuming less than 12 watts in a pin-grid array package, and capable of executing 7 MIPS (million instructions per second). This may seem like comparing an elephant to an ant. However, it does illustrate how far this field has come in a little over 40 years.

Before the introduction of the HP 3000 Computer in 1973, HP was regarded as strictly an instrumentation company. Today computation products make up over 60% of HP's sales and orders. This change has been reflected in the pages of the HP Journal. For instance, in 1970, out of 25 articles, only five articles or 20% featured something about computation products, whereas in 1980,

out of 83 articles, 31 articles or 37% featured computation products.

Although HP's computer products also include all the peripheral items that go with a computer, such as terminals, printers, disk drives, and different types of input devices, this section will focus only on computers and calculators. Since computers are worthless without software, a section on software is also included.

#### Calculators

The story of HP's entry into the calculator business started in 1965 with the development of the HP 9100A Calculator. Four ingredients helped to pull this product together. The first ingredient was the product of a young inventor who had perfected a simple calculator using reverse Polish notation. At about the same time another inventor brought to the attention of HP management another prototype calculator that could calculate transcendental functions-this was the second ingredient. The third ingredient was the recognition that these two inventions could be brought together to build a powerful calculator. The last important ingredient was the availability of a project already under way at HP to develop a read-only memory (ROM). This ROM, which was composed of 32,267 bits, was eventually used to store all the calculating and display routines for the HP 9100A. Two major problems had to be overcome by the HP 9100A development team. The first was packing eight circuit boards (remember the read/write memory was magnetic core and the control logic diode-resistor logic), a power supply, a CRT, a magnetic card reader, and a keyboard into a package 81/4 inches high, 16 inches wide, and 19 inches deep. For the technology available at the time this was quite a challenge. The second major challenge was compressing 27 floating-point arithmetic operations and functional computations into 4K bytes of ROM. This is quite an accomplishment when you consider that software engineers today consider it a challenge to fit a simple application into 1 Mbyte of memory.

The HP 9100A was a very easy to use, programmable calculator that had 196 program steps, 27 single-keystroke mathematical operations including trigonometric and logarithmic operations, and instructions and constants for repetitive operations. Single-keystroke computation is not a big deal today; in fact, we take it for granted, but before the HP 9100A, to do anything more than a simple addition or subtraction was a multistep, error-prone process.

The successor to the HP 9100A, the HP-35, the first handheld scientific calculator, turned out to be one of the most successful products ever introduced by HP. Fig. 7b shows the HP Journal

Fig. 7. (a) Sept. 1968. This entire issue was devoted to the HP 9100A Calculator. The cover shows the final test area for the calculator. The price for the HP 9100A was \$4900.00. (b) June 1972. The HP Journal issue describing the HP-35. The HP-35 cost \$395 at introduction.

Fig. 8. (a) March 1967. The issue describing the HP 2116A Computer. The cover shows some of the integrated circuits used in the computer. The machine could handle up to 32K bytes of magnetic core memory with a 1.6-μs cycle time. The HP 2116A also came with a software package that included a Fortran compiler, an assembler, a symbolic editor, and a basic control system (a very primitive operating system). (b) Oct. 1971. The cover shows a

mockup of the front-panel buttons of the HP 2100A Computer, and inside the plastic box are two boards containing the microprocessor, which was the heart of the machine. The machine contained a special emulator to emulate the earlier HP 2116A Computer. The instruction set for the HP 2100A was decoded and executed partly in hardware and partly in firmware. This meant that the basic instruction set could be expanded without new hardware. The machine still used magnetic core memory that had a 980 ns cycle time. (c) Oct. 1978. The HP 1000 system, which was introduced in 1976, was based on a successor to the HP 2116A, the HP 21MX Computer. The HP 1000 provided a complete package—computer system, a set of standard computer peripherals, the RTE-IV operating system, and other software. The display shows the output of a utility that monitored the activities of the RTE-IV operating system. The HP 21MX F-Series machine had a system cycle time of 420 ns and a maximum memory size of 1280K bytes in the mainframe. The memory technology was semiconductor dynamic RAM.

issue that described the HP-35. The HP-35 provided 17 arithmetic, trigonometric, and logarithmic functions, and functions for data storage and positioning. It was battery-powered, weighed nine ounces, was small enough to fit in a shirt pocket, and computed answers to 10 significant digits. At the time the development of the HP-35 began, it was estimated that if 10,000 units could be sold in the first year the program would be a success. HP sold over 100,000 units the first year. The HP-35 completely supplanted the major computational device for engineers and scientists, the slide rule.

#### Computers

HP's involvement in the computer business also started in 1965 with a minicomputer project at HP Laboratories and a young engineer with a PhD in computer science (a rare degree in 1965). HP Laboratories carried the research far enough to demonstrate the feasibility of the project, and because of customers' increasing demands for automated testing, the project was given the go-ahead. At the time there was a separate HP organization called Dymec that was responsible for doing work related to automated testing, so the responsibility for computer development was transferred from HP Laboratories to Dymec.

HP 2116A. The minicomputer project at Dymec produced HP's first computer, the HP 2116A, in November 1966 (see Fig. 8). Emphasis was placed on the fact that HP was not in the computer business, but that the HP 2116A was intended for instrument automation. Since the machine was intended for instrument automation it was ruggedized to operate under the same environmental conditions as HP's instruments. This gave the HP 2116A a good reputation for reliability.

One of these early automated system applications was the HP 8542A Automatic Network Analyzer (February 1970). The HP 8542A was a combination of microwave test equipment and a computer that was used for characterizing RF and microwave devices. The system was configured either with an HP 2114B or an HP 2116B, two descendants of the HP 2116A. This system demonstrated the advantages of connecting a collection of instruments to a computer specially tailored for instruments.

Despite the emphasis on using the HP 2116A for instrumentation

systems, one of its early successors, the HP 2116B, was used to build a time-sharing system. The system was called the Hewlett-Packard Model 2000A Time-Shared BASIC System (July 1968), and was capable of handling 16 users at once. The terminals were teletypewriters and a special teleprinter multiplex card occupied one I/O slot in the host computer to service all sixteen terminals. For direct connection, the system could handle terminals up to one mile away, and for longer distances voice-grade telephone coupling equipment was used. One interesting application of this system was computer-assisted instruction (CAI) (February 1971). The HP/CAI system used an HP 2000B system that could handle up to 32 users. The system provided mathematics drills and practice programs for elementary school children.

The HP 2116A eventually evolved into the HP 2100A (see Fig. 8b), the 21MX, the HP 1000 (see Fig. 8c), and today the HP 1000 A-Series machines (February 1984). These systems continue to be used for real-time applications, such as automatic test systems and data acquisition and control systems.

HP 3000. In 1972 HP introduced its first small general-purpose computer system, the HP 3000 (see Fig. 9). The HP 3000 was a significant milestone because it was HP's first entry into the busi-

Fig. 9. Jan. 1973. This is not an organist in concert, but a system administrator sitting at the system console for the HP 3000 Computer System. On the table on each side are control panels used for system maintenance and system checkout. In the background is the HP 3000 and some of the peripherals typically connected to the system (card reader, cartridge disk, paper tape reader and punch, and so on).

Fig. 10. (a) Aug. 1985. This was the first of a series of Journal issues covering HP Precision Architecture. This particular issue introduced the major design principles associated with HP Precision Architecture. There is a discussion of the genealogy of computer architectures from von Neumann to HP Precision Architecture. (b) Sept. 1987. This issue describes the NMOS-III implementation of HP Precision Architecture computers. The cover shows the processor boards for the HP 9000 Model 825 and the HP 9000 Model 850S/HP 3000 Series 950, and an unmounted pin-grid array package housing an NMOS-III VLSI chip.

ness computer market, and it was a major change from HP's traditional electronic test and measurement instrumentation business. The HP 3000 was also HP's first truly integrated software and hardware design. Unlike many computers of the past, it was not built by hardware engineers and then turned over to the software engineers to see what they they could do with it—it had the total involvement of both teams in the design. The HP 3000 had features that in the early 1970s were only found in large mainframes, including:

- A hardware stack architecture and virtual memory

- Separation of code and data

- Automatic relocation of programs and data

- Reentrancy to permit code sharing

- Recursion to allow a routine to call itself.

The operating system for this machine, the HP 3000 MPE (Multiprogramming Executive) provided time-sharing and batch processing concurrently. The MPE operating system has evolved into MPE XL, which runs on the new HP Precision Architecture machines.

HP Precision Architecture. HP's Precision Architecture is still technological history in the making. Research on the architecture started in 1981 and was known within HP as the Spectrum program (see Fig. 10a). It was the largest development program ever undertaken by HP. HP Precision Architecture fits loosely within the class known as reduced instruction set computers, or RISCs, and it takes full advantage of VLSI and new software technologies. It does not, however, depend on any particular circuit technology, so instead of being rendered obsolete by the inevitable development of new circuit technologies in the future, it allows designers to exploit new technologies for increased performance gains.

The first systems with the new architecture were introduced in 1986 and included the HP 9000 Model 840 technical computer and the HP 3000 Series 930 commercial system. The Model 840 ran the HP-UX operating system and the Series 930 ran the MPE XL operating system. Both systems used the same processor which is based on a relatively old-fashioned integrated circuit technology, TTL, and yet achieves an average performance rating of 4.5 MIPS, about four times that of the fastest of HP's previous-generation

machines. In 1987 two more HP Precision Architecture systems (the HP 3000 Series 950 and HP 9000 Model 850S) were introduced, using HP's proprietary NMOS-III integrated circuit technology (see Fig. 10b). The system processing units, or SPUs, in both systems are the same. These systems verified the point that HP Precision Architecture is portable over different integrated circuit technologies. The VLSI development involved 12 chips with up to 150 thousand transistors per chip and was the largest multichip VLSI project HP has undertaken to date.

The saga of HP Precision Architecture computers continues with higher performance being achieved with faster VLSI parts, bigger caches, floating-point coprocessors, and other enhancements. For instance, one of the latest versions, the system processing unit for the HP 3000 Series 935 and the HP 9000 Model 835, has been benchmarked at 14 MIPS (June 1989).

#### Software

Software today is like the knobs and dials on instruments. It is expected to be there and provide the human interface to the machine. At the time HP started to develop and produce computers (1966), most work in computers at the time focused on commercial and business applications and special-purpose machines for military applications. There were, however, many innovative concepts in use and being developed. For example, the technique of virtual memory was being developed to get around the problem of limited core memory space, and high-level languages such as Fortran, BASIC, and Algol were beginning to be accepted as standards for interfacing to computers.

Since the HP 2116A was strictly intended as an instrumentation computer all of the software development was focused on making it easy for the machine to communicate effectively with instruments. As a result, many of the early Journal articles on software were about software for automatic test and measurement systems (see Fig. 11a). With the introduction of the HP 3000 Computer

Fig. 11. (a) Nov. 1968. The first HP Journal article in which a software product made the front cover and where a software product filled half of the issue. HP's motivation for developing a BASIC (Beginner's All-purpose Symbolic Instruction Code) compiler grew out of the need to provide HP 2116A users with a simple interface to the machine for writing programs for automatic testing. The project started in May 1967 with the goal of developing a single-terminal BASIC compiler to run on any HP computer having at least 8K bytes of core memory and an ASR-33 teletypewriter. (b) July 1974. This issue contained an article on the HP Image/3000 Data Base Management System. The images on the head are supposed to represent information that must be organized, made readily available to those who need it, and protected from those who don't—capabilities inherent in Image.

System, HP was officially in the computer business and therefore in the software business (see Fig. 11b). One software product, the HP Image/3000 Data Base Management System, was rated the best in its class for three consecutive years by Datapro International (see Fig. 11c).

Today at HP, software design and development occupy the same level of importance as many hardware developments of the past. One area where this is noticeable is in instrument design and development. Since the introduction of microprocessors into instruments, firmware routines have added a large amount of functionality to instruments and in some cases replaced some functions formerly performed in hardware. As a result, almost every new instrument development has a complement of hardware and software design engineers working in parallel to develop an instrument. The synergism between hardware and software engineers was evident in the development of HP Precision Architecture discussed earlier.

Journal pages for the last five or six years have reflected the increasing importance of software in HP. In some cases over half an issue has been devoted to software products and research efforts.

#### Components

In the mid-1950s HP established a semiconductor operation to design and produce special-purpose diodes for use in instruments. Commercial diodes, although less expensive, did not have the performance required for HP instruments. To gain a foothold in the rapidly emerging field of semiconductors, a subsidiary called HP Associates was founded in 1961. The purpose of this organization was to perform research, development, and manufacturing in the semiconductor field (see Fig. 12). Today there are many entities within HP doing this type of work. The components produced by these organizations form the cornerstone of many HP products—from instruments to computers (see Fig. 13).

Fig. 12. (a) Dec. 1965. The cover shows the energy diagram for a Schottky barrier. This issue describes the hot-carrier diode, a device that was used as a very fast detector, as a microwave mixer, and as a switch. Hot-carrier diodes were distinguished from conventional semiconductors at the time in that the junction consisted of a metal and a semiconductor rather than two semiconductors. (b) Feb. 1969. The cover shows the HP Model 5082-7000 Numeric Indicator, a small, low-power, all-semiconductor module, which used four-line binary-coded-decimal input signals to display digits 0 through 9 as an array of brightly glowing red dots. Each red dot is a GaAsP light-emitting diode. Today one can get LEDs in other colors besides red, and the new red AlGaAs LEDs (August 1988) are bright enough to be considered for such applications as light bulbs in automotive tail lights, airport markers, and traffic signals.

In instruments, special thin-film and thick-film hybrid packages containing such things as amplifiers and samplers are used to lower costs and improve performance. Likewise, in computer products, VLSI (very large-scale integration) circuits implement fast floating-point processors, ALUs, and other circuits. VLSI circuits are also being incorporated into instruments to supplant functions formerly performed by discrete hardware or by software.

#### Not to be Forgotten

There are many more product innovations that appeared in the HP Journal that can be considered to have made significant contributions to the technological history of Hewlett-Packard, but there is not enough room in this article to discuss them. Therefore, to ensure that these products are not forgotten the following is a list of these products and their associated HP Journal references.

- HP 8551A/851A Microwave Spectrum Analyzer (August 1964)

- HP 5000A Logic Analyzer (October 1973)

- Time-Domain Reflectometry

- HP 1415A Time-Domain Reflectometer Plug-in (February 1964)

- HP 8145A Optical Time-Domain Reflectometer (December 1988)

- HP 5525A Laser Interferometer (August 1970)

- HP 3406A Broadband Sampling Voltmeter (July 1966)

- HP-IB (IEEE 488 and IEC 625)(October 1972, January 1975)

- Chemical Analysis Instruments

- □ HP 8450A Spectrophotometer (February 1980)

- □ HP 1090 Liquid Chromatograph (April 1984)

- Medical Instrumentation and Systems

- HP Model 47210A Capnometer (CO<sub>2</sub> Analyzer) (September 1981)

- ☐ HP 77020A Ultrasound Imaging System (October 1983)

- Printers

- □ HP ThinkJet (thermal inkjet printer)(May 1985)

- HP DeskJet and HP PaintJet printers (September 1989, October 1989)

- Plotters

- HP's low-mass, low-inertia plotting technology (October 1981)

- ☐ HP 7580A Drafting Plotter (November 1981)

#### References

- A. Thiesen, A History of the General Radio Company, General Radio, 1965, p. 19.

- Inventions of Opportunity: Matching Technology with Market Needs, Hewlett-Packard Company, 1983.

- 3. Ibid., p. x.

- 4. Ibid., p. xi.

- 5. Ibid., p. viii.

### A Modular Family of High-Performance Signal Generators

Three signal generators, each designed for a particular type of application and each offering several options, let the user choose and pay for exactly the capability required.

by Michael D. McNamee and David L. Platt

DVANCES IN DIGITAL AND RF TECHNOLOGY over the last decade have made the RF signal generator a common tool on the workbenches of design engineers. High-quality commercially available generators offer excellent frequency stability, wide tuning range, reasonable switching speed, and a broad array of modulation types, including AM, FM, ΦM, and pulse. However, while LSI and design for manufacturability have brought down the price of the typical generator, most of these signal generators are general-purpose in nature and users are often forced to pay for performance that they don't need.

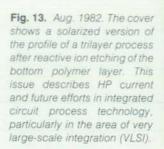

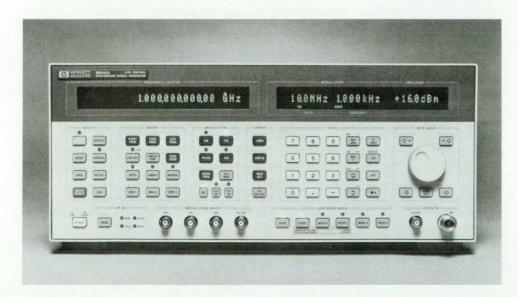

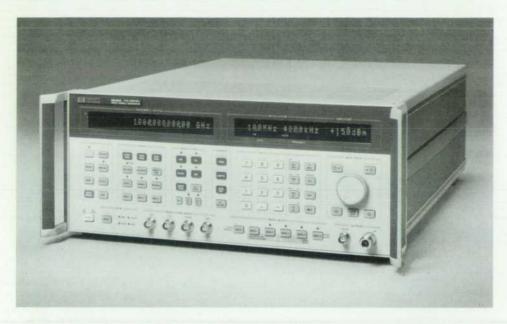

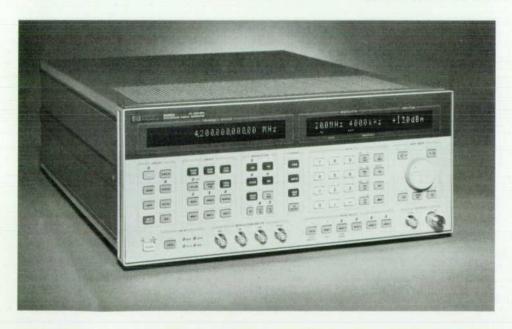

As test system complexity grows, the need to reduce both the price and the rack space of each piece of test equipment becomes critical. This requirement is the driving force behind such externally modular schemes as the VXIbus and the HP Modular Measurement System. Modularity offers the flexibility to tailor a system more specifically to a given application. With this in mind, HP has developed a new family of internally modular signal generators called the Performance Signal Generators (PSG). The three members of this family are the HP 8644A 1-GHz or 2-GHz Synthesized Signal Generator (Fig. 1), the HP 8645A 1-GHz or 2-GHz Agile Signal Generator (Fig. 2), and the HP 8665A 4.2-GHz Synthesized Signal Generator (Fig. 3).

These three signal generators are designed for three specific application segments. The HP 8644A is for the traditional out-of-channel transceiver test applications. The HP 8645A Agile Signal Generator is focused on frequency agile transceiver testing. The HP 8665A is designed for high-performance applications up to 4.2 GHz, particularly radar, telemetry, and spurious testing of UHF transceivers.

The internal modularity of the three PSGs allows a user to select among several options for each that provide a wider range of performance at a lower price than a single high-performance signal generator can provide. The user pays only for the performance required. Optional capabilities include phase noise enhancement, extended frequency range, numerically synthesized internal modulation, high-performance pulse modulation, and improved RFI leakage.

#### User-Selectable Performance Trade-Offs

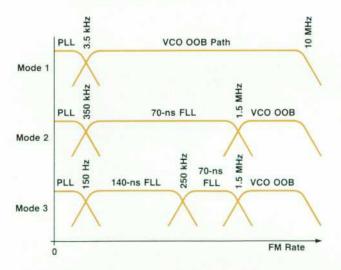

The most unusual feature of all three PSGs is the ability to make trade-offs among phase noise performance, maximum FM deviation, and switching speed from the front panel. This is done manually by selecting the desired mode of operation or automatically by selecting auto mode. When the PSG is in auto mode, the instrument automatically selects the mode that allows the lowest phase noise for a given carrier frequency and selected deviation.

Both the HP 8644A and the HP 8645A offer one standard and one optional enhanced mode. In the standard enhanced mode, the typical phase noise at a 20-kHz offset on a 1-GHz

Fig. 1. The HP 8644A Synthesized Signal Generator comes in 1-GHz and 2-GHz versions and is designed for out-of-channel transceiver testing.

Fig. 2. The HP 8645A Agile Signal Generator is available in 1-GHz and 2-GHz versions. It is designed for testing frequency agile trans-

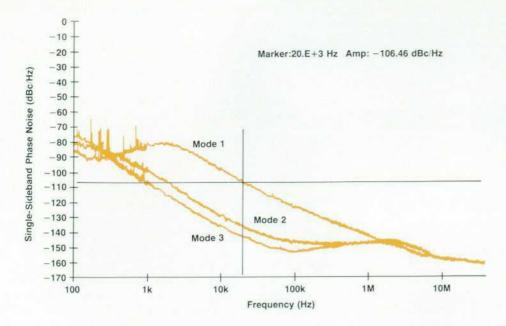

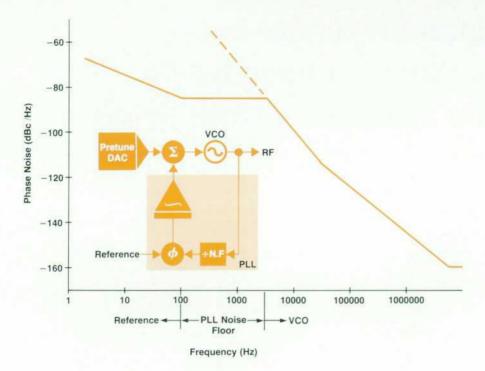

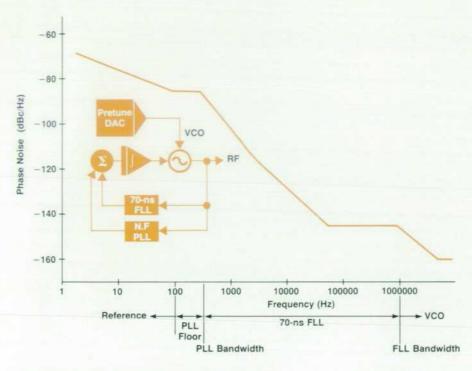

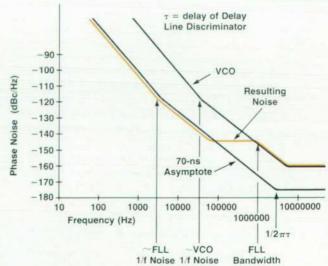

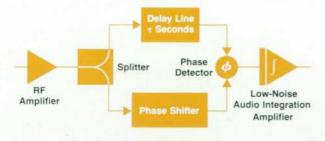

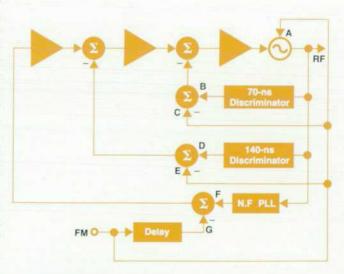

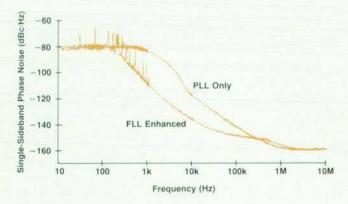

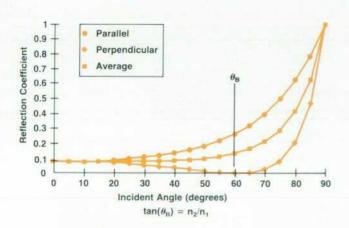

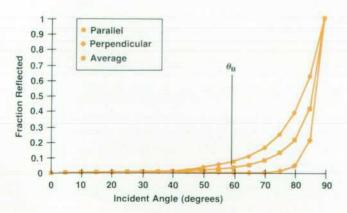

carrier is around -134 dBc/Hz. The optional enhanced mode improves this to -142 dBc/Hz. The HP 8665A offers one optional enhanced mode which improves the typical 20-kHz noise on a 1-GHz carrier from -124 dBc/Hz to -142 dBc/Hz. In an enhanced mode, a frequency discriminator detects the FM noise on the internal oscillator and cancels it in a feedback loop. This lowers the phase noise substantially over that of the phase-locked oscillator alone. However, a trade-off is required. The maximum available FM deviation is lower and frequency switching time is longer than in the unenhanced mode. Fig. 4 shows the phase noise obtained with the three available modes of the HP 8644A.

#### Surface Mount Technology

For many years, surface mount technology (SMT) has been used in critical RF circuitry because of its improved and consistent RF performance. Only recently has it been recognized that SMT offers improved reliability and lowercost parts placement in addition to smaller size. The PSGs are the first signal generators from HP using SMT extensively, including the power supply and controller. An extensive SMT process center was established specifically for automatic loading and soldering of the PSG surface mount assemblies. Electrical designers were asked to converge on a minimum set of "core" SMT components. As a result, approximately 80% of the components in the PSGs represent less than 400 SMT components. This approach reduces the cost traditionally associated with purchasing and maintaining large numbers of leaded components.

#### **Automatic Calibration**

Manual calibration adjustments are time-consuming and costly. Moreover, the components that allow these adjustments, trimmer potentiometers and capacitors, have higher failure rates than fixed-value components. For these reasons, the PSG designers replaced manual adjustments wherever possible using either precision fixed-value com-

Fig. 3. The HP 8665A Synthesized Signal Generator is a 4.2-GHz instrument designed for radar, telemetry, and UHF transceiver testing.

Fig. 4. HP 8644A phase noise in the normal and two enhanced modes

ponents or digital-to-analog converters (DACs) controlled by instrument firmware. As a result, the HP 8644A and HP 8645A have no manual adjustments. All calibration is done automatically by the microprocessor controller using precision internal sources and calibration data stored in EE-PROM. Even with its complex YIG circuitry, the HP 8665A only requires a few manual adjustments for calibration.

#### Single-Loop Design Concept

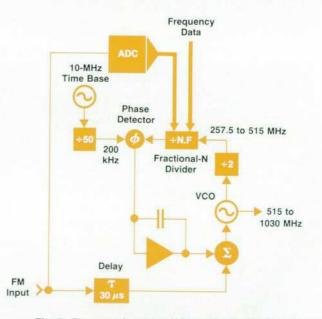

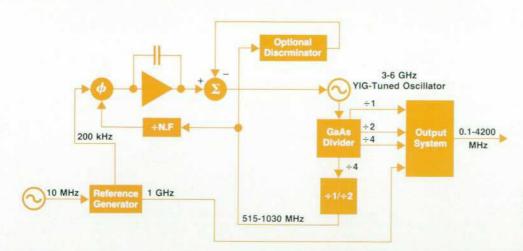

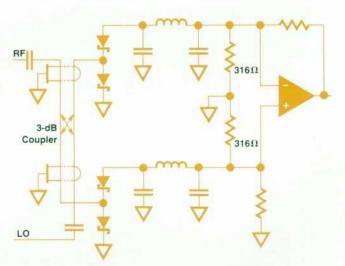

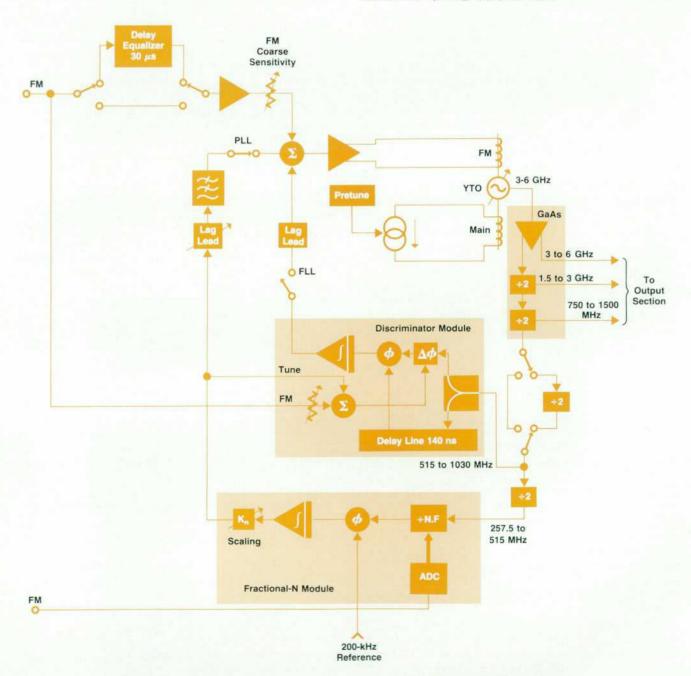

All three PSGs are based on the same fundamental frequency synthesis scheme, shown in Fig. 5. This scheme uses a single phase-locked loop (PLL), which is a fractional-N loop of the type used in many earlier HP signal generators. This loop provides the required frequency resolution as well as highly accurate digital FM at rates within the loop's bandwidth. The single-synthesis-loop approach has the advantages of better spurious performance and lower overall cost, parts count, and mechanical complexity. The single-loop approach, with its low reference frequency, requires a relatively narrow loop bandwidth to prevent multiplied reference phase noise from dominating the output phase noise. This impacts both switching speed and power line spurious cleanup. The PLL bandwidth of the PSGs varies between 150 Hz and 3 kHz.

Single-loop synthesizers have not been widely used in general-purpose signal generators. Typically, multiple loops are used—one loop providing frequency modulation, another providing high-resolution frequency control, and finally a sum loop, in which the VCO output is mixed with the outputs of the other loops and fixed reference frequencies to produce the signal that is fed to the phase detector. The reason the single-loop approach has not been used is that it has been difficult to achieve both fine frequency resolution and good spurious performance close to the carrier at the same time with a single phase-locked loop. The high-resolution fractional divider developed for the PSGs overcomes these problems, allowing 0.01-Hz frequency resolution and spur levels typically less than —48 dBc at less than a 1-kHz offset from a 3-GHz carrier.

This synthesis scheme results in an unusual approach

to frequency modulation (FM). Traditionally, FM is done in a phase-locked loop by injecting the modulating signal in two places—directly into the VCO to generate the FM and also into the loop integrator (after integration) to prevent the loop from trying to cancel the FM that was generated within its bandwidth. In the PSG approach, the FM that occurs within the loop bandwidth is not injected in an analog fashion, but digitally, by digitizing the FM input and adding it to the instantaneous frequency data that is fed into the fractional-N control chip. This ensures that the loop does not try to remove the FM, since it is programmed to generate the correct instantaneous frequency.

With this scheme, FM occurring at rates well within the loop bandwidth is done digitally and FM at rates well above the loop bandwidth is done in the traditional analog

**Fig. 5.** The same fractional-N frequency synthesis system is used in all three generators. However, in the HP 8665A, the voltage-controlled oscillator (VCO) runs at 3 to 6 GHz.

fashion. A major drawback is that the digital FM is delayed by 30 microseconds, the time required to digitize it and clock it into the fractional-N control chip. This results in a large group delay variation, from 30 microseconds at low rates to less than a microsecond at high rates. For the loop bandwidth of 3 kHz, this would cause a large FM inaccuracy at rates around 3 kHz. Moreover, such a high group delay variation would cause excessive FM distortion for complex modulating signals. To correct this problem, a 30-microsecond delay is added into the FM path to the voltage-controlled oscillator (VCO). This causes all FM to experience a 30-microsecond delay, and the variation in group delay is reduced to only a few microseconds.

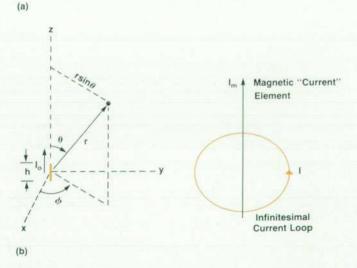

#### HP 8645A Concept

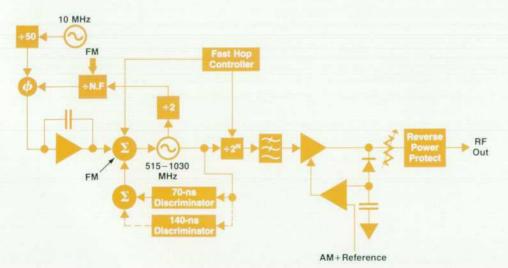

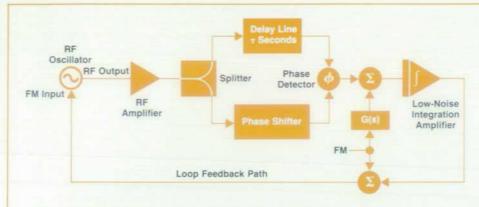

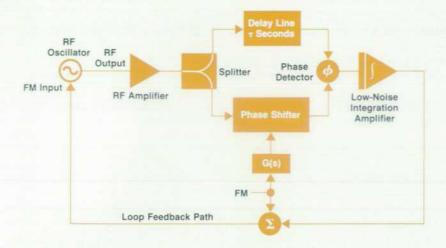

The first of the three PSGs to exit the investigation phase was the HP 8645A Agile Signal Generator. A basic block diagram of the HP 8645A is shown in Fig. 6. In addition to the single PLL described previously, the HP 8645A also contains one or two delay line frequency discriminators to detect and feed back FM noise to the VCO for cancellation. When operated in mode 1, the HP 8645A uses only the PLL for frequency stability. This mode offers the fastest synthesized frequency switching speed and greatest FM deviation. Mode 2 adds a frequency-locked loop (FLL) containing a 70-nanosecond discriminator, which improves the phase noise at the expense of reduced deviation and switching speed. Mode 3 adds an optional 140-nanosecond discriminator which extends this trade-off even further, reducing the phase noise another 8 dB.

The HP 8645A also offers a fast frequency hopping mode (mode 5). In this mode, the PLL is opened but the 70-nanosecond FLL remains connected. Thus, the VCO remains frequency locked but not phase locked. Fast hopping is done using several DACs to set control and pretune voltages in the FLL to force the VCO frequency to change very rapidly. The exact control voltages are determined by the microprocessor controller during a "learn" process prior to fast hopping.

In the fast hopping mode the frequency can switch in less than 15 microseconds. The frequency accuracy, which is a function of the drift of several critical components in the FLL, is typically better than  $\pm 1$  part per million. Fre-

quency hopping of the HP 8645A is discussed further in the article on page 34.

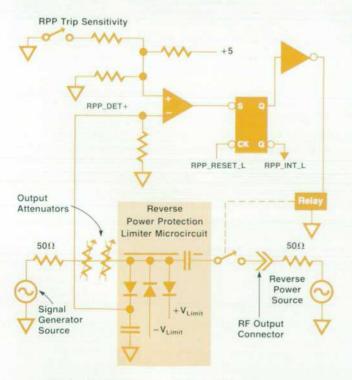

The VCO output of 515 to 1030 MHz is digitally divided to the desired output frequency (doubling is also available with Option 002). A switched, half-octave low-pass filter follows the divider to reduce harmonics. The signal is amplified and leveled in an automatic level control (ALC) loop. AM is performed in the traditional manner within the ALC loop bandwidth. The loop bandwidth can also be narrowed greatly to improve intermodulation performance to better than -50 dBc. The output attenuator is a set of two mechanical attenuators from the HP 33320 Series. This is followed by a reverse power protection relay that protects the output from an accidental application of up to 50 watts of RF.

#### HP 8644A Concept

It was recognized that the single-loop synthesizer with discriminator-enhanced spectral purity is ideal for out-of-channel transceiver testing because of its ability to achieve -100 dBc spurious and -134 dBc/Hz phase noise at a reasonable cost. This led to the concept of the HP 8644A as a cost-reduced version of the HP 8645A.

During the investigation phase of the HP 8644A it was tempting to scale down some of the common modules such as the power supply and the microprocessor controller, since that hardware had much more capability than we actually needed. While this redesign would have allowed a lower HP 8644A cost, it would not have allowed some of the reuse advantages discussed later in this article. Therefore, we focused on changes in the VCO and modulation circuitry.

The HP 8644A block diagram is similar to that shown for the HP 8645A except that the fast hop controller is not present. The approach taken was to remove all the circuitry associated with fast frequency hopping as well as the high-rate FM capability. This allowed us to combine the VCO, standard discriminator, and phase shifter functions into a single module. The modulation drive circuitry was greatly simplified and standard modulation features, such as FM preemphasis and internal 300-Hz, 400-Hz, 1-kHz, and 3-kHz modulation oscillators were added.

The HP 8644A output section is identical to the HP

**Fig. 6.** Block diagram of the HP 8645A Agile Signal Generator.

8645A output section except that an optional high-reliability 1-GHz electronic attenuator (Option 005) is also available. This attenuator uses pin diodes instead of mechanical switches and is identical to the attenuator used in the HP 8657A Synthesized Signal Generator.

#### HP 8665A Concept

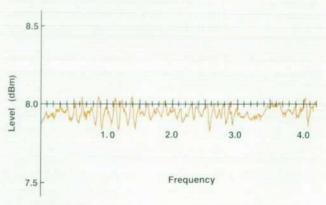

The HP 8665A concept was driven by two factors. First, users find it increasingly necessary to push RF signal generator performance into the low microwave region. For example, 900-MHz radio manufacturers need spurious testing capability to at least 4 GHz. Spurious testing requires precise level control to very low signal levels and low adjacent channel spurious content. The HP 8665A's -100-dBc spurious performance and  $\pm 1\text{-}\text{dB}$  level accuracy at 3 GHz allow these high-performance measurements.

The second driving factor was the desire for high reuse of the single-loop, discriminator-enhanced PSG block diagram. By using whole modules from the other PSG projects along with a few special modules, the HP 8665A development required far less in engineering resources than would have been required if the product had been designed "from scratch."

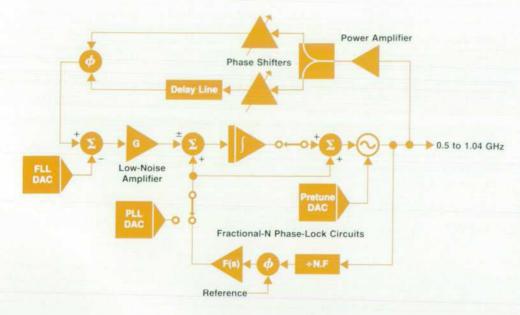

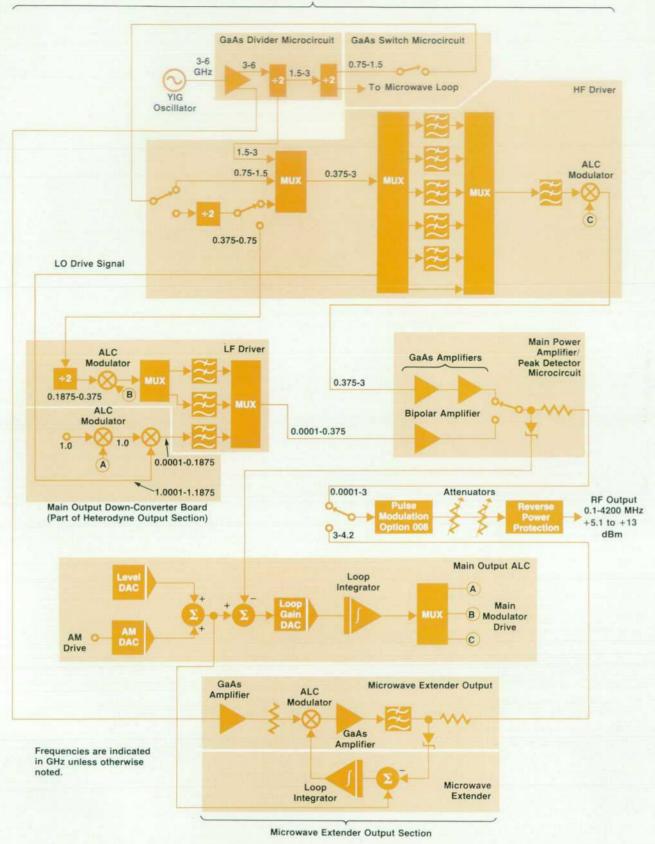

The HP 8665A block diagram, Fig. 7, is very straightforward. The synthesis is accomplished by a single phase-locked loop. A phase-noise-selected YIG oscillator running from 3 to 6 GHz is prescaled by four with a specially developed GaAs divider to 750 to 1500 MHz. A silicon ECL divider further divides the signal to the phase detector module input frequency of 257.5 to 515 MHz.

The phase detector module is the same fractional-N module used by the HP 8644A and HP 8645A. This module is highly complex and handles much of the FM function as well as the loop synthesis.

FM is added to the YIG's output via two paths. For dc and low frequencies the modulation signal is applied to the fractional-N divider by digitizing the signal. At higher modulation frequencies, the modulation is applied outside the loop bandwidth through the YIG driver. A detailed discussion of the synthesis section can be found in the article on page 37.

The spectral purity of the HP 8665A can be enhanced with the use of a discriminator attached to the input to the phase detector module. The error signal generated by the discriminator is an indication of the phase noise content of the synthesis loop and is applied through the YIG driver to reduce the noise of the output. The discriminator module is another of the common assemblies developed for the PSG family.

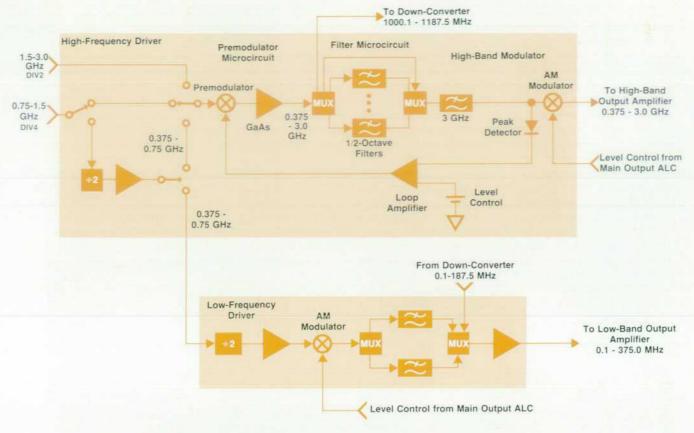

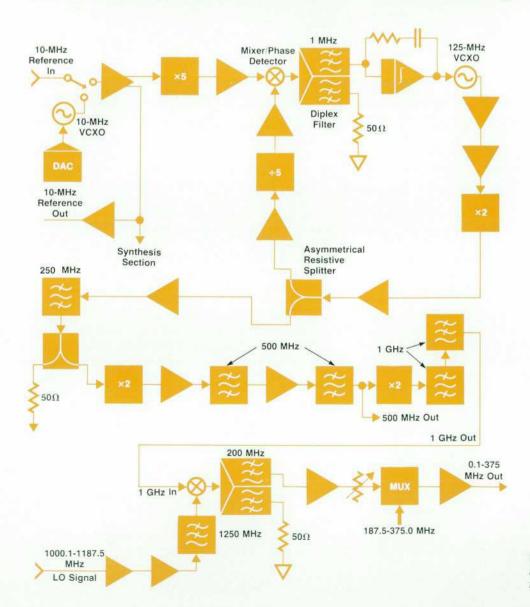

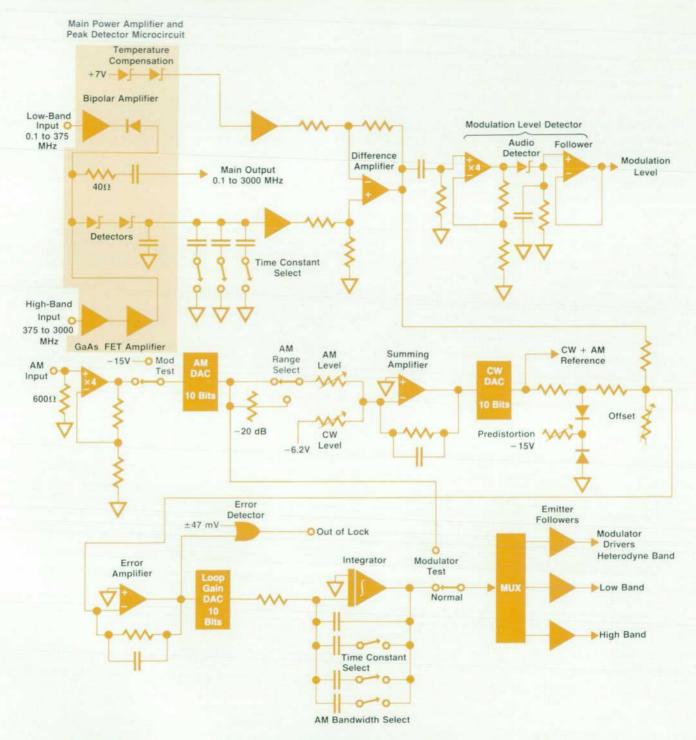

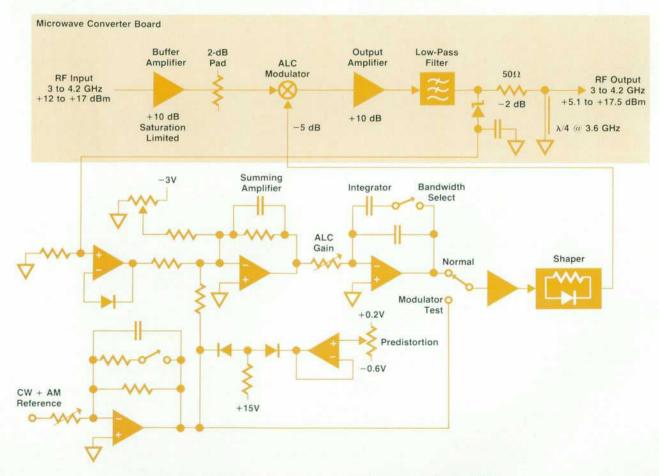

To allow phase noise to be scaled with frequency, the output section is constructed around a hybrid approach found in most of HP's high-performance RF generators. For frequencies from 187.5 MHz to 4200 MHz, the signals are derived by frequency division. For the highest octaves, the frequency division is done by the GaAs divider in the synthesis loop. To preserve the FM deviation at lower frequencies, a heterodyne approach is used below 187.5 MHz. A 1-GHz reference is developed from the 10-MHz time base and this signal is mixed with a 1000-to-1187.5-MHz frequency range produced by a divider in the output section to form the output signal. The HP 8665A output system is discussed in the article on page 42.

#### Common Hardware

The following sections describe hardware that is used in all three PSG products.

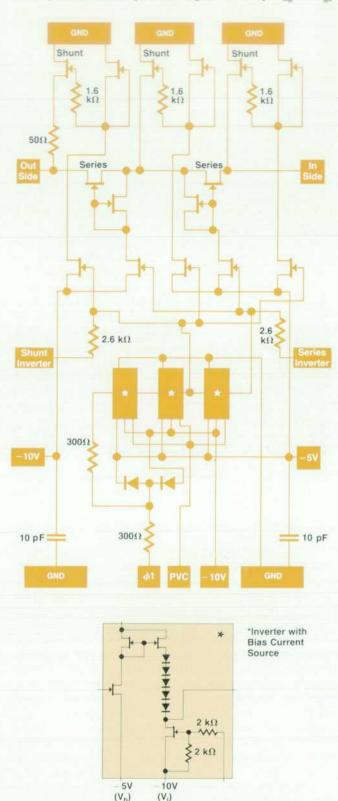

#### Fractional-N Module

The PSG fractional-N module performs the fractional division, phase detection, and integration functions of the PSG phase-locked loop. It also digitizes the low-rate FM and sums it with the desired frequency information. The RF input is 257.5 to 515 MHz and the reference input is a 200-kHz pulse train supplied from the reference module by dividing down the 10-MHz time-base. The fractional-N board, shown in Fig. 8, is a six-layer Class III printed circuit board. This board is extremely complex, and because of the relatively high reference frequency, required several iterations to reduce the fractional-N spurious below  $-60\,\mathrm{dBc}$ .

Two custom integrated circuits, which can be seen in Fig. 8, make this level of complex synthesis circuitry possible. The first is a four-watt ECL gate array, which performs the fractional division (÷N.F). The second is the fractional-N control chip, which combines the FM input with the desired carrier frequency and controls the fractional division.

Fig. 7. Block diagram of the HP 8665A Synthesized Signal Generator.

Fractional frequency division generates spurious signals, as already indicated. A technique known as automatic phase interpolation (API) allows these spurs to be largely cancelled. This cancellation requires extremely precise control of very small currents, and is only effective to  $-50\,$  to  $-60\,$  dBc. The API correction in the PSG uses an automatic spur nulling technique in which the spurs are synchronously detected and the API currents are adjusted to minimize the spur levels. For more information, see the box on page 28.

#### **PSG Modulation Oscillator**

Early in the PSG development we realized that simulating complex modulation signals is becoming difficult for our customers. With the advent of integrated implementations of numerical synthesis techniques, a powerful solution exists. The key synthesis IC developed for the HP 8904A Multifunction Synthesizer1 was used to build the PSG's compact and versatile modulation assembly. This assembly consumes little more than 15 square inches of board space yet allows synthesized modulation signals from dc to 400 kHz. Square waves and Gaussian noise can be generated in addition to sine waves. The oscillator can produce two simultaneous waveforms to emulate many signaling tones and it can internally modulate itself. Modulation waveforms such as those used in aircraft VOR and ILS applications can now be generated totally inside the signal generator.

#### **PSG Front Panel**

The PSG front panel assembly deviates from those found on previous generators in two ways. An in-depth reliability study showed that keyswitch problems accounted for a disproportionately high number of failures. This drove our choice of rubber keyswitches for the front panel. Rubber keyswitches have been shown to have a very low failure rate compared with their mechanical counterparts.

The other area of difference is the use of vacuum fluorescent displays. These devices are rugged and reliable, and

Fig. 8. Two custom ICs, an ECL gate array and a control chip, make the small size of the fractional-N module possible.

have very high readability. Special consideration was given to their driving waveshapes to minimize RFI emissions from the generator and RFI effects on the low-spurious circuitry inside the product.

#### **PSG Microprocessor Controller**

The PSG digital control unit controls all of the PSG hardware. The design is based on an 8-MHz Motorola 68000 microprocessor. The control board holds 512K bytes of ROM, which contains all the instrument control firmware. This board also contains the HP-IB interface, which uses a TMS9914. Interrupt handling, timers, and serial communication to the front panel are provided by a Motorola 68901 multifunction peripheral chip. For setting up the RF hardware and performing diagnostics, the board includes voltmeter circuitry to measure dc or rms voltages throughout the instrument. The voltmeter and a simple RF detector provide basic power measurement capability for RF hardware diagnostics. The processor execution stack and instrument state reside in 64K bytes of static RAM. Store/recall registers and the instrument state are maintained by a NiCadbattery-backed RAM when the instrument is powered down. The battery is charged during normal operation by an onboard regulator. The processor communicates with the rest of the instrument through memory-mapped parallel I/O ports.

#### **PSG Power Supply**

The PSG power supply is a linear supply capable of 180 watts distributed among several supply voltages. The supply is designed for extremely low levels of conducted and radiated line-related spurious outputs. Careful attention was paid to the layout to minimize magnetic loops and ensure that sensitive circuitry and noisy rectifier circuits did not have common ground return paths.

The PSG power supply contains circuitry to shut down the supply when the internal temperature exceeds safe limits. This can occur, for example, if the airflow from the fan is interrupted. Circuitry also exists to vary the fan speed with temperature to improve instrument reliability at high temperatures while maintaining a quiet fan at room temperature. Precision reference ICs are used in the regulators to avoid manual adjustments of the supply voltages.

#### Modularity Effects in Development

An important benefit of internal modularity lies in the resulting potential for reuse of circuitry among instruments. One of the primary PSG design goals was to make as much hardware and firmware as possible common to all three PSGs. Using this approach, the development of these three high-performance products took place almost as quickly as a single product, and used only slightly more resources.

Probably the most difficult phase in a product's development is the production buildup. Unforseen yield and process problems show up, along with design tolerance problems in mechanical parts as a greater number of parts are processed. Debugging and streamlining of test and assembly procedures is required. This phase takes a lot of time and resources and anything that can be done to shorten this critical learning process will help.

The modularity of the PSG family was an important ad-

vantage in this phase. Because of the high degree of reuse, we are able to build all three signal generators on the same production line using the same assembly processes and test equipment. Even in the product-specific modules, designers were constrained to use a common pool of surface mount parts and design techniques. The result was that, while it took more effort to handle all three products initially, the overall time to get through the learning process was much shorter than it would have been with three very different products produced on their own production lines.

The development effort for the PSG family was organized into three separate concurrent projects. In addition to product-specific modules, each project developed one or more of the modules used in all three signal generators. The HP 8644A project developed the fractional-N synthesis circuitry. The HP 8645A project developed the power supply, microprocessor controller, and low-noise frequency discriminator. The HP 8665A project developed the front panel and numerical-synthesis modulation source. This concurrent development required a high degree of discipline on the part of the project designers to reuse hardware and firmware and to resist the urge to optimize by redesigning.

Another key component of this concurrent development was interproject communications and management. The magnitude of the overall management task was much greater than originally thought. It was necessary to maintain rigid, detailed I/O specifications on each assembly. In addition, all three project managers met regularly with their section manager and with manufacturing, marketing, QA, and finance people.

#### Acknowledgments

The authors would like to thank Ray Fried for his fundamental contributions to the PSG concept and his support throughout the development. We would also like to thank Dave Molinari for his contribution as HP 8645A project manager. Finally, we would like to acknowledge the tremendous effort on the part of numerous R&D, production, and assembly and test engineers who worked on the PSGs during the initial production phase.

#### Reference

F.H. Ives, "Multifunction Synthesizer for Building Complex Waveforms," Hewlett-Packard Journal, Vol. 40, no. 1, April 1989, pp. 52-57.

## Firmware Development for Modular Instrumentation

Of three major subsystems in the Performance Signal Generator control firmware, only one contains instrumentspecific code. Additional hardware and firmware for calibration and diagnostic purposes provide important customer and production benefits.

by Kerwin D. Kanago, Mark A. Stambaugh, and Brian D. Watkins

HE PERFORMANCE SIGNAL GENERATOR (PSG) product line described in this issue represents an internally modular platform approach to the development of signal generators. There are currently three full-function signal generators in this family, each with a number of options. The similarities between these signal generators, including a large amount of shared RF hardware, suggests that the firmware to control them can be shared or highly leveraged between versions. This is in fact the case.

The major design objectives for the control firmware were:

Reuse as much firmware as possible to reduce development and test time relative to developing three different sets of signal generator firmware.

- Structure the firmware so that it can be extended to allow for future versions and options.

- Give the three instruments a common look and feel from the front panel.

- Use consistent symbolic HP-IB control language and formats for all three signal generators that could also be used in future signal generators.

Since reuse was a key issue in PSG control firmware development, the majority of the control firmware was written in a high-level language. Only time-critical routines, code that directly interfaces with hardware, and certain library routines were written in assembly code. The control firmware for all three PSG instruments consists of 100 KNCSS (thousands of noncomment source statements) of Pascal source code and 8 KNCSS of assembly language

source code. The firmware executes on a 68000 microprocessor with 512K bytes of ROM and 64K bytes of RAM.

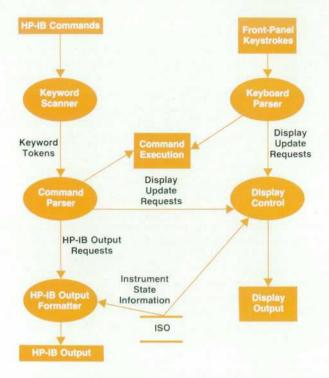

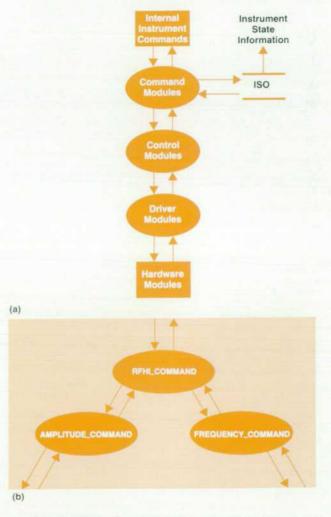

#### Control Firmware Architecture

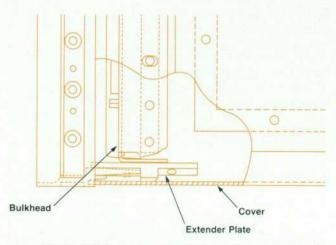

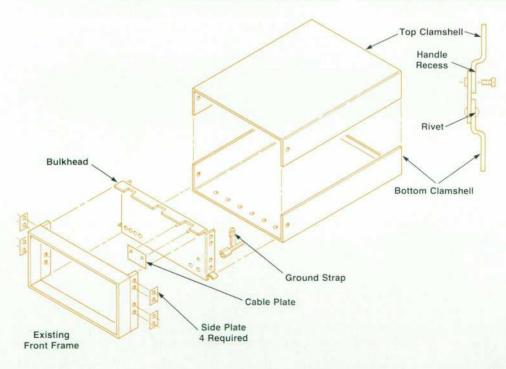

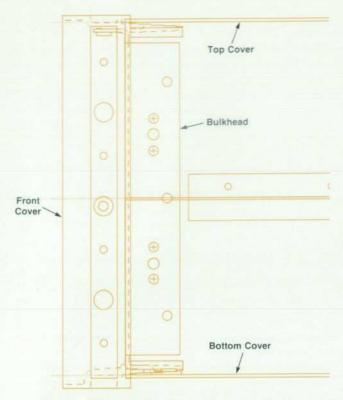

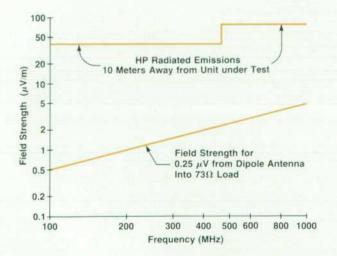

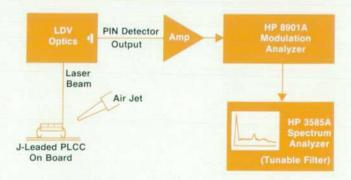

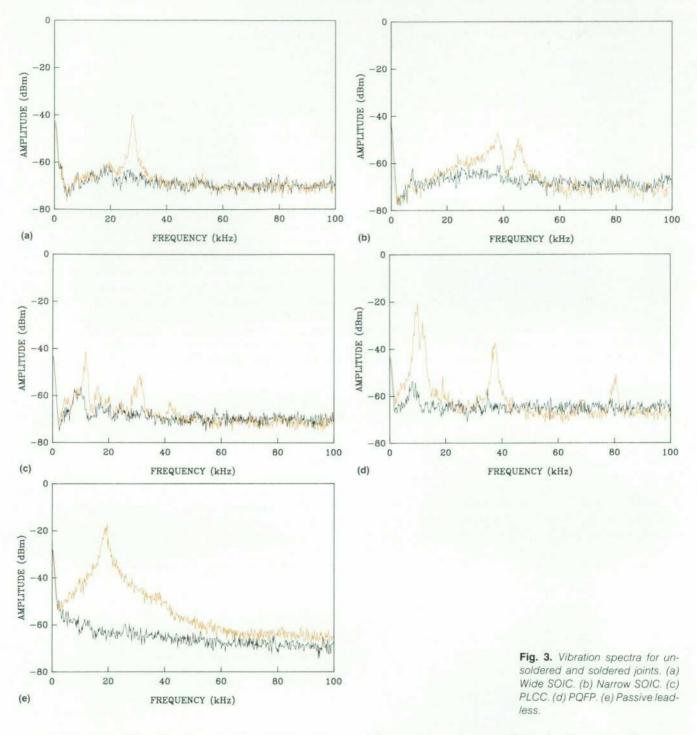

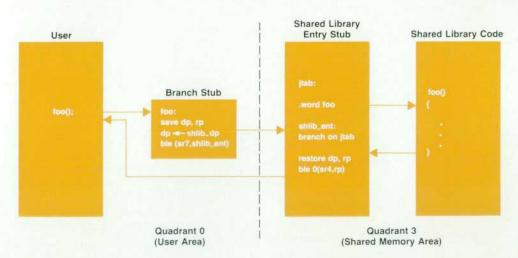

The control firmware for the PSG family is partitioned into three major subsystems (Fig. 1). They are the KRNL (operating system kernel), the UI (user interface), and the RFHI (RF hardware interface). The KRNL contains the operating system, support libraries, and low-level I/O drivers. It passes input data from the front panel and HP-IB to the UI. The UI takes character data from the KRNL and converts it to internal instrument commands with parameters which are passed to the RFHI. The UI also formats data to be output via the HP-IB (IEEE 488, IEC 625) or displayed on the front panel. The RFHI section takes commands from the UI, range checks the parameters, and configures the hardware appropriately. The RF hardware interface also stores the current instrument configuration.