## HEWLETT-PACKARD

**APRIL 1986**

# HEWLETT-PACKARD JOURNAL

April 1986 Volume 37 . Number 4

#### Articles

A Data Acquisition System for a 1-GHz Digitizing Oscilloscope, by Kenneth Rush and Danny J. Oldfield Random repetitive sampling yields an equivalent digitizing rate of 100 GHz for repetitive signals.

5 General-Purpose 1-GHz Digitizing Oscilloscopes

- High-Performance Probe System for a 1-GHz Digitizing Oscilloscope, by Kenneth Rush, William H. Escovitz, and Arnold S. Berger Because a typical system includes more than one class of signal, a versatile probe system is a must.

- **20** Waveform Graphics for a 1-GHz Digitizing Oscilloscope, by Rodney T. Schlater Fast plotting algorithms approximate the feel of an analog oscilloscope.

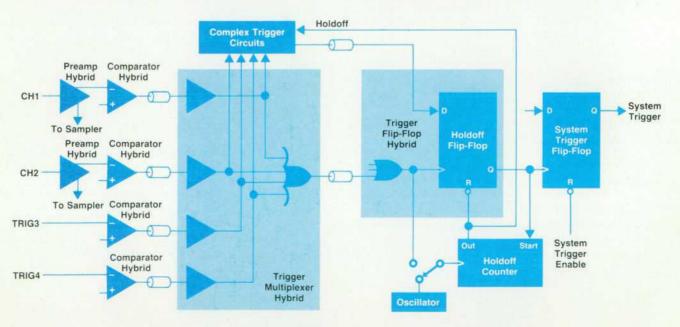

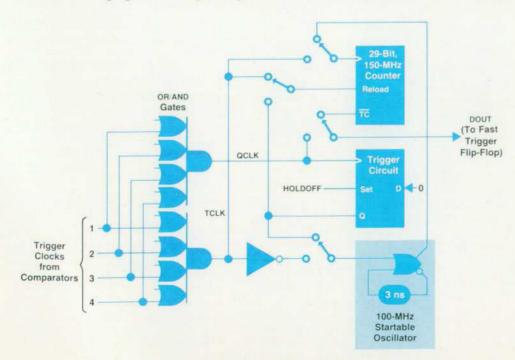

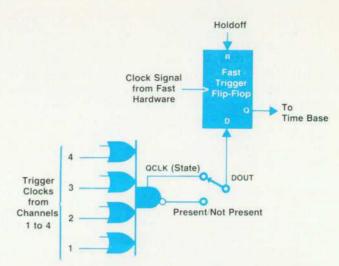

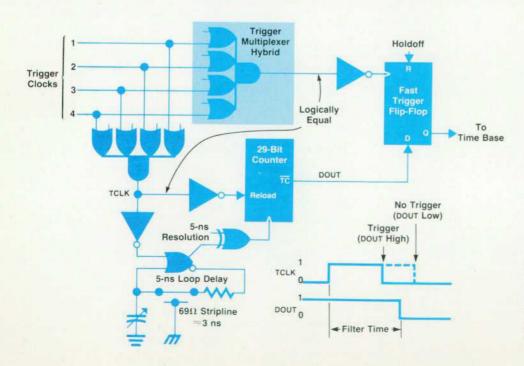

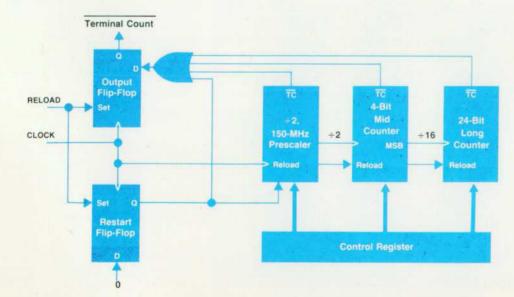

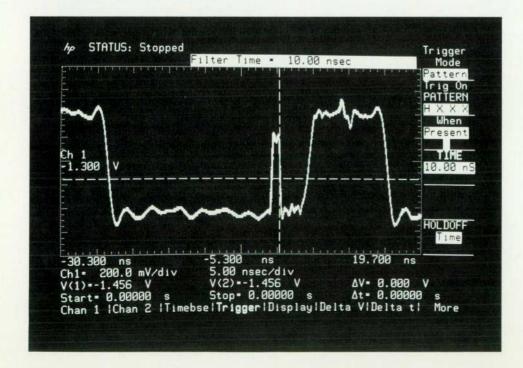

- Hardware Implementation of a High-Performance Trigger System, by Scott A. Genther and Eddie A. Evel The trigger system resembles the front end of a logic analyzer.

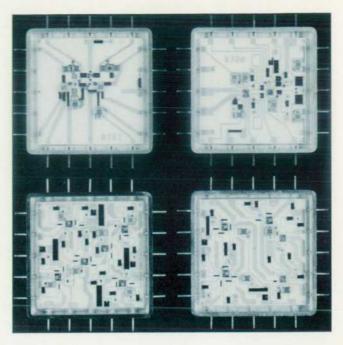

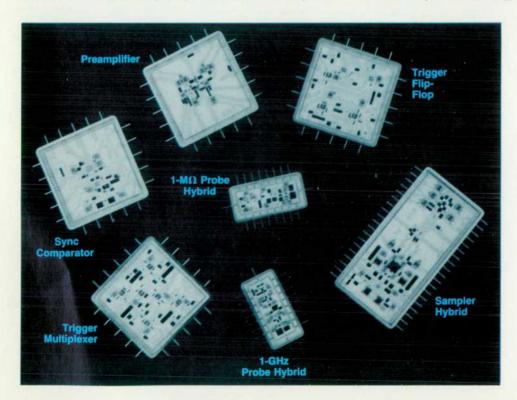

- 33 1-GHz Digitizing Oscilloscope Uses Thick-Film Hybrid Technology, by Derek E. Toeppen Some new processes were developed and some old ones were improved.

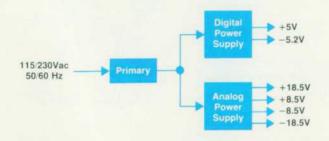

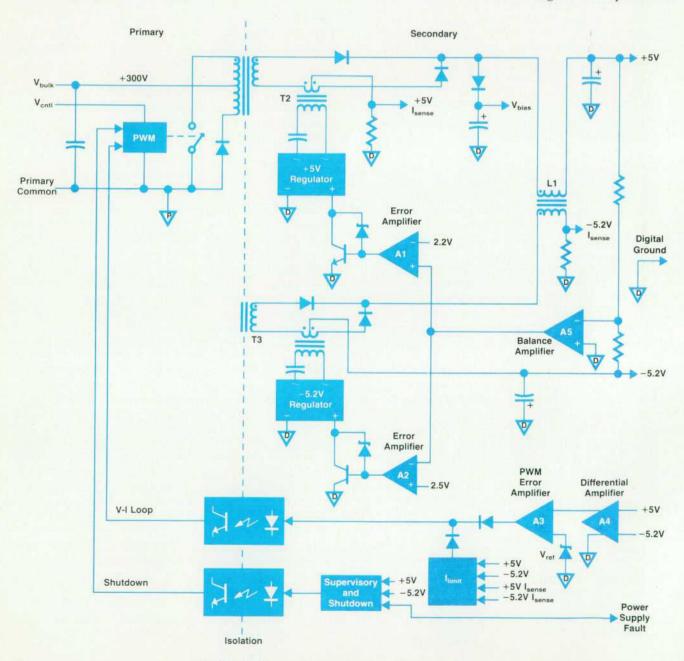

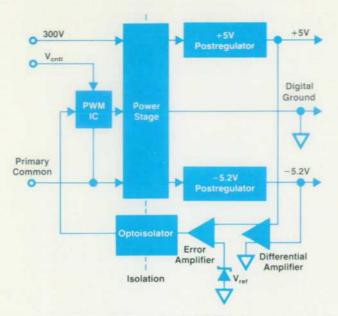

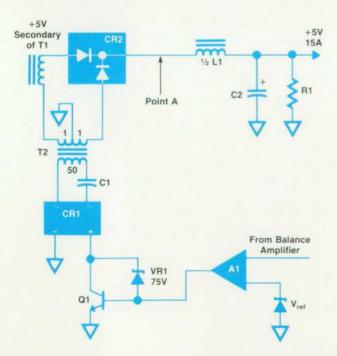

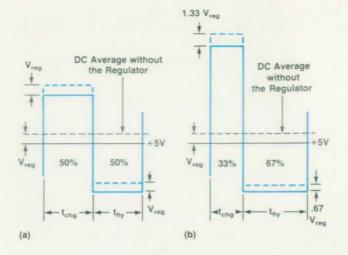

- 37 A Modular Power Supply, by Jimmie D. Felps A primary assembly drives two switching mode dc-to-dc converters.

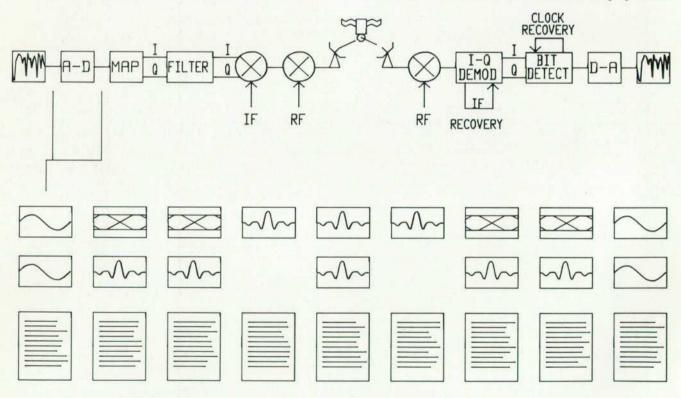

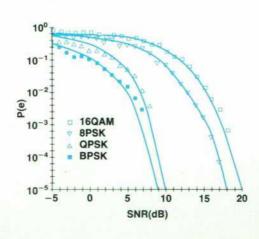

- Program Helps Teach Digital Microwave Radio Fundamentals, by Christen K. Pedersen Even someone entirely unfamiliar with electronics and communications can learn something.

- 47 Authors

Editor, Richard P. Dolan

Associate Editor, Business Manager, Kenneth A. Shaw

Assistant Editor, Nancy R. Teater

Art Director, Photographer, Arvid A. Danielson

Support Supervisor, Susan E. Wright Illustrator, Nancy S. Contreras.

Administrative Services, Typography, Anne S. LoPresti

European Production Supervisor, Michael Zandwijken

Publisher, Russell M. H. Berg

#### In this Issue

One of my memories of my first engineering job is of my efforts to measure 0.1-microsecond pulse rise times with an oscilloscope—state-of-the-art at the time—that had a 0.35-microsecond rise time. How wonderful it would have been to have one of the scopes whose design is the subject of the first six papers in this issue. These instruments have 350-picosecond rise times, a thousand times shorter than my old scope's. On the other hand, the designers they're intended for are working with high-speed logic families and high-speed data communications, where rise times are typically less than one nanosecond. That's how it goes—better instruments help create

better circuits, which create a need for better instruments, and so on.

The oscilloscopes discussed in this issue are the HP 54100A/D and HP 54110D Digitizing Oscilloscopes. All three models have 1-GHz bandwidth, 100-picosecond time base accuracy, 10-picosecond time interval resolution, and a digitizing rate of 40 megasamples per second. Using a technique called random repetitive sampling (page 4), they sample the input signal, convert the samples to digital form, store the resulting numbers, and display them on demand. Their storage capability lets them show input events that occurred before the trigger event and provide infinite-persistence displays. The HP 54100A has three input channels—two vertical and one trigger. The HP 54100D has an extra trigger input and provides complex pattern-recognition triggering like a logic analyzer (page 26). The HP 54110D adds a high-resolution full-color display, waveform math functions, semiautomatic channel-to-channel time interval measurements, and automatic measurements on stored waveforms. HP expects that up to 80 percent of its customers for 1-GHz oscilloscopes will prefer the full-color HP 54110D. All three models are fully programmable for use in automatic manufacturing test systems.

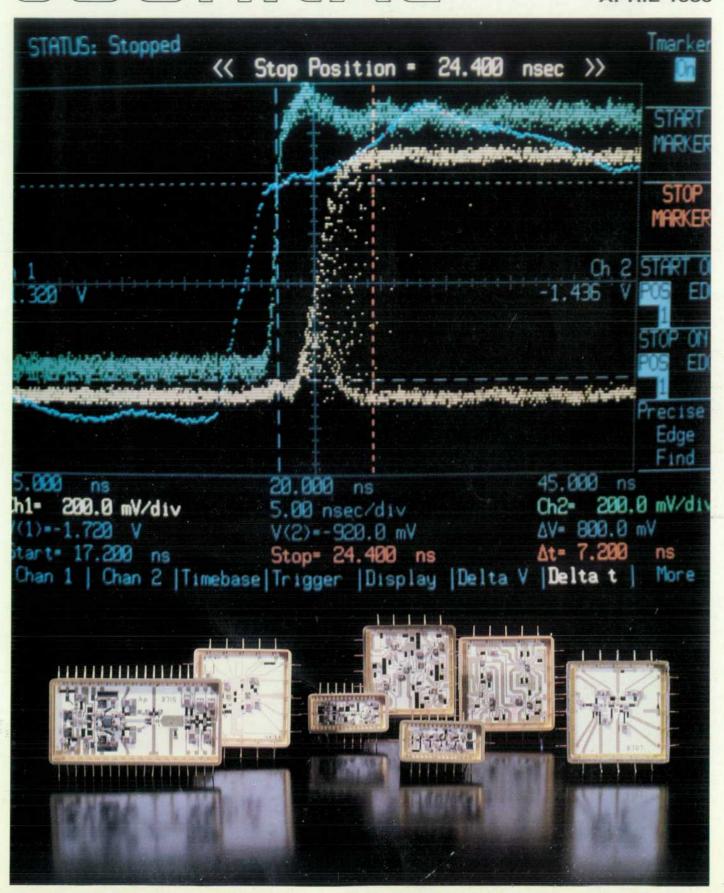

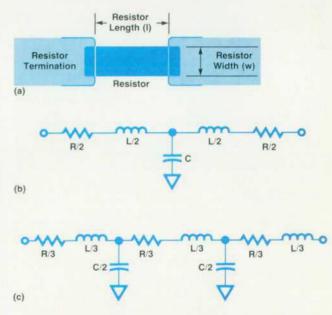

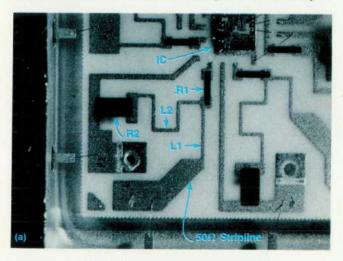

The box on page 5 introduces these three scopes and discusses the need for them. The paper on page 33 describes the thick-film hybrid technology that's responsible for the scopes' performance. Shown on the cover, in front of a display from the HP 54110D, are the seven hybrid circuits in each instrument: a 1-GHz preamplifier, a 3-GHz sampler, a 1-GHz probe receiver, a 300-MHz probe receiver, and three trigger hybrids making up a 500-MHz trigger system. Other papers describe the scopes' data acquisition system (page 4), probe system (page 11), waveform graphics (page 20), trigger system (page 26), and power supply (page 37).

Until recently, the most cost-effective method for long-distance voice communications over terrestrial and satellite microwave links was analog transmission using frequency division multiplexing and mechanical switching. Now, thanks to advances in integrated circuits and high-speed logic, the balance is beginning to tip in favor of the all-digital communications system, using pulse code modulation, time division multiplexing, and digital switches. The article on page 40 describes a software package that teaches the fundamentals of digital microwave radio by simulating a real system in action. It's intended for technical people who are new to digital communications, and for senior engineers and engineering managers who need to increase their familiarity with the subject.

-R.P. Dolan

#### What's Ahead

The design and features of a line of instrument modules for use with personal computers is the primary subject of the May issue. These members of HP's PC Instruments family make use of a personal computer's display as a soft front panel to reduce their cost. They come in small packages that can be stacked and racked.

Also included in the May issue is a research report about a new VLSI metallization technology using titanium silicide.

### A Data Acquisition System for a 1-GHz Digitizing Oscilloscope

by Kenneth Rush and Danny J. Oldfield

HE DREAM OF MANY oscilloscope users is to own an instrument that can store for all time a record of a single event to high resolution in both amplitude and time. Towards this end, many people around the world are designing very fast analog-to-digital converters (ADCs) and producing digitizing oscilloscopes. The approach has typically been to digitize to a modest resolution at very high rates. Currently, several manufacturers offer 8-bit, 100-MHz ADCs. The reason for the emphasis on faster ADCs is the need of end users for greater time resolution in their measurements.

If we recognize that many signals of interest can be made to repeat, then alternate methods can be used to achieve high time resolution in a digitizing oscilloscope. This article describes a system used to realize one of these methods, called random repetitive sampling. The system achieves an equivalent sampling rate of 100 GHz and a bandwidth of 1 GHz for a time resolution of 10 ps.

#### Random Repetitive Sampling

The HP 54100A/D Digitizing Oscilloscope makes random observations of input signal voltages and stores these observations in memory. The true timing of these observations is determined by measuring the time relationship between a trigger event related to the input signal and the sample clock in the instrument. Every 25 ns the input signals are sampled, digitized, and stored into memory. While each sample is time correlated with every other sample because the samples are spaced 25 ns apart, the samples are not correlated in time with the input signal. When a trigger event is detected, the timing relationship between the trigger event and the sample clock (40 MHz) is measured to a

resolution of 10 ps by a circuit called the trigger interpolator, to be described later.

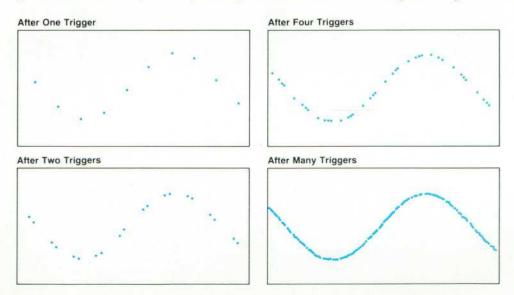

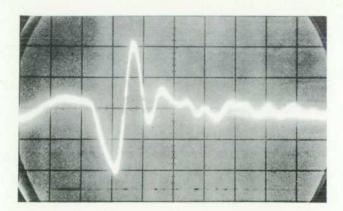

If we are able to keep the information gained from this first measurement, that is, the sampled voltage values and the time relationship value, then the measurement could be repeated to obtain a new set of voltage values and a new random time relationship value. Repetitively making this measurement on a signal that doesn't change much from measurement to measurement will yield an accurate image of the signal waveform with 10-ps time resolution by reconstructing the waveform from the information stored over many measurements. Fig. 1 illustrates how data accumulates in a typical case.

If we have an acquisition memory depth of 1024 samples, and we do not arm the trigger until we have stored 1024 points, then the memory is holding a history of the signal that spans about 25 microseconds. If we stop storing samples as soon as we detect a trigger event, then we can accumulate over many triggers up to 25 microseconds of information before the trigger, even at high time resolution. If the sample rate is reduced by a factor of ten, then the amount of pretrigger viewing can be extended to 250 microseconds. This method of reducing the sampling rate is used to achieve very long pretrigger viewing in the HP 54100A/D. This is one of the contributions of random repetitive sampling, that is, pretrigger viewing with high time resolution without the necessity of delay lines to time shift the signals.

The HP 54100A/D has a posttrigger delay counter to program what portion of the 1024-point acquisition memory is stored before and after the trigger. When measurements are to be made a long time after the trigger, it is not necessary to change the sample rate. The posttrigger counter is simply

Fig. 1. In random repetitive sampling, the accumulation of information over many triggers or measurements produces an accurate image of the signal waveform.

(continued on page 6)

#### General-Purpose 1-GHz Digitizing Oscilloscopes

The six articles on pages 4 through 39 of this issue report on various aspects of the design of the HP 54100A/D and HP 54110D Digitizing Oscilloscopes. These general-purpose oscilloscopes take advantage of a completely digital oscilloscope architecture, random repetitive sampling, and state-of-the-art technologies to meet the new demands faced by engineers involved with digital design and high-speed data communications. The HP 54100A/D and HP 54110D simplify analog time-domain measurements on high-speed logic circuits. They can make the new measurements needed when working with the most recently developed logic families, and they can make many measurements faster and more accurately than conventional oscilloscopes.

Introduced in October 1984, the HP 54100A/D was HP's first completely digital oscilloscope, and industry's first 1-GHz-bandwidth digital oscilloscope. The A model has two vertical channels and one trigger channel, and provides three-bit pattern recognition triggering. The D model has an additional trigger channel and provides four-bit pattern recognition triggering and other complex triggering features. The HP 54110D (Fig. 1), introduced in October 1985, adds a color display and several additional measurement capabilities to the feature set of the HP 54100D.

In addition to their 1-GHz bandwidth (350-ps rise time), the HP 54100A/D and HP 54110D also provide a 100-ps/div time base and 10-ps time resolution. These capabilities allow the user to measure subnanosecond rise times, propagation delays, and glitches.

A 40-megasample/second digitizing rate and infinite persistence mode allow the user to capture fast, low-repetition-rate signals, infrequent error conditions, or variations in a signal. The infinite persistence mode is also useful when looking at worst-case conditions such as noise, jitter, and drift.

Three types of interchangeable input pods allow the user to measure signals from a variety of source impedances. The HP 54300A Probe Multiplexer accepts all three input pods and allows up to 16 probes to be multiplexed at one time. Up to two HP 54300As can be cascaded in series, increasing the number of inputs that can be multiplexed.

#### Design Trends

The oscilloscope has always been the workhorse of the digital circuit designer. This is still true today, especially for designers working to advance the state of the art in processes and technologies. Three trends pose a particular challenge to oscilloscope manufacturers if they are to continue to provide a useful tool for the digital designer: the increasing speeds of digital circuits, their increasing complexity, and the rate of turnover in technologies and products.

Not only are designers turning to faster logic families such as ECL 10KH and 100K, but semiconductor technologies are constantly undergoing improvement. With TTL and even CMOS now commercially available with edge transition times and gate delays approaching one nanosecond, an oscilloscope must have a 1-GHz bandwidth to be truly useful when working with these logic families

As system speeds increase, bus cycle and memory cycle times shrink. With more going on in less time, the designer must pay stricter attention to precise timing. Transmission line characteristics are becoming more important. With a shorter cycle time, solutions to timing problems that may have worked in the past will no longer suffice. For example, with no extra time in the bus-cycle-time budget, the designer may not be able to slow down the clock rate or reshuffle events within the allotted time. With this increased emphasis on precise timing, good analog

Fig. 1. HP 54110D Digitizing Oscilloscope adds a color display and other functions to the features of the HP 54100D.

design techniques are essential to the success of digital designs. The oscilloscope is the most useful tool for characterizing the analog performance of digital circuits.

Examples of increasing logic speed are not limited to semiconductor gate delays and transition times. Disc drive manufacturers strive to pack more bits per square inch on the surface, which translates to higher data rates in both read and write circuits. Fiber optics and satellite communications offer the attraction of getting more information to more places faster and with fewer errors, pushing data rates up to gigabits per second. Local area networks, data multiplexers, and the computers' internal buses must all go faster to keep up with the logic circuits' ability to perform mathematical operations on numbers faster.

#### Oscilloscope Requirements

A 350-ps rise time, by itself, is not sufficient for an oscilloscope to make the required measurements. The precision, resolution, and range of time interval measurements are probably the most important attributes of an oscilloscope. The most basic measurement expectation of an oscilloscope is to measure the time between events on waveforms. How long after the driver started its transition did the input to the last RAM pass through logic low? How far from the center of the data window was the peak of a pulse on a disc drive? By how much time do the edges of the clock vary in different parts of a system?

In complex digital systems, it is important to be able to view events leading up to the trigger. Otherwise, it is difficult if not impossible to determine the cause of events. In an asynchronous system, where cycle times are not always the same, reliably measuring such basic parameters as setup time requires the ability to display events before the trigger.

One of the most frustrating behaviors of complex digital circuits for digital designers is the tendency for catastrophic errors, which occur very infrequently. Digital systems have an almost infinite number of states they can occupy, and an erroneous operation may be related to only one of these states (which the system has a very low probability of being in at any time) or, worse yet, to a unique sequence of states. Even normal, periodic events, such as an individual pulse on a disc drive, may have a very low duty cycle in a complex digital system. It is difficult for the digital designer to see such events using a conventional oscilloscope. The infinite persistence mode on the HP 54100A/D retains information on the display indefinitely, so the designer can see

those very infrequent error conditions, as well as examine signals having a very low duty cycle.

Faster means smaller and denser, since distance is proportional to time in electric circuits. As circuits become denser, they become harder to probe. Frequently, the hardest part of making an oscilloscope measurement is probing the desired signal. At the same time, the effect of the probe on the circuit under test, and the distortions introduced by the probe and its grounding path on the signal going to the oscilloscope, are often the dominant source of error in high-bandwidth oscilloscope measurements; this effect becomes more pronounced at high speeds. Therefore, a truly general-purpose oscilloscope must offer solutions to the conflicting requirements of probing: small physical dimensions, low mass, high bandwidth, and minimum loading (particularly capacitive loading).

Chips, the simplest and lowest-level circuit building blocks, are rapidly becoming more complex, with many more functions and connections. Examples range from gate arrays to fiber optic receivers. Today's board is tomorrow's chip. As this happens, the number of variables in their transfer function increases exponentially, and the number of opportunities for errors that have an undesired impact on system operation increases proportionally. To characterize such a circuit—and especially to troubleshoot it if it isn't working properly—may require thousands of measurements.

Thus, the designer needs instruments—including oscilloscopes—that can be programmed to make measurements automatically. A truly general-purpose oscilloscope must be programmable, but shouldn't require a doctorate in computer science to program effectively. This makes it possible to program computers to take over the repetitive tasks of setting up measurements and of gathering, sorting, and analyzing the data. A newgeneration oscilloscope must also be easy to operate manually. All the measurement features in the world are of little benefit if they are obscured by an arcane control architecture, or hidden in a bewildering array of buttons and knobs.

Meeting all of these requirements was the basis of the design objectives for the oscilloscopes discussed in this issue.

Arthur W. Porter Product Marketing Engineer Colorado Springs Division

(continued from page 4)

programmed to count the correct number of sample periods (greater than 1024) to reach the time window of interest. Using a crystal to control the sample clock guarantees high time base stability. Very long delays can be achieved without the long time base ramps required in conventional oscilloscopes. This leads to low overall time base jitter and

counter-like time base accuracy.

The availability of very high time resolution leads to the possibility of high bandwidth. By designing a high-bandwidth sample-and-hold circuit and using random repetitive techniques, we can achieve very high bandwidth. In the case of the HP 54100A/D we achieve bandwidth

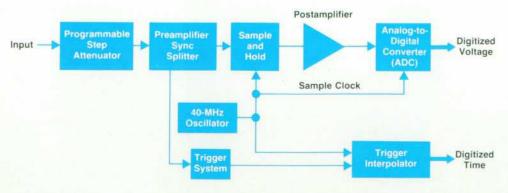

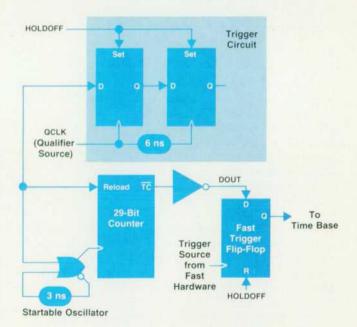

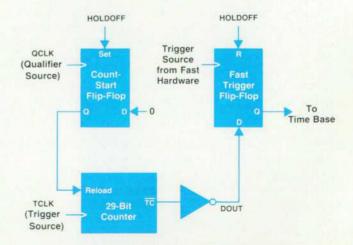

Fig. 2. Simplified block diagram of the HP 54100A/D data acquisition system.

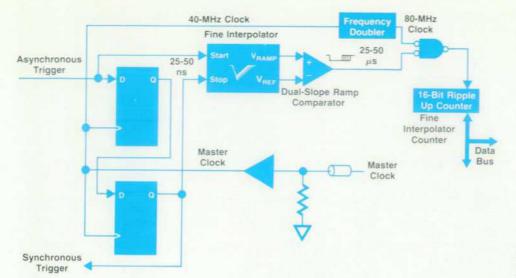

Fig. 3. Fine interpolator block diagram.

orders of magnitude higher than the sample rate. The rise time is limited by the bandwidth of a hardware preamplifier and sampler and not by the sample rate.

The advantages of accurate, stable, high-resolution timing and high bandwidth do not come free, however. There is one significant disadvantage of random repetitive sampling. If the sample rate is limited to 40 MHz as it is in the HP 54100A/D, then there exists a 25-ns hole between two data points taken on the same trigger. There is a finite probability that a time window narrower than 25 ns might not receive any data from a given acquisition cycle or trigger event. A 10-ns window will have a probability of only 10/25 of receiving one data point given one acquisition cycle, and a 1-ns window will have a probability of 1/25. Therefore, for a 1-ns window of interest, the signal must repeat 25 times on the average for each data point plotted on the screen. Because the data points are stored digitally and do not fade away, this effect is minimized. For a 1-ns time window (100 ps/div) and a signal repetition rate of 1000 Hz, the HP 54100A/D can still accumulate 40 digitally stored points per second, and the data rate goes up proportionally with signal repetition rate and time window width, reaching rates as high as 50,000 data points per second.

The realization of random repetitive sampling required the development of several new circuits. Fig. 2 illustrates

Sync Out

Sync Out

Main Out

Fig. 4. Basic elements of the preamplifier and sync splitter.

in greatly simplified form the basic components required. The circuits to be described in this article are the preamplifier/sync splitter, the sample-and-hold circuit, and the trigger interpolator. The programmable step attenuator is similar to the HP 33321G Attenuator. The trigger system is discussed in detail in the article on page 26. Two Siemens SDA 6020, 6-bit, 50-MHz flash ADCs are stacked to get seven-bit resolution at 40 MHz in the HP 54100A/D.

#### Fine Interpolator

The role of the fine interpolator is to provide the timing information that is necessary to reconstruct waveforms from multiple acquisitions of digitized data. The basic time base accuracy of the instrument is also set by the operation of this circuit. Fig. 3 shows a block diagram of the fine interpolator circuit. Its function is to measure very accurately the time between the trigger event and the next occurrence of the system master clock. Knowing the individual times allows reconstruction of random repetitively sampled waveforms from raw data.

Circuit operation begins with a block called the synchronous trigger generator. It has two inputs, the master clock and the asynchronous trigger coming from the trigger system discussed elsewhere in this issue. The synchronous

Fig. 5. Sampler kickout. Vertical: 5 mV/div. Horizontal: 200 ps/div.

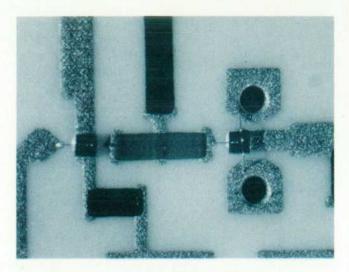

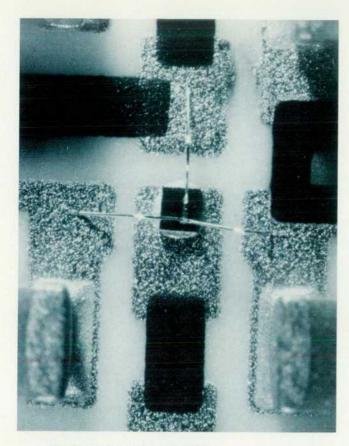

Fig. 6. Preamplifier thick-film hybrid substrate.

trigger generator consists of two high-speed ECL D flipflops. The output of the circuit is another trigger signal that is coincident with the second occurrence of the master clock after the initial trigger is generated. The flip-flops are necessary to ensure that no false synchronous triggers are generated because of operation in a metastable region. Because of the random nature of the two inputs, the setup and hold specifications are by design often violated.

This output signal is referred to as the synchronous trigger. Because the asynchronous and synchronous triggers are related only by the master clock, the actual time difference is a random time between 25 ns and 50 ns, or one period of the 40-MHz master clock. This time is stretched by a factor of 1250 by the dual-slope analog-to-digital converter—the heart of the fine interpolator. This ADC consists of a high-speed differential comparator that switches a 10mA reference current. The reference current discharges a capacitor for 25 to 50 ns. The capacitor is then charged from a current source 1250 times smaller than the discharge current. The ratio of the currents is the expansion ratio of the interpolator. The discharge is the fast ramp and the charge is the slow ramp of the dual-ramp circuit. The ramp is an input to a comparator that produces a logic output that is equal in time to the stretched or slow ramp time. The logic output enables a 16-bit counter that counts an 80-MHz clock derived from the master clock. This doubling in frequency is necessary to achieve 10-ps resolution for the system. The resultant digital word is then grouped with the digitized sampled data from the vertical system for reconstruction of the measured waveform.

#### Preamplifier

Typically the preamplifier in a conventional oscilloscope terminates the input signal and splits it into the main and sync paths. Isolation between the two paths is important, but is not a major constraint because the main path typically drives a terminated transmission line. For a random repetitive sampling system, however, the design constraint is different. The sampling process, by its very nature, generates a charge disturbance at the sampling bridge that propagates towards the preamplifier in the opposite direction

Fig. 7. Preamplifier step response. Vertical scale: 0.05V/div. Time scale: 200 ps/div.

from the input signal. Should the disturbance not be blocked by the preamplifier and couple into the sync path, it could cause a trigger event synchronous with the system master clock to occur. This would cause an erroneous trigger, or more likely, one that is statistically related to the master clock. The more the signals are coupled, the less random the acquisition of data.

Fig. 4 shows a schematic representation of the basic elements of the preamplifier and sync splitter. Because the circuit must pass the input signal with a bandwidth well in excess of 1 GHz, it is fabricated using a custom thick-film hybrid on a ceramic substrate. This is necessary to achieve fine geometries and low parasitic capacitance. The circuit is essentially a two-transistor differential amplifier with emitter resistors that reduce the gain and help stabilize the circuit. The first transistor splits the input signal into two parts—the main and sync signals. The second transistor is a common-base stage with its main function being to block any unwanted signal from the sampling bridge from coupling into the sync signal.

Fig. 5 shows a measurement made of "kickout" from the sampling bridge; this must be significantly attenuated before coupling into the sync signal. The design goal was to achieve 35-dB isolation between the preamplifier output and the sync output. The ingredients necessary to achieve, this with the common-base stage were very low collector-to-emitter capacitance and near-zero base impedance to ground at 1 GHz. The latter was achieved with dual base

Fig. 8. Equivalent circuit of a track-and-hold or sample-and-hold circuit.

Fig. 9. Transmission line loading on a sampler

bond wires that go directly to conductive vias (holes) near the die location. Total inductance at the base has been measured at 0.5 nH, which is sufficiently low to achieve the desired low impedance at that terminal. Fig. 6 is a photograph of the implementation on the preamplifier substrate. Fig. 7 shows the output response of the circuit measured at the main output with a 40-ps rise time stimulus. Note that the response has no overshoot and has a rise time of 200 ps.

#### Random Sampler

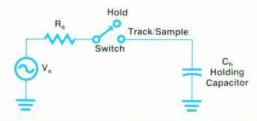

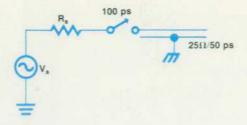

The key to extending the bandwidth of a digitizing oscilloscope without having to increase the digitizing rate is narrow-aperture sampling. Currently, there are two techniques used to achieve the narrow-aperture effect. The track-and-hold method is most commonly used at low frequencies where the required switch can be put into a feedback loop to reduce the nonlinear effects. The HP 54100A/D uses sample-and-hold methods because of the many advantages offered at high frequencies. The equivalent circuit used to illustrate these two methods is shown in Fig. 8. The circuit consists of a source voltage (V<sub>s</sub>) to be measured and the associated back impedance (R.) of the source, a switch, and a holding capacitor loading the switch. In a track-and-hold circuit, the switch is closed for relatively long times, and in this mode the voltage on the capacitor must track the source voltage. Then at a prescribed instant, the switch is opened. If the switch, being an electronic device (typically a diode bridge), changes state from low resistance to high resistance quickly, then a narrow aperture effect can be realized, that is, the voltage on the capacitor is held and is not affected much by the turn-off

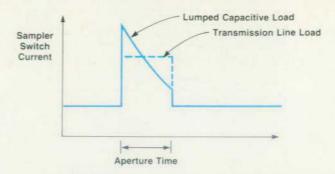

Fig. 10. Sampler switch current for lumped C or transmission line loading.

transient. However, in the track mode, the input signal is filtered through the source resistance and holding capacitance, limiting the bandwidth of the output signal. This filtering effect and the excess time used in tracking the signal limit the usefulness of track-and-hold methods at high frequencies.

Operating the same circuit in the sample-and-hold mode alleviates these two problems, but introduces more. A sample-and-hold circuit closes the switch only briefly (about 100 ps in the case of the HP 54100A/D), removing a small amount of charge from the source. This charge, when integrated on the hold capacitor, generates a voltage proportional to the average value of the input signal over the sampling aperture time (100 ps). There is typically a net voltage transfer loss with a sample-and-hold circuit because the short sampling aperture offers insufficient time for the voltage on the capacitor to achieve a steady-state value. The loss in voltage is called sampling efficiency. For example, if  $R_{\rm s}$  is  $25\Omega$ ,  $C_{\rm h}$  is 2 pF, and the sampling aperture  $T_{\rm s}$  is 100 ps, the sampling efficiency  $N_{\rm s}$ , which is given by:

$$N_s = 1 - e^{-T_s/R_sC_h}$$

is about 86%.

In designing the HP 54100A/D, we found that the sampling efficiency could be improved by loading the sampling switch with a distributed capacitance or transmission line

Fig. 11. Simplified schematic diagram of the sampling circuit.

Fig. 12. Simplified postamplifier schematic diagram.

rather than a lumped capacitor. If, as shown in Fig. 9, we load the sampler with a  $25\Omega$  transmission line 50 ps long. then with a sampler aperture of 100 ps, the initial wavefront moving down the transmission line reflects off the end of the open line, returns to the switch just as the switch opens, and is trapped on the line. For this case, the sampling efficiency is exactly 100%. The efficiency can be made greater or less than 100% by making the transmission line load greater or less than 25 $\Omega$ . The total capacitance of the transmission line load is 50 ps  $\div$  25 $\Omega$ , or 2 pF, the same as the previous example, but we have increased the sampling efficiency by 14%. Another advantage of transmission line loading is greater uniformity of current flowing through the sampling switch during the aperture time. The initial current flowing into a lumped capacitor load is twice the current flowing into the matched  $25\Omega$  line, and decreases exponentially over the aperture duration while the current into the transmission line is constant (Fig. 10). The lower peak current leads to improved linearity for large signals.

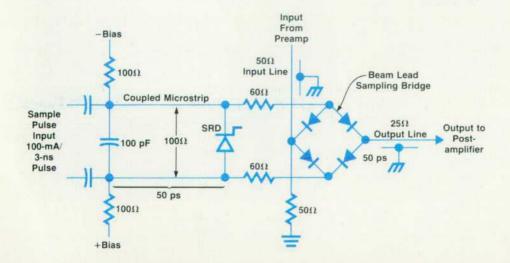

Fig. 11 illustrates the relationship between the input circuitry, the output circuitry, and the sample strobe generation circuitry used in the HP 54100A/D. This circuit is realized as a thick-film microcircuit. The input travels down a  $50\Omega$  microstrip transmission line past the sampling bridge and is terminated in a  $50\Omega$  load. The sampling bridge taps the input line and connects to the output  $25\Omega$  microstrip line on the right. To the left of the input line is the sample strobe generation circuit. The primary source of the fast edge pulse used to turn the sampling bridge on is the step recovery diode (SRD). This diode generates a 10V, 50-psrise-time edge. The circuitry to the left of the SRD serves the dual purpose of matching the signal from the sample pulse generator to the SRD as well as shaping the 100-ps sample strobe pulse. The SRD is normally biased with current flowing from the positive bias supply through the SRD and out the negative bias supply. If the bias supplies are balanced, the positive and negative reverse bias of the sampling bridge is equal to half the SRD forward bias. To initiate sampling, a 100-mA, 3-ns-wide current pulse is applied from the sample pulse generator into the matching network with such a polarity as to reverse-bias the SRD.

When forward-biased, the SRD acts as a short circuit. It continues to act as a short circuit under reversed-bias cur-

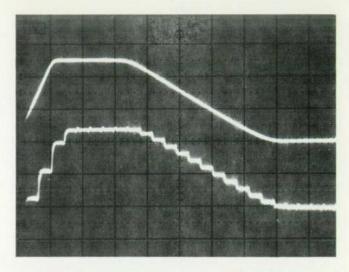

Fig. 13. A ramp-type input to the sampler and the output of the postamplifier held in steps 25 ns apart.

rent conditions until the stored charge in the diode goes to zero, at which time the diode quickly changes to an open circuit. In this case, there is sufficient bias current to allow the reverse current to reach about 100 mA before the diode opens. When the diode charge goes to zero, the 100-mA current is suddenly (<50 ps) interrupted, and a portion of the current is forced to flow through the  $60\Omega$  resistors into the sampling bridge. The rest of the current flows back into the  $100\Omega$  coupled microstrip structure where it is shorted by the 100-pF capacitor and is reflected back toward the SRD. When the wavefront reaches the SRD, it again forward-biases the SRD, causing the current flowing into the sampling bridge to turn off. The strobe time and thus the aperture time of the sampler are fixed at 100 ps by the two-pass length of the coupled microstrip. During this aperture time, the sampling bridge shorts the input line to the output line, allowing current to flow from one to the other. The amount of charge transferred into or out of the load capacitor is proportional to the difference between the

Fig. 14. Sampling efficiency adjustment. A step input to the sampler and the postamplifier output for three settings of the FET drain resistance.

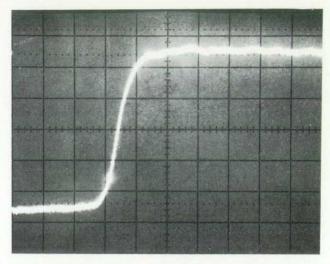

Fig. 15. Reconstructed sample step response has a rise time of 130 ps. Time scale: 50 ps/div.

input and output voltages. If the sampling efficiency is not exactly equal to 100%, then the first sample taken after a step change in the input signal will not be correct, but subsequent samples will measure the difference between the input and the output and reduce the error to zero. To minimize this error on the first sample, the sampling efficiency must be as close to 100% as possible.

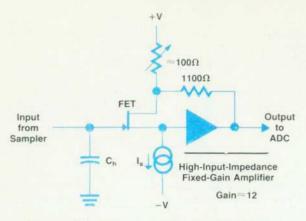

The sampling efficiency depends on the load capacitance. If there were other parasitic capacitances in parallel with the load capacitor, such as the input capacitance of an amplifier needed to boost the output signal to a sufficient level to be digitized, then the sampling efficiency would not be 100%. Therefore, the postsampler amplifier must have zero input capacitance. In fact, if there are any vari-

ances in the load capacitance because of thick-film process variations, the input capacitance of the postamplifier might have to be negative to compensate for other parasitics. The design of the postsampler amplifier is therefore not a trivial matter, especially since its output must settle and be digitized at high rates (40 MHz in the HP 54100A/D).

Fig. 12 illustrates the postamplifier used in the HP 54100A/D. A source follower input stage is used with bootstrapping to reduce the effect of gate drain capacitance. In a normal case, the positive feedback to the drain is 100% (i.e., the drain voltage change is forced to be equal to the gate voltage change). Then the effective load capacitance of the FET is zero. The  $100\Omega$  resistor in the drain circuit can be trimmed, allowing the  $\pm 0.2$ -pF input capacitance to compensate for variances in the total holding capacitance according to:

$$C_{\rm in} = C_{\rm gd} (1 - A_{\rm fb}),$$

where  $A_{\rm fb}$  is the positive feedback gain and  $C_{\rm gd}$  is the gate-to-drain capacitance of the FET.

If  $A_{fb}$  is greater than unity, the input capacitance of the amplifier can be negative. This does not cause a stability problem, however, because the holding capacitor makes the total capacitance of the node to ground positive.

Altogether the sampler serves to measure the instantaneous value of an input signal and hold this value to be digitized at a 40-MHz rate. Fig. 13 shows a ramp type input to the sampler, and the output of the postamplifier held in steps 25 ns apart.

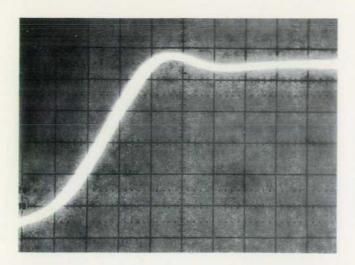

Fig. 14 illustrates a step-like input to the sampler and the output of the postamplifier for three settings of the FET drain resistance. Fig. 15 is a reconstructed image of the sampler step response to an HP tunnel diode step generator. The rise time of this sampler is about 130 ps, indicating a bandwidth of about 2.7 GHz.

## High-Performance Probe System for a 1-GHz Digitizing Oscilloscope

by Kenneth Rush, William H. Escovitz, and Arnold S. Berger

TYPICAL SYSTEM to be measured by an oscilloscope usually contains not just one class of signal, but several classes. Making signals from these different classes available to the measuring oscilloscope is the goal of the probing system for the HP 54100A/D Digitizing Oscilloscope.

The probing system consists of the following products:

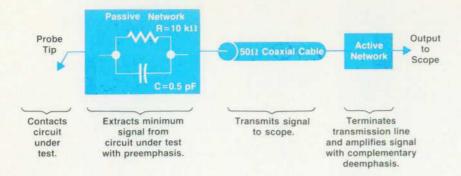

- The HP 54001A 1-GHz Miniature Active Probe

- The HP 54002A 50Ω Input Pod

- The HP 54003A 1-MΩ Probe

- The HP 54300A Probe Multiplexer.

Circuits that are sensitive to capacitive loading are usually fast circuits having low resistances. For this class, the probe capacitance dominates the design trade-offs. Fast circuits, say ECL 100K, also demand a high-bandwidth probe to preserve the shape and timing of the signal sent to the oscilloscope. The HP 54001A Miniature Active Probe is the optimum probe for this class of signals. This probe's pole-zero cancellation technique results in an extremely small probe tip with low capacitance (2 pF), medium resistance (10 k $\Omega$ ), and extremely high bandwidth (1 GHz). In size and bandwidth, the HP 54001A is an improvement

Fig. 1. Block diagram of the HP 54001A Miniature Active Probe.

over previous active probes.

A large class of signals exists in a  $50\Omega$  environment of coaxial connectors. The requirements of  $50\Omega$  terminated coaxial signals cannot be met easily by other probing solutions, so the HP 54002A was designed to cover this class. The HP 54002A offers low insertion loss and good termination.

Circuits that are sensitive to resistive loading (i.e., having resistances above a kilohm) are usually slow circuits and are not so sensitive to capacitive loading. A probe can be optimized for this class of circuits by keeping the probe resistance high at the expense of probe capacitance. Such is the case with the HP 54003A. The HP 54003A probe offers equivalent performance to conventional oscilloscope probes, high resistance (1 M $\Omega$ ), moderate capacitance (8 pF), and relatively high bandwidth (300 MHz) for requirements where resistive loading is more important than capacitive loading.

The idea that allows these products to make a significant contribution is a system of interchangeable pods and a method of multiplexing the outputs of the pods into an oscilloscope. The HP 54300A Probe Multiplexer allows these probes to form a measurement solution. Now signals from several classes of circuits can be brought together and measured in one system. Low-speed, high-resistance oper-

Fig. 2. Gain of HP 54001A probe components versus frequency.

ational-amplifier signals can be measured by the HP 54003A and multiplexed with high-speed ECL signals measured by the HP 54001A. Amplifier outputs in  $50\Omega$  coax can now be measured in the same system as the low-power CMOS used to program the amplifier gain.

#### Miniature Active Probe

Careful consideration of noise, bandwidth, and loading effects led to some unusual design concepts in the HP 54001A. The single most significant problem in designing an oscilloscope probe is dealing with the cable capacitance. The cable capacitance in a conventional probe is part of a capacitive voltage divider. Hence, the higher the cable capacitance, the higher the probe tip capacitance must be. Historically, designers have used several methods to minimize cable capacitance. One common method is to make the cable short, since capacitance is proportional to length. Unfortunately, this leads to probes that are often too short to bridge the gap between the circuit under test and the oscilloscope. Another method is to make the cable have very high impedance. If we could realize a 150 $\Omega$  cable, it would have one-third the capacitance of a  $50\Omega$  cable. Unfortunately, high-impedance coaxial cable tends to have a large outer diameter. Carrying both of these techniques to their extremes-maintaining sufficient length to be useful, and maintaining a small diameter cable—yields the HP 54003A, which is similar to the HP 10017A passive probe, having a tip capacitance of about 8 pF.

Other techniques have been used to reduce tip capacitance, but they usually have severe drawbacks. First, plac-

Fig. 3. Simplified schematic of the active network in the HP 54001A Miniature Active Probe.

ing an amplifier near the probe tip to drive the cable capacitance eliminates the tip impedance's dependence on cable properties, but power must be supplied to the amplifier, and it takes up space, making the probe tip large. Second, the cable could be considered as a transmission line and terminated as such as in resistive divider probes. However, this leads to probes with very low resistance at the probe tip— $500\Omega$  for a 10:1,  $50\Omega$  probe such as the HP 10020A.

Obviously a new approach was needed to produce the ideal probe for high-speed logic. To achieve higher bandwidth in a longer probe requires low-loss, high-quality coaxial cable terminated in a  $50\Omega$  impedance. The small tip size restraint requires a passive tip. The requirement of high resistance forces us to introduce gain into the system to terminate the cable in  $50\Omega$ . One approach might be to use a resistive divider probe with a high division ratio, followed by an amplifier to make up the gain loss. This poses two problems. First, gain at very high frequencies (>300 MHz) is not easy to get, and if we could get it, the gain would add noise to the system. However, if we are willing to remove more signal from the circuit under test using slight capacitive loading, we will not be attenuating the signal as much at high frequencies. Thus, less gain is required. This is the method used in the HP 54001A probe.

Fig. 1 illustrates the concept in a block diagram. In the probe tip, a thick-film microcircuit is used to realize an RC passive network. The resistance is a laser-trimmed, thick-film resistor. The capacitance is the front-to-back capacitance of a couple of metal traces on the ceramic substrate and has a value of 0.5 pF.

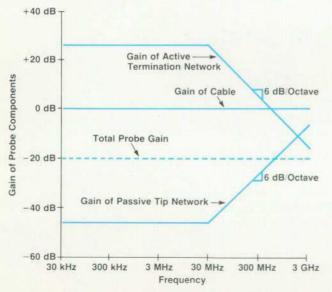

Fig. 2 illustrates the transmission gain of the passive tip network and the active network gain required to get a total probe gain of -20 dB (10:1). Note the transmission zero caused by the parallel action of the resistance and capaci-

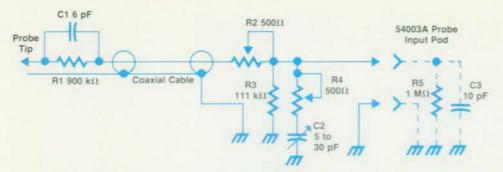

Fig. 4. Block diagram of the HP 54003A 1-M $\Omega$  Probe input pod.

**Fig. 5.** Basic circuit of the high-frequency thick-film hybrid for the HP 54003A 1- $M\Omega$  Probe input pod.

tance in the probe tip. This transmission zero must be cancelled in the active network with a pole at 30 MHz. Below 30 MHz, the passive network has a loss of 46 dB, and the active network must have a gain of 26 dB while the coaxial cable has no loss or gain. Above 30 MHz, the gain of the passive network increases at 6 dB/octave, while the active network gain decreases at 6 dB/octave, yielding a constant -20-dB gain over the frequency range of the probe. The required gain of the active network goes through 0 dB at about 630 MHz.

The requirements on the active network are rather severe. It must terminate the coaxial cable in its characteristic impedance of  $50\Omega$ , boost the signal by 26 dB below 30 MHz, roll off its gain at -6 dB/octave to well past the desired bandwidth of the probe, and drive the  $50\Omega$  input of the oscilloscope to a reasonable dynamic range of  $\pm 2$  V, giving a 20V dynamic range at the probe tip (10:1 probe). Thickfilm hybrid microcircuit technology is used to realize the circuit.

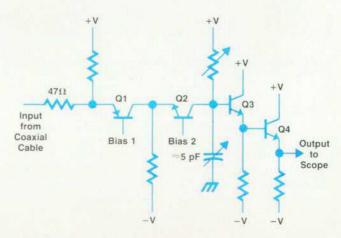

Four discrete microwave transistors are used in cascade. Fig. 3 illustrates the circuit. Transistor Q1 and the  $47\Omega$ resistor in series with its emitter terminate the coaxial cable in its characteristic impedance. The base bias of Q1 is automatically adjusted with an operational-amplifier feedback circuit to guarantee that the input offset is zero volts. Q2 acts as a buffer to isolate the high impedance at its collector from the low impedance of the active network input. At the collector of Q2 is an RC network that generates the required current-to-voltage conversion of the signal current passing through Q1 and Q2. The resistive and capacitive values are trimmed at calibration to guarantee a match with the passive network to achieve the proper gain at all frequencies. Q3 and Q4 form a cascade of emitter followers to isolate the high-impedance node at the base of Q3 from the low impedance of the output node.

The overall performance of this probe is limited by the choices of the passive network values. Obviously, if we made the tip resistance extremely high and the tip capacitance extremely low, we would have an extremely small signal to work with, making recovery and measurement of the signal very difficult. The capacitance value chosen vields a total probe tip capacitance of about 2 pF. This gives less than a 3% increase in rise time for a  $50\Omega$ , 1-nsrise-time resistive source. The 10-k $\Omega$  resistance gives about 0.5% dc loading error on a  $50\Omega$  source. The ultimate bandwidth of this approach is limited primarily by the thick-film active network, and in the case of the HP 54001A probe, this exceeds 1 GHz. The cable losses, primarily caused by skin effect, form a secondary limitation on bandwidth. First-order compensation for these losses is done by an overadjustment of the active network trim capacitor.

#### 1-MΩ Probe

Although the HP 54100A/D is a 1-GHz oscilloscope with 50 internal signal paths, its digital architecture, HP-IB control, and automatic measurement capabilities make it useful at much lower frequencies. To take advantage of this, the HP 54003A 1-M $\Omega$  Probe was designed. It is a unity-gain, general-purpose, 300-MHz input buffer amplifier with a 1-M $\Omega$ , 10-pF input. It requires an external HP oscilloscope probe. Probes for it include the HP 10017A 1-M $\Omega$ , 8-pF miniprobe, the HP 10014A 10-M $\Omega$ , 10-pF standard probe, and the HP 10032A 100:1 Probe. Its bandwidth of 300 MHz and its rise time of 1.2 ns are specified both at the BNC input and at the probe tip. It is useful for circuits ranging from high-impedance operational amplifiers to ECL logic circuits to power supplies up to 200V.

Most oscilloscope amplifiers are preceded by attenuators, which limit the dynamic range that the amplifiers must cover. The HP 54100A/D has  $50\Omega$ , 1-GHz attenuators

already built into it, so the HP 54003A buffer amplifier must have a large dynamic range. The dynamic range is  $\pm 2V$ , which covers most digital circuit and operational-amplifier applications with a  $\times 10$  probe. This is about twice the dynamic range of buffer circuits in active probes and oscilloscope inputs.

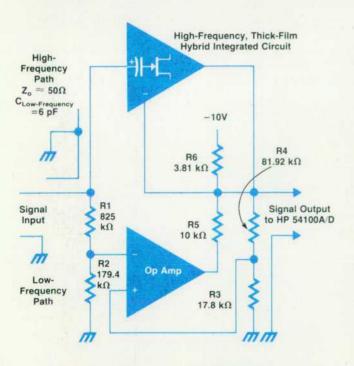

As shown in Fig. 4, the HP 54003A is a two-path amplifier. Signal components less than about 1 MHz pass through the low-frequency path, an operational-amplifier circuit, then to a low-frequency input of the high-frequency amplifier. The operational amplifier also controls the operating point of the high-frequency amplifier.

Signal components higher than 20 Hz also follow the high-frequency path. There is sufficient overlap of the two circuits' passbands to ensure a smooth total response. Because of the closed-loop design and modern operational-amplifier stability, there is almost no visible drift. Also, the high open-loop gain of operational amplifiers means that 0.1% resistors R1, R2, R3, and R4 accurately and repeatably set the low-frequency gain to:

$$A = \{R2/(R1 + R2)\} \{(R3 + R4)/R3\}.$$

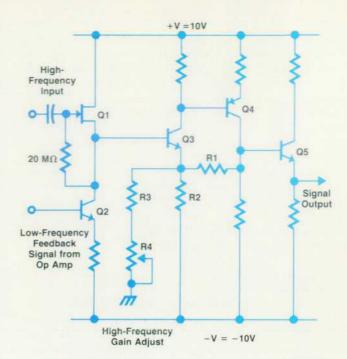

One adjustment in the high-frequency amplifier sets the high-frequency gain equal to the low-frequency gain so that the overall response is flat. The high-frequency circuit (Fig. 5) is a unity-gain amplifier with input, gain, and output sections. Because the input and output sections are followers with gain less than 1, a gain section is necessary. Transistors Q1 and Q2 make up the input section. FET source follower Q1 is operated at gate-to-source voltage  $V_{\rm gs}\!=\!0$ , maintained by the 20-M $\Omega$  gate-to-source resistor. However, the Miller effect between the gate and source causes the input impedance to be much greater than that resistance. The input resistance does not significantly load the 1-M $\Omega$  input resistor of the low-frequency operational-amplifier

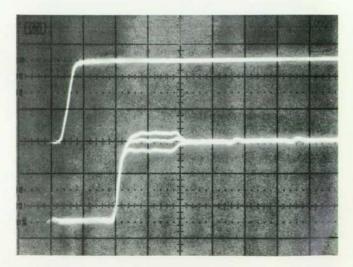

Fig. 6. Response of the HP 54003A probe input pod with the HP 10100C 50 $\Omega$  feedthrough terminator and artificially long 600mm  $50\Omega$  cable as a stub, with the HP 10100C directly on the HP 54003A input pod, and with no HP 10100C. The 50Ω feedthrough terminator with stub creates 33% overshoot (top trace). The HP 54003A input line as a stub (middle trace) causes less overshoot because it is fairly short for this bandwidth. Proper use of the HP 54003 A is without feedthrough terminator (bottom trace).

Fig. 7. Schematic diagram of the HP 54003-61617 1-M $\Omega$ , 8-pF, 10:1 oscilloscope probe (same as the HP 10017A).

circuit. The feedback input from the operational-amplifier circuit maintains the proper current in Q1 and Q2 for FET operation at  $V_{\rm gs}\!=\!0$  regardless of the input bias level within the  $\pm 2V$  dynamic range and regardless of individual FET variations.

The gain stage is the common-emitter/common-emitter circuit of Q3 and Q4 with voltage series feedback. Resistors R1 through R4 make up the feedback network. R4 is adjusted so that the high-frequency amplifier gain is equal to the low-frequency operational-amplifier circuit gain.

The high-frequency circuit is implemented as a thick-film hybrid. The technology is described in the article on page 33. The short length of chip-to-substrate wire bonds and repeatable geometry of traces minimize variable parasitic impedances at 300 MHz. This produces consistently high-performance circuits.

The HP 54003A input should be driven from a 50 $\Omega$  source or oscilloscope probe such as the HP 54003-61617 (HP 10017A). Although the input capacitance is about 10 pF. the BNC input connector and the input line look like a  $50\Omega$  transmission line terminating at the input capacitance of the high-frequency amplifier, which is only about 2 or 3 pF. Thus, a  $50\Omega$  source can drive the input well beyond 300 MHz. It is common to terminate high-impedance inputs with  $50\Omega$  feedthrough terminators, such as the HP 10100C, to reduce reflections in high-frequency measurements. However, this causes overshoot with fast rise time signals because of the inevitable stub of BNC connector and buffer amplifier input line. For a long stub, the overshoot is 33%. Instead of a feedthrough termination, it is better to use a  $\times 5$  or  $\times 10~50\Omega$  attenuator at the BNC input if the signals are large enough. If the source impedance is close enough to  $50\Omega$ , no termination or attenuator is necessary. Fig. 6 shows how the waveform varies for three different terminations. Only analysis of individual cases reveals the best termination, if any, to use with high-impedance inputs. Of course, the HP 54002A  $50\Omega$  Input Pod is best for dedicated use in a  $50\Omega$  system.

Most high-impedance inputs are used with probes to characterize or troubleshoot circuits. Probes represent the highest-resistance, lowest-capacitance, lowest-disturbance connection to circuits that do not have buffered 50Ω test points. The main probe for the HP 54003A is the HP 54003-61617, which is identical to the HP 10017A Miniature Divider Probe (Fig. 7). It is designed to drive 1-M $\Omega$  inputs with approximately 10 pF input capacitance. Up to about 10 MHz, it is a capacitor-compensated 10:1 resistive voltage divider. The divider consists of the parallel combination of R1 and C1 in series with the parallel combination of R3, R4, R5, C2, C3, and the cable capacitance. The R2 and R4 network terminates the characteristic impedance of the cable at very high frequencies, where transmission line effects in the cable become important. The center conductor of the cable is resistive to damp out remaining reflections.

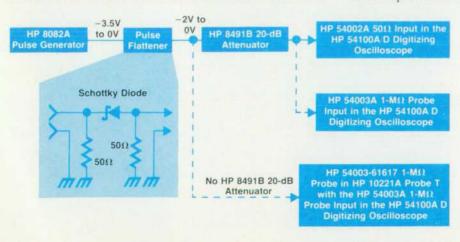

#### 1-MΩ Probe Performance

Fig. 8 is a block diagram of some of the equipment used to characterize the high-frequency performance of the HP 54003A. It produces flat pulses of approximately 1-ns rise time, typical of the fastest pulses the HP 54003A can usefully measure. The pulse flattener is a Schottky diode series clipper. When the HP 8082A output is negative, it is connected to the pulse flattener output through the diode, which is turned on. When the HP 8082A output returns to 0V, it is connected to the flattener output only through the diode capacitance, about 1 pF. The output of the flattener returns rapidly to 0V through the  $50\Omega$  output resistor. The small capacitance of the turned-off diode filters the pulse-

Fig. 8. Equipment to produce flat pulses for characterizing oscilloscopes and probes.

Fig. 9. Response of the HP 54100 A/D with the HP 54002A  $50\Omega$  probe to a 1-ns rise time reference pulse (top trace), compared with the response of the HP 54003A 1-M $\Omega$  input pod (bottom trace).

top aberrations of the pulse generator, which are already small, and the  $50\Omega$  output resistor reduces reflections when the diode is off. The 20-dB attenuator is a nearly  $50\Omega$  load for the pulse flattener regardless of the device under test. The HP 8082A's amplitude and offset are adjusted to produce the flattest reference pulse near the pulse transition.

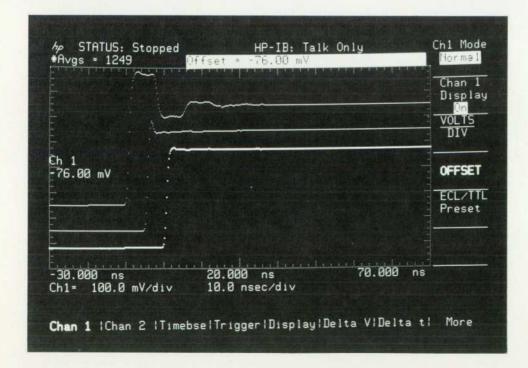

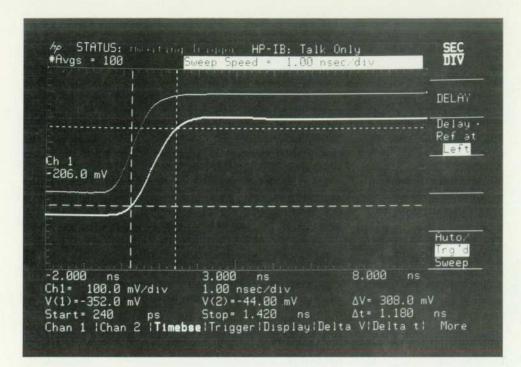

Fig. 9 shows the response of the HP 54100A/D with the HP 54002A  $50\Omega$  input (top trace, the reference pulse) and the HP 54003A 1-M $\Omega$  input (bottom trace). The reference trace has a 1.02-ns rise time and aberrations of about 1% peak-to-peak for the first 10 ns, which require the HP 54100A/D's magnify mode to see. The HP 54003A trace

has a rise time of 1.18 ns and about 2% overshoot compared to the reference pulse.

Fig. 10 compares the performance of the HP 54003A and the HP 54003-61617  $\times 10$  miniprobe (bottom trace) with the reference trace. No attenuator is used because the probing tee is already terminated in  $50\Omega$ . The rise time with the probe is 1.09 ns and the perturbations are about 3% peak-to-peak. The 1.09-ns rise time of the probe compared to the 1.02-ns rise time of the reference waveform or the 1.18-ns rise time of the HP 54003A itself does not mean that the 1-M $\Omega$  probe is exceptionally fast, but only that it can be tuned using its adjustable termination resistors.

Fig. 10. Response of the HP 54100A/D with the HP 54002A  $50\Omega$  probe to a 1-ns rise time reference pulse (top trace), and the response of the HP 54100A/D with the HP 54003A 1-M $\Omega$  probe input pod and the HP 54003-61617 1-M $\Omega$  miniprobe (bottom trace).

Fig. 11. The HP 54300A Probe Multiplexer, shown with the HP 54100A Digitizing Oscilloscope.

#### Probe Multiplexer

As previously discussed in this article, the difficulties associated with probing a circuit increase as the circuit's density and frequency limits increase. One manifestation of this problem is probing multiple nodes in a complex system. Quite often, the mechanical fixturing needed for probing points of interest in a circuit must be designed into the circuit itself. Thus, part of an overall probing strategy must address the need for a greater number of probes than can be accommodated by an instrument's input.

The HP 54100A/D can accommodate four HP 54000-series probes as inputs. Two of its inputs are dedicated to the vertical inputs, as in a traditional oscilloscope, and two are devoted to the time base trigger channel. The HP 54300A Probe Multiplexer is designed to expand the inputs of the HP 54100A/D or other  $50\Omega$  instruments. It is configured as two independent, eight-to-one, analog input channels. Each channel can be thought of as an eight-position rotary switch, capable of switching  $50\Omega$  transmission line signals with a signal bandwidth greater than 1.5 GHz.

Fig. 11 shows the HP 54300A with a full complement of probes. Any of the HP 54000-series probes can be interchanged in any slot position, thus allowing up to 16 points in the circuit to be probed without having to remove and reconnect the probe tips. Once the signal exits the probe, it is in a well-controlled  $50\Omega$  environment. The active channel is routed through an eight-channel RF coaxial switch to a BNC connector on the front panel.

#### Multiplexer System Electronics

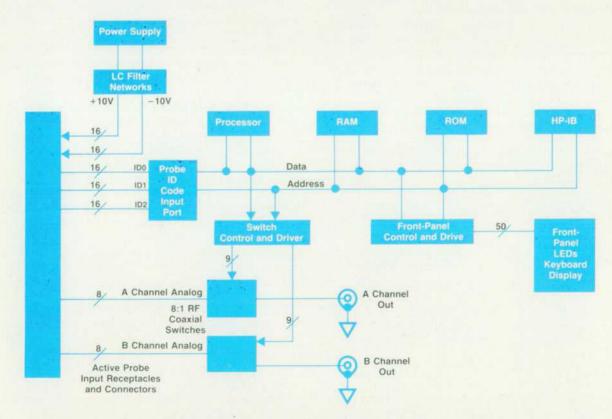

Fig. 12 is a block diagram of the HP 54300A. The heart

Fig. 12. Block diagram of the HP 54300A Probe Multiplexer control circuitry.

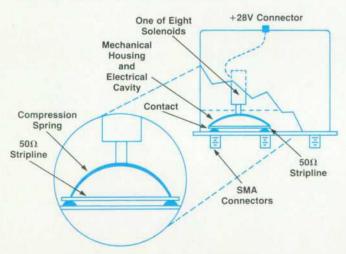

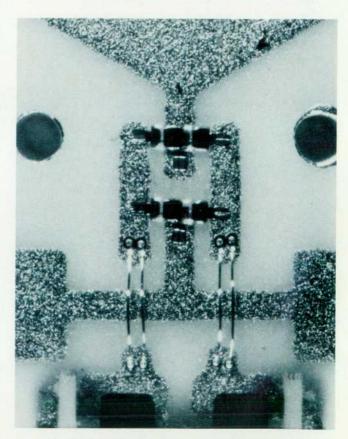

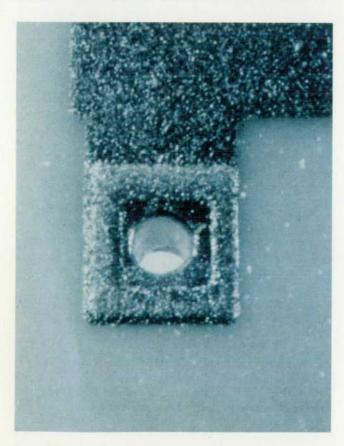

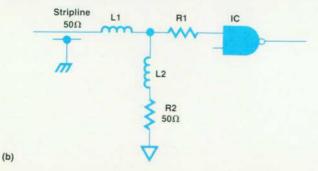

of the instrument is two eight-channel, RF coaxial switches that have bandwidths from dc to greater than 2 GHz. The switches are solenoid-actuated. Each solenoid is connected to a  $50\Omega$  stripline cable that can make a connection between the central contact of the switch and a contact around the perimeter. Actuating the solenoid with 24Vdc connects the associated  $50\Omega$  peripheral connector to the center one. Only one solenoid may be actuated at a time. The RF switch design is shown in Fig. 13.

The instrument is controlled by a 6809A microprocessor operating with a 1-MHz clock frequency. The entire operating firmware is contained in single 8K×8 EPROM circuit. The remainder of the memory consists of 2K bytes of scratchpad memory, used for power-on system storage, and 4K bytes of battery-backed-up nonvolatile memory, which is used to store sequences of switch closures (lists).

The HP-IB interface, front-panel switches and display, and RF coaxial switches are controlled by LSI controller circuits.

The power supply is a linear design, capable of supplying 5V at 2A for the digital circuitry, ±10V at 2A for active probe power, and 28Vdc at 500 mA for the solenoids. The 5V and ±10V supplies are regulated by self-contained IC regulators. The 28V supply is essentially unregulated. However, to limit power dissipation within the solenoids, an LM317 regulator is used as a 30V clamp. At voltages less than 30Vdc, the LM317 looks like a series diode with a forward voltage drop of approximately 1V. When the input voltage rises above 30Vdc, the regulator begins to regulate, effectively clamping the voltage seen by the solenoids at 30Vdc.

#### Multiplexer Design Considerations

Three factors were extremely important in the design of the HP 54300A. They are mechanical switch reliability, electrical system noise and grounding, and probe power integrity and probe protection.

The issue of mechanical switch reliability was the most important factor in the design of the HP 54300A, and the most development time went into this aspect of the design. Although manufacturing RF coaxial switches is a mature

Fig. 13. Cutaway view of the multiplexer RF coaxial switches. The mechanical housing and  $50\Omega$  stripline form a widebandwidth, low-loss transmission environment.

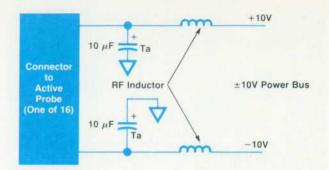

Fig. 14. The tantalum capacitors and RF inductors provide high-frequency power supply filtering and prevent cross talk between active probes.

technology, we had to be certain that the switches could achieve the performance level that our customers expect. With the help of marketing, we surveyed potential HP 54300A users to determine the limits of acceptable performance. This survey provided us with two performance benchmarks. First, the switches had to be able to perform reliably for 700,000 to 1,000,000 operations per switch contact, and second, the rate of soft failures, that is, partial closures or incomplete openings, should be less than 0.05% per contact.

We instituted an extensive test program to evaluate RF switch performance. The switches were tested by cycling each switch through all eight contact positions while ramping the temperature continuously from  $-20^{\circ}\text{C}$  through  $+60^{\circ}\text{C}$ . After 200,000 cycles, the switch was removed from the environmental chamber and tested for RF performance and dc resistance. The dc test was the most stringent. Each contact position was exercised 10,000 times and the numbers of failures to open, failures to close, and contact resistance values greater than 50 m $\Omega$  were logged to an HP 9000 Model 226 Computer. If the rate of these failures went above 0.05%, the switch was considered worn out.

These tests were performed in close cooperation with the switch manufacturers. From these tests, we selected a vendor whose switches met the performance criteria we had established.

Since the HP 54300A was designed as a companion product to the HP 54100A/D, a major design challenge was managing grounding and electrical system noise. To control system noise, the HP 54300A contains three separate ground buses. The analog supply, the digital supply, and the solenoid supply grounds are all isolated from each other and come together at one point—the flange of one of the RF coaxial switches. Furthermore, the ±10V analog power supply is filtered by a separate LC circuit at each power connector to the probe housings (Fig. 14). Whenever a signal must cross between the analog and digital ground planes, it is sent through a 100-k $\Omega$  series resistance that straddles the two ground planes on the inner layers of the main printed circuit board in the instrument. These signals are then buffered by high-impedance CMOS logic circuitry. This technique effectively eliminates currents flowing between the two grounding systems.

Even with careful design of the grounding system, early tests revealed noise pulses that were correlated with the

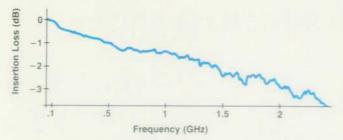

Fig. 15. Plot of insertion loss versus frequency for the HP 54300A Probe Multiplexer. The overall shape of the curve is the result of skin-effect losses. The fine structure is caused by small impedance discontinuities at internal connections.

1-MHz system clock emanating from the 6809A microprocessor. Since all external inputs to the microprocessor are interrupt driven, once an external (front panel or HP-IB) command is executed, the microprocessor need only wait until the next interrupt occurs. The SYNC instruction was used to put the 6809A in a wait mode. In this mode, all address and data bus activity ceases, and the microprocessor halts all instruction processing until an interrupt occurs. Thus, the digital system is only active when executing switch closure or system instructions. This effectively eliminates all coupled noise in the system.

As mentioned earlier, each connector to the probe housing has a separate LC filter at the  $\pm 10$ V inputs. This helps eliminate cross talk between probes and provides clean power. The power supply is a linear design, which at worst case is only 40% efficient. The use of a linear rather than a switching power supply design was decided upon since the potential for noise coupling problems was much higher with a switching power supply. Since the HP 54300A chassis is rather roomy and a fan is used to cool the active probe circuitry, the heat developed by the power supply is not a problem in the system design.

The potential for a power supply failure destroying all the active probes in the instrument is handled by two separate circuits. The IC regulators are internally current-limited to a safe level to prevent catastrophic failure of the supply. In addition, overvoltage protection ICs, located downstream from the voltage regulator ICs, separately monitor the plus and minus 10V lines. Should either of the supplies go above 12Vdc, the circuits activate an SCR, which short-circuits the line and blows a protection fuse.

The analog voltages are monitored by a comparator circuit that can generate a processor interrupt if a power supply failure occurs.

#### **Multiplexer Operational Features**

Normal operation of the probe multiplexer is quite straightforward. The pushbuttons A0 through A7 and B0 through B7 toggle the corresponding switch inputs on and off. An LED lights to show the active channel. In addition, scanning sequences (lists) can be created and stored in nonvolatile memory. These lists are similar to those used in the HP 3488A Switch Control unit. A list can be up to 99 steps long and up to 100 lists may be created. The total number of stored steps may not exceed 3761, the capacity of the nonvolatile RAM array. A list may be recalled from memory and edited and/or executed. NEXT and PREV keys allow

sequencing through a list. If these keys are held down, the instrument will move rapidly through the list, but will not activate a channel until the key is released. Where practical, the HP-IB command set mimics that of the HP 3488A. The front panel also contains a four-digit LED display. The two left-hand digits display the currently active list, and the two right-hand digits display the current step in a list. The display is also used to display error messages in the format: Er nn, where nn is an error message number.

Lists can also be scanned by pulsing an external, rearpanel BNC input connector. A positive TTL pulse causes the current list to be scanned forward one entry. The instrument also issues a pulse from another rear-panel BNC output connector when the switch contact has settled and data can be taken. Thus, a data logger scheme can be implemented without the intervention of a computer/controller. In this mode of operation, the end of a list rolls around to the beginning as the next step.

#### Using the Multiplexer

The HP 54300A is easily connected to other test instruments. Its BNC outputs are  $50\Omega$  transmission lines and can be connected to any instrument that has  $50\Omega$  input terminations. When used with an HP 54002A  $50\Omega$  Input Pod, the HP 54300A has an input-to-output bandwidth greater than 1.5 GHz (3 dB). When connected to an HP 54100A/D, the system bandwidth is still greater than 1 GHz.

Since the analog signal path is essentially that of a  $50\Omega$  transmission line, the signal losses that occur through the instrument are those that would naturally occur in any cabling and connection system of equal length. Fig. 15 is a graph of the swept frequency response of the instrument. The losses are not the usual 6 dB per octave of a single pole, but rather skin-effect losses normally associated with transmission lines.

In theory, very large multiplexing systems could be built by cascading multiple HP 54300A instruments. However, because of the increased cabling and connections, the signal losses would become excessive. Therefore, we recommend that no more than one additional level of HP 54300As be cascaded, giving a total of 128 input channels. Cascading one additional level reduces the multiplexer's bandwidth to 1 GHz (3 dB), and reduces the system bandwidth of the HP 54100A/D to less than 1 GHz, but this may be a reasonable compromise in applications requiring many input channels.

#### Acknowledgments

The authors would like to acknowledge the contributions of the following people: Rick James and Frank Leri developed the mechanical design of the pods and pod housing. Martin Guth designed the thick-film microcircuits used in the HP 54001A probe tip and amplifier. Lewis Dove designed the thick-film microcircuits for the HP 54003A amplifier, and Ken Miller aided in the design and test of the amplifer circuit. Tom Cheski did the quality assurance testing of the RF coaxial switches. Bill G. Smith did the final mechanical design of the HP 54300A. Jonathan Mahaffey put the entire firmware for the HP 54300A into one 8K ROM. Don Smith guided the development of a number of disjointed projects with aggressive schedules and kept them all on track.

## Waveform Graphics for a 1-GHz Digitizing Oscilloscope

by Rodney T. Schlater

AVEFORM GRAPHICS are an important part of an oscilloscope. By looking at a displayed waveform, a user can understand more about a signal than if it is described by several pages of data. For example, at a glance a user can tell whether the rise time is too slow, whether the signal has ringing on it, whether the lower level is floating, or whether the signal is misbehaving.

Recognizing the importance of the display, special attention was paid to developing a good graphics interface for the HP 54100A/D Digitizing Oscilloscope. Several new methods of displaying waveforms were developed that provide users greater insight into their circuits. In addition, new techniques were created for plotting waveforms on the screen very quickly, making the HP 54100A/D very responsive and giving it the feel of an analog oscilloscope.

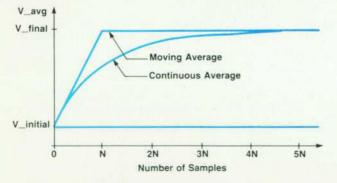

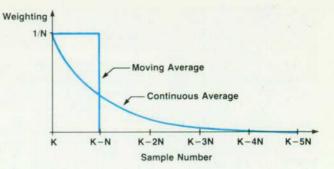

The three display modes of the HP 54100A/D are variable persistence, infinite persistence, and averaging. Variable persistence and infinite persistence are new to digitizing oscilloscopes. The averaging used is a continuous average. Most digitizing oscilloscopes now use a terminating type of average that stops when the selected number of repetitions have been averaged.

#### Variable Persistence

Variable persistence is the normal display mode of the HP 54100A/D. With variable persistence, the user can con-

trol how long waveforms remain on the screen. The waveform persistence can be set from 0.2 second to 10 seconds

For short persistence times, variable persistence behaves like the normal display mode of an analog oscilloscope. The screen is continuously updated with new waveforms, and the picture on the screen changes as the input signal changes. For longer persistence times, variable persistence can convey more information than a conventional oscilloscope.

In addition to displaying amplitude versus time, variable persistence gives the user a view of what the waveform is doing over a long period of time (e.g., jittering, drifting, or changing in amplitude). In analog oscilloscopes, variable persistence has proved valuable for capturing single-shot and infrequently occurring signals. Because it is implemented using different techniques, the HP 54100A/D's variable persistence solves many of the problems that are inherent in analog techniques: the persistence time can be set precisely, the picture is always clear and easy to adjust, and the display does not fade or bloom.

Variable persistence overcomes one of the major shortcomings of digitizing oscilloscopes—inability to handle dynamic waveforms. Most digitizing oscilloscopes work well when the waveform is static and well-behaved, but have problems with waveforms that are changing, such as multiple-trace waveforms, envelope waveforms, and

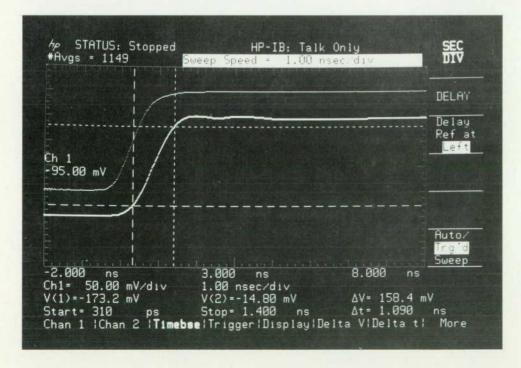

Fig. 1. With variable persistence, digitizing oscilloscopes can display waveforms that are multivalued in time. The two vertical markers in the photo are positioned to measure the setup time between the data strobe (top waveform) and an address line (bottom waveform) of a 68000 microprocessor.

Fig. 2. Variable persistence shows the different waveform modes in an eye diagram. The quality of the transmission line can be determined by measuring the width and height of the eye opening.

waveforms that are aliased, jittering, or noisy. This is because they treat all waveforms as single-valued functions (i.e., having one vertical point for every time point), whereas many waveforms are multivalued over time.

Variable persistence handles changing waveforms very easily. Fig. 1 shows an example of a multiple-trace waveform displayed with the variable persistence set to 0.5 second. A multiple-trace waveform occurs when a signal has several modes depending on the circuit conditions. Sometimes it is possible to display only one of the waveform modes by selecting an appropriate trigger signal, but such a signal is not always available. In many cases, it is desirable to display the signal as a multiple-trace waveform. In the example, the multiple-trace waveform is used to measure the setup time between a 68000 microprocessor data strobe and an address line.

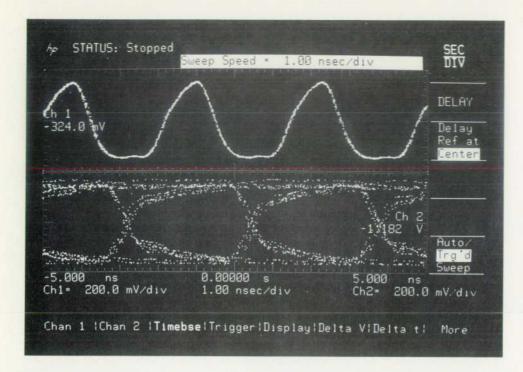

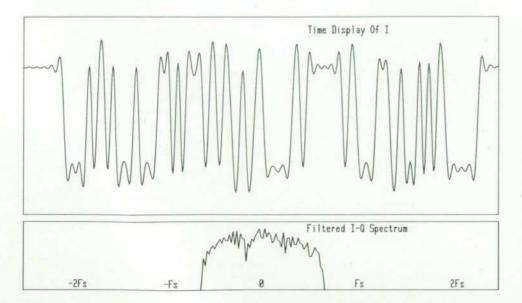

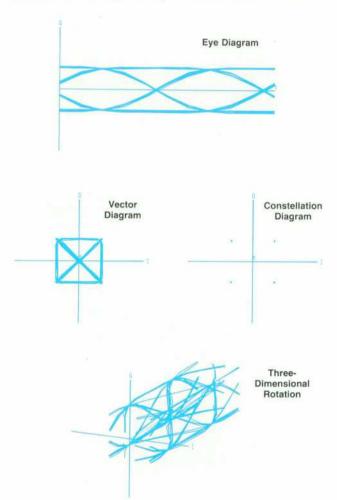

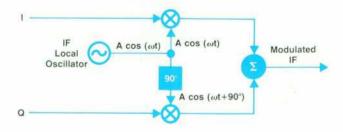

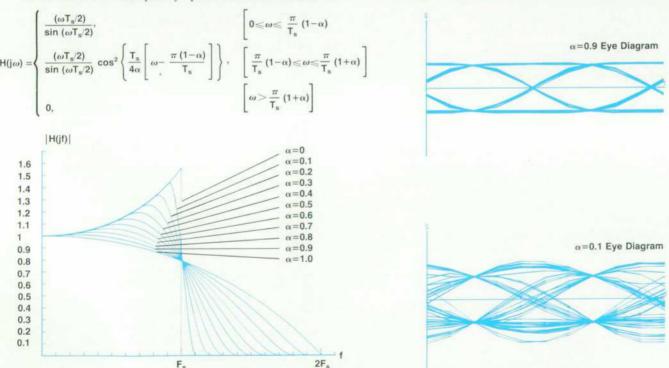

Fig. 2 shows another example of a multiple-trace signal, one that is both noisy and jittering in time. The display shows the eye diagram of an output signal from a long transmission. The quality of the transmission line can be determined by measuring the height and width of the eye pattern.

#### Infinite Persistence

The maximum setting on the variable persistence control knob selects the infinite persistence mode. In this mode, waveforms accumulate on the display indefinitely or until the user presses the **CLEAR DISPLAY** key. This erases the screen and restarts the process.

Infinite persistence is a feature that is new to both digital and analog oscilloscopes. The maximum persistence time in analog storage oscilloscopes has been limited to between 10 and 60 seconds in the viewing mode.

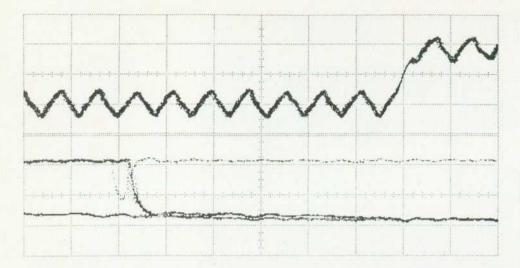

Infinite persistence is valuable because it can catch all the variations of a signal. It is useful for making worst-case measurements, such as jitter, noise, or metastable measurements, and for trapping circuit problems that occur infrequently, even those that occur every few days.

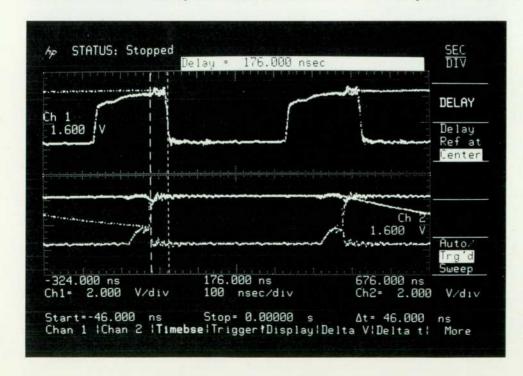

Fig. 3 shows an example of an infrequently occurring problem that was solved using infinite persistence. The problem involved a two-stage ECL counter circuit. The problem only occurred about once every two seconds and turned out to be a 2-ns negative-going glitch on the carry output of the counters. In Fig. 3, the top waveform is the trigger signal and the bottom waveform is the carry output from the counter. The problem also illustrates the HP 54100A/D's ability to look back in time at events that occur before the trigger.

#### Averaging

The averaging display mode is useful for removing uncorrelated noise from signals and for increasing the resolution of displayed waveforms. Averaging is performed on the samples that fall within a time slot. Features that distinguish the HP 54100A/D's method are that the averaging is performed very quickly and that it is done using a continuous averaging algorithm, which causes the screen to be constantly updated with the newest averaged waveform. Other digitizing oscilloscopes that perform averaging generally use a terminating method in which the averaging stops after a selected number of sweeps.

Two front-panel controls affect averaging. The CLEAR DISPLAY key erases the screen and restarts the averaging process, and there is a control for selecting the number of averages, which can be a value between 1 and 2048. There is also a display readout that shows the current number of averages.

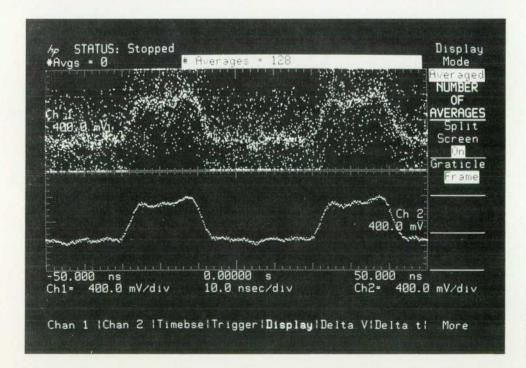

Fig. 4 shows an example of how averaging can be used to recover a signal buried in noise. The top waveform shows the original signal, and the bottom waveform shows the signal after averaging 128 sweeps. The top waveform was acquired in the variable persistence mode and then was

Fig. 3. An ECL counter was not reaching full count. The cause of the problem, a glitch on the carry output, was discovered using infinite persistence. The picture was obtained using the hard-copy output capability of the HP 54100AID.

saved in the waveform memory.

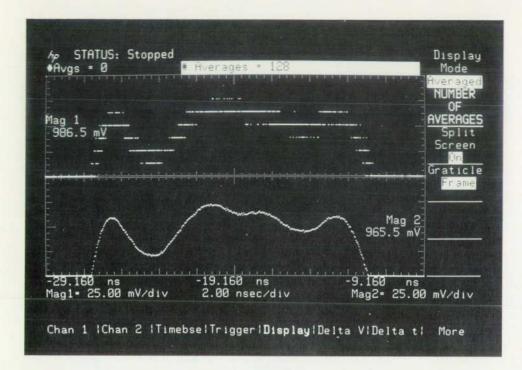

The HP 54100A/D uses a seven-bit analog-to-digital converter (ADC). Averaging extends the resolution to ten bits. Normally, not all of the extra resolution is required, since the resolution of the screen is only eight bits. However, there are several places where the extra resolution is of value. One is for time measurements; more accurate results can be obtained using the extra precision. A second is for HP-IB applications; HP-IB users can read out full-precision values over the bus. A third is for display magnification.

The HP 54100A/D has a vertical magnification feature that is useful for looking at distortions on waveforms such as ringing and reflections. This feature works by placing a window over the part of the waveform that is to be magnified, and then turning the magnification on. Fig. 5 shows an example of the top of a pulse that is magnified by a factor of 16. The top waveform was acquired in the variable persistence mode. The ADC quantization levels show up

as lines across the screen. The bottom waveform was acquired in the averaging mode. With averaging, enough additional bits of resolution are provided to fill in the gaps between quantization levels.

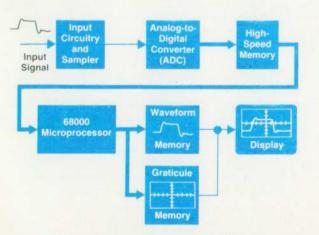

#### **Graphics System**

Fig. 6 shows a simplified block diagram of the HP 54100A/D. The first block is the input circuitry and the sampler. The input circuitry contains attenuation and offset circuits to bring the signal within the range of the sampler and ADC. The sampler performs a sample-and-hold function. The sample window is narrow enough to ensure a 1-GHz bandwidth.

The sampled data is then passed to the ADC, which converts each sample to a seven-bit digital number. These values are stored in a high-speed memory; 1024 points are stored on each acquisition cycle. However, the number of points that reach the display screen depends on the time-

**Fig. 4.** The top waveform shows a signal that is buried in noise. The bottom waveform shows the signal after averaging.

Fig. 5. The photo shows the top of a pulse magnified by a factor of 16. In the variable persistence mode (top waveform), the analog-to-digital quantization values show up as levels. In the averaging mode (bottom waveform), the points between the levels are filled in.

per-division setting.

When an acquisition cycle is complete, the 68000 microprocessor reads the digitized values from the high-speed memory, processes the points, and stores the points as bits in the waveform pixel memory. Every 1/60 second, the display circuitry reads the waveform memory and displays the points on the screen.

The HP 54100A/D uses two memory planes, one for the graticule and one for the live waveforms. Using two memory planes has several advantages. First of all, the graticule or static display is separated from the waveform or live display. This method results in a faster screen update rate, because the software does not have to take the graticule into account when the waveforms are displayed and erased. Second, the waveforms and graticule can be displayed at two intensities, half-bright and full-bright. This makes it easy for the user to distinguish the waveforms from the graticule.

Fig. 6. Simplified block diagram of the HP 54100A/D Digitizing Oscilloscope.

The instrument uses a raster display. The screen is 576 pixels wide by 368 pixels high. The waveforms and graticule are drawn in the graphics area, which is 501 pixels wide by 256 pixels high. The area outside the graphics area is used for text.

The waveform and graticule memories are seen as RAM by the 68000 microprocessor. Each bit in the graphics memory corresponds to a pixel on the screen. When the microprocessor sets a bit in the memory, it shows up as a dot on the screen.