PCM 91 Service Manual Troubleshooting

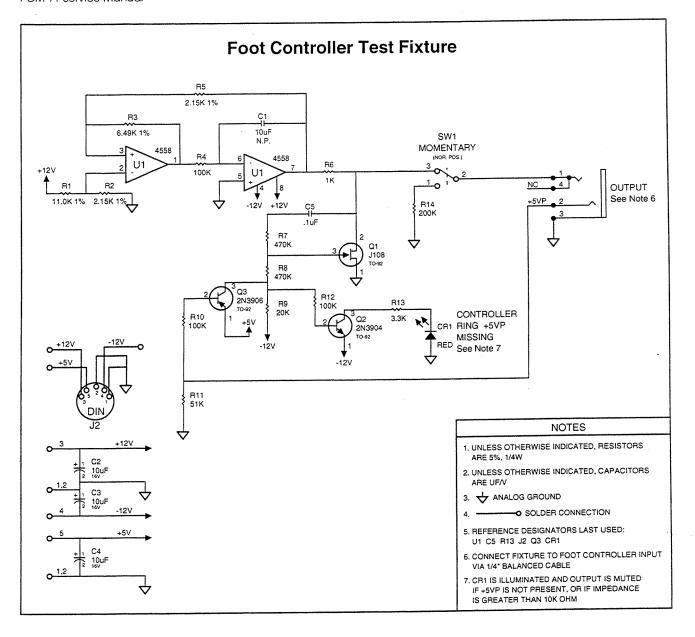

| PART NO.  | DESCRIPTION              | QTY | REFERENCE | Foot Controller Fixture |

|-----------|--------------------------|-----|-----------|-------------------------|

| 340-00740 | IC,LINEAR,4558           | 2   | U1        | Parts List              |

| 520-00941 | IC SCKT,8 PIN,PC,LO-PRO  | 2   | U1        |                         |

| 202-00529 | RES,CF,5%,1/4W,1K OHM    | 1   | R6        | •                       |

| 202-00538 | RES,CF,5%,1/4W,3.3K OHM  | 1   | R13       |                         |

| 202-00555 | RES,CF,5%,1/4W,20K OHM   | 1   | R9        |                         |

| 202-00564 | RES,CF,5%,1/4W,51K OHM   | 2   | R11       |                         |

| 202-00570 | RES,CF,5%,1/4W,100K OHM  | 2   | R4,10,12  |                         |

| 202-00576 | RES,CF,5%,1/4W,200K OHM  | 2   | R14       |                         |

| 202-00579 | RES,CF,5%,1/4W,470K OHM  | 3   | R7,8      |                         |

| 203-00460 | RES,MF,1%,1/8W,2.15K OHM | 1   | R2,5      |                         |

| 203-00465 | RES,MF,1%,1/8W,6.49K OHM | 3   | R3        |                         |

| 203-00474 | RES,MF,1%,1/8W,11.0K OHM | 1 . | R1        |                         |

| 240-00609 | CAP,ELEC,10uF,16V,RAD    | 4   | C2,3,4    |                         |

# **Troubleshooting**

Problems with the PCM 91 can usually be classified as user interface problems or audio problems. User interface problems can range from one non-functioning front panel control to no display. Audio problems affect the signal quality from the analog or digital audio inputs and outputs. Some failures can be traced directly to one particular subsystem within the PCM 91, while others are caused by multiple sub-system failures.

When a problem is encountered, it is good practice to verify overall operation of the PCM 91 by running both the Power Up and the Extended Diagnostics. Refer to the Diagnostic functional instructions and troubleshooting hints given earlier in this chapter.

#### **User Interface Problems**

#### Display problems

Verify that all cable connections from the Host/Motherboard (J18-J22) to the various Front Panel boards are secure.

Vibration can eventually break the strands of cables making them intermittent or possibly open. Connections can become oxidized, corroded or otherwise contaminated causing them to be intermittent, open or resistive. For all of these reasons, caution should be used in troubleshooting. Before any cables are removed, they should be carefully inspected for proper seating and checked for continuity at all points between the Host/Motherboard and the Front Panel boards.

Verify that the +5VD supply is operational and within specification. Check the distribution of the supply to ensure that power is reaching the appropriate front panel display buffer and the register ICs.

If only one control on the Front Panel is failing, then the problem is probably a bad switch, encoder or potentiometer. If more than one control is failing, the problem may be with the Host Processor. Refer to the Diagnostic Descriptions and Theory of Operation.

#### Audio Problems

The first step when troubleshooting audio problems is to collect as much information as possible. The following lists some basic questions which should be answered before any repairs are attempted.

#### Is the problem:

- 1. on one output only?

- 2. at certain signal frequencies only?

- at certain signal levels only?

- 4. in certain programs only?

- 5. at certain sample frequencies only?

- 6 with input only?

- 7. only without input?

- 8. temperature sensitive?

- shock sensitive?

PCM 91 Service Manual Troubleshooting

In general, it is best to verify overall audio performance and to further isolate the problem by running all of the audio proof-of-performance tests. This can be vital when troubleshooting subtle problems. Some system failures may cause a variety of tests to fail but troubleshooting based on one symptom type may be much easier than another. For example, a bad capacitor may produce a high level of distortion and a frequency response problem. The frequency response problem is easier to trace because the signal level can be monitored throughout the signal path on an ordinary oscilloscope.

#### One Bad Channel

One of the most useful pieces of information is determining whether a problem occurs on only one or on both channels. If the problem occurs at only one output, the following assumptions can generally be made with some level of confidence:

- 1. The power supplies are OK.

- 2. The system timing (clocks) is OK.

- 3. The digital circuitry (except for A/D and D/A conversion) is OK.

This type of problem can be fairly easy to troubleshoot, as the working channel can be used as a reference. With the same signal applied to both inputs, compare the signals on both channels at various points along the analog signal path. This may localize the problem fairly quickly.

The system diagnostics may be helpful in isolating RAM or DSP processor failures that might cause bad audio. Refer to the Diagnostics Descriptions for more information.

#### **Both Channels Bad**

As the likelihood of two separate components failing in the same way at the same time is remote, problems which occur in both channels can usually be traced to a component or components that are common to both channels, or to a system problem such as a power supply or timing problem. Verify that the power supplies are operational and within specification. If there is no output, refer to the next section.

#### No Output

First, determine whether the problem occurs on one or both channels.

When the machine has no output from only one channel, apply the same signal to both inputs, then compare the signals on both channels at various points along the analog signal path.

When the machine has no output from either channel, verify that the  $\pm 15V$  and the  $\pm 5V$  analog power supplies are operational and within specification. If the power supplies are OK, determine whether the problem lies within the A/D or the D/A conversion, then troubleshoot the corresponding circuitry.

Troubleshooting Lexicon

# Internal Adjustments and Troubleshooting

The following information allows testing of a non-functioning unit: no display, pegged input meters, load noises, popping crashes and /or no output. Test procedures are provided for checking power supplies, system clocks, battery voltage, and both analog and digital signal paths.

#### WARNING

CAUTION

As these tests require removal of the PCM 91 cover, it is imperative that these tests be performed with regard to all safety and ESD precautions.

#### **Required Equipment**

- DMM ( Digital Mulitimeter )

- Frequency Counter

- 100 MHz oscilloscope ( with 1X ,10X probes )

- Bench power supply providing a variac voltage adjustment and transformer isolation

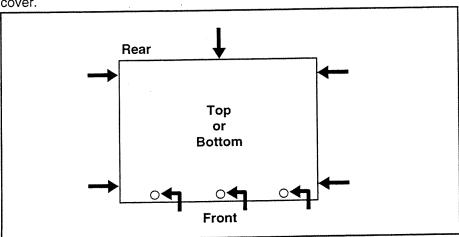

# Removing the Top and Bottom Covers

Remove the eight (8) screws which attach the top cover. Repeat for the bottom cover.

# WARNING

THE POWER SUPPLY IN THIS UNIT HAS A LIVE HEAT SINK. DO NOT TOUCH WHILE THE UNIT IS PLUGGED IN AND POWERED ON.

# **Power Supply**

1. Plug in the PCM 91 and set the variac for nominal line voltage. A clicking noise from the relays should occur 30 seconds after you have powered up the PCM 91.

PCM 91 Service Manual Troubleshooting

2. Set DMM to measure VCD, and check the regulated voltages for proper levels. Use the ground test point (GND-4), located on the board to the right of U9 as a ground reference, The test points for the supplies in the unit are shown below.

| Supplies     | Location                     | Range                         |  |

|--------------|------------------------------|-------------------------------|--|

| +5VD<br>+15V | U37 Pin 20                   | (4.85-5.35)                   |  |

| -15V         | Right of U9<br>Just above U9 | (15.00-16.95)<br>14.25-15.75) |  |

| +5VA<br>-5VA | Right of U9<br>Right of U9   | (4.75-5.25)<br>(4.75-5.25)    |  |

- 1. Power off the PCM 91 and detach the power cord.

- 2. Set DMM for a DC voltage reading on the 20volts DC scale.

- 3. Place the positive (red) DMM Probe on top of the battery located just behind the front panel on the main board.

- 4. Place the negative (black) probe on the test point marked FOOTPEDAL ADC GND-10 to the right of U37 in the middle of the board.

- 5. The reading on the DMM should be  $\geq$  2.75volts. Replace the battery if the voltage is at 2.75 volts or lower.

These procedures test the major crystals and other clocks that are important to the operation of the unit. A frequency counter and an oscilloscope are required for these tests. The oscilloscope's ground lead should be connected to the PCM 91 chassis (away from the power supply).

- Looking down on the unit with the top cover off, locate the DSP board which

is screwed on to standoffs just to the right of the power supply area. Near

the center of this board is Y1, a crystal that runs the Lexichip. Measure either

side of this with the frequency counter. The reading should be 25.8MHz.

- Turn PCM 91 power off and detach the power cord. Remove the screws that hold the DSP board in place. Remove the board and turn the power on. The message: Error E7 will be displayed.

- 3. Measure Y1, Y2, and Y3. Y3, the 16MHz clock that runs the microprocessor, is located to the left of the microprocessor (U34). Place the probe at U40 pin 1.

Crystals Y1 (the 12.28MHz crystal) and Y2 (the 11.29MHz crystal) are located toward the rear of the unit. To measure Y1, which is used to generate the 48kHz Sample Rate Clock, place the probe at U21 pin 10.

To measure Y2, which is used to generate the 44.1 kHz Sample Rate, place the probe at U22 pin 10.

Internal Battery Voltage

**System Clocks**

# Analog Audio Signal Tracing

# **Required Equipment**

- Level meter with oscillator

- Oscilloscope ( to confirm audio signals for any visible problems )

#### Setup

- 1. Place the PCM 91 in Bypass, Analog InLvl=100%, OutLvl=+4dBu, Sample Rate=Internal 44.1 or 48kHz. (See Analog Audio Performance Check: Setup).

- 2. Apply a 1kHz signal @ -20dBu (77.5 mVrms)

- 3. Turn input pot fully clockwise.

| Name<br>Input Stage | Measurement Point U3 Pin 7 Left signal U3 Pin 1 Right signal | Levels -20dBu – Input Switch OUT or 0dBu – Input Switch IN                           |

|---------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Input Level Pot     | R93 Left Signal<br>R92 Right Signal                          | -20dBu OUT or 0dBu IN<br>(77.5mVrms-0.775 Vrms)                                      |

| Left ADC<br>Buffer  | LADC+, LADC-                                                 | -17dBu OUT or +3dBu IN<br>(0.108 mVrms–1.085Vrms)                                    |

| Right ADC<br>Buffer | RADC+, RADC-                                                 | -17dBu OUT or +3dBu IN<br>(0.108 mVrms-1.085Vrms)                                    |

| ADC Inputs          | U10 Pins 4+5 Left<br>U10 Pins 24+25 Right                    | -17dBu OUT or +3dBu IN<br>(0.108 mVrms-1.085Vrms)                                    |

| ADC Outputs         | U10 Pin15 or R76                                             | This is a Digital audio signal +5volt CMOS Characteristics                           |

|                     |                                                              | If there is no output at this pin check for clocks at 256FSA at pin 19, 64FSA at pin |

WCA/ = Sample Rate (44.1 or 48kHz) 64FSA = 64xSample Rate (2.82 or 3.07MHz) 256FSA = 256xSample Rate (11.29 or 12.28MHz)

14, WCA/ at pin 13)

D/A Converter Input U8, Pin10

Digital audio signal

PCM 91 Service Manual Troubleshooting

16dBu OUT for AdDu IN

| Audio signal      | R58+R60<br>R72+R74           | Left out<br>Right out | -16dBu OUT or<br>(0.123m Vrms)                                                                          | +4dBu IN<br>(1.23 Vrms ) |

|-------------------|------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------|--------------------------|

| Lowpass Filter    | LDAC<br>RDAC                 | Left out<br>Right out | -14dBu OUT<br>(0.154mVrms)                                                                              | +6dBu IN<br>(1.54Vrms)   |

| Output Gain Stage | LOUT<br>ROUT                 | Left in<br>Left out   | With output level set<br>-4dBu OUT<br>(0.489mVrms<br>With output level set<br>-18dBu OUT<br>(97.5mVrms) | +16dBu IN<br>(4.89 Vrms) |

|                   | LOUT+, LOUT-<br>ROUT+, ROUT- | •                     | With output level set<br>-4dBu OUT<br>(0.489mVrms<br>With output level set<br>-18dBu OUT<br>(97.5mVrms) | +16dBu IN<br>(4.89 Vrms) |

1 0 4 0 . . .

DAC Outputs

DEO. DEO

This procedure verifies the Digital Audio Path of the PCM 91.

(typical) via Pin 26.

# The input for the Digital signal is RCA J12 (white, marked S/PDIF) or XLR J10 (marked AES/EBU) on the back of the PCM 91. Typical input level is 0.5 Vpp for S/PDIF. The signal goes to the input of the Digital Audio Receiver (U15, Pin 9) after buffering (U19 pin 12/10) and selected by U16 pin 2/15. Depending on which is selected, S/PDIF or AES/EBU digital signals will appear at U16 pin 15. U15 outputs a serial audio data stream at 5Vpp

- 2. The signal travels to pin A8 of J16, then goes to the DSP board for processing.

- 3. After the signal is processed, it comes back down onto the Host board via pin B16 of J16, and then passes through a gate (U45, Pins 1 and 3). The 5Vpp signal goes to the input of the Digital Audio transmitters (U17, U18, pin 8). Audio Transmitter U17 generates the AES/EBU formatted signals which are output through the isolation transformer (TX2) to meet the AES standard at the output jack (J11).

- 4. The Digital Audio Transmitter (U18) generates the S/PDIF formatted signal. This 5Vpp signal exits U18 at Pin 20 and goes through a resister divider network (R110, R111) to bring the signal level down to 1Vpp. When properly terminated by  $75\Omega$ , the signal level will drop further to 0.5Vpp.

# Digital Audio Signal Tracing

## **System Signal Tracing**

This procedure tests basic digital control signals in the PCM 91. For each of the following signals, load **P0 0.0 Prime Blue**, probe at the indicated place, and check for the expected results.

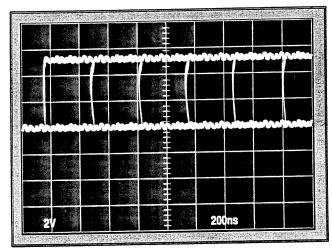

#### **DSP Board Clocks**

FCLK DSP board: Probe on circuit-side at either side of

R44

DSP56002 Clock: Should be a 40MHz square wave.

SLVCLK, SLVCLK/

DSP board: Probe on circuit-side at either side of

R47 and R46, respectively

Slave Clocks: Should be a 10 MHz square wave.

Misc Signals

HWAIT/ DSP board connector: Probe on circuit-side of DSP

board J2 pin B26) Host Wait Signal. Double low-going pulse spaced at about 10  $\mu$ S apart. These two pulses should repeat every 20mS. More activity can be seen when adjusting the size parameter in the

Edit menu (matrix position 2.0).

MUTE/ (U32 pin 15) Master Mute Line: Normally high, low on

power-up.

**Reset Signals**

MRST/ (U69 pin 1) Master Reset: Normally high, low on

power-up.

SLVRST/ DSP board connector: Probe on circuit-side of DSP

board (J2 pin A22).

Slave Reset: Normally high, low on power-up.

LEXRST/ DSP board connector: Probe on circuit-side of DSP

board (J2 pin A20).

Lexichip Reset: Normally high, low on power-up.

56KRST/ DSP board connector: Probe on circuit-side of DSP

board (J2 pin B10).

DSP56002 Reset: Normally high, low on power-up.

Interrupt Signals (See Theory of Operation: Interrupt Timing)

HNMI (U38 pin 3) V40's NMI line: Normally low. When

DIOIMSK/ is high, it is pulsed high on digital I/O

errors such as as loss-of-lock

PROGINT5 (U49 pin 2) V40's INTP5 line: Periodic high-going

pulse

Pulse width=10mS (approx.)

Period=20ms

PCM 91 Service Manual Troubleshooting

PROGINT7

(U49 pin 6) V40's INTP7 line: Periodic high-going

pulse

Pulse width=11ms (approx.)

Period=40 ms

WDKICK/

(U48 pin 5) Watch Dog Timer Kick Pulse:

Pulsewidth=150nS

Period=1mS

**Encoder Signals**

ASNB, ASNA

(U73 pins 3 and 2 respectively)

Adjust Soft Knob Lines B and A: As ADJUST is rotated clockwise, the following patterns should ro-

tate in relative order:

High, High High, Low Low, Low Low, High

SSNB, SSNA

(U73 pins 5 and 4 respectively)

Select Soft Knob Lines B and A: As ADJUST is rotated clockwise, the patterns described above

should rotate in relative order.

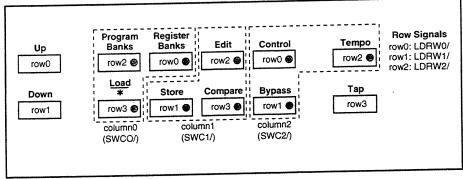

**LED/Switch Scanning Signals**

LHRCOL/, RHRCOL/

(U65 pins 14 and 13 respectively)

Left and Right Headroom LED Column Strobes:

Square Wave with a 4mS period.

SWC0/, SWC1/,

SWC2/

(U68 pins 19, 18, 17 respectively)

Switch & LED Column Strobes: Low-going pulse,

Pulse width=2 mS, Period=6mS

LDRW0/, LDRW1/,

LDRW2/

U68 pins 16, 15, 14 respectively)

LED Row Strobes: Reload P0.0 Prime Blue.

Observe the following on U68 pin 16:

Low-going pulse, Pulse width=2mS, Period =6mS

Press "Edit" Button.

Observe the following on U68 pin 15:

Low-going pulse, Pulse-width=2mS, Period=6mS

Press "Register" Button.

Observe the following on U68 pin 14:

Low-going pulse

Pulse width=2mS, occasionally 4mS when tempo

light blinks Period=6mS

# Restoring Factory Settings

The following procedure restores the PCM 91 factory default settings. This may be necessary due to memory problems, or following internal battery replacement.

This procedure will destroy any user settings or registers. Save setups and registers on a Memory Card to reload after this procedure is completed.

- Set the INPUT GAIN switch on the rear panel of the PCM 91 to the OUT position.

- 2. Set the front panel INPUT control fully counterclockwise.

- 3. Press Down until the display reads: System Edit Mode/1.0/Go

- 4. Turn SELECT until the display reads: System/Initialize/1.9 (Press STORE)

- 5. Press **Store** and verify that the display flashes the following message: **Are** you sure? (Press STORE)

- Press Store and verify that the display flashes the following message for about 1/2 second: Restoring Original Factory Settings... then the message: Loading Effect ... then the display: Chorus+Rvb/P0 0.0/Prime Blue

- 7. Turn off the PCM 91 and detach the power cord.

- 8. Remove the 4 phone plug cables from the PCM 91.

The following procedure will restore the factory defaults without destroying the user registers, but may leave erroneous data in RAM.

- 1. Press Control, then use the ▲ and ▼ buttons to display: Row 4 Setup.

- 2. Turn SELECT until the display reads: 4.1 Load.

- Turn ADJUST counterclockwise to display: Factory Settings.

- 4. Press Load. The display should show: Setup restored.

# Theory of Operation

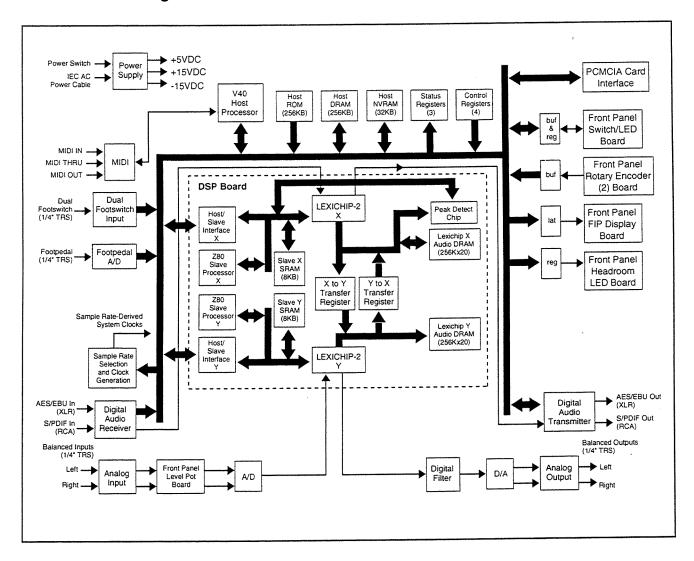

The PCM 91 digital hardware utilizes multiple microprocessors and digital signal processors to perform digital audio effects which are controlled via the front-panel interface, and the MIDI serial interface.

The PCM 91 features five major circuit sections: Host, DSP (Digital Signal Processing), Digital I/O, Analog Conversion, and Power Supply sections. A 10 MHz NEC uPD70208, also known as the V40, provides host microprocessor functions. The host processor circuit manages the user interface including the FIP display, softknobs, switchboard, status and headroom LEDs, MIDI, the footswitch and footpedal, and digital I/O circuitry. It is also responsible for program-load and parameter-passing to the DSP circuitry on the DSP board. The DSP board is responsible for the digital effects processing of the PCM 91. It has a multi-DSP engine featuring two of Lexicon's proprietary Lexichip-2 ASICs. A slave microprocessor, the Zilog Z-80, provides independent house-keeping functions for the Lexichip-2. The analog conversion circuitry handles A-to-D conversion and D-to-A conversion as well as a high performance analog interface to the balanced-line jacks on the rear-panel. The digital I/O circuitry implements AES/EBU and S/PDIF digital audio I/O.

The PCM 91 is physically sectioned into two major circuit boards, five minor circuit boards and a power supply module. The two major circuit boards are the Host Board and the DSP Board. The host processor, digital I/O and analog conversion circuitry reside on the Host Board while the DSP circuitry resides on the DSP Board which connects to the Host Board directly via a 72-pin connector. Smaller boards which are connected to the Host Board include the Front-Panel Switch Board, Front-Panel Encoder Board, Front-Panel Headroom Indicator LED Board, Front-Panel Input Level Pot Board, and the Intelligent FIP Display Module. The Power Supply Module supplies +5VDC, +15VDC, and -15VDC.

**Architectural Overview**

## **Block Diagram**

The Host Circuit is responsible for management of front-panel controls and displays, MIDI interface, Tap/Tempo/LFO functions, and download and real-time control of DSP code. There are 256K bytes of ROM, 256K bytes of DRAM, and 32K bytes of battery backed-up SRAM. The 32K bytes of SRAM are for non-volatile system parameter and user register storage.

Host Processor Circuitry

The main processor of the host circuit is the NEC V40 (uPD70208) (U34). The V40 CPU has several on-chip peripherals including an 8-level priority interrupt controller, DMA controller, timers, and a serial port. The 8-level interrupt controller allows for management of several time-critical periodic tasks in order to meet the real-time requirements of the PCM 91. The DMA controller allows DSP-code download to happen in the background without significant impact on system performance. The timers provide MIDI UART clock generation, and timing references for tempo and LFO functions. The serial port is used to implement the MIDI interface.

In summary, the main host responsibilities are:

- · Management of the user-interface:

- Intelligent front panel display FIP

Front-panel switches

Switch status LEDs

Headroom LEDs

Foot controller pedal jack via 8-bit A/D

Footswitch jack

- Processing data and instructions to and from the MIDI UART (internal)

- Maintenance of non-volatile SRAM for storage of user registers

- Transparent refresh of Host DRAM.

- Providing download/upload to/from PCMCIA card interface

- Loading of slave Z80/Lexichip program code and data

- Controlling slave Z80/Lexichip reset and interrupt functions.

- Selecting sampling rate to be 44.1 kHz, 48 kHz or PLL frequency

- Management of channel status and reset functions for digital I/O interface

- Controlling audio muting hardware

- Management of user-defined control patching and LFO functions

- Management of Tap key and Tempo functions

#### Clocks

A 16 MHz crystal (Y3) is used to generate an 8 MHz clock used as the internal processor clock. This clock is also sourced from the V40 (HCLK) to clock external control logic: a hex flip-flop (74HC174) at U46 and a GAL20V8 at U40. HCLK is also inverted by a 74AC00 (U42) to source HCLK/. HCLK/ clocks a hex flip-flop (74AC174) at U47 and a GAL16V8 on the DSP board.

#### **Bus Interface**

The V40's 8-bit data bus is bidirectionally buffered by a 74HC245 (U35). Since twelve of the twenty V40 address lines are multiplexed with data and processor status, two 74HC573s (U36, U41) are used to latch and buffer sixteen of them (HA<19:0> less HA<11:8>). HA<11:8> are sourced directly from the V40.

Host Bus Status lines (HBS<2:0>), Host Memory Read Line (HMRD/), Host Memory Write Line (HMWRB/), and the Host Refresh Request Lines (HREFREQ/) are sourced to the GAL20V8 for memory interface logic.

#### Interrupts

The host processor has nine interrupts: one non-maskable interrupt (NMI) and eight maskable priority interrupts (INTPx). The priority ordering of the eight priority interrupts is preset as follows: INTP0 (highest) to INTP7 (lowest).

|       | Non-Maskable Interrupt                                                      |

|-------|-----------------------------------------------------------------------------|

| NMI   | Digital Audio Receiver Error Condition                                      |

|       | Maskable Interrupts                                                         |

| INTP0 | Timer 0 (LFO Interrupt) (Periodic: 1 msec) (Internal) (Highest Priority)    |

| INTP1 | MIDI Port Transmit/Receive (Internal)                                       |

| INTP2 | Timer 2 (Front Panel Display Interrupt)                                     |

| INTP3 | Unused                                                                      |

| INTP4 | DSP Interrupt (Z80)                                                         |

| INTP5 | Programmable Interrupt P5 (Patch Calculations Process)                      |

| INTP6 | Programmable Interrupt P6 (MIDI Data Process)                               |

| INTP7 | Programmable Interrupt P7 (Front Panel Interface Process) (Lowest Priority) |

INTP0 and INTP1 are sourced internal to the V40. INTP2 is sourced from the V40's Timer 2. INTP4 is sourced externally by an interrupt sourced either by the Z80 on the DSP board. The interrupt can be identified by reading bits 1 and 0 in Status Register 1. INTP5, INTP6 and INTP7 are sourced by software-programmable bits in Control Register 1 (U49 pins 2, 5 and 6). The interrupts are rising-edge triggered.

When probing with an oscilloscope, the following should be observed on each of the V40's interrupt pins, while running the program **P0 0.0 Deep Blue**:

| NMI   | (U34 pin 66) | Normally low.                                                                        |

|-------|--------------|--------------------------------------------------------------------------------------|

|       |              | (When DIOIMSK/ is high, it is pulsed high on digital I/O error such as loss-of-lock) |

| INTP0 |              | Not accessible (Internal to V40)                                                     |

| INTP1 | (U34 pin 37) | <ul> <li>Not accessible (Internal to V40)</li> </ul>                                 |

|       |              | (Externally grounded)                                                                |

| INTP2 | (U34 pin 38) | Periodic low-going pulse                                                             |

|       |              | (Pulse-width=250ns, Period=2ms)                                                      |

| INTP3 | (U34 pin 39) | Periodic low-going pulse                                                             |

|       |              | (Pulse-width=125ns, Period=3.6ms (approx.)                                           |

| INTP4 | (U34 pin 40) | Non-periodic                                                                         |

| INTP5 | (U34 pin 41) | Periodic high-going pulse                                                            |

|       |              | (Pulse-width=10ms (approx.), Period 20ms)                                            |

| INTP6 | (U34 pin 42) | Reserved for future enhancement                                                      |

| INTP7 | (U34 pin 43) | Periodic high-going pulse                                                            |

|       |              | (Pulse-width=11ms (approx.), Period 40ms)                                            |

#### **On-Chip Peripherals**

V40 on-chip peripherals include:

- · Clock generator

- · Bus interface

- · Bus arbitration

- Programmable wait-state generator

- DRAM refresh controller

- 316-bit timer/counters:1 for MIDI UART clock, 1 for 2ms display interrupt tick, 1 for 1ms interrupt tick

- Asynchronous serial I/O controller (for MIDI)

- 8-input interrupt controller

- 4-channel DMA controller

Theory of Operation Lexicon

#### **Host Memory**

A GAL20V8 (U40) provides memory decoding for ROM, SRAM, DSP56002 Host port, Slave Z80 RAM Access, and DRAM. Following is the Host V40 memory map:

| \$FFFFF                       |                                           |

|-------------------------------|-------------------------------------------|

|                               | ROM<br>(256K)                             |

| \$C0000<br>\$BFFFF<br>\$B8000 | SRAM Expansion (32K)                      |

| \$B7FFF<br>\$B0000            | SRAM (Non-volatile) (32K)                 |

| \$AFFFF<br>\$AE000<br>\$ADFFF | reserved                                  |

| \$AC000<br>\$ABFFF            | *                                         |

| \$A8000<br>\$A7FFF            | Slave Y Memory Bus (16K)                  |

| \$A6000<br>\$A5FFF            | Slave X Peak Detect Chip                  |

| \$A4000<br>\$A3FFF            | **                                        |

| \$A0000<br>\$9FFFF            | Slave X Memory Bus (16K)                  |

| \$90000<br>\$8FFFF            | reserved                                  |

| \$80000                       | PCMCIA Memory Card<br>(64K Page)          |

| \$7FFFF                       | ROM/SRAM Expansion***<br>(64K) (reserved) |

| \$70000<br>\$6FFFF            |                                           |

|                               | ROM Expansion<br>(192K)                   |

| \$40000                       | (reserved)                                |

| \$3FFFF                       |                                           |

|                               | DRAM (256K)                               |

| \$00000                       |                                           |

- \* If SLVRSTY/=0, ROM Lexichip WCS can be read (only)

One Host wait state must be added.

If SLVRSTY/=1, any access will clear Slave-to-Host Interrupt Y.

- \* If SLVRSTX/=0, ROM Lexichip WCS can be read (only)

One Host wait state must be added.

If SLVRSTX/=1, any access will clear Slave-to-Host Interrupt X.

Memory Address Map

<sup>\*\*\*</sup> If MAPINSRAM=0, ROM Expansion for 512Kx8 ROM. If MAPINSRAM=1, SRAM Expansion for 128Kx8 SRAM.

#### ROM

A 27C020/27C2001 (U55) which is a 2-megabit EPROM in a 256Kx8 configuration is installed.

The ROM enable signal (HROMEN/) is sourced by the GAL20V8 (U40) to enable the ROM when the memory address range is \$C0000 to \$FFFFF. (If a 512Kx8 ROM is used, the lower 256KB is mapped to \$40000 to \$7FFFF, and the higher 256KB is mapped to \$C0000 to \$FFFFF. Note that the upper 64K of the lower 256KB is displaced by SRAM if a 128KB SRAM is used and the control bit MAPINSRAM is asserted.)

#### **Dynamic RAM (DRAM)**

256Kx8 Dynamic RAM is provided. Two 44256 (256Kx4) parts at locations U50 and U51 in 20-pin ZIP packages are used to implement high and low nibble. U51 implements the low nibble. Refresh is taken care of by the V40 automatic refresh cycle which needs to be set up by software. Host address bits 17-0 are multiplexed to provide 9 row and 9 column address bits.

DRAM control is implemented by a GAL20V8 (U40) and a 74AC174 (U47). The GAL generates two signals DMEMOP/ and SELCA. DMEMOP/ is asserted for both read and write accesses to the DRAM. This signal is clock-delayed by U47 to generate HRAS/, the row address strobe. PTHRAS/ (pre-terminated version of HRAS/) is clock-delayed once again to generate HCAS/, the column address strobe. SELCA goes to 74AC157 multiplexers (U56, U57, U58) to source row and column address lines. When SELCA is asserted high, address lines HA<19:10> are selected to source the column address to HDRA<9:0>. When SELCA is not asserted (low), address lines HA<9:0> are selected to source the row address to HDRA<9:0>. During DRAM access, HMRD/ distinguishes between reads and writes. When HMRD/ is asserted low, it is a read operation. Otherwise it is a write operation.

The timing of the Host DRAM interface is shown in detail in later in this chapter.

## Non-Volatile Battery Backed-Up Static RAM

A battery backed-up 32Kx8 Static RAM (U54) is provided to implement non-volatile storage. It is primarily used for system control parameter and user register storage. The 32-pin SRAM socket is factory shipped with a 28-pin 32Kx8 SRAM, installed with pin 1 of the IC aligned to pin 3 of the 32-pin socket.

The following table outlines the memory mapping for various configurations. The signal NVRAMEN is asserted by the GAL20V8 depending of the address lines and the control signal MAPINSRAM. MAPINSRAM, when asserted, allows the full use of 128Kx8 SRAMs. However, the lower 64KB of SRAM displaces the upper 64K portion of the reserved ROM expansion space. As current software only supports the 32Kx8 SRAM, MAPINSRAM should never be asserted.

| RAM Type                        | MAPINSRAM   | Memory Size           | Address Range                                                                                                        |

|---------------------------------|-------------|-----------------------|----------------------------------------------------------------------------------------------------------------------|

| 32K x 8<br>128K x 8<br>128K x 8 | 0<br>0<br>1 | 32KB<br>64KB<br>128KB | \$B0000-\$B7FFF<br>\$B0000-\$BFFFF (upper 64KB only)<br>\$70000-\$7FFFF (lower 64KB)<br>\$B0000-\$BFFFF (upper 64KB) |

Theory of Operation Lexicon

NVRAMEN is inverted by a 74AC00 (U61) NAND gate to yield QNVRAMEN/ which is an asserted-low signal going to the chip enable of the SRAM. QNVRAMEN/ is also qualified by PWR\_OK which is source from the +5V Monitor (MC34164-U53). When power is going down, PWR\_OK gets asserted and QNVRAMEN/ is gated off. The 74AC00 is powered by VRAM which is the battery backup voltage. This ensures that as power goes down, that the CE1/ pin of the RAM tracks Vcc as required by the SRAM manufacturer for reliable data retention. When the unit is on, VRAM should be at 5V. When the unit is on, VRAM follows the voltage from the backup lithium battery (3V) (BAT1).

#### **Battery Backup**

The Battery Backup circuitryis designed to protect data in the non-volatile SRAM. It is triggered (controlled) by the +5V Monitor, U53. To ensure the lowest possible leakage current during power on, two transistors (Q8 and Q9) are used to switch between backup operating modes.

A buffer (HC08), guaranteed to operate down to 2V is used to drive Q8. R205 ensures that the transistor stays off while the HC08 Vcc is less than 2V.

D19 is a Schottky diode to minimize the forward voltage drop while power is off. R209 protects the battery in case the diode should fail.

The battery low indicator is set to trigger at approximately 2.1-2.5V. If the battery is low, the status line BATLOW is asserted.

#### **PCMCIA Memory Card**

A PCMCIA memory card slot (J23) provides removable user register storage, and capability for algorithm and host software updates. Up to 1 MB of memory on a PCMCIA card is accessable. The host has a 64K window into the card memory space. The PCMCIA card enable signal CARDEN/ is asserted by the HOST GAL20V8 (U40) whenever the address accessed is the range \$80000-\$8FFFF. The PCMCIA interface in the PCM 91 is designed to handle all cards with an access time of 250ns or faster. The selected 64KB page within the 1MB of card space is set by 4 bits in Control Register 3. This allows up to 16 pages (16x64KB=1MB). The location within the page is selected by the 16 LSBs when the card is selected. The 4-bit page register CA<19:0>, set by Control Register 3 <3:0>, extends the card addressing capability to 1MByte. When the CREG/control bit (Control Register 3 bit 7) is asserted low, the card's configuration register is selected instead of normal memory access.

Three 71HC541 octal buffers provide address line buffering (U59, U60) and control line buffering (U71). All three are enabled by software when doing card operations, and are disabled otherwise. They are enabled by de-asserting (setting high) DISCARD/ (Control Register bit 6.)

#### When DISCARD is asserted high:

- Address lines are pulled-down to ground via R187-R202.

- CCE1/, COE/, and CWE/ are pulled-up to CVCC via R228, 227, 225.

- CARDENB/ is pulled to a high by R223, disabling the bidirectional data buffer (U70).

A bidirectional data buffer 74HCT245 (U70) is used to isolate the card data lines from the host data bus HD<7:0>. The signal HMRD/ determines the direction. When low, data is enabled from the card data bus CD<7:0> to HD<7:0>. When high, data is enabled from HD<7:0> to CD<7:0>.

Software detects whether or not there is a card installed by reading CARDDET/ (Status Register 0 bit 4). This signal is asserted low when both ends of the PCMCIA card are plugged in, ensuring that the card is not powered-up or accessed until fully plugged in. The end-pin signals: CDET1/ and CDET2/ are pulled high when their respective pins are not inserted. These pins are grounded and, when they are inserted into J23, the corresponding lines are pulled low. A 74AC32 (U72) provides this logic by ANDing CDET1/ and CDET2/ to assert CARDDET/ (low).

Software reads the PCMCIA card write protection switch by reading CWRPROT (Status register 0 bit 5). CWRPROT is a buffered version of CWP via U71. Both CWRPROT and CWP are pulled-up to CVCC. When no card is inserted, CVCC will dischage to ground. Therefore, CWRPROT is not valid unless the card is fully inserted and enabled by setting DISCARD/ high.

The three remaining sections of the 74AC32 (U72) are used to produce a gated version of HMWR/ called PREBCWE/. This signal gives an earlier rising edge to give the PCMCIA card the proper data setup time. PREBCWE/ is buffered by U66 to source CWE/ (the write enable that goes directly to the card).

The timing of the PCMCIA Card interface is shown in detail later in this chapter. Note that one wait state (generated by the V40 preset by software) is inserted for all card access.

Two status lines (CARDBVD<2:1>) from an inserted SRAM PCMCIA card indicate the condition of its battery. These are read by the host from Status Register 0 bits 3:2 respectively. Both signals are kept asserted when the battery is in good condition. A replacement warning condition is signaled by CARDBVD1 asserted and CARDBVD2 not asserted. In that case, data integrity on the card is still assured. If CARDBVD1 is not asserted, with CARDBVD2 either asserted or not asserted, the battery is no longer servicable and data is lost.

The following summarizes PCMCIA card control bits via Control Register 3: Control Register 3 (I/O location=\$0006)

7 6 5 4 3 2 1 0

CREG/ DISCARD/ AESINSEL MAPINSRAM CA19 CA18 CA17 CA16

The following outlines the PCMCIA card status via Status Register 0 Status Register 0 (I/O location=\$0000 Read-Only)

7 6 5 4 3 2 1 0

FOOTSWT SINGOUT/ CWRPROT CARDDET/ CARDBVD2 CARDBVD1 spare FOOTSWR

#### Host-to-Slave Z80/Lexichip Interface

The host has direct access to the DSP board's Slave Z80 8K SRAM. The Z80, in turn, is responsible for loading and modifying Lexichip program code internal to the chip. The address range for host access to the Slave Z80 SRAM is \$A0000-\$A1FFF. This memory address range is decoded by the HOST GAL20V8 (U40) to assert SBUSEN/ (low). (This corresponds to the Z80's local address range of \$0000-\$1FFF.)

# Host I/O I/O Address Map

Two 74HC138s (U62 and U63) provide I/O decoding for writeable and readable registers. The 74AC00 (U42) provides decode for the 8-bit ADC used to read the foot controller jack. The 74HC174 (U46) provides various HCLK delayed signals for I/O interface control. Host I/O address mapping is summarized as follows:

#### READS:

| Host I/O Address HA<15:0> | Actual Address Used | I/O                                |

|---------------------------|---------------------|------------------------------------|

| xxxx xxxx xxx1 xxxx (B)   | \$0090 (H)          | Footcontroller A/D Conversion Data |

| xxxx xxxx xxx0 111x (B)   | \$008E (H)          | Watchdog Timer Kick                |

| xxxx xxxx xxx0 110x (B)   | \$008C (H)          | Switch Matrix Row and Soft Knobs   |

| xxxx xxxx xxx0 101x (B)   | \$408A (H)          | (unused)                           |

| xxxx xxxx xxx0 100x (B)   | \$0088 (H)          | Clear Lexichip Overload Flag       |

| xxxx xxxx xxx0 011x (B)   | \$0086 (H)          | (unused)                           |

| xxxx xxxx xxx0 010x (B)   | \$0084 (H)          | Status Register 2                  |

| xxxx xxxx xxx0 001x (B)   | \$0082 (H)          | Status Register 1                  |

| xxxx xxxx xxx0 000x (B)   | \$0080 (H)          | Status Register 0                  |

|                           |                     |                                    |

#### WRITES:

| Host I/O Address HA<15:0> | Actual Address Used | I/O                                  |

|---------------------------|---------------------|--------------------------------------|

| xxxx xxxx xxx1 xxxx (B)   | \$0090 (H)          | Foot Controller A/D Conversion Start |

| xxxx xxxx xxx0 111x (B)   | \$008E (H)          | Front Panel Display FIP              |

| xxxx xxxx xxx0 110x (B)   | \$008C (H)          | Switch/Status LED Matrix Cols/Rows   |

| x1xx xxxx xxx0 101x (B)   | \$408A (H)          | Set Host-to-Slave Interrupt Y        |

| x0xx xxxx xxx0 101x (B)   | \$008A (H)          | Set Host-to-Slave Interrupt X        |

| xxx xxxx xxx0 100x (B)    | \$0088 (H)          | Headroom LED rows                    |

| xxxx xxxx xxx0 011x (B)   | \$0086 (H)          | Control Register 3                   |

| xxxx xxxx xxx0 010x (B)   | \$0084 (H)          | Control Register 2                   |

| xxxx xxxx xxx0 001x (B)   | \$0082 (H)          | Control Register 1                   |

| xxxx xxxx xxx0 000x (B)   | \$0080 (H)          | Control Register 0                   |

#### **Front Panel Switches**

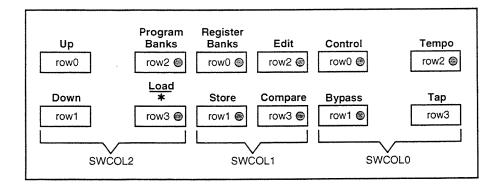

The front-panel switches are arranged on the front-panel board as shown below.

Switches are arranged in a 4 row x 3 column matrix in which each column of 4 rows are read by:

- 1. Asserting one bit of the Switch Column (SWCOL<2:0>/) field of the SWITCH/LEDs MATRIX REGISTER (74HC574,U68).

- 2. Then reading the Switch Row (SWROW<3:0>) field of the the Switch Matrix Input Buffer (74HC541, U73).

The control register and the Switch Column Matrix Buffer are outlined follows:

#### Switch/LED Matrix Register (I/O location=\$000C Write-Only)

7 6 5 4 3 2 1 0 spare spare LDRW2 ·LDRW1 **LDRW0/ SWC2/ SWC1/ SWC0/**

#### Switch Matrix/Soft Knobs Input Buffer (I/O location = \$000C Read-Only)

7 6 5 4 3 2 1 0 SWROW3 SWROW2 SWROW1 SWROW0 SSNB SSNA ASNB ASNA

#### Soft Knobs

Two 36-position 2-bit gray-code encoded knobs with detents are used to implement the SELECT and ADJUST Soft Knobs. The 2-bits of each (available by reading the Switch Matrix/Soft Knobs Input Buffer) are assigned as follows:

#### Switch Matrix/Soft Knobs Input Buffer (I/O location = \$000C Read-Only)

7 6 5 4 3 2 1 0 SWROW3 SWROW2 SWROW1 SWROW0 SSNB SSNA ASNB ASNA

The encoded bits for the SELECTSoft Knob are SSNB and SSNA. The encoded bits for the ADJUST Soft Knob are ASNB and ASNA. As each knob is rotated clockwise, the sequence for each pair (SSNB:SSNA, and ASNB:ASNA) should be: LL, LH, HH, and HL, etc. in a rotating sequence. This can be observed at the inputs of the Soft Knobs Input Buffer (U73) pins 5 & 4, and 3 & 2 respectively.

Theory of Operation Lexicon

## Front Panel LEDs

#### **Switch-Status LEDs**

On the front-panel board, green LEDs are physically embedded in each of 9 switch button-caps. These LEDs are matrix-driven determined by 6 register bits consisting of 3 columns and 3 rows. The columns are the same as those that drive the switch columns (SWCOL<2:0>). The LED matrix columns and rows are determined by 6 bits of a 74HC574 Octal Register (U68). During operation, each column should individually be asserted for 2ms of a 6ms period. Transistors Q12, Q13, and Q14 source the needed current for each column. R248, R251 and R253 pull down each column when any respective transistor is off. Any LED within a column can be lit by asserting the corresponding rows (LEDROW<2:0>) (asserted-low). When LED(s) are on, peak current through R254, R255, and R256 should be about 20 mA. As the control bit LEDSEN tri-states all the LED control register bits, all LEDs are off during reset. LEDSEN must be asserted before any LEDs can come on. The front panel switches and LEDs are arranged as shown below.

Status LED Column Grouping and Row Assignments

Switch/LEDs Matrix Register (I/O location = \$000C Write-Only)

7 6 5 4 3 2 1 0

spare spare LDRW2/ LDRW1/ LDRW0/ SWC2/ SWC1/ SWC0/

#### **Headroom Indicator LEDs**

The Headroom LEDs are matrix-driven determined by 2 columns of 5 rows. The columns and rows are determined by 7 bits of a 74HC574 Octal Register (U65). During operation, each column should individually be asserted for 2ms of a 4ms period. The two columns are LHRCOL/ for the left input level, and RHRCOL/ for the right input level. Transistors Q10 and Q11 provide the necessary current to drive each column's LEDs. R235 and R237 pull down each column when its respective transistor is off. LEDs within a column can be lit by asserting the corresponding rows (LED-24DB/R, LED-18DB/R, LED-12DB/R, LED-6DB/R, LEDOVRL/R). When LED(s) are on, peak current through R238-242 should be about 10.4mA. As the control bit LEDSEN tri-states all the LED control register bits, all LEDs are off during reset. LEDSEN must be asserted before any LEDs can come on. The headroom indicator LEDs are arranged as shown below.

| Left<br>Headroom<br>Column<br>(LHRCOL/) | Right<br>Headroom<br>Column<br>(RHRCOL/) |                           |

|-----------------------------------------|------------------------------------------|---------------------------|

| 0dB                                     |                                          | Overload row (LEDOVRLD/R) |

| 6dB                                     |                                          | -6dB row (LED-6DB/R)      |

| 12dB                                    |                                          | -12dB row (LED-12DB/R)    |

| 18dB                                    |                                          | -18dB row (LED-18DB/R)    |

| 24dB                                    |                                          | -24dB row (LED-24DB/R)    |

| Rows and col                            | umns are as                              | serted low signals.       |

Headroom Indicator LEDs

Column and row control bits are in the headroom LED register. They are summarized as follows:

#### HeadroomLED Register (I/O location = \$0008 Write-Only)

7 6 5 4 3 2 1 0 HIOUTLVL RHRCOL/ LEDOVRLD/LED-6DDB/ LED-12DB LED-18DB LED-24DB

#### **Front Panel Display**

The front panel alphanumeric display is a Futaba M202SD01HA, an intelligent vacuum fluorescent display module with 2 rows of 20 characters each. The module has its own display controller and is connected to the host system bus via an 8-bit data latch (U66). The display data write signal, DISPDWR/, is sourced from the I/O write decoder (74HC138 (U62). It is inverted by a 74HC04 (U44) to be the latch signal DISPDWR for the 74HC573 (U66) which is the display data latch. When the signal is asserted, data from the host (HD<7:0>) flows through to source the display connector, then the display. When the signal is de-asserted, the latch is closed, and data should be held. This provides proper hold time for the display. DISPDWR/ goes to the display directly. DISPBSY is a handshake signal that, when asserted high, indicates that the display is busy. When the signal is low, it indicates that the display is ready to accept the next character or command. DISPBSY is monitored by the host via Status Register 1 bit 7 (U33 pin 9).

#### Display Data Buffer Latch (I/O location = \$000E Write-Only)

7 6 5 4 3 2 1 0 DISPD7 DISPD6 DISPD5 DISPD4 DISPD3 DISPD2 DISPD1 DISPD0

For more information, including the character set codes and cursor commands, see the Futaba Dot Matrix VFD Module M202SD01HA Instruction Manual.

#### Lexicon

#### Footpedal ADC

An Analog Devices ADC0804 (U37) performs 8-bit A-to-D conversion for the footpedal input. Note that this input (J8) can also be used as a footswitch input in addition to the dual footswitch input jack (J9).

Conversion is started by an I/O write to location \$0090. Conversion data is ready after the ADCDONE/ is asserted low (Status Register 0 bit 7). Conversion data is read by an I/O read from location \$0090. ADCEN/, the enable for both reads and writes, is sourced by a 74AC00 (U42) via a series-terminating resistor.

#### **Footswitches**

The stereo 1/4" jack at J9 provides input for two footswitches. The primary switch should be wired from the tip to the sleeve. (This is the circuit that is used on a mono-plug footswitch.) The secondary switch should be wired from the ring to the sleeve. Each one can be normally-open or normally-closed. The two inputs can also accept a 0-5V voltage level. FB15-16 and C111-112 provide RFI isolation of the footswitches to prevent any high frequency signals from entering or exiting the box. R100, R102, D15 and D16 provide current limiting and overvoltage protection. R99 and R101 pull the inputs high when the circuit is open. FOOTSWT and FOOTSWR and the respective signals that go to Status Register 0 bits 7 and 0 for host processor monitoring.

#### MIDI

The MIDI interface in the PCM 91 complies with the MIDI specification. MIDI is implemented using the on-chip serial port of the V40 with buffering between it and the rear-panel 5-pin DIN jacks (J13-J15).

MIDI IN is accepted from J15. A 6N138/139 (U24) provides opto-isolation to source the buffered MIDI signal MIDIIN. This buffered signal goes to the RxD input of the V40 (U34 pin 34).

The unbuffered MIDIOUT signal is sourced from the TxD output of the V40 (U34 pin 35). It is then buffered by a 74HC14 schmitt trigger inverter (U25) and a 2N3904 transistor (Q5) before going to the MIDI OUT jack (J13).

MIDI THRU is sourced by a 74HC14 (U25) and a 2N3904 transistor (Q6) which is a buffered version of the MIDI input (MIDIIN). The MIDI THRU output is provided at the rear panel via J14. W4 provides selection between normal MIDI THRU operation of J14, and a special test mode. For normal operation, W4 should have a jumper shunt on pins 1 and 2. For testing, the jumper may be put on 2 and 3 to have the MIDI THRU jack duplicate the function of the MIDI OUT iack.

#### Analog I/O (Host Control Interface)

The following describes analog I/O control signals from the host. For further information, see Analog Circuitry.

ADCAL/ is a host control signal going to the A-to-D converter (ADC) and the D-to-A converter (DAC). ADCAL/ must be asserted low during power-up to calibrate the ADC and DAC, then brought high for normal operation. ADCAL/ must be brought low whenever the samp[le rate changes to maintain proper operation of the converters.

#### Control Register 1 (I/O location = \$0001 Write-Only)

7 6 5 4 3 2 1 0 FIMTMSK/ DIOMSK/ LEDSEN **ADCAL/ Spare** PRGINTP7 PRGINTP6 PRGINTP5

The MUTE/ signal when asserted (low) opens the analog output relays to prevent any audio glitches from reaching the analog outputs during power-up and power-down. Also, the MUTE/ signal, when asserted-low gates off analog input, analog output, and digital input serial streams. This gating is done by three sections of a 74HC08 AND gate (U45). When the MUTE/ signal is de-asserted (high), the analog output relay is closed, and the serial audio streams are enabled, allowing audio to pass through.

#### Control Register 0 (I/O location = \$0000 Write-Only)

7 6 5 4 3 2 1 0 HMRST OUTLVLD **MUTE**/ DIORST/ FRCMOD 56KRST/ LEXRST/ SLVRST/

When the control signal HIOUTLVL is asserted (high), the +4 dBu setting for analog output level is selected. When HIOUTLVL is not asserted (low), the -10 dBu setting for analog output level is selected.

#### Headroom LED Register 1 (I/O location = \$0008 Write-Only)

7 6 5 4 3 2 1 0 **HIOUTLVL** RHRCOL/ LEDOVRLD/ LED-6DB LED-12DB LED-18DB LED-24DB

#### Digital I/O

The host is responsible for managing the channel status of the Crystal Semiconductor CS8412 digital audio receiver, and the Crystal Semiconductor CS8402 digital audio transmitters. Status Register 2 and Control Register 2 contain bits to monitor and set channel status bits received and transmitted respectively. More details on Digital I/O are given later in this chapter.

#### **System WordClock Source Selection**

The user can select from among three different wordclocks (sample-rates): 44.1kHz, 48kHz and External. An 11.2896 MHz crystal (Y2) is used to derive the 44.1kHz wordclock, and a 12.2880 MHz crystal (Y1) is used to derive the 48.0kHz wordclock. (Both crystal circuits use a 74HCU04 (U22,U21) as crystal drivers operating the crystal in its parallel resonance mode.) An on-chip PLL on the CS8412 (U15) digital audio receiver is used to derive External wordclock.

The following table outlines the options for the wordclock source under host control. Note that appropriate digital I/O bits need to be set accordingly.

| CTRL2<7><br>SRSSEL1 | CTRL2<6><br>SRSSEL0 | Wordclock Source                 |

|---------------------|---------------------|----------------------------------|

| 0                   | 0                   | Internal 44.1kHz                 |

| 0                   | 1                   | Internal 48kHz                   |

| 1                   | 0                   | External Sync from Digital Input |

| 1                   | 1                   | Disabled (DC tied low)           |

A 74HC253 (U23) multiplexer controls selection of sources. The multiplexer's output is 256FS. A 74AC74 dual flip-flop (U27), two 74HC161 counters (U28,U29), and a 74HC175 quad flip-flop (U26) divide down 256FS to other various wordclock-dependent clock signals. The following is a summary of these clock signals and their functions:

| 256FS | Other Variations: | PT256FS, 256FSA                                                                                   |

|-------|-------------------|---------------------------------------------------------------------------------------------------|

|       | Frequency:        | 256 x selected wordclock frequency (50% duty cycle) @44.1 KHz = 11.2896MHz; @48.0kHz = 12.2880MHz |

|       | Function:         | a. Goes to 74AC74 (U27) to divide clock down further.                                             |

|       |                   | b. Goes to the A/D and D/A converters (U8, U10) as their master input clock.                      |

|       |                   | c. Goes to DSP board connector (J16) for future functions.                                        |

| 128FS | Other Variations: | PT128FS                                                                                           |

|       | Frequency:        | 128 x selected wordclock frequency (50% duty cycle) @44.1kHz: 5.6448MHz; @48.0kHz: 6.1440MHz      |

|       | Function:         | a. Goes to 74AC74 (U27) to divide clock down further.                                             |

|       |                   | <ul><li>b. Goes to CS8402 digital audio transmitters (U17, U18) as their master clock.</li></ul>  |

| 64FS  | Other Variations: | PT64FS, 64FSB, 64FS/, 64FSA (inverted)                                                            |

|       | Frequency:        | 64 times the selected wordclock frequency (50% duty-cycle)                                        |

|       |                   | @44.1kHz: 2.8224MHz; @48.0kHz: 3.0720MHz                                                          |

|       | Function:         | a. Goes to two 74HC161s (U28, U29) and a 74HC175 (U26) to divide the clock down further.          |

|       |                   | b. Goes to AK5391 ADC (U10), CS4390 DAC (U8), and the Lexichip-2 on the DSP board.                |

|       |                   | c. Goes to CS8412 digital audio receiver (U15) and                                                |

CS8402 digital audio transmitters (U17, U18).

**AIOFRAME**

Frequency:

2 times the selected wordclock frequency (High going pulse once every 32 64FS bit clocks.)

Function:

Goes to the Lexichips on the DSP board to mark the start of a sample frame. (2 frames/Wordclock pe-

riod.)

WC/ Other variations:

Frequency:

WCA/, CHSEL (inverted)

User-selected Wordclock frequency of 44.1kHz,

48kHz, or External.

Function:

a. The falling edge of WC/ (or the rising edge of CHSEL) denotes the beginning of a sample period. b. Goes to Lexichip on the DSP board via connector J16 to interrupt or reset the processors to the first instruction of the sample-period's instruction se-

quence.

c. WCA/ goes to the ADC and DAC to indicate, when low, that the serial audio data frame corresponds to the right channel. Otherwise it corresponds to the left channel.

#### **System Reset Circuitry**

PCM 91 reset circuitry consists of four functional blocks, three of which join together and generate the Master Reset (MRST/) signal. The Watchdog Timer, the +5V Monitor, the reset delay circuitry and the Reset Register. The reset circuitry has no provision for early detection of power failure. Therefore, if the +5V Monitor detects less than 4.3V, the hardware will immediately force reset.

After a successful power on and a delay of approximately 0.75 sec., the Host CPU reset, the Reset Register reset, and the UART reset are released. The outputs of the Reset Register, except the Host Master Reset (HMRST), are left in an active state. It is, therefore, the responsibility of the software to release reset for other devices after the reset cycle. The Host can assert Host Master Reset, causing the Watchdog Timer circuitry to create a reset pulse to prevent reset latchup.

#### **Watchdog Timer**

The main component of the Watchdog timer circuitry is a Monostable Multivibrator, U48 (74HC4538). The HC4538 has a very well defined trigger input. They are all edge sensitive and have hysteresis. This design takes advantage of that and the retrigger capability of the multivibrator. Kicks from the Host ensure that the Q output of the first device stays high, provided that the kicks occur in shorter intervals than the pulse width. If a kick does not happen within the required time period, the first device will time out and its output will change state from high to low, triggering the second device, which will generate a pulse which will cause C182 to discharge, resetting the system. After the reset pulse disappears, C182 will start charging, as during the power on cycle. The output or the +5V Monitor is also connected to the second MMV, through an AND gate, to ensure an instant reset pulse when power is interrupted. The HMRST signal is connected to the second device's positive edge input, thereby triggering a reset pulse when HMRST is asserted.

As the Watchdog timer circuitry is inactive after power on until it is kicked, the software has to deliver the first kick to activate the timer.

Theory of Operation Lexicon

+5V Monitor: The +5V monitor U53 (Motorola MC34164) is a Micropower Undervoltage Sensing Circuit which triggers at +4.33V (+5V increasing) and +4.27V (+5V decreasing). It has an Open Collector output. This device is used to control the Battery Backup and Reset circuitry. The combination of R183 and R184 is selected to ensure minimum VIH when C182 is fully discharged and the +5V monitor's output transistor is turned off.

All control registers are initialized with their outputs in a low state. Control Register 0 contains all other sub-system resets including resets for the digitial I/O circuitry (DIORST/), SLVRSTX/, SLVRSTY/, and LEXICHIP-2 (LEXRST/) on the DSP board. HMRST is a control register bit which will, when set, reset the entire unit. When the unit is reset via HMRST, the control register itself will be cleared after a delay.

MUTE/ is another initialization related control bit. Like the other control bits, it powers up in the low state. This enables all muting circuitry, including holding the audio output relays in an open state. The MUTE/ signal, when asserted, isolates the outputs (both digital and analog) from any power-on/power-off glitches.

The following summarizes the bits involved reset and initialization in Control Register 0:

#### Control Register 0 (I/O location = \$0000 Write-Only)

7 6 5 4 3 2 1 0 HMRST OUTLVLD MUTE/ DIORST/ FRCMOD 56KRST/ LEXRST/ SLVRST/

#### **Status Bits Summary**

#### Host Status Register 0 (I/O location = \$0080 Read-Only)

7 6 5 4 3 2 1 0 FOOTSWT Spare CWRPROT CARDDET/ CARDBVD2 CARDBVD1 spare FOOSWR

FOOTSWT Footswitch Jack Tip Input Level.

CWRPROT PCMCIA Card Write Protect.

CARDDET/ PCMCIA Card Detect (Asserted-Low).

BVD2 PCMCIA Card Battery Voltage Detect Bit 2

BVD1 PCMCIA Card Battery Voltage Detect Bit 1

FOOTSWR Footswitch Jack Ring Input Level

#### Host Status Register 1 (I/O location = \$0082 Read-Only)

DISPBSY LWAITY/ BATLOW LEXCFLG/ SHINTY/ LWAITX/ reserved SHINTX

DISPBSY

LWAIT/

Lexichip Y WC Wait line (Asserted Low)

BATLOW

BATLOW

LEXCFLG/

SHINTY/

LWAITX/

Slave Z80 Y to Host Interrupt

LWAITX/

SHINTX

Slave (Z80) X to Host Interrupt.

Theory of Operation

PCM 91 Service Manual

Host Status Register 2 (I/O location = \$0086 Read-Only)

7 6 5 4 3 2 1 0 ADCDONE/ ERF F2/IGC FI/ORG F0/C3/ E2/C2/ E1/C1/ E0/C0/

ADCDONE/ Footpedal ADC done. (Asserted-low)

The following bits are explained in more detail in the Digital I/O Receiver section.

ERF Digital I/O Receiver Error Flag. Digital I/O Receiver Frequency Reporting Bit 2/ F2/IGC Ignorant Category Bit. Digital I/O Receiver Frequency Reporting Bit 1/ F1/ORG Original Bit Digital I/O Receiver Frequecy Reporting Bit 0 / CS3/ F0/C3/ Digital I/O Receiver Error Condition Bit 2 (asserted high)/ E2/C2/ CS2/ (asserted low) Digital I/O Receiver Error Condition Bit 1 (asserted high)/ E1/C1/ CS2/ (asserted low) E0/C0/ Digital I/O Receiver Error Condition Bit 0 (asserted high) CS2/ (asserted low)

#### **Control Bits Summary**

Control Register 0 (I/O location = \$0080 Write-Only)

7 6 5 4 3 2 1 0

HMRST OUTVLD MUTE/ DIORST/ SLVRSTY/ reserved LEXRST/ SLVRSTX/

HMRST Host Master Reset.

OUTVLD Digital Output Valid Bit.

MUTE/ Mute Analog I/O (asserted low)

DIORST/ Digital I/O Circuitry Reset (Asserted Low)

SLVRSTY/ Slave Z80 Y Reset (Asserted Low)

LEXRST/ Lexichip-2 Reset (Asserted Low)

SLVRSTX/ Slave Z80 X Reset (Asserted Low)

Control Register 1 (I/O location = \$0082 Write-Only)

7 6 5 4 3 2 1 0

SHYIMSK/ DIOIMSK/ LEDSEN ADCAL/ Spare PRGINTP7 PRGINTP6 PRTGINTP5

SHYIMSK/ Slave-to-Host Interrupt Y Mask (Asserted Low)

DIOIMSK/ Digitial Input Interrupt Mask

DIOIMSK/ Digitial Input Interrupt Mask

LEDSEN Front-Panel LEDs enable

ADCAL/ A-to-D Converter Calibrate (asserted low)

PRGINTP7 Programmable Interrupt Priority 7

PRGINTP6 Programmable Interrupt Priority 6

PRGINTP5 Programmable Interrupt Priority 5

#### Control Register 2 (I/O location = \$0084 Write-Only)

7 6 5 4 3 2 1 0 SRSSEL1 SRSSEL0 DIOCSSEL OUTCS15/ OUTCS3/ OUTCS2/ FC1 FC0

The following bits are explained in more detail later in this section.

SRSSEL1:0 Wordclock Source Selection Bits 1:0

DIOCSSEL Digital I/O Receiver Channel Status Select.

OUTCS15/ Digital I/O Transmitter Channel Status Bit 15 Output (asserted low)

OUTCS3/ Digital I/O Transmitter Channel Status Bit 3 Output (asserted low)

OUTCS2/ Digital I/O Transmitter Channel Status Bit 2 Output (asserted low)

FC1:0 Digital I/O Transmitter Frequency Control Bits 1:0.

#### Control Register 3 (I/O location = \$0086 Write-Only)

7 6 5 4 3 2 1 0 CREG/ DISCARD/ AES\_INSEL MAPINSRAM CA19 CA18 CA17 CA16

CREG/ PCMCIA Register Select (Asserted-Low)

DISCARD/ Disable PCMCIA Card Drivers (Asserted-Low)

AES\_INSEL Select AES/EBU Digital Audio Input

(otherwise S/PDIF Input is selected)

MPINSRAM Map In RAM to reserved ROM space

CA<19:16> PCMCIA Card Address <19:16> (Page Address)

#### **DSP Board Circuitry**

The PCM 91's DSP board is Lexicon's proprietary digital signal processing module. It does not contain any servicable parts. Contact an authorized repair facility, or Lexicon Customer Service for exchange or repair.

#### Digital Audio I/O Circuitry

The PCM 91 supports both S/PDIF (IEC-958) consumer and AES/EBU professional digital audio formats. Two RCA jacks (J12) are provided on the rear panel for the S/PDIF interface. The white jack is the input, the red jack is the output. Male and female XLR connectors are used for the AES/EBU interface. Sample rates of 48, 44.1 and 44.056kHz are supported.

#### **Digital Audio Receiver**

The S/PDIF input is terminated with a  $75\Omega$  resistor per IEC 958 specifications and 33 pF caps for RFI suppression. The input signal passes through a 0.01uF DC blocking cap to a 74HCU04 (U19) configured as an amplifier to insure its levels exceed the threshold of the CS8412 receiver. BAV99 diodes provide overvoltage protection for the 74HCU04.

The AES/EBU input is terminated by a 1:1 transformer and an 110W resistor. The input signal goes to a 75ALS180 differential receiver (U14) which features a TTL-compatible output.

A 74HC4053 multiplexer (U16) selects the appropriate digital audio input. When AES\_INSEL is high, the AES/EBU input is chosen; when low, S/PDIF is selected. The output of the mux is AC-coupled to the input of the CS8412 digital audio receiver (U15). Note that the meaning of the Channel Status bits decoded by the CS8412 change depending on whether the digital audio format is professional or consumer.

The CS8412 locks onto the frequency of the incoming S/PDIF signal with its internal PLL. R105 and C117 provide the time constant for the PLL Filter. C115, C116, and R104 provide power supply isolation and bypass capacitance for the CS8412's PLL circuitry and other analog circuitry. The output of the PLL, the MCK pin, sources the 256FS master clock. When external lock is selected by the 74HC253 Multiplexer (U23), this serves as a master clock for all digital audio clocking. This clock has 256 pulses per wordclock period.

The CS8412 has individual output pins for the more popular channel status bits. The function of Host Status Register 2 bits 5:0 is determined by DIOCSSEL (Control Register 2 bit 5). If DIOCSSEL is high, Status Register 2 bits 5:0 are channel status bits. When DIOCSSEL is high DIOCSSEL/ should be low clearing the output of the 74HC74 (U39) that sources the CS12 pin of the CS8412. This ensures that the channel status corresponds to sub-frame 1 (as opposed to sub-frame 2). If DIOCSSEL is low, those bits become Error Condition and Frequency Reporting bits. In either case, Status Register 2 bit 6 indicates an digital audio receiver error condition detected by the CS8412. This is outlined in the following table:

#### Digital I/O

|            |          | Host                         |                       |                         |

|------------|----------|------------------------------|-----------------------|-------------------------|

| Status Bit | DIOCSSEL |                              | Funct                 | ion                     |

| STAT2<0>   | 0        | E0                           | Error Condition bit 0 |                         |

| STAT2<1>   | 0        | E1                           | Error Condition bit 1 |                         |

| STAT2<2>   | 0        | E2                           | Error Condition bit 2 |                         |

| STAT2<3>   | 0        | F0                           | Frequency Reporting   | g bit 0                 |

| STAT2<4>   | 0        | F1 Frequency Reporting bit 1 |                       |                         |

| STAT2<5>   | 0        | F2 Frequency Reporting bit 2 |                       |                         |

| STAT2<6>   | X        | Error F                      | Flag                  |                         |

| STAT2<0>   | 1        | C0/                          | Professional (low)    | Consumer (high)         |

| STAT2<1>   | 1        | C1/                          | Non Audio             | Non Audio               |

| STAT2<2>   | 1        | CB                           | EMO Emphasis          | C2/ Copy Inhibit        |

| STAT2<3>   | 1        | cc                           | EM1 Emphasis          | C3/ Emphasis            |

| STAT2<4>   | 1        | CD                           | C9/ Channel Mute      | ORIG Original Copy      |

| STAT2<5>   | 1        | CE                           | CRCE/ CRC Error       | IGCAT Ignorant Category |

The Error Flag signal is gated by the Digital I/O Interrupt Mask (DIOIMSK/) with a 74HC08 AND gate (U45). The signal, after being buffered by a 74HC32 OR gate (U38), sources the V40's Non-Maskable Interrupt (HNMI). (The other input to U38 should always be low.) When DIOIMSK/ is high, ERF can trigger the V40's NMI. At that time, the type of error condition can be determined by reading the Error Decode bits. (When doing so, DIOCSSEL, Control Register 2 bit 5, must be set low.) When an error occurs, the corresponding error decode is latched. Since only one error can be indicated at any given time, there is a priority associated with each error code. Validity has the lowest priority while No-Lock has the highest priority. The error code is cleared by bringing the SEL pin of the CS8412 (U15) high for more than eight MCK cycles. From the V40's perspective, this is done by keeping DICSSEL high for 12 T-states or 3 instructions cycles. The following table describes the error conditions:

| E2 | E1 | E0 | Error                | Comments                                                                                                  |

|----|----|----|----------------------|-----------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0  | No Error             |                                                                                                           |

| 0  | 0  | 1  | Validity Bit High    | Validity bit for a previous sample<br>was high since the last clearing of<br>the error codes              |

| 0  | 1  | 0  | Confidence Flag      | The received data eye opening is less than half a bit period, indicating a poor transmission link         |

| 0  | 1  | 1  | Slipped Sample       | A stereo sample has been dropped or re-read due to differences in internal vs. external sample rates      |

| 1  | 0  | 0  | CRC Error (Pro only) | N/A                                                                                                       |

| 1  | 0  | 1  | Parity Error         | Incoming sub-frame does not have even parity as specified by digital audio interface standards            |

| 1  | 1  | 0  | Biphase Coding Error | Biphase coding violation occurred                                                                         |

| 1  | 1  | 1  | No Lock              | PLL is not locked on incoming data stream. Lock is lost after not receiving 4 consecutive frame preambles |

#### PCM 91 Service Manual

The frequency reporting bits are status bits from the CS8412 (U15) that indicate the sample rate of the incoming digital input. When digital input is selected, the system sample-rate should lock to the sample-rate of the incoming signal. In this case, one of three sample-rates is supported: 44.056kHz, 44.1kHz and 48kHz. (32kHz is accepted and will be locked to, but none of the DSP algorithms support it.) The frequency reporting bits' status is the result of a measurement by an internal circuit that uses a 6.144MHz clock as a reference. This reference is supplied by a 74HC74 (U39) that divides down the output of the 12.288 MHz crystal oscillator circuit. If all three frequency reporting bits are zero, it indicates that the incoming sample-rate is out-of-range. Note that the No-Lock condition, indicated by the Error Decoding bits, is a separate condition from being out-ofrange. In either case, audio is muted. The CS8412 receiver outputs zeros upon loss of lock, and outputs the previous valid data for each channel upon detection of an error condition. To meet the Level 2 (Normal Accuracy Mode) specification, of the EIAJ CP-340 standard, only the 400 ppm tolerance is acceptable. Otherwise, the PCM 91 should be considered out-of-lock or going-out-of-lock. The decoding of the frequency reporting bits are summarized in the following table:

|    | F2 | F1 | F0 | Sample Frequency   |  |

|----|----|----|----|--------------------|--|

|    | 0  | 0  | 0  | Out of Range       |  |

|    | 0  | 0  | 1  | 48kHz +4%          |  |

| l  | 0  | 1  | 0  | 44.1kHz +4%        |  |

|    | 0  | 1  | 1  | 32kHz +-4%         |  |

|    | 1  | 0  | 0  | 48kHz +-400ppm     |  |

| ļ. | 1  | 0  | 1  | 44.1kHz +-400ppm   |  |

|    | 1  | 1  | 0  | 44.056kHz +-400ppm |  |

|    | 1  | 1  | 1  | 32kHz +-400ppm     |  |

Theory of Operation Lexicon

#### **Digital Audio Transmitter**

Two independent CS8402 digital audio transmitter ICs are used to implement the digital audio outputs. One CS8402 (U18) is wired for consumer format and dedicated to the S/PDIF output, while the other CS8402 (U17) is wired for professional format and dedicated to the AES/EBU output. The PCM81 cannot support the professional format on the S/PDIF output or the consumer format on the AES/EBU output.

For S/PDIF, the TXP output of U18 goes through a resistive voltage divider to provide a 1 volt peak-to-peak output waveform with a 75W output impedance per IEC 958 specifications. A 33pF capacitor is placed across the output to suppress RFI.

The TXP and TXN outputs of U17 are AC-coupled to a transformer per AES/EBU specifications. After the transformer, the output signal passes through a filter composed of 22W resistors and a 150pF capacitor. This filter suppresses RFI by limiting the rise and fall times of the signal while maintaining the required 110W output impedance.

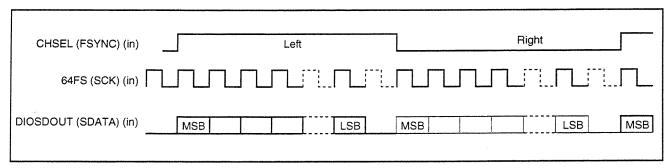

Both CS8402s are hard-wired for the identical serial audio input format as shown:

CS8402 Audio Serial Port Format

Each CS8402 outputs the appropriate Channel Status for the professional (U17) and consumer (U18) digital audio formats. Most of the status bits are set in control register 2 as shown below:

#### **Digital Audio Transmitter Control Bits**

| Host Control Bit | Fur  | nction                           |

|------------------|------|----------------------------------|

| CTRL2<0>         | FC0  | Frequency Control bit 0          |

| CTRL2<1>         | FC1  | Frequency Control bit 1          |

| CTRL2<2>         | CS2/ | Copy Inhibit Out (asserted low)  |

| CTRL2<3>         | CS3/ | Emphasis Out (asserted low)      |

| CTRL2<4>         | C15  | Generation Status (asserted low) |

The professional Emphasis Status bits (AES\_EM0, AES\_EM1) are set by gating CA[16:17] from control register 3 with LEDSEN. The CS8402 uses AES\_EM0 and AES\_EM1 to encode the professional channel status bits C2, C3, and C4. Their encoding and definition is shown in the following table.

**Professional Emphasis Encoding**

| AES_EM1 | AES_EM0 | C2 | C3 | C4 | Function      |

|---------|---------|----|----|----|---------------|

| 0       | 0       | 1  | 1  | 1  | CCITT J.17    |

| 0       | 1       | 1  | 1  | 0  | 50/15 us      |

| 1       | 0       | 1  | 0  | 0  | No emphasis   |

| 1       | 1       | 0  | 0  | 0  | Not indicated |

Frequency control bits FC0 and FC1 specify the sample rate channel status for both consumer and professional formats. Some glue logic (U38, U44) is required to interface FC0 and FC1 with the professional audio transmitter. The following table outlines the function of the frequency control bits.

#### Sample Frequency Encoding

| FC1 | FC0 | C24<br>(cons) | C25<br>(cons) | Function       | C6<br>(pro) | C7<br>(pro) |

|-----|-----|---------------|---------------|----------------|-------------|-------------|

| 0   | 0   | 0             | 0             | 44.1 kHz       | 1           | 0           |

| 0   | 1   | 0             | 1             | 48 kHz         | 0           | 1           |

| 1   | 0   | 1             | 1             | 32 kHz*        | 1           | 1           |

| 1   | 1   | 0             | 0             | 44.1k-CD/48k*  |             |             |

|     |     |               |               | (consumer/pro) |             |             |

<sup>\*</sup>Not supported