Service Manual

LXP-5

Effects Processing Module

exicon

#### **Precautions**

The LXP-5 is a rugged device with extensive electronic protection. However, you should observe the same reasonable precautions that apply to any piece of audio equipment:

- Always use the correct line voltage and power pack.

- Don't install the LXP-5 in a closed, unventilated rack, or directly above heat-producing equipment such as power amplifiers.

- Never attach audio power amplifier outputs (speaker outputs) directly to any of the LXP-5's connectors.

- To prevent fire or shock hazard, do not expose the LXP-5 to rain or moisture.

#### **FCC Notice**

#### Class A Computing Device

This equipment generates, uses, and can radiate radio frequency energy. If not installed and used in accordance with the instruction manual, it may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J, Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his/her own expense will be required to take whatever measures are needed to correct the interference.

The Federal Communications Department has prepared a booklet which you may find useful:

"How to Identify and Resolve Radio-TV Interference Problems"

This booklet is available from the US Government Printing Office, Washington, DC 20402, Stock No. 004-000-0345-4.

Copyright © 1989

Lexicon Inc.

100 Beaver Street

Waltham MA 02154 USA

617-891-6790

Fax: 617-891-0340

#### All Rights Reserved

This publication is protected by copyright and all rights are reserved. No part of it may be reproduced or transmitted by any means or in any form, without express prior consent in writing from Lexicon.

# **Table of Contents**

| 1. | LXP-5 Controls and Connectors            |

|----|------------------------------------------|

|    | Front Panel1-2                           |

|    | Rear Panel1-3                            |

|    | Power1-4                                 |

|    | Audio Cabling1-4                         |

|    | Periodic Maintenance 1-4                 |

|    | Ordering parts                           |

|    | Returning units for service              |

|    | Trotariang arms for service              |

| 2. | Performance Verification                 |

|    | Front Panel Diagnostics2-2               |

|    | Using Diagnostic Tests2-3                |

|    | Test Programs                            |

|    | Clocks and Power Supply Measurements2-10 |

|    | Performance Tests2-12                    |

|    | Troublesheating 2-12                     |

|    | Troubleshooting2-21                      |

| 3. | Circuit Description                      |

| o. | Analog Block Diagram3-2                  |

|    |                                          |

|    | Power Supply                             |

|    | Reset                                    |

|    | Battery Backup3-5                        |

|    | Analog Circuitry3-5                      |

|    | Converter Circuitry3-6                   |

|    | Output Circuitry3-7                      |

|    | Digital Block Diagram3-8                 |

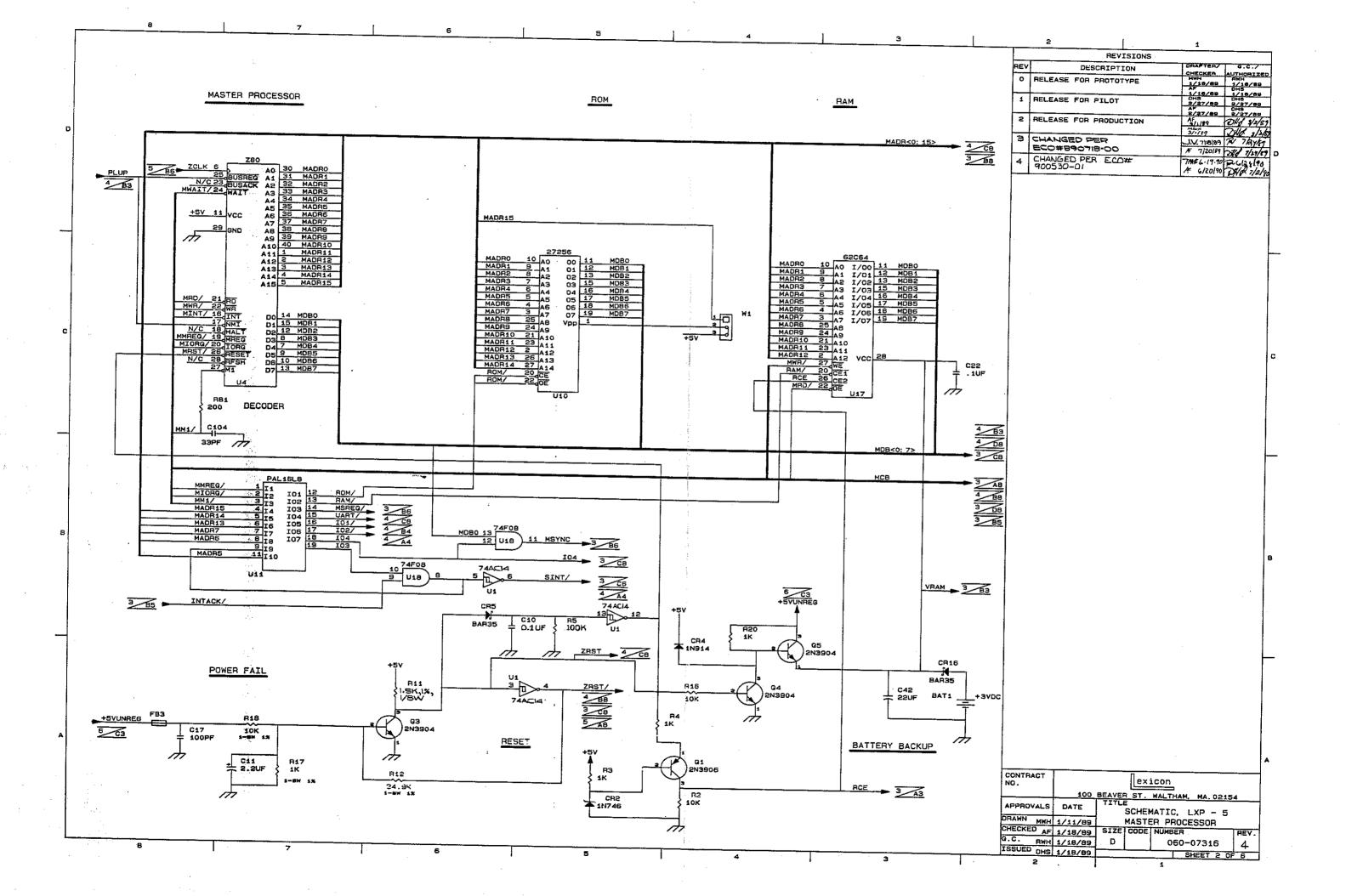

|    | Z80 Processor Circuitry3-9               |

|    | Memory3-10                               |

|    | Master/Slave Interface3-11               |

|    | Master Decoding3-12                      |

|    | Slave Decoding3-13                       |

| •  | Digital Audio Processor3-16              |

|    | UART, I/O3-17                            |

|    | Signal and Bus Descriptions              |

|    | 3                                        |

| 4. | Specifications                           |

| 5. | Parts List                               |

| 6. | Schomatics and Accombin Drawings         |

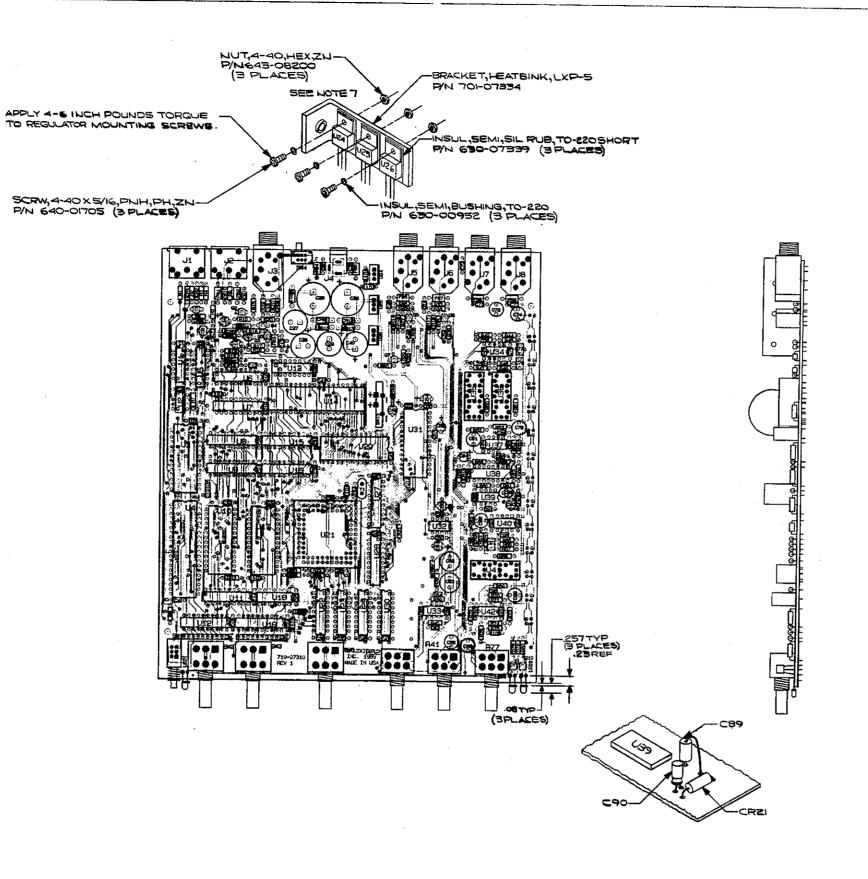

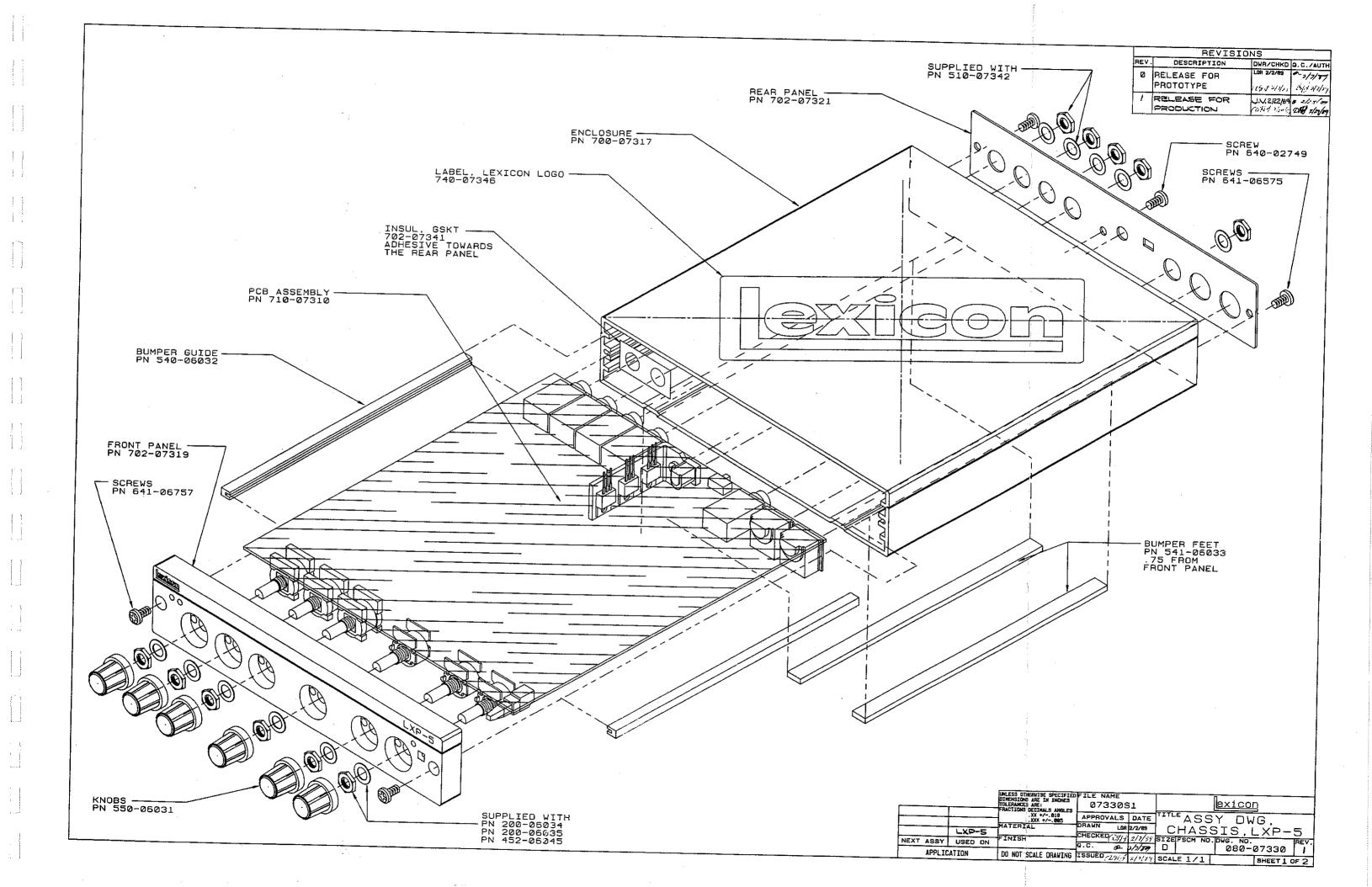

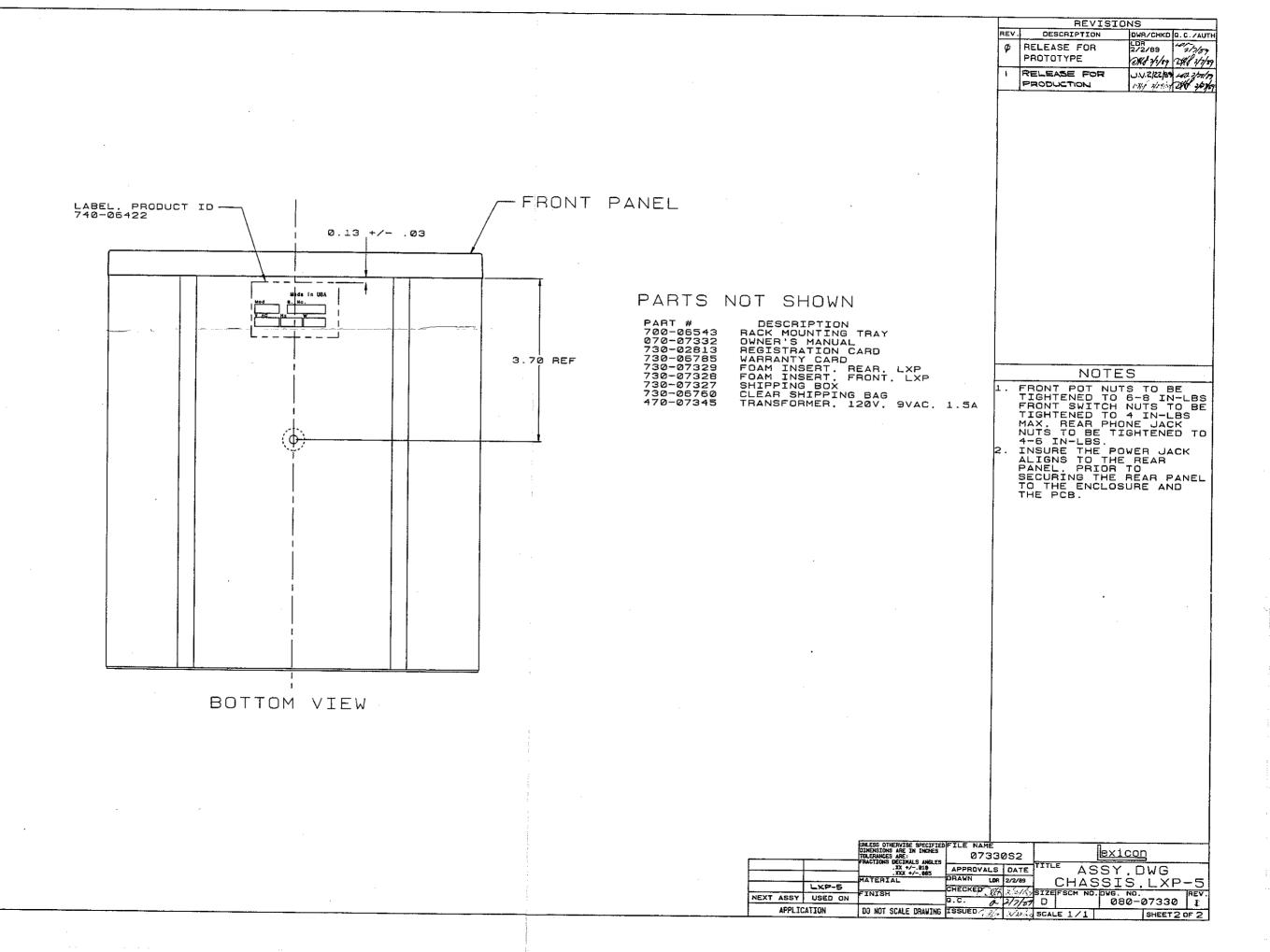

| U. | Schematics and Assembly Drawings         |

Controls and Connectors

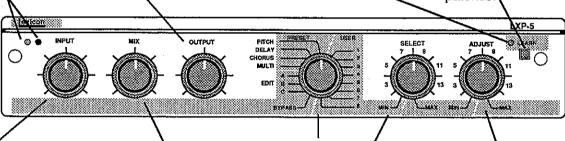

#### **Front Panel**

#### Level indicators

The left LED indicates signal present; the right flashes red when the signal is -3 dB from peak overload.

#### Output

Mix

Controls the signal level sent to the LXP-5's outputs.

#### Learn LED

Confirms that power is on, and blinks in red or green at different rates to indicate LXP-5 status.

#### Learn

This button is used with an external MIDI device to select a MIDI channel, store, edit and retrieve User registers and learn patches.

Sets the audio input level.

Controls the ratio of dry (source) to wet (effect) signal present at the LXP-5 outputs. Turn the control all the way to the left for 100% dry/0% wet. Straight up is 50% dry/50% wet. All the way to the right is 0% dry/100% effect.

#### **Function and Select**

Used for selection of factory presets, User registers, Bypass and three edit modes.

#### Adjust

Used to adjust a single parameter in a factory preset or User register, or to adjust the selected parameter in Edit Mode.

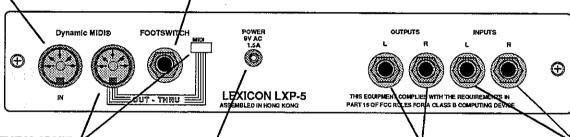

#### Rear Panel

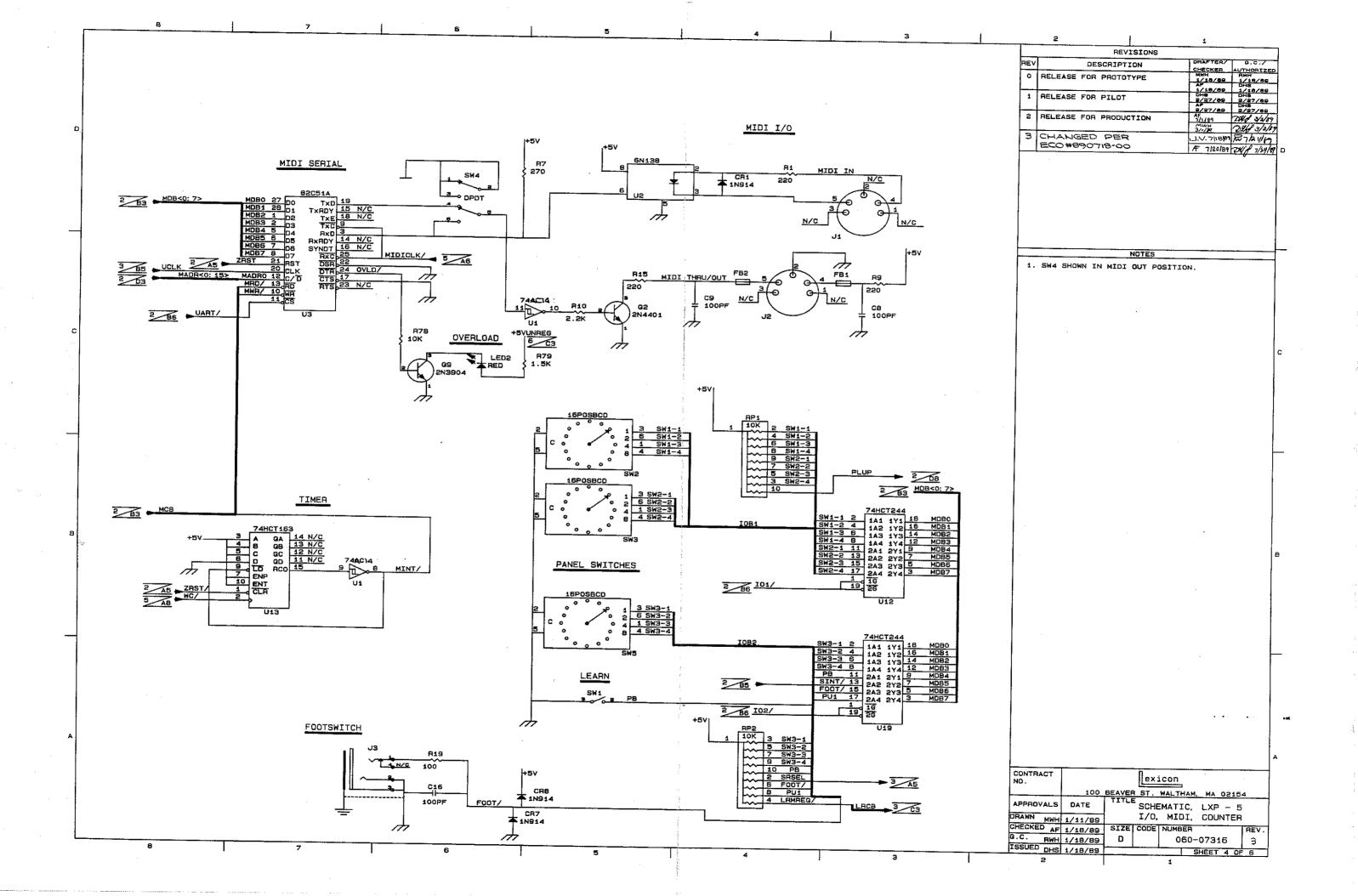

#### MIDI IN

Receives MIDI information from other MIDI equipment, such as master keyboard controllers, MIDI foot controllers, sequencers, and synthesizers.

#### Footswitch

Connector for toggle (push-on/push-off) or momentary contact footswitch for:

Defeat Input Defeat Output Bypass Memory Step

#### MIDI THRU (OUT)

With the recessed slide switch set for MIDI THRU, any MIDI data received is sent without change. The recessed slide switch can also be set for MIDI OUT.

#### Power

Accepts power from the supplied power pack.

#### Outputs (L and R)

Single-ended (unbalanced) stereo outputs provide +4dBu nominal output level.

#### Inputs (L and R)

Single-ended (unbalanced) inputs accept levels from -20 to +20 dBu. Input impedance is 50 kilohms in stereo, 25 kilohms in mono.

#### Power

Connect the LXP-5 power pack to an appropriate AC wall socket, and the cable end to the LXP-5 power connector. The LXP-5 must be used only with the supplied power pack. Voltage requirements are printed on the power pack. The LXP-5 has no power switch—it can be left on all the time. To keep the power plug from working loose from the rear of the unit during travel, you may wish to apply a small amount of silicone sealer to the plug after inserting it.

# **Audio Cabling**

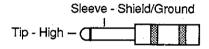

Under most conditions, cables which have a single conductor and a shield are adequate to connect the audio inputs and outputs of the LXP-5 to other equipment.

However, to insure the best performance, especially under high EMI (Electrical Magnetic Interference) conditions, cables with a twisted pair and separate shield are recommended. When using this type of cable, connect one of the twisted pairs to the tip of the phone jack, the other to the sleeve. (Be sure to connect the shield at one end only.) The shield should be connected at the input jack of the LXP-5 for input cables, and at the input of the piece of equipment connected to the LXP-5 output jack.

A tip/sleeve phone jack is recommended for the audio connections.

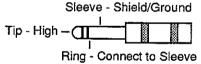

A tip/ring/sleeve jack may also be used. Just be sure to short the ring and sleeve.

## Periodic Maintenance

Under normal conditions the LXP-5 requires minimal maintenance. Use a soft, lint-free cloth slightly dampened with warm water and a mild detergent to clean the exterior surfaces of the unit.

Do not use alcohol, benzene or acetone-based cleaners or any strong commercial cleaners.

Avoid using abrasive materials such as steel wool or metal polish. If the unit is exposed to a dusty environment, a vacuum or *low-pressure* blower may be used to remove dust from the LXP-5 exterior.

# Obtaining Factory Parts and Service

When ordering parts, identify each part by type, value and Lexicon Part Number. Replacement parts can be ordered from:

**Ordering Parts**

Lexicon Inc. 100 Beaver Street Waltham MA 02154 Telephone: 617-891-6790 Fax: 617-891-0340

ATT: Customer Service

# Before returning a unit, consult with Lexicon to determine the extent of a problem.

Returning units for service

If you choose to return an LXP-5 to Lexicon for service, Lexicon assumes no responsibility for the unit in shipment from customer to the factory, whether the unit is in or out of warranty. All shipments must be well packed (using the original packing materials if possible), properly insured, and consigned to a reliable shipping agent.

When returning a unit for service, please include the following information:

- ° Name

- ° Company name

- ° Street address

- ° City, State, Zip Code, Country

- ° Telephone number (including Area Code)

- Serial number of unit

- ° Description of the problem

- Desired return date

- ° Preferred method of return shipment

Please include a brief note describing conversations with Lexicon personnel and give the name and telephone number of the person directly responsible for maintaining the unit.

Do not include accessories such as manuals, cables, etc. with the unit.

Performance Verification

# Performance Verification

Inspect the unit for any obvious signs of physical damage. Verify that all pots, the MIDI OUT/THRU selector switch, the LEARN momentary push button and the 16-position rotary switches operate smoothly and correctly. (Refer to the LXP-5 Owner's Manual for detailed explanations of functionality.)

Verify that all screws and rear panel jacks are secure.

Inspect the AC power transformer for any signs of physical damage. Make sure its output rating is 9VAC at 1.5 Amp and the appropriate 5mm/2.5mm barrel connector is attached.

# Front Panel Diagnostics

Power on the LXP-5 while holding in the LEARN button on the front panel of the unit. When the LEARN button is released, the LXP-5 will enter Diagnostic Mode and will be awaiting the selection of a diagnostic test.

Diagnostic test programs are selected by turning the FUNCTION knob to one of its 16 positions (see Table 1 below). Slave Tests and Alternative System Exits also require a turn of the ADJUST knob to choose the specified diagnostic program. (See Tables 2 and 3.) Once a diagnostic test has been selected, the program is activated by pressing and releasing the LEARN button.

Generally, a test is performed once and the results are displayed upon completion of the test. In the case of tests marked by an asterisk (\*) the tests are performed continuously; the results are displayed when the LEARN button is pressed and released a second time.

Unless noted otherwise in the test descriptions, successful completion of a diagnostic test is indicated by red flashing of the bicolor LEARN LED (located at the far right of the front panel). Failure is indicated by alternate red flashing of the LEARN LED and the OVLD LED (located at the far left of the front panel)

The following tables show the available diagnostic tests. For convenience, some related tests are grouped together under another test, such as Run All.

| FUNCTION Knob<br>Position | Diagnostic Test<br>Program Names                         |

|---------------------------|----------------------------------------------------------|

| BYPASS                    | LED test                                                 |

| EDITC                     | Run All Master tests                                     |

| EDIT B                    | Rotary Switch test                                       |

| EDIT A                    | Clear RAM test (special<br>procedure required)           |

| MULTI                     | Non-volatile memory test                                 |

| CHORUS                    | Footswitch test                                          |

| DELAY                     | Audio Test Loop (runs continuously)                      |

| PITCH                     | Exit to system                                           |

| USER 1                    | ROM test*                                                |

| USER 2                    | Master RAM test*                                         |

| USER 3                    | Master address test                                      |

| USER 4                    | Master interrupt test*                                   |

| USER 5                    | MIDI wraparound test                                     |

| USER 6                    | Slave tests (requires selection via ADJUST)              |

| USER 7                    | DRAM test                                                |

| USER 8                    | Alternative system exits (requires selection via ADJUST) |

Table 1

Diagnostic Test Programs

accessed by FUNCTION knob

| ADJUST Knob<br>Position | Slave Diagnostic<br>Program Names |

|-------------------------|-----------------------------------|

| MIN                     | Run All Slave tests               |

| 2                       | Shared RAM test                   |

| 3                       | Slave Reset test                  |

| 4                       | Slave Communications test         |

| 5                       | Slave Interrupt test              |

| 6                       | Slave RAM test                    |

| 7                       | Master WCS test                   |

| 8                       | Slave WCS test                    |

| 9                       | Run All Slave tests               |

| 10                      | Run All Slave tests               |

| 11                      | Run All Slave tests               |

| 12                      | Run All Slave tests               |

| 13                      | Run All Slave tests               |

| 14                      | Run All Slave tests               |

| 15                      | Run All Slave tests               |

| MAX                     | Run All Slave tests               |

|                         |                                   |

Table 2 Slave Diagnostic Test Programs (User 6) accessed by ADJUST knob

|         | ADJUST Knob<br>Position | Alternative System Exit<br>Program Names                        |

|---------|-------------------------|-----------------------------------------------------------------|

|         | MIN                     | All Registers Dump exit                                         |

|         | 2                       | N/A                                                             |

|         | 3                       | N/A                                                             |

|         | 4                       | N/A                                                             |

| - 1, 18 | 5                       | N/A                                                             |

|         | 6                       | N/A                                                             |

|         | 7                       | N/A                                                             |

|         | 8                       | N/A                                                             |

|         | 9                       | Exit to System without Diagnostics                              |

|         | 10                      | N/A                                                             |

|         | 11                      | N/A                                                             |

|         | 12                      | N/A                                                             |

|         | 13                      | N/A                                                             |

|         | 14                      | N/A                                                             |

|         | 15                      | N/A                                                             |

|         | MAX                     | N/A                                                             |

| An er   |                         | A=none available. these positions are used to select a program. |

Table 3

Alternative System Exit

(User 8)

accessed by ADJUST knob

The LXP-5 diagnostic tests are designed to facilitate the "process of elimination" technique of troubleshooting, but running a single diagnostic test will not always sufficiently isolate a hardware failure. Although related tests are indicated in each test description, it is recommended that the appropriate section of Chapter 3: Circuit Description be read to maximize the usefulness of the diagnostic tests. Chapter 3 also contains a reference glossary of signal and bus abbreviations.

For example: a unit is behaving in an inconsistent manner and Diagnostic tests are run to isolate possible hardware problems. *Master RAM test* is run and passes. *Master Address test* runs and fails. The diagnostic description of *Master Address test* states that the test checks all Master Processor addressable memory. In Chapter 3: Circuit Description: Memory, it is noted that the Master Processor can address all of the Slave RAM and the WCS located in the Lexichip.

**Using the Diagnostic Tests**

Because the *Master RAM test* passed, you can assume that the Master RAM (U17) is functioning properly, and the problem must be in the Slave RAM or WCS. *Slave RAM, Shared RAM, Slave WCS* and *Master WCS* tests should be performed.

- 1. If Shared RAM and Slave RAM tests both fail, the Slave RAM is suspect.

- If Shared RAM test and Master WCS tests fail, the Master/Slave interface circuitry is suspect. Running further diagnostics which exercise the Master Processor's access to the slave bus will verify this. (Slave Communications test, Slave Reset and Slave Interrupt.)

- 3. If both Master and Slave WCS tests fail, the Lexichip is probably faulty.

#### **Test Programs**

#### LED test (Bypass)

This test should cause the OVLD and LEARN LEDs to blink red in unison until the next test selection. If it does not, check the OVLD or LEARN LED hardware, the Master Z80 or MID! Serial circuitry, or the Lexichip.

If either the OVLD or the LEARN LED does not flash in this test, their associated pulsed signals can be traced while the LED test is being run. Keep in mind that these signals originate from different places. —the LEARN LED signal originates at U5 pins 7 and 10; the OVLD LED signal originates from pin 24 on the UART (U3).

#### Run All Master tests (Edit C) requires a MIDI cable

This test is designed to save time by performing the following tests in sequence:

ROM test Master Address test Master Interrupt test MIDI Wraparound test Run All Slave tests DRAM test

This test requires a 5 pin DIN MIDI cable to be connected from the MIDI IN jack to the MIDI OUT/THRU jack located at the rear of the unit. The MIDI OUT/THRU switch should be set to its OUT position (toward the MIDI jacks).

The LEARN LED will flash a few times while this sequence of tests is running. After approximately 30 seconds, the tests should be completed and the results displayed. If all tests pass, the LEARN LED will flash red. If any of the tests fail, the LEARN and OVLD LEDs will alternately flash red. In the event of a failure indication, each test in the sequence should be run individually to determine which has failed.

#### Rotary Switch test (Edit B)

This test compares the positions of the Function, Select and Adjust knobs. When the positions match, the LEARN LED will be green. The LEARN LED will be red when any one of these three knobs is in a different position than the other two. Turn each knob to every position to complete this test. If the test fails, knob hardware may be faulty.

If a switch position combination triggers a failure indication, keep the switches in the failing position. With an oscilloscope set to measure DC levels at 2V/cm, probe pin 1 on SW2, SW3, and SW5 and compare. When all switches are in the same position they should all have the same level. Repeat this procedure on pins 2 through 6, noting any dissimilarities. If one out of the three switches is at a different level, suspect the switch or the signal line's associated pullup resistor (RP1 or RP2).

# CAUTION: RUNNING THIS TEST WILL DELETE THE CONTENTS OF <u>ALL</u> USER REGISTERS.

Clear RAM test (Edit A ) special procedure required

This diagnostic program clears the contents of the master processor's static RAM, and runs a series of write/read tests on the RAM. Since this program will delete any stored user registers, a series of steps are required to activate this procedure. The steps are as follows:

- 1 Set FUNCTION to EDIT A; set SELECT and ADJUST to MIN. Press LEARN. (The LEARN LED will flash red once.)

- 2 Set SELECT and ADJUST to 2; set FUNCTION to BYPASS. Press LEARN. (The LEARN LED will flash red once.)

- 3 Set FUNCTION to *EDIT C*, and press LEARN. (The LEARN LED will flash red once.)

- 4 Press LEARN once again to run the test.

If the LEARN and OVLD LEDs flash alternately at any time during the first three steps, the procedure is not being performed correctly and needs to be reselected by turning FUNCTION to *EDIT A* and pressing LEARN. When the procedure is followed correctly, and the test has been successfully completed, the LEARN LED will flash continuously. Alternate flashing of the LEARN and OVLD LEDs after step 4 indicates test failure. If failure occurs, the Slave and Master RAM ICs (U20, U17) are suspect. If the Slave RAM is failing, run the *Slave tests* to determine whether failure is caused by the support circuitry or the Slave RAM IC.

This test checks the non-volatile area of RAM used by both the master and slave processors by comparing a character string stored in ROM to a character string stored at a specific address in RAM. When the two differ, a failure will result, indicating RAM storage failure may have occurred. Pressing the LEARN button a second time will copy the character string from ROM to RAM and perform the test again. A second failure indicates a possible RAM hardware malfunction or defective Battery Backup circuitry. If the test passes on the second try, power down the unit for at least 10 seconds, then power up in Diagnostic Mode and rerun this test.

Note: This test will fail if the Clear Ram test has been performed since the last copy of the character string from ROM to RAM.

Non-volatile Memory test (MULTI)

#### Test Programs, cont'd.

#### Footswitch test (Chorus)

Performance of this test requires a toggling off/on or momentary contact footswitch with an appropriate 1/4" tip/sleeve plug connected to the FOOTSWITCH jack on the rear panel. If a footswitch is not available, a 1/4" shorting plug may be used.

The OVLD LED will light to indicate that the footwitch is OFF (or that nothing is plugged into the footswitch jack). When the footswitch is ON (or the shorting jack is inserted) the OVLD LED will turn off. If this test fails, check footswitch hardware for defects. Check also J3, R19, C16, CR8, CR7, RP2 and U19.

#### Audio Test Loop (Delay) runs continuously

This diagnostic program tests the converter circuitry audio specifications by producing a digitally processed output signal which is identical to the input signal. When this test is selected, and the the LEARN button is pressed, the LEARN LED will flash once to indicate that the program has been successfully loaded. The Audio Test Loop runs continuously until another diagnostic program is selected. If this test fails, refer to Audio Signal Tracing test later in this chapter. Note that Audio Test Loop does not write or read from the DRAMs in processing the signal.

#### Exit to System (Pitch)

This allows the user to exit Diagnostic Test mode and returns the LXP-5 to its normal operating mode.

#### ROM test (User 1)

This test calculates the ROM checksum and compares it to the stored value. Failure indicates that the code programmed in ROM is probably corrupt.

#### Master RAM test

(User 2)

This tests the area of volatile RAM which is used by the master processor, by requiring the master procesor to store and read various values. If this test fails, check Master RAM (U17), Master data and address busses, Master Z80 and PAL U11.

#### Master Address test

(User 3)

This diagnostic program performs an address test as well as a test of all areas of volatile RAM used by the master processor. The test requires the master procesor to store and read various values in this area of RAM. If this test fails. check Master Ram and associated hardware, as well as Slave RAM, Master/ Slave interface and Lexichip WCS. This test can be used in conjunction with the Slave RAM test and other Slave tests to isolate the specific hardware problem.

# Master Interrupt test

(User 4)

This test checks the interrupt timing of the master processor by comparing it to coded timing loops. Failure indicates a problem in the Interrupt Timing circuitry (U13, U1), or the Lexichip WC/ signal line.

This test checks the MIDI serial port transmit and receive functions. It requires a 5 pin DIN MIDI cable to be connected from the MIDI IN jack to the MIDI OUT/THRU jack located at the rear panel. The MIDI OUT/THRU switch should be set to its OUT position (toward the MIDI jacks). This test takes approximately 5 seconds before results are displayed. Failure indicates a problem with MIDI hardware, or UART (U3).

MIDI Wraparound test (User 5) requires a MIDI cable

The following steps will isolate the problem to the component level:

- 1. Power down the unit and power up in the normal operating mode.

- 2. Set FUNCTION to PITCH; set SELECT to MIN.

- Connect a MIDI cable from MIDI IN to MIDI OUT and set the rear-panel MIDI OUT/THRU switch to OUT.

- 4. When ADJUST is turned, a MIDI message will be sent (and returned to the LXP-5) at each new knob position. The Master Processor should cause the LEARN LED to flicker to acknowledge the receipt of each MIDI signal. If it does not, there is probably a hardware error.

- 5. While ADJUST is turned, the serial MIDI signal can be traced through the MIDI circuitry with an oscilloscope. A pulsed waveform can be traced from the UART TxD pin (U3,pin 19) to U1 pin 10, and then to MIDI output jack J2 pin 5. The signal can then be traced on the MIDI input J1 pin 5. Check the optocoupler output U2 pin 6 for the presence of serial MIDI data and verify that U3 receives this signal on its RxD pin (3).

When this position is selected by FUNCTION, the specific slave test is chosen by turning ADJUST to the appropriate position (see Table 2). Remember to press and release the LEARN button after turning ADJUST to select a test.

Slave tests (User 6)

Choosing any of the designated Run All Slave tests runs the following tests sequentially:

Run All Slave tests (User 6: MIN, 9-MAX)

Shared RAM test Slave reset test Slave communications test Slave interrupt test Slave RAM test Master WCS test Slave WCS test

This program will display success or failure after approximately 5 seconds. If any test in the sequence fails, a failure indication will be displayed. In this case,run each test individually to pinpoint the area of failure.

This diagnostic program tests the area of volatile RAM shared by the master and slave processors. This test consists of storing and reading various values in RAM by the master processor. Failure indicates a problem with the Slave RAM or the Master/Slave interface. Run *Master Address* and *Slave RAM* tests to isolate the problem.

Shared RAM test (User 6: 2)

#### Test Programs, cont'd.

## Slave Reset test

(User 6: 3)

This test checks the ability of the master processor to put the slave processor in reset mode. This test requires the master processor to send a program to the slave processor while holding it in reset. The program instructs the slave processor to load a message into a specific area of memory upon removal of reset. After removing reset, the master processor checks to see if the message is in memory. If this test fails, check the Master/Slave interface and the Master I/O decoding signal. Run all other Slave tests to further isolate the problem.

#### Slave Communications test

(User 6: 4)

This test checks the ability of the master and slave to communicate with each other using shared memory space. Failure indicates a problem with the Slave Decoder, or the Master/Slave interface. Run all other Slave tests to further isolate the problem.

#### Slave Interrupt test

(User 6: 5)

This test checks the ability of the master processor to send interrupts to the slave processor. A program is sent to the slave processor from the master which tells the slave to load a message into a specific area of memory upon receipt of an interrupt. The master processor then sends an interrupt, and checks for the message in memory. Failure indicates a problem in the Master Decoder (U11), or SINT signal hardware. Run all other Slave tests to further isolate the problem.

#### Slave RAM test

(User 6: 6)

This test checks the area of volatile RAM used by the Slave Processor. This test consists of storing and reading various values in RAM by the Slave Processor. This test can be used to help isolate Slave RAM problems by determining if a Slave RAM problem is caused by RAM, Master/Slave interface, or Slave Processor problems. Note that only the upper 4K of RAM is exercised in this test.

#### Master WCS test

(User 6: 7)

This test performs a RAM test on the WCS portion of the Lexichip by the master processor. Failure indicates possible Lexichip problems. This test should be run in conjunction with the *Slave WCS* and *Master Address* tests to eliminate Master/Slave interface problems, and to isolate Lexichip WCS errors.

#### Slave WCS test

(User 6: 8)

This test performs a RAM test on the WCS portion of the Lexichip by the slave processor. Failure of this test and the *Master WCS* test indicate problems with Lexichip WCS.

### DRAM test

(User 7)

This test checks the DRAM in the Lexichip address area. The duration of this test is approximately 30 seconds, after which the results are displayed. Failure indicates a problem with Audio Memory (U22, 23, 29, 30). Faulty WCS will also cause this test to fail.

Test Programs, cont'd.

When this position is selected by FUNCTION, an alternative system exit can be chosen by turning ADJUST (see Table 3). If an ADJUST position is selected for which there is no program, the LEARN and OVLD LEDs will flash alternately to indicate an error. At this time another diagnostic program may be selected.

Alternative System Exits (User 8)

This system exit program instructs the LXP-5 to dump the contents of all user registers through the MIDI OUT jack. This program allows the user to copy these registers to another unit.

All Registers Dump Exit (User 8: MIN)

This program allows the user to exit to the system without going through the boot diagnostic tests. This procedure is useful when troubleshooting a unit that will not power up correctly due to a boot diagnostic failure.

Exit to System without Diagnostics (User 8: 9)

# Static Electricity Precautions

Many of the LXP-5's internal components are extremely sensitive to static electricity. The following practices minimize possible IC damage which can result from electrostatic discharge.

- 1. Don't handle ICs and boards any more than is necessary.

- 2. Discharge personal static by touching the LXP-5 mainframe before handling ICs or boards.

- 3. Handle each IC by its body.

- 4. Do not slide ICs or boards over a surface.

- 5. Avoid having plastic, vinyl or styrofoam in the work area.

- 6. Handle ICs only at a static-free workstation.

- 7. Use only grounded-tip soldering irons.

- 8. Use antistatic containers for handling and transport.

# Clocks and Power Supply Measurements

#### **Equipment Required**

Variac DMM Frequency Counter (50MHz) 50 MHz Oscilloscope Remove the two screws from the LXP-5 front panel and the center screw from the rear panel. Remove the 5 hex nuts from the 1/4" phone jacks on the rear panel. The pc board should now slide outtowards the front of its case, allowing easy access to the circuitry.

- 1. Plug the LXP-5 power pack into the Variac and set output for 120 VAC.

- 2. Set the DMM to measure VAC. Apply power to the LXP-5 and measure the voltage across C25; it should measure between 9 and 11 VAC. If measurement is below 9VAC, the power pack may be faulty.

- 3. Set the DMM to measure VDC and check the regulated voltages for proper levels:

| Location: Power/Ground | Allowable voltage range |

|------------------------|-------------------------|

| U25 pin 3/U25 pin 2    | 11.40 to 12.60 VDC      |

| U26 pin 3/U26 pin 1    | -11.40 to -12.60 VDC    |

| U24 pin 3/U24 pin 2    | 4.75 to 5.25 VDC        |

| U1 pin 14/pin 7        | 4.25 to 4.50 VDC        |

| U38 pin 16/pin 8       | 6.75 to 8.25 VDC        |

| U38 pin 7/pin 8        | -6.75 to -8.25 VDC      |

4. Power off the LXP-5 and measure DC voltage across battery BAT1 with DMM; it should be 3.00 VDC or greater. If voltage is low, replace the battery.

- 1. Set oscilloscope for 2.5v/div (w/X10 probe) and a 1 mSec/div time base.

- Brown Out / Power Down Test

- 2. Connect scope probe to U1 pin 4.

- 3. Vary the Variac output level between 104VAC to 125VAC while monitoring U1 pin 4 on oscilloscope. This level should remain in a logical high condition (+5V).

- 4. Continue to monitor U1 pin 4 with oscilloscope and slowly reduce Variac output to 85 VAC. Pin 4 signal level should go to a logical low condition when the Variac output passes through the 100 85 VAC range. If this test fails, make certain that transformer AC output (across C25) is between 9.0-11.0 VAC with 120 VAC input. If AC transformer is OK, suspect LXP-5 power down reset circuitry failure.

- 5. Return Variac to 120 VAC.

Using the frequency counter, measure the clock frequencies at the following points:

**Clock Measurements**

| Signal Name | Location  | Meas   | Tolerance                 |

|-------------|-----------|--------|---------------------------|

| ZCLK        | U4 /pin 6 | 4MHz   | ±0.5%(3980000-4020000 Hz) |

| MIDICLK     | U3 /pin 9 | 500kHz | ±0.5% (497500 -502500 Hz) |

#### **Peformance Tests**

#### **Equipment Required**

Low Distortion Oscillator with single-ended 600 ohm output, <.005%

THD.

THD+N Distortion

Analyzer/Level Meter with switchable 30Khz or audio bandpass

filtering

Audio input cable single-ended, shielded audio cable with

> 1/4" plug on one end and proper connector on other end to connect to Low Distortion

Oscillator output

Audio output cable single-ended, shielded audio cable w/ 1/4"

plug on one end and the proper connectors

on other ends to connect to THD+N

Distortion Analyzer

Audio terminator plugs two 1/4" plugs, each with a 100K ohm

resistor attached between tip and sleeve

1/4" Shorting plug with tip and sleeve shorted inside shielded

casing

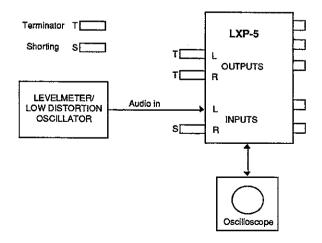

**Audio Signal Tracing**

Input Level: Fully clockwise to Maximum Level

Output Level: Fully clockwise to Maximum Level

Mix: Fully counter clockwise to 100% Dry (unprocessed)

Program: Audio Test Loop (See Diagnostic Tests, Page 2-2)

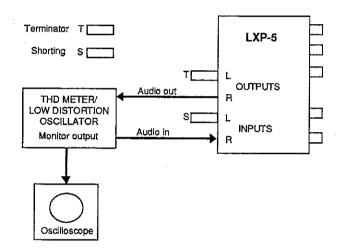

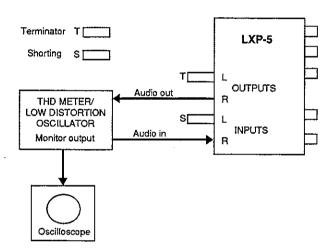

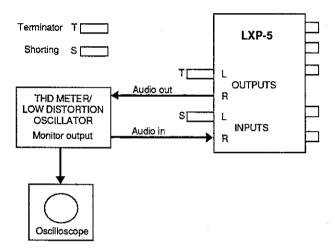

#### **Audio connections**

- 1. Audio input cable from Low Distortion Oscillator output to left or right channel input

- 2. 1/4" shorting plug to unused channel input

- 3. Audio terminator plugs to left and right channel outputs

#### **Procedure**

- 1. Apply a 1kHz signal at -25dBV (159mVp/p) to left channel input for *Left Channel* connection, or to right channel input for *Right Channel* connection.

- With an oscilloscope set to DC coupling, 2v/division sensitivity at 5mS/ division sweep rate, trace audio signal as follows. Observe any excessive DC offset levels on any input or output stage, as this could indicate a supply or amp problem which would affect the audio signal.

- 3. Set Mix control fully counter clockwise.

|                              | Signal Level    |                 |

|------------------------------|-----------------|-----------------|

|                              | Left Channel    | Right Channel   |

| Left channel output (pin 7)  | 4.8Vp/p         |                 |

|                              | (4.6 - 5.0Vp/p) | No Signal       |

| Right channel output (pin 1) | No Signal       | 4.8Vp/p         |

|                              | •               | (4.6 - 5.0Vp/p) |

Analog Input Stage (U42)

4. Turn Input Level Control fully counter clockwise

|                             | Sign         | al Level      |

|-----------------------------|--------------|---------------|

|                             | Left Channel | Right Channel |

| Left channel input (pin 5)  | No Signal    | No Signal     |

| Right channel input (pin 3) | No Signal    | No Signal     |

5. Set Input Level fully clockwise

|                | Signal Level              |

|----------------|---------------------------|

| Input (pin 5)  | 1.0Vp/p (0.95 - 1.05Vp/p) |

| Output (pin 7) | 2.7Vp/p (2.6 - 2.8Vp/p)   |

Pre-emphasis Stage (U40)

|                     | Signal Level                               |

|---------------------|--------------------------------------------|

| Hold Input (pin 2)  | Virtual Ground (No Signal)                 |

| Hold Output (pin 6) | 2.7Vp/p staircase waveform (2.6 - 2.8Vp/p) |

Input Hold Stage (U39)

|               | Signal Level               |

|---------------|----------------------------|

| Input (pin 3) | 2.7Vp/p staircase waveform |

|               | (2.6 - 2.8Vp/p)            |

Comparator (U32)

|                              | Signal Level                                  |

|------------------------------|-----------------------------------------------|

| Right channel output (pin 1) | 2.7Vp/p staircase waveform<br>(2.6 - 2.8Vp/p) |

| Left channel output (pin 7)  | 2.7Vp/p staircase waveform<br>(2.6 - 2.8Vp/p) |

Output Hold Stage (U37)

### De-emphasis Stage (U34)

| Signal Level               |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| 1.15Vp/p (1.10 - 1.20Vp/p) |                                                                                        |

|                            | 1.15Vp/p (1.10 - 1.20Vp/p)<br>1.15Vp/p (1.10 - 1.20Vp/p)<br>1.15Vp/p (1.10 - 1.20Vp/p) |

#### Output Stage (U33)

|                              | Signal Level    |                 |  |

|------------------------------|-----------------|-----------------|--|

|                              | Left Channel    | Right Channel   |  |

| Right channel input (pin 3)  | No Signal       | 4.8Vp/p         |  |

|                              |                 | (4.6 - 5.0Vp/p) |  |

| Left channel input (pin 5)   | 4.8Vp/p         | No Signal       |  |

|                              | (4.6 - 5.0Vp/p) | •               |  |

| Right channel output (pin 1) | No Signal       | 4.8Vp/p         |  |

|                              | -               | (4.6 - 5.0Vp/p) |  |

| Left channel output (pin 7)  | 4.8Vp/p         | No Signal       |  |

|                              | (4.6 - 5.0Vp/p) | _               |  |

#### 6. Set Mix Control fully clockwise

|                      | Signal Level            |

|----------------------|-------------------------|

| Right channel input  | 2.5Vp/p (2.4 - 2.6Vp/p) |

| Left channel input   | 2.5Vp/p (2.4 - 2.6Vp/p) |

| Right channel output | 2.5Vp/p (2.4 - 2.6Vp/p) |

| Left channel output  | 2.5Vp/p (2.4 - 2.6Vp/p) |

7. Keep Mix Control fully clockwise (100% Wet)

# Output Mute (either side of FB6 and 7)

|                     | Signal Level            |

|---------------------|-------------------------|

| Right channel (FB7) | 2.5Vp/p (2.4 - 2.6Vp/p) |

| Left channel (FB6)  | 2.5Vp/p (2.4 - 2.6Vp/p) |

8. Set Mix Control fully counter clockwise (100% Dry)

|                     | Signa           | Level           |

|---------------------|-----------------|-----------------|

|                     | Left Channel    | Right Channel   |

| Right channel (FB7) | No Signal       | 4.8Vp/p         |

|                     |                 | (4.6 - 5.0Vp/p) |

| Left channel (FB6)  | 4.8Vp/p         | No Signal       |

|                     | (4.6 - 5.0Vp/p) |                 |

9. Set Output Level Control fully counter clockwise

|                     | Signal Level |

|---------------------|--------------|

| Right channel (FB7) | No Signal    |

| Left Channel (FB6)  | No Signal    |

Input Level: Fully clockwise to Maximum Level Output Level: Fully clockwise to Maximum Level

> Mix: Fully counter clockwise to 100% Dry (unprocessed)

Audio Test Loop (See Diagnostic Tests) Program:

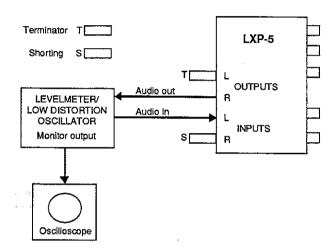

#### Inter-Channel Crosstalk Measurement

#### **Audio connections**

- Audio input cable from Low Distortion Oscillator output to left channel

- 1/4" shorting plug to right channel input 2.

- 3. Audio output cable from right channel output to Level Meter input

- 4. Audio terminator (100k) plug to left channel output

- 1. Apply a 1 kHz signal at -20dBV (283mVp/p) to left channel input.

- Measure Right channel output level . Acceptable level < -60dBV 2. (2.8mVp/p).

- 3. Swap all right and left channel audio connections and repeat steps 1 and 2 on left channel.

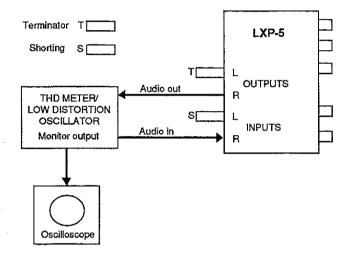

#### Dry (unprocessed) THD Measurement

Input Level: Fully clockwise to Maximum Level

Output Level: Fully clockwise to Maximum Level

Mix: Fully counter clockwise to 100% Dry (unprocessed)

Program: Audio Test Loop (See Diagnostic Tests)

#### **Audio connections**

1. Audio input cable from Low Distortion Oscillator output to right channel input

2. 1/4" shorting plug to left channel input

Audio output cable from right channel output to THD+N Analyzer input

4. Audio terminator (100k) plug to left channel output

- 1. Apply a 1 kHz signal at -20dBV (283mVp/p) to right channel input.

- Measure THD+N at right channel output. Make sure 30kHz or audio bandpass filter on meter is ON. Acceptable reading will be <.01%.</li>

- 3. Swap all right and left channel audio connections and repeat steps 1 and 2 on left channel.

Input Level: Fully clockwise to Maximum Level

Output Level: Fully clockwise to Maximum Level

Mix: Fully counter clockwise to 100% Dry (unprocessed)

Program: Audio Test Loop (See Diagnostic Tests)

Dry (unprocessed) Frequency Response

#### **Audio connections**

- Audio input cable from Low Distortion Oscillator output to right channel input

- 2. 1/4" shorting plug to left channel input

- 3. Audio output cable from right channel output to Level Meter input

- 4. Audio terminator (100k) plug to left channel output

- Apply a 1 kHz signal at -20dBV (283mVp/p) to right channel input. Set Level Meter to measure right channel output as the 0 dB reference. Make sure all filters on meter are OFF.

- 2. Sweep from 20 Hz to 20kHz.

- 3. Right channel output should measure within  $\pm 0.1$  dB (referenced to 1kHz output) over the range.

- 4. Swap right and left channel audio connections and repeat steps 1-3 on left channel.

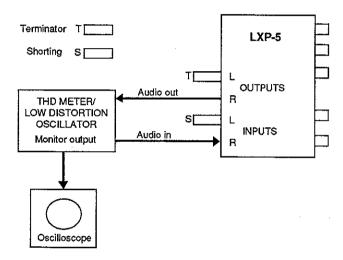

# Wet (processed) THD Measurement

Input Level: Fully clockwise to Maximum Level

Output Level: Fully clockwise to Maximum Level

Mix: Fully clockwise to 100% Wet (processed)

Program: Audio Test Loop (See Diagnostic Tests)

#### **Audio Connections**

Audio input cable from Low Distortion Oscillator output to right channel input

2. 1/4" shorting plug to left channel input

Audio output cable from right channel output to THD+N Analyzer input

4. Audio terminator (100k) plug to left channel output

- 1. Apply a 1 kHz signal at -25dBV (159mVp/p) to right channel input.

- 2. Measure THD+N at right channel output. Make sure THD meter has 30 kHz or audio bandpass filter ON. Acceptable reading will be < .02%.

- 3. Swap all right and left channel audio connections and repeat steps 1 and 2 on left channel.

Input Level: Fully clockwise to Maximum Level

Output Level: Fully clockwise to Maximum Level

Mix: Fully clockwise to 100% Wet (processed)

Program: Audio Test Loop (See Diagnostic Tests)

Wet (processed)

Frequency Response

Measurement

#### **Audio connections**

- 1. Audio input cable from Low Distortion Oscillator output to right channel input

- 2. 1/4" shorting plug to left channel input

- 3. Audio output cable from right channel output to Level Meter input

- 4. Audio terminator (100k) plug to left channel output

- Apply a 1 kHz signal at -25dBV (159mVp/p) to right channel input. Set Level Meter to measure the right channel output as the 0 dB reference. Make sure meter has 30 kHz or audio bandpass filter OFF.

- 2. Sweep from 20 Hz to 15kHz.

- 3. Right channel output should measure within +1.0 to -1.5 dB (referenced to 1kHz output) over the range.

- Swap right and left channel audio connections and repeat steps 1-3 on left channel.

### Dynamic Range/ Signal to Noise

Input Level: Fully clockwise to Maximum Level

Output Level: Fully clockwise to Maximum Level

Mix: Fully clockwise to 100% Wet (processed)

Program: Audio Test Loop (See Diagnostic Tests)

#### **Audio connections**

Audio input cable from Low Distortion Oscillator output to right channel input

2. 1/4" shorting plug to left channel input

3. Audio output cable from right channel output to Level Meter input

4. Audio terminator (100k) plug to left channel output

- Apply a 1 kHz signal at -25dBV (159mVp/p) to right channel input. Set Level Meter to measure right channel output as the 0 dB reference. Make sure meter has 30 kHz or audio bandpass filter ON.

- 2. Unplug input to right channel. This will short out both right and left channel inputs.

- Measure level on right channel output. Acceptable reading will be ≤ -75 dB (referenced to 1kHz output level; typical reading will be about -85dB.)

- 4. Swap right and left channel audio connections and repeat steps 1-3 on left channel.

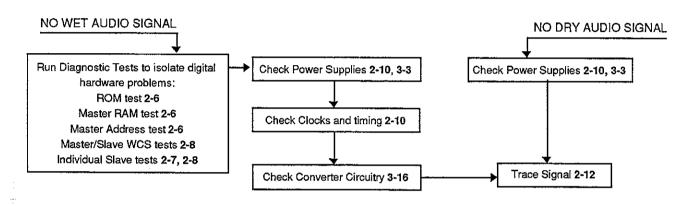

Since Diagnostic Tests can be performed without opening the unit they should generally be run first. This greatly reduces repair time, as a problem can be isolated to a specific circuit, even to a specific IC before opening the unit

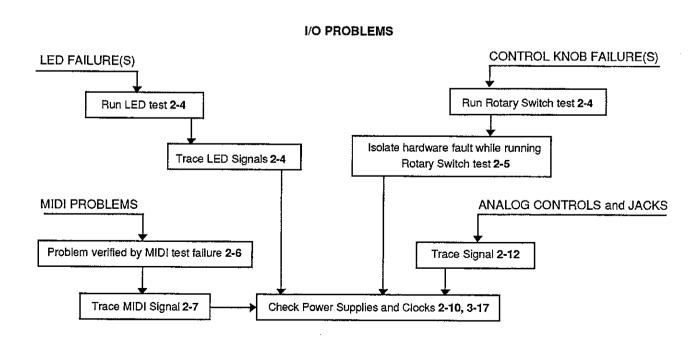

#### **Troubleshooting**

The following presents a diagrammatic version of the recommended troubleshooting procedure with page references.

#### **AUDIO SIGNAL PROBLEMS**

Circuit Description

# Analog Circuit Description

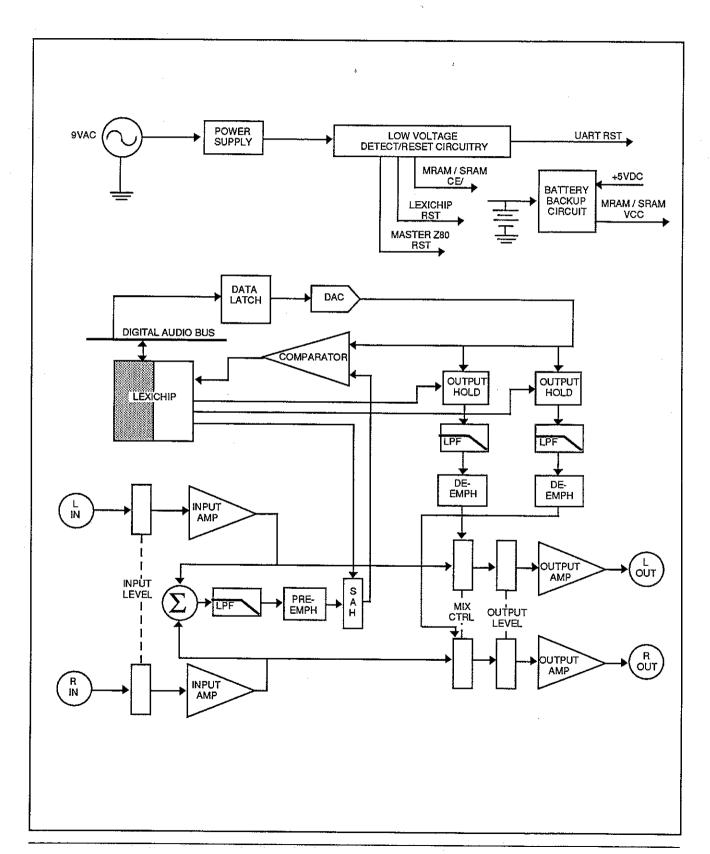

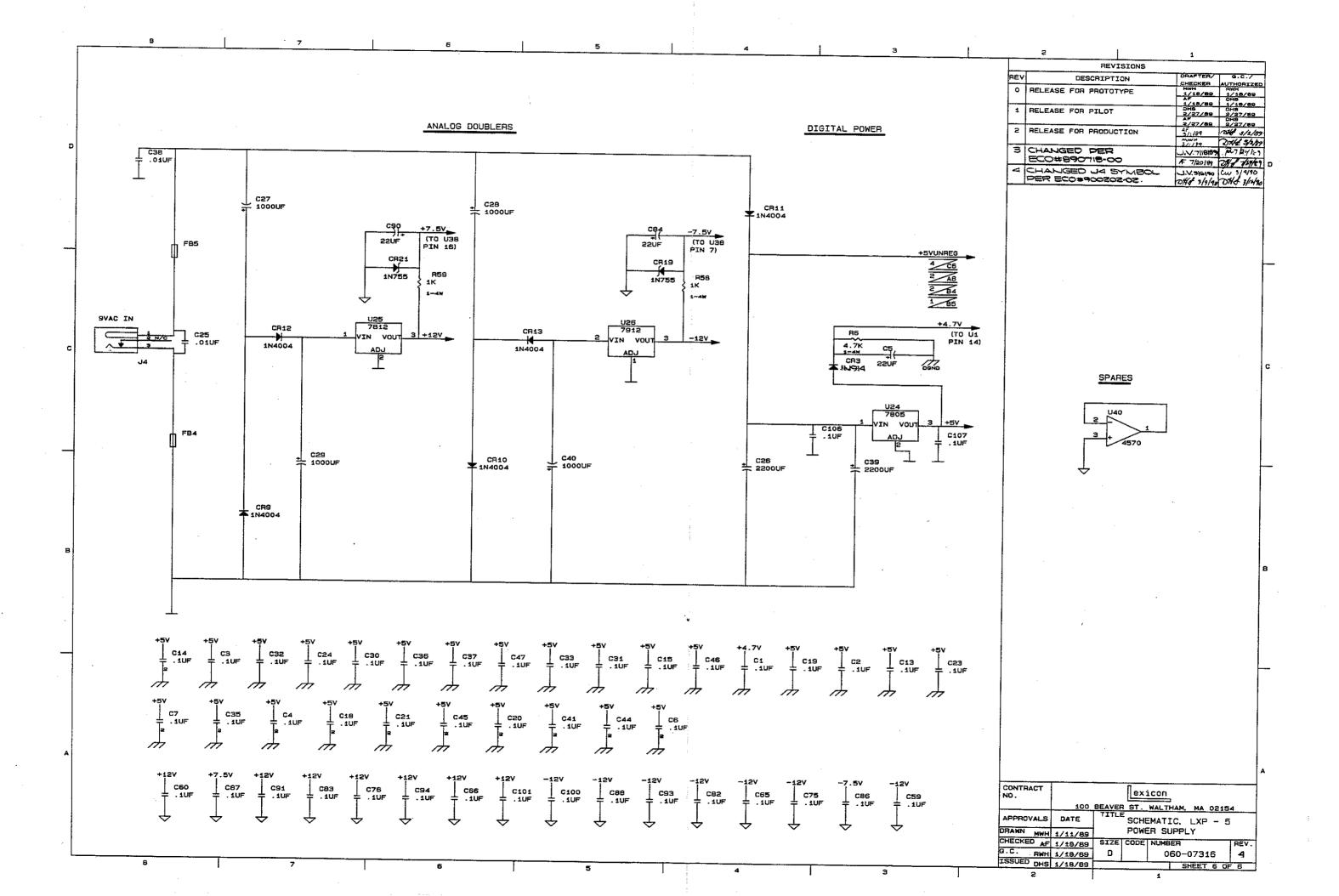

The LXP-5 power supply provides five regulated DC output voltages:

## **Power Supply**

+5 VDC +12 VDC -12 VDC -7.5 VDC +7.5 VDC

AC power is provided by an external transformer rated at 9 VAC @ 1.5 A. The transformer output is terminated with a 5 mm/2.5 mm barrel-type connector, with its mating input jack located at the rear panel of the LXP-5. A .01 uF capacitor, C25, is connected across the AC input to help prevent noise spikes from entering the unit. In addition, C25 along with C38 and ferrite beads FB4 and FB5 stop circuit-generated RFI from radiating through the power line.

A pair of voltage doubler circuits develop the unregulated DC voltages for the  $\pm$  12 volt supplies. C27 and C28 store the peak level of AC input voltage during one half of the AC cycle. This stored charge adds with the next AC half cycle to produce approximately twice the peak AC input voltage across C29 and C40. Diodes CR9 and CR12 are polarized to produce the unregulated +12 volt supply (approximately +20 VDC) across C29. CR10 and CR13 are polarized to produce the unregulated - 12 volt supply (approximately - 20 VDC) across C40.

A single diode (CR11) is used as a half wave rectifier to produce the unregulated + 5 volt supply (approximately + 10 VDC) across C26 and C39. The +5 VUNREG supply powers two of the front panel LEDs and is monitored by the LXP-5 Reset and Battery Backup circuits for power up and power fail conditions.

Voltage regulation is handled by three TO220 packaged ICs:

+12 VDC regulation - U25 (7812) -12 VDC regulation - U26 (7912) +5 VDC regulation - U24 (7805)

Current limiting and short circuit protection are incorporated into the internal circuitry of these ICs.

$A\pm7.5$  VDC supply is created from the  $\pm12$  VDC supply by using 1K resistors in series with 1N755 zener diodes and 22uF capacitors. R59 and CR21 develop the  $\pm7.5$  volt supply across C90, while R58 and CR19 develop the  $\pm7.5$  volt supply across C84.  $\pm7.5$  VDC is required by the CD4053 analog switch (U38) only.

A+4.7 VDC supply is produced from the +5 VDC supply by placing a schottky diode (CR3) in series with R6 and C5. A charge is stored across C5 which provides the +4.7 volt supply for an extended time during power down due to the polarization of CR3. This supply is used by a 74HCT14 (U1) to insure proper operation of the LXP-5 Reset and Battery Backup circuitry when power failure occurs.

# **Reset Circuitry**

The reset circuitry insures proper operation of the LXP-5 during power up and power fail conditions. This circuitry monitors the +5VUNREG supply and provides ZRST, ZRST/, MRST/ and RCE command signals.

The +5VUNREG supply is filtered by FB3 and C17 to prevent noise spikes on the AC line from tripping the reset function. R17 and R18 create a voltage divider which feeds C11 and the base of transistor Q3. C11 provides low frequency filtering for the base voltage. Q3 has a common emitter configuration with a pull-up resistor (R11) to +5 VDC on its collector. The collector voltage is applied to the input of a Schmitt inverter (U1, pin 3) whose output provides feedback to the base of Q3 through R12. During power up Q3 is off until the +5VUNREG supply exceeds the level necessary to bring the transistor into its active state. At this time, the collector voltage starts to drop, which causes the inverter output to go high and turns Q3 on. During a power fail or low power sequence, the +5VUNREG supply starts to drop, bringing Q3 out of saturation and into its active state. The collector voltage starts to increase which causes the inverter output to go low and turns the transistor off.

With the supplied 120 VAC power pack, an AC line voltage above 100 volts will turn Q3 on and insure the proper power up sequence for the LXP-5 circuitry. If the AC line voltage drops below 100 volts, Q3 turns off, enabling the required reset signals.

The collector of Q3 provides the ZRST command signal. ZRST is applied to the UART's Reset pin (U3, pin 21) and the Battery Backup circuitry, which require an active high signal for reset to occur.

The inverter output (U1, pin 4) provides the ZRST/ command signal. ZRST/ is applied to the Lexichip's Reset pin (U21 pin 74) which requires an active low signal for reset to occur. The ZRST/ command is also used to clear a latch (U5) and the MIDI timer (U13).

ZRST is also applied to another inverter input (U1,pin 13) through a delay circuit made up of CR5, C10 and R5. The output of this inverter provides the MRST/ command signal. MRST/ is used to reset the Master Z80 Processor (U4, pin 26) which requires an active low signal. The Master Z80 Processor is the last device enabled by the LXP-5 Reset circuitry, due to the delay circuit associated with MRST/. This insures that all other devices are in a known active state when the Master Z80 (U4) is enabled.

MRST/ is also used to provide RCE, which is the SRAM Chip Enable. RCE is controlled by Q1. The collector of Q1 is connected to the chip enable pins of the SRAMs (U17 & U20, pin26), and provides the RCE command signal. MRST/ is applied to the emitter of Q1 through R4. The base of the transistor is biased by CR2 and R3. Upon power up, MRST/ will go high after a delay, causing RCE to go high and enabling the SRAMs. The delay provided by MRST/ allows the SRAM VCC to stabilize before they are enabled. MRST/ and RCE immediately go low upon power fail, before +5 VDC goes out of regulation and the SRAM VCC drops to +3 volts.

The 74HCT14 hex inverter (U1) is an important component in the LXP-5 Reset circuitry. Therefore, its power supply is independent from the +5 VDC supply. CR3, R6 and C5 provide a separate 4.7VDC supply to insure proper operation of U1 for a brief time during a power fail condition.

Battery Backup is required in the LXP-5 to maintain the non-volatile function of the processors' associated SRAMs. A 3 volt lithium battery (BAT1) maintains the minimum power requirement of the SRAM IC's, U17 and U20, while power is disconnected from the unit.

ZRST is used for controlling the Battery Backup circuitry, and drives the base of Q4 through R16. During power up, ZRST goes low which turns Q4 off. In turn, Q5 becomes active in its emitter follower configuration. The base of Q5 is biased by R20 and CR4, causing its emitter to ramp to +5 volts as C42 charges. This voltage is applied to the VCC pins of the SRAMs (U17 & U20, pin 28). CR16 is reverse biased, preventing the +5 volts from reaching BAT1.

Upon a power fail condition, ZRST goes high which turns Q4 on and Q5 off. C42 discharges until CR16 becomes forward biased, which provides +3 volts from the lithium battery for the SRAM VCC.

The Battery Backup circuitry, along with the RCE signal command, prevents stored data from being destroyed during power failure.

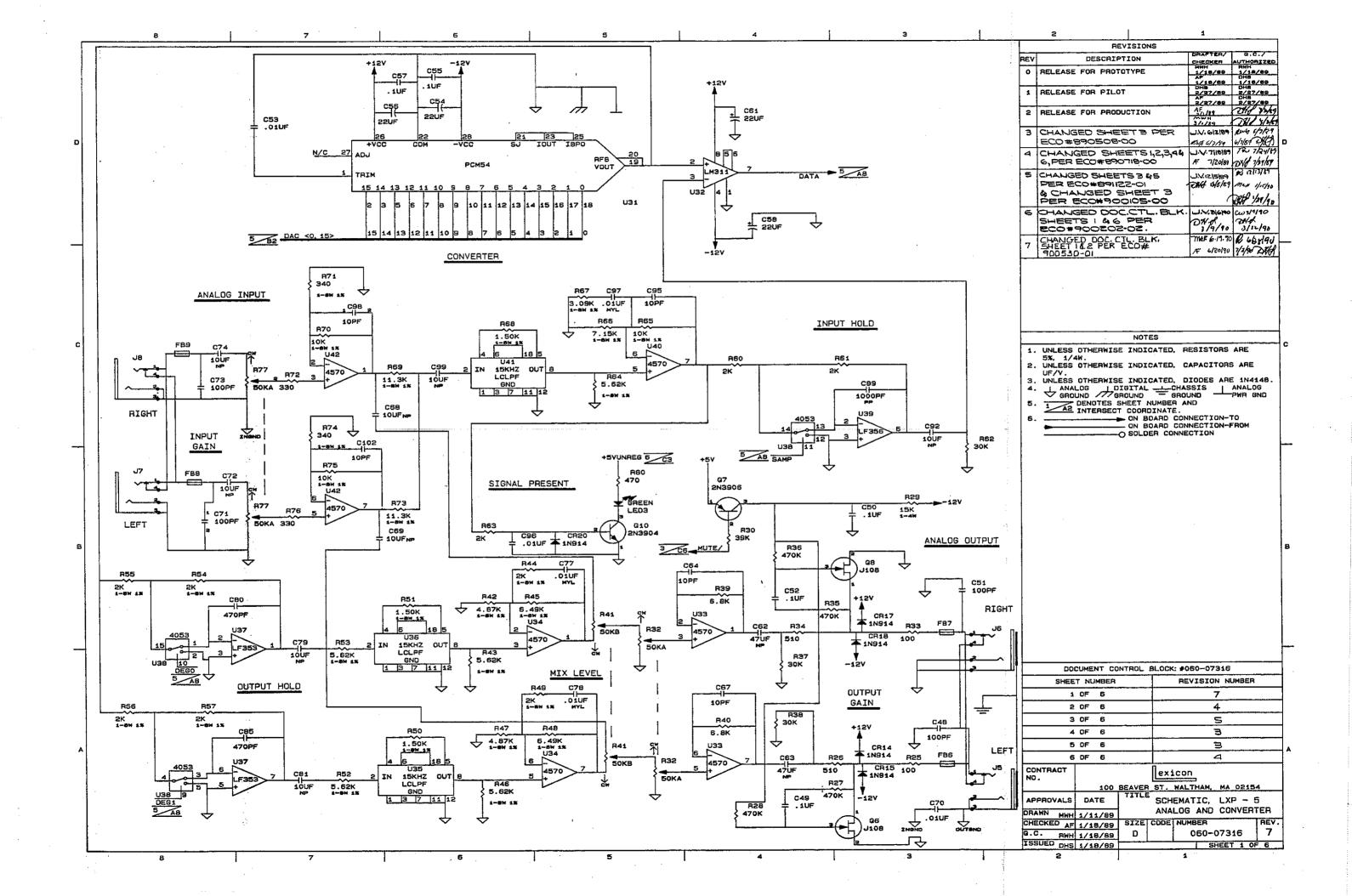

**Analog Circuitry**

**Battery Backup**

Input Stage

Separate unbalanced 1/4" phone jacks (J7 and J8) are provided for left and right input signals. A single input source will be routed to both left and right input stages by applying the signal to either input jack, thereby maintaining the proper operating level.

Ferrite beads (FB8 and FB9) and capacitors (C71 and C73) are found at the inputs to prevent unwanted high frequency interference from entering or leaving the LXP-5 through the input cables. DC isolation is incorporated by bipolar capacitors (C72 and C74) in line with the signal path. The left and right signals feed a dual potentiometer (R77) which controls the input signal level to the preamplifier stage. A dual op amp (U42) acts as the preamp by providing 30 dB of gain. This enables the LXP-5 to perform satisfactorily for nominal input levels as low as -27 dBV.

The left and right outputs of the preamp are applied to the stereo Mix control (R41) through AC coupling capacitors (C68 and C69). The preamp output signals also terminate at resistors R69 and R73 which sum the left and right signals. This summed signal is applied to a passive 7 pole 15 kHz low pass filter (U41) through an AC coupling capacitor (C99). A pre-emphasis function is performed by an op amp (U40), whose output drives the sample and hold circuit. The pre-emphasis is calibrated at the factory, and offers no provisions for user calibration.

The pre-emphasis amplifier also drives the signal detect circuitry. The signal passes through R63 after which a diode (CR20) removes the negative portion of the audio signal and develops an average DC level across capacitor C96. A sufficient DC voltage level will turn on transistor Q10, which illuminates a green LED (LED3) by conducting +5VUNREG through R80. This LED can be found on the front panel, and will illuminate at an input signal level of -34 dBV or greater, with the input level control set at maximum.

### **Converter Circutry**

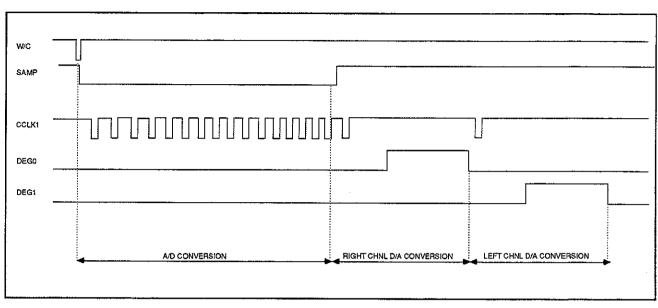

A/D SAR Conversion Timing

#### SAH

The sample and hold (SAH) circuitry consists of op amp U39, an SPDT analog switch U38 and capacitor C89. The SAH is controlled by the SAMP signal command from the Lexichip, which terminates at pin 11 of U38. When SAMP is high, pins 13 and 14 of switch U9 are shorted, which performs the sample function. At this time, an output level from pin 6 of U39 is used to charge C89. The hold function takes place when SAMP goes low, which shorts pins 12 and 14 of switch U38. The charge across C89 keeps the audio signal level constant during the analog to digital conversion. The output of the SAH passes through an AC coupling capacitor (C92) and a pulldown resistor (R62) to prevent DC offsets from affecting system performance.

DAC The analog to digital conversion involves use of a comparator (U32), the Lexichip (U21), and a 16 bit digital to analog converter (DAC, U31). The SAH output is applied to pin 3 of the comparator. The output of the DAC feeds pin 2 of the comparator. During the analog to digital conversion cycle, the internal successive approximation register (SAR) of the Lexichip is used in conjunction with the DAC to output different voltage levels. These voltages are compared with the audio signal level. The conversion is completed when the two voltage levels are equal. After the conversion, the L+R signal is processed digitally.

After the signal has undergone digital processing, separate left and right analog signals reappear after the digital to analog conversion. At this time, the Lexichip sends 16-bit data to the DAC, which converts it into analog voltage levels (see Data to Voltage chart below). These voltage levels are applied to the output hold circuitry.

| Digital Input Code | Analog Output |  |

|--------------------|---------------|--|

| 0000h              | +2.99991V     |  |

| 7FFFh              | 0.0000V       |  |

| 8000h              | -91.6uV       |  |

| FFFFh              | -3.0000V      |  |

DAC Data to Voltage

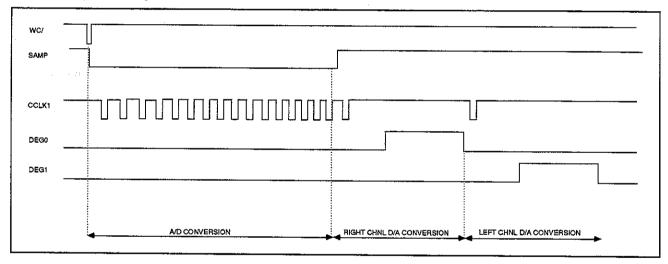

Separate output hold circuits are provided for reconstructing the left and right audio signals. This circuitry includes a dual op amp (U37) and two analog switches (U38). DEG0 and DEG1 command signals from the Lexichip terminate respectively at pins 10 and 9 of U38, providing separate control of the right and left output hold switches. During the digital to analog conversion cycle, either the DEG0 or DEG1 signal goes high when the DAC is ready to output the respective right or left analog voltage. This permits capacitors C80 or C85 to charge to the corresponding voltage level for the audio waveform. When the DEG0 or DEG1 signal goes low, the related capacitor will remain at the current signal level until the next conversion cycle.

**Output Hold**

The left and right signals from the output hold circuitry are applied to separate 7 pole passive 15 kHz filters (U35 and U36). De-emphasis circuitry is incorporated into the signal path to compensate for the pre-emphasis function performed before the conversion process. A dual op amp (U34) with its associated circuitry provides the de-emphasis function.

**Output Circuitry**

The outputs of U34 are applied to one end of the stereo Mix control, R41. The other end of this potentiometer is connected to the outputs of the input preamplifier. By adjusting the wiper of the Mix control, the ratio of wet (processed) to dry (unprocessed) signal can be controlled.

Mix and Output Level Controls

The wipers of R41 are connected to one end of the Output level control, R32. R32 adjusts the signal level being applied to the output amplifier, U33. This dual op amp provides unity gain and buffers the left and right signals separately. An impedance of 600 ohms is developed by resistors R33, R34 for the right output, and R25, R26 for the left output. These resistors also provide current limiting protection. Bipolar AC coupling capacitors (C62 and C63) and pulldown resistors (R37 and R38) are installed to prevent DC offset voltages from appearing at the outputs of the LXP-5.

Output Buffer and Mute Circuitry

Two discrete JFETs, Q6 and Q8, provide a muting function by creating a low impedance path to ground along the output signal path. In this case, R26 and R34 serve as current limiting resistors by preventing the outputs of op amp U33 from shorting directly to ground. The mute function is under software control. The Mute/ command signal emanates from U5 pin 2, and is applied to the base of transistor Q7 through R30. When Mute/ is low, Q7 is on, which provides a positive DC voltage to the gates of Q6 and Q8. The JFETs turn on and enable mute. When Mute/ is high, Q7 turns off which allows a negative voltage to be applied to the JFETs. Q6 and Q8 turn off and disable mute. C50 insures a quiet transition between mute and unmute by ramping the gate voltages. Mute is enabled during power up or power down conditions, and some program change sequences.

The output jacks (J5 and J6) are located next to the input jacks on the rear panel. The 1/4" unbalanced phone jacks are configured in such a way that the left and right output signals are summed together if only one plug is connected. However, both output jacks should be utilized for the full stereo effect to be attained.

Static protection is provided for the output circuitry by diodes CR14, CR15, CR17 and CR18. Ferrite beads FB6 and FB7 and capacitors C48 and C51 prevent unwanted high frequency interference from entering or leaving the LXP-5 through the output cables.

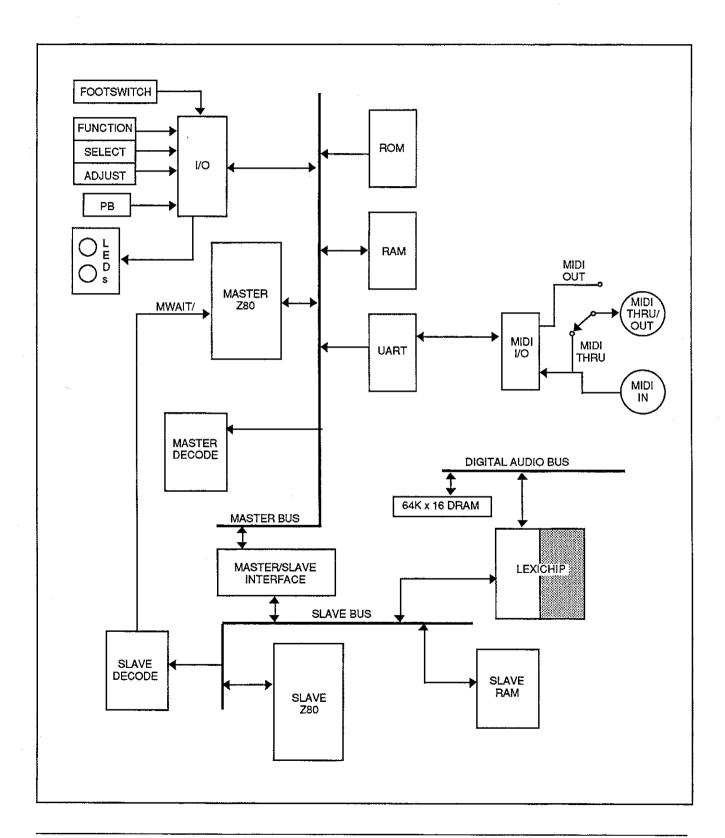

# **Digital Circuitry**

The LXP-5 utilizes two Z80 microprocessors and the Lexchip digital signal processor to perform multiple digital audio effects which are controlled via three front-panel selections, as well as a serial MIDI interface. Each processor has its own support circuitry, data and address buses. Communication between processors is performed via two interfaces. The Master/Slave Interface allows Master Z80 access to the Slave bus where read/write operations can be performed on Slave RAM and Lexichip. The Lexichip Writeable Control Store (WCS) contains program memory and registers. It can be accessed via its on-chip Z80 interface which connects directly to the Slave Bus.

Overview

During normal operation, sampled audio is converted into digital data by the converter circuitry. Digital effects processing is performed by the Lexichip under the control of both Master and Slave Z80 processors. The Master Z80, which handles all operator I/O and housekeeping functions, is able to pass on DSP control information to the other two processors. The Slave Z80 is dedicated to the task of controlling the Lexichip and is, therefore, used to perform any DSP control functions which require precise timing, such as pitch shifting.

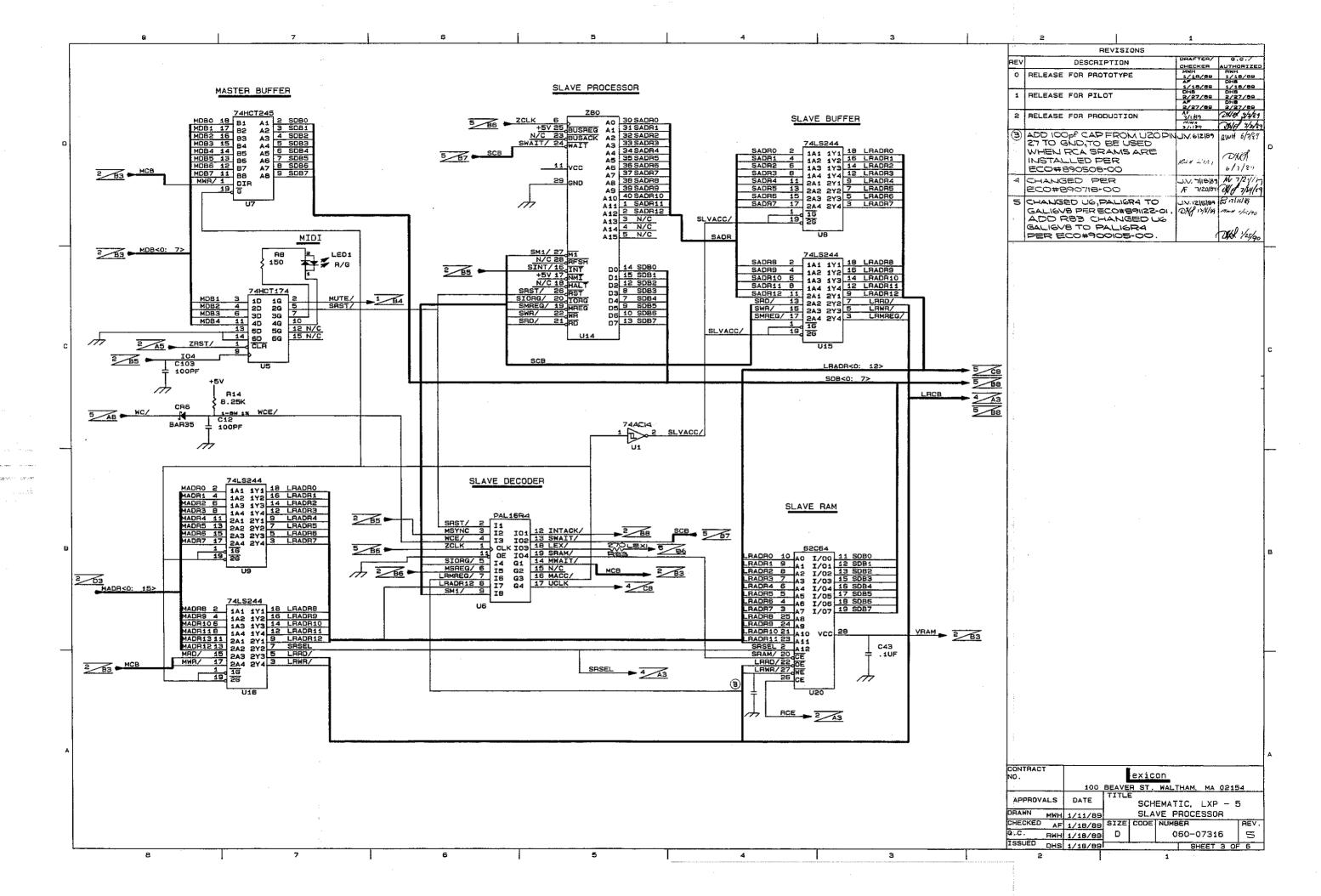

The LXP-5 utilizes two 4 MHz Z80 microprocessors (U4 and 14) in a master/slave configuration. Tasks are shared between these two processors as described below:

Z80 Microprocessor Circuitry

The Master Z80 (U4) handles basic housekeeping and user interface I/O operations. It has the ability to write program code and data directly into the Slave Z80 Program RAM and Lexichip Writeable Control Store (WCS) by directly accessing the Slave Z80 bus via the Master / Slave Interface. Its specific tasks are:

**Master Processor Functions**

- Processing data and instructions to and from the UART

- Processing data and instructions to and from the Lexichip

- Handling user-data input and LED operations

- · Maintenence of non-volatile, user-controlled registers.

- · Loading and manipulation of Slave processor program code and data

- · Controlling Slave processor reset and interrupt functions

- · Controlling audio muting hardware

#### Slave Processor Functions

The Slave Z80 (U14) is strictly dedicated to controlling Lexichip operations. This task is performed by accessing the Lexichip Writeable Control Store, the on-chip memory and register storage which is connected to the Slave Z80 bus via a Read/Write port .

## Memory

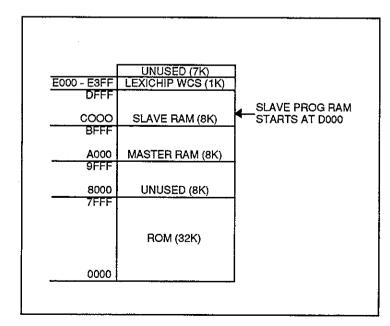

32K bytes of ROM space is contained in a single 27C256 PROM (U10). This ROM is mapped into the Master processor memory space. It contains Slave Z80 and Lexichip program routines which are loaded by the Master Z80 via the Master/slave interface. Diagnostics, I/O, and housekeeping subroutines executed by the Master Processor are also contained in this ROM space.

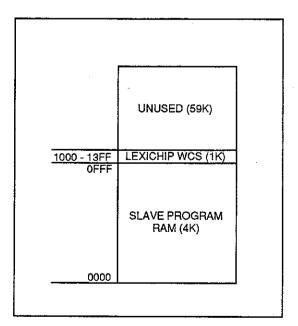

Two CMOS 4364C SRAM ICs (U17, U20) provide a total of 16K of RAM space for both Z80 processors. This RAM is kept non-volatile by the Battery Backup circuitry explained in the power supply section of this chapter. All 16K bytes of RAM are mapped into the Master Z80 memory space. Because U20 is connected to the Slave bus, the Master Z80 must access this upper 8K of RAM via the Master/Slave interface explained below. Only the upper 4K of RAM contained in U20 is mapped into the Slave Z80's memory space to function as both program and data memory for that processor. Slave Z80 code is loaded into memory by the Master Z80. The lower 4K of space contained in U20 serves as user-register storage. This is managed by the Master processor and cannot be accessed by the Slave Z80.

The Lexichip (U21) contains its own on-chip program RAM and I/O registers which are addressable by both Z80 processors via the Slave Bus. This 1K byte of memory is mapped into the 64K of addressable memory space of both Master and Slave processors.

Master Processor Memory Map

Slave Processor Memory Map

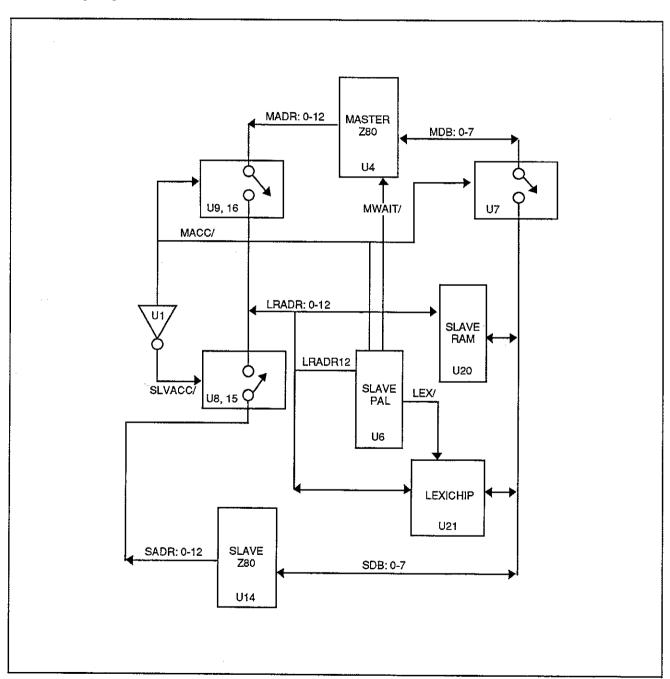

A memory refresh period is produced by a Z80 processor for two clock cycles during every instruction fetch. Since the static RAM used by the Master and Slave Z80s does not require refreshing, the master processor utilizes the Slave Z80's available refresh period to gain access to the Slave processor bus in a manner that is completely transparent to Slave operations. Syncronization of timing for Master Z80 access to the Slave Bus is performed by the Slave Decoding PAL (U6).

### Master/Slave Interface

The following diagram illustrates the actual hardware interface.

Master /Slave Interface Diagram

## Master Decoding

U11, a PAL16L8 decodes address bus signals of the Master Z80 into memory and I/O device signaling. Two AND gates (U18) ,an inverter (U1) and a 74HCT174 D latch (U5) are also utilized in this function. The chart below shows the PAL decoding scheme for Memory and I/O operations. A description of each output signal provided by the Master Z80 decoding circuitry is also provided at the end of this section.

## Master Decoding Chart -

|   | MASTEF                                  | IASTER PAL DECODING CHART: (MMREQ/ = L) |    |    | МЕМ                       | ORY                                  |     |     |

|---|-----------------------------------------|-----------------------------------------|----|----|---------------------------|--------------------------------------|-----|-----|

|   | MADR:                                   | 15                                      | 14 | 13 | HEX ADDRESS               | Active Sel Line                      | H,  |     |

|   |                                         | 0 0                                     | 0  | 0  | 000h<br>through<br>7FFFh  | ROM/                                 | L   |     |

|   |                                         | 1                                       | 0  | 1  | A000h<br>through<br>BFFFh | RAM/                                 | L   |     |

|   |                                         | 1                                       | 1  | 0  | C000h<br>through<br>DFFFh | MSREQ/<br>SLAVE PAL DECODE:<br>SRAM/ |     | -   |

|   |                                         | 1                                       | 1  | 1  | E000h<br>through<br>E3FFh | MSREQ/<br>SLAVE PAL DECODE:<br>LEX/  | l   | -   |

|   | MASTER PAL DECODING CHART: (MIORQ/ = L) |                                         |    |    | )RQ/ = L)                 | 1/0                                  |     |     |

| Γ | MADR:                                   | 7                                       | 6  | 5  | HEX ADDRESS               | Active Sel Line                      | R/W | H/L |

|   |                                         | 0                                       | 0  | 0  | 00h                       | 101/                                 | R   | L   |

|   |                                         | 0                                       | 0  | 1  | 20h                       | 102/                                 | R   | L   |

|   |                                         | 0                                       | 1  | 0  | 40h                       | 103                                  | R   | Н   |

|   |                                         | 0                                       | 1  | 1  | 60h                       | IO4                                  | W   | Н   |

|   |                                         | •                                       |    |    | MDB<br>7 6 5 4 3 2 1 0    |                                      |     |     |

| 1 |                                         |                                         |    |    | XXXXXXXX                  | MSYNC/                               | Χ   | L   |

| 1 |                                         |                                         |    |    | X X X X X X X 0 X         | MUTE/                                | Х   | L   |

| 1 |                                         |                                         |    |    | XXXXXXXXX                 | SRST/                                | Х   | L   |

| 1 |                                         |                                         |    |    | 0 1                       | MIDI LED=GREEN MIDI LED=RED          |     |     |

|   |                                         |                                         |    | [  | 0 0 or or                 | MIDI LED=RED                         |     |     |

|   | •                                       | 1                                       | 0  | 0  | 80h                       | UART/                                | R/W | L   |

The Slave PAL (U6) handles the Mapping of the Slave RAM and Lexichip WCS into both Z80 processors' memory. Address and control signals on the Slave Bus are decoded as shown below.

## Slave Decoding

Master Z80 access to the Slave Bus is also controlled by the Slave PAL. Access is synchronized to occur during the memory refresh period of the Slave Z80 by forcing wait states on the Master Z80. This is also illustrated in the timing diagram in the following section.

#### SLAVE PAL DECODING CHART SLAVE BUS ACCESS AND MASTER Z80 WAIT SIGNALING INPUT SIGNALS **OUTPUT SIGNAL** MSYNC/ MWAIT/ Х MWAIT/ MACC/ Х Х 0 Х 1 Х 0 Х Х Х 0 b 0 Х Х Χ Х Х 0 0 clears condition a or b 0 Х Х 0 clears condition c Χ 0 0 Х 0 or x Х 0 $x \mid x$ SLAVE BUS DECODING MSREO/ LRADR12 LRMREO/ ZCLK SM1/ SRAM/ LEX/ INTACK/ UCLK Х 0 Х 0 0 1 Х 0 Х 0 Х Х 1 0 Х Х Х Х Χ Х Х 1 1 Х Х Х Х Х 0 0 Х Х 0 Х Х Х Χ UCLK

## Slave Decoding Chart

|          | KEY                                         |

|----------|---------------------------------------------|

| х        | DON'T CARE                                  |

| 1        | RISING EDGE                                 |

| <b>†</b> | TWO RISING EDGES<br>(ONE FULL CLOCK PERIOD) |

| 0        | LOGICAL LOW                                 |

| 1        | LOGICAL HIGH                                |

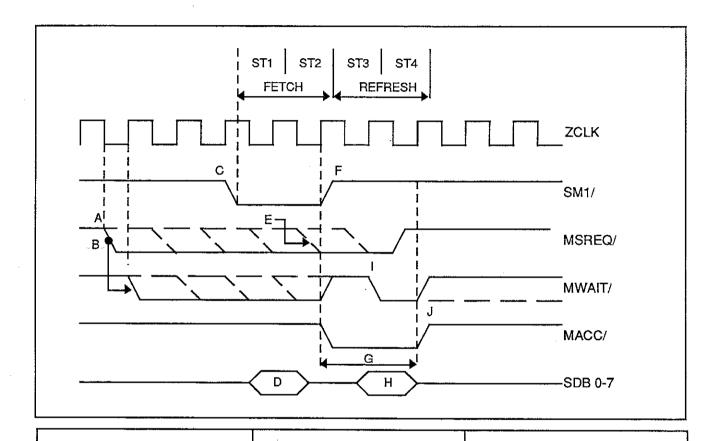

## Slave Instruction Fetch Cycle

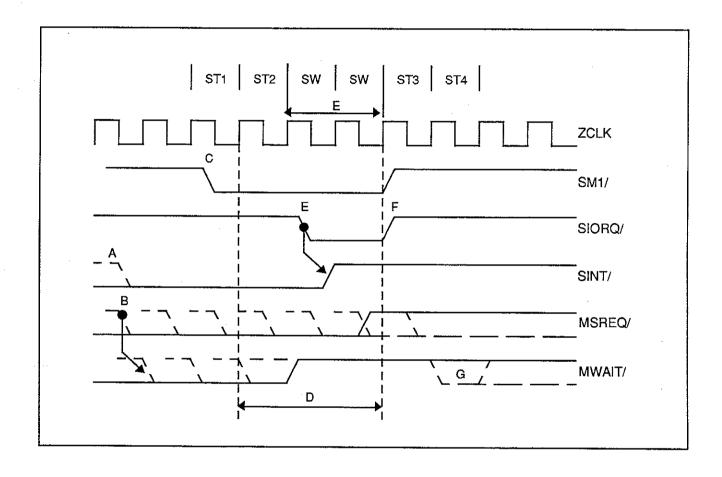

There are three different periods where the Master Z80's request to gain access to the Slave Bus is honored. The first is when Slave Z80 reset (SRST) has been asserted. In this case the Master Z80 gains immediate access with no wait states. The other two periods occur while the Slave Z80 is performing either an instruction fetch or an interrupt acknowledge. Timing for these two conditions are illustrated and explained below.

- A The Master Z80 requests Slave Access by asserting MSREQ/

- B MWAIT/ is asserted to keep the Master Z80 in a wait state until the Refresh window occurs.

- C SM1/ indicates Slave Z80 Instruction Fetch period.

- D Instruction code is read from the 8-bit data bus.

- E If MSREQ/ is asserted during the second T state of Instruction Fetch period (SM1/), the Master Z80 is in sync with the Slave Z80 Refresh period and no wait states will occur.

- F The rising edge of SM1/ indicates the beginning of Slave Z80 Refresh period, which is the Slave Bus access window.

- G The Refresh access window occurs for the last two T states during a Slave Z80 Instruction Fetch cycle. If MSREQ/ has been previously asserted, MACC/ will go low to enable Slave Bus buffers for the Master Z80, allowing it access to Slave RAM or Lexichip WCS.

- H During this Refresh period, the Slave Z80 data lines are placed in a high impedance state. The Master Z80 is then allowed access to the 8-bit data bus for a read or write operation.

- MWAIT/ goes low for the 4th T state of the Slave Instruction Fetch. If the Master Z80 has already gained access to the Slave Bus at this point this MWAIT/ will be ignored. If MSREQ/ is activated just after D, this wait signal will be acknowledged, and the Master processor will insert waits until the next Refresh period.

- J At the end of Slave Refresh Access, MACC/ is returned to a logical high, which removes Master Z80 from the Slave Bus.

## Interrupt Request/Acknowledge Cycle

- A Master Z80 requests an Interrupt from the Slave processor

- B Master Z80 requests Slave Bus Access. Since this request is not syncronous with a Refresh window, MWAIT/ is activated. Master Z80 inserts wait states until the next available window.

- C SM1 goes low as the beginning of an interrupt acknowledge cycle is occurring. In the interrupt mode used by the Slave Z80, its data bus will be in a high impedance state during this entire cycle.

- D SM1/ is low for 4 T states during the Interrupt Acknowledge cycle. Due to this extended SM1, the Master Z80 can request Slave Bus Access (by activating MSREQ/) and gain access without wait states during the last 3 T-states of SM1/.

- E SIORQ/ goes low. This, in conjunction with SM1/ staying low for an additional two wait periods, creates the Interrupt Acknowledge signal.

- F SM1/ and SIORQ/ both go high, indicating Refresh period has begun.

- G If MSREQ/is low during ST4, MWAIT will become active. This wait will be ignored by the Master Z80 if MSREQ/ went low on the last SW clock before Refresh, as the Master has already gained access. If MSREQ/ goes low during ST3, wait states will be inserted by the Master Z80 until the next Refresh window occurs.

## Digital Audio Processor Circuitry

#### LEXICHIP: Z80 Interface

The Lexichip (U21) performs all the digital effects processing calculations for the LXP-5. It receives instructions from its internal program RAM, referred to as the Writeable Control Store (WCS). Address, data, and control lines for the WCS are shared with the Slave Z80 bus. This allows both Slave and Master Z80 processors to load audio effects programs into the Lexichip, monitor status of audio data, and synchronously change program parameter values in audio programs. Both Master and Slave Z80 processors treat the 1K bytes of WCS as mapped memory space.

#### Clocks

An internal crystal oscillator driver circuit drives a 16MHz crystal mounted across pins 75 and 76 on the Lexichip. Internal Lexichip circuitry divides this clock frequency down to provide the 4MHz ZCLK which is used by the Z80 processors.

The PCLK1 (pin 73) output is programmed to divide down the 16MHz clock to the 500kHz MIDICLK signal. This signal is utilized by the UART IC (U3) to set up the serial communications baud rate.

WC/ (pin 59) is used as a clock reference by the LXP-5. It operates at a 31.25 kHz sample rate and is utilized by the UART interrupt timing circuitry, as well as by the Slave decoding circuitry, to sync the Master processor to DSP operations.

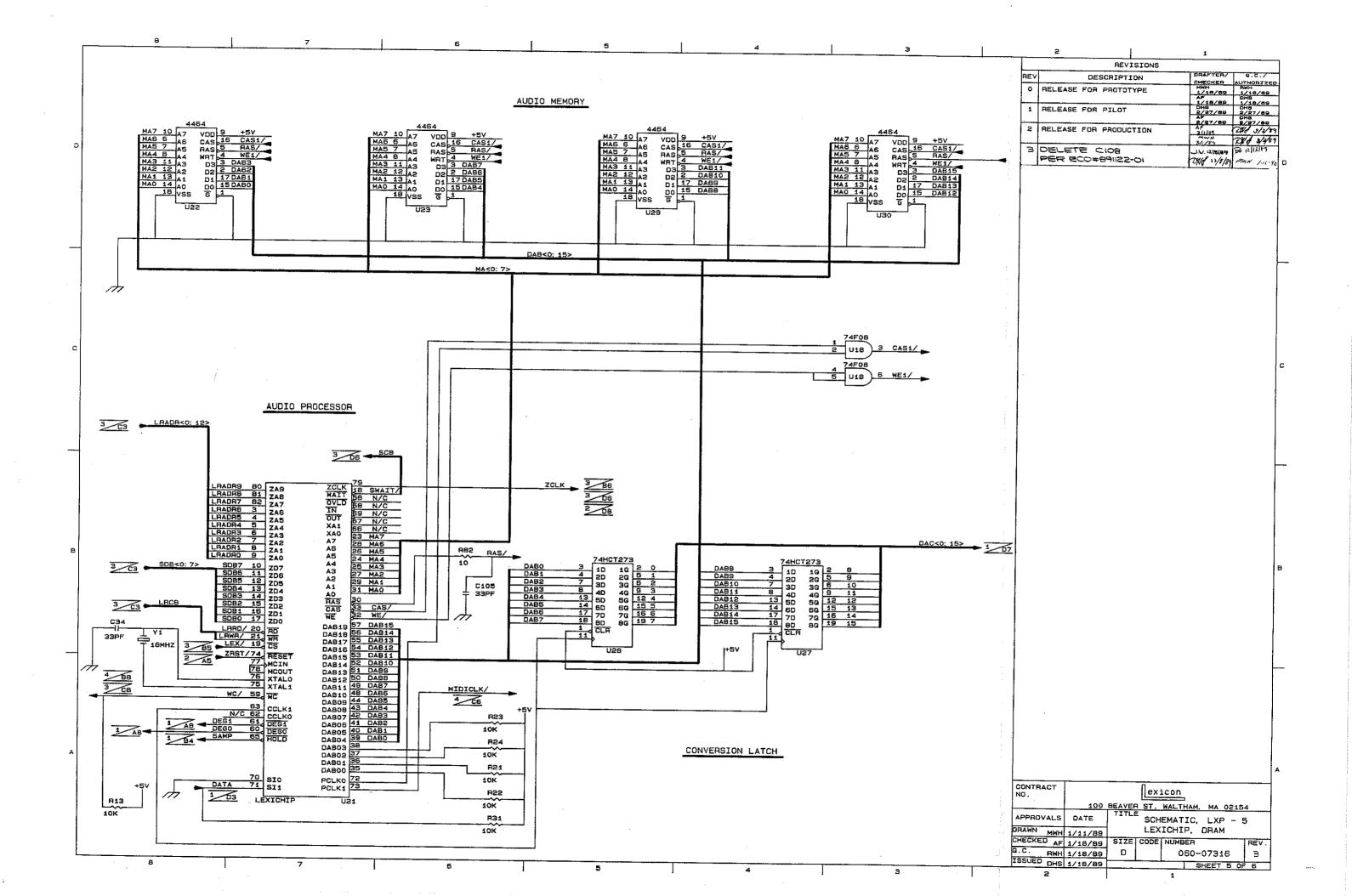

#### **Audio Memory**

Four 64Kx 4-bit dynamic RAM ICs (U22,U23,U29,U30) provide the 64Kx 16-bit RAM space used by the Lexichip for audio data storage. DRAM read, write, and refresh functions are performed by a dedicated set of address and control lines and a 16-bit data bus provided by the Lexichip.

## LEXICHIP: DAC/ADC Control Logic and Data Port

Internal control logic circuitry enables the Lexichip to command complete control over external DAC functionality with minimal external circuitry.

Two 8 bit latches (U27,U28) are used to latch 16 bit data out to the DAC via the DRAM data bus. Lexichip output CCLK1 clocks DAC data into these DAC conversion latches.

An internal Successive Approximation Register (SAR) allows the DAC, in conjunction with an external comparator, to perform analog to digital conversions. A data value is latched into the conversion latch. DAC output is compared to analog input by the comparator. The comparator's resulting output (DATA) is applied to Lexichip input SI1, and the SAR logic circuitry determines either the next DAC output value or an end of conversion. Converted data is then processed by the Lexichip with instructions from its RAM resident digital effects program.

DAC logic signals are provided by the Lexichip to control the Sample and Hold (SAH) and deglitch functions and conversion data latching. A Word Clock signal (WC/) is used as a clock reference and indicates the beginning of a conversion cycle.