# LINEAR APPLICATIONS Volume 2

**National**

# **National**

PREFACE The second volume of National's Linear Applications handbook picks up where Volume I left off. Data sheets, application briefs and pertinent articles published in the 3 years since Volume I was printed are included in this handbook. Volume II retains the same format as Volume I, to facilitate its use.

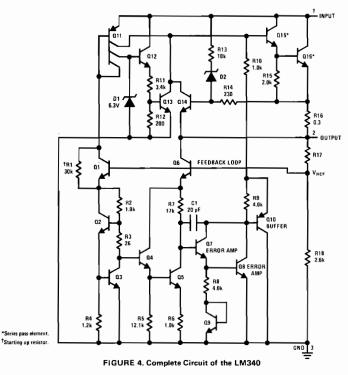

In this volume, as in Volume I, application schematics call out the generic family, which, by coincidence, is the military temperature range version of the device. Generally, any device in the generic family will work in the circuit. For example, an amplifier marked LM108 refers to the generic 108 family, and does not imply that only military-grade devices will work. Military (or industrial) grade devices need only be considered when their tighter electrical limits or wider temperature range warrant their use. As a reminder to our users, our numbering system is:

| Device No. | Grade      | Specified Temperature<br>Range                     |

|------------|------------|----------------------------------------------------|

| LM1XX      | Military   | $-55^{\circ}$ C $\leq$ TA $\leq$ +125 $^{\circ}$ C |

| LM2XX      | Industrial | $-25^{\circ}$ C $\leq$ TA $\leq$ +85 $^{\circ}$ C  |

| LM3XX      | Commercial | $0^{\circ}C \le T_{A} \le +70^{\circ}C$            |

Because commercial parts are less expensive than military or industrial, these points should be kept in mind when trying to determine the most cost-effective approach to a given design.

National Semiconductor Corporation 2900 Semiconductor Drive, Santa Clara, California 95051, (408) 737-5000/TWX (910) 339-9240

Manufactured under one or more of the following U.S. patents: 3083262, 3189758, 3231797, 3303356, 3317671, 3323071, 3381071, 3408542, 3421025, 3426423, 3440498, 3518750, 3519897, 3557431, 3560765, 356218, 3571630, 3575609, 3579059, 3593640, 3607469, 3617859, 3631312, 3630352, 3638131, 3648071, 3651565, 3693248.

National goes not assume any responsibility for use of any circuitry described; no circuit patent licenses are implied; and National reserves the right, at any time without notice, to change said circuitry. 1976 National Semiconductor Corp.

### APPLICATION LITERATURE NUMERICAL LIST

| APPLICATION NOTES DATE                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                          |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

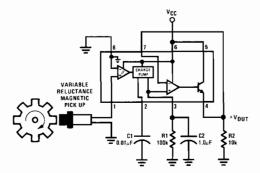

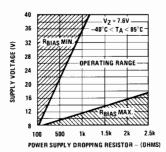

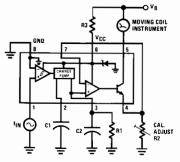

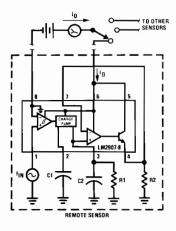

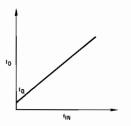

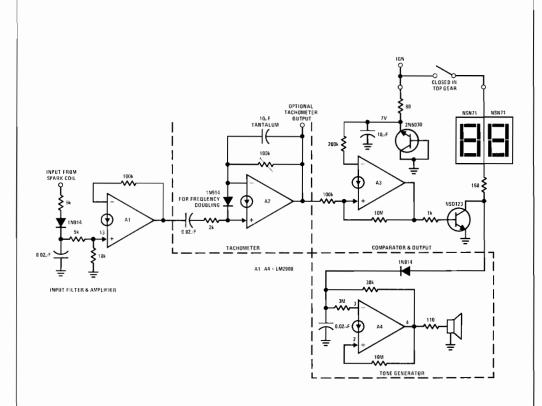

| AN-79<br>AN-81<br>AN-82<br>AN-87<br>AN-88<br>AN-97<br>AN-103<br>AN-104<br>AN-115<br>AN-115<br>AN-127<br>AN-127<br>AN-129<br>AN-132<br>AN-146<br>AN-147<br>AN-151<br>AN-151<br>AN-153<br>AN-154<br>AN-156<br>AN-161<br>AN-162 | IC Pre-Amp Challanges Choppers on Drift LM1800 (LM1310, LM1310E) Phase Locked Loop FM Stereo Demodulator LM125, LM126, LM127 Precision Dual Tracking Regulators Comparing the High Speed Comparators CMOS Linear Applications Versatile Timer Operates from Microseconds to Hours LM340 Series Three Terminal Positive Regulators Noise Specs Confusing? Fast IC Power Transistor with Thermal Protection. Wide Range Function Generator. Use the LM158/LM258/LM358 Dual, Single Supply Op Amp LM377, LM378 and LM379 Dual Two, Four and Six Watt Power Amplifiers LM143 Monolithic High Voltage Operational Amplifier Applications A Linear Multiple Gain-Controlled Amplifier The Monolithic Temperature Transducer—A New Interfacing Concept. FM Remote Speaker System Low Cost IC Stereo Receiver. The Low Noise JFET—The Noise Problem Solver Constant Current LED 1.3V IC Flasher, Oscillator, Trigger or Alarm Specifying A/D and D/A Converters IC Voltage Reference has 1 ppm Per Degree Drift LM2907 Tachometer/Speed Switch Building Block Applications | 6/73<br>5/74<br>6/73<br>7/73<br>12/73<br>3/74<br>5/74<br>5/74<br>5/74<br>1/75<br>4/76<br>8/75<br>12/74<br>6/75<br>1/76<br>10/75<br>12/75<br>2/76<br>6/76 |  |  |

| LB-21<br>LB-22<br>LB-23<br>LB-24<br>LB-25<br>LB-26<br>LB-27<br>LB-28<br>LB-29<br>LB-30<br>LB-31<br>LB-32<br>LB-33<br>LB-34                                                                                                   | Instrumentational Amplifiers Low Drift Amplifiers Precise Tri-Wave Generation Versatile IC Pre-Amp Makes Thermocouple Amplifier with Cold Junction Compensation True RMS Detector Specifying Selected Op Amps and Comparators. Micropower Thermometer. General Purpose Power Supply Low Cost AM Radio System using LM1820 and LM386 Low Cost LED Thermometer. Crystal Oven Controller and Precision Voltage Reference Microvolt Comparator High Speed Warning Device for Automobiles A Micropower Voltage Reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6/73<br>6/73<br>6/73<br>6/73<br>10/73<br>1/74<br>6/74<br>2/75<br>7/75<br>6/76<br>6/76                                                                    |  |  |

| APPENDICES                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                          |  |  |

| A<br>B<br>C                                                                                                                                                                                                                  | The Monolithic Operational Amplifier: A Tutorial Study A Color TV Primer for the E.E. Subject Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                          |  |  |

## DEVICE/APPLICATION LITERATURE CROSS-REFERENCE

| DEVICE                 | APPLICATION                  | DEVICE  | APPLICATION          |

|------------------------|------------------------------|---------|----------------------|

| NUMBER                 | LITERATURE                   | NUMBER  | LITERATURE           |

|                        |                              |         |                      |

| LH0033                 | AN-115                       | LM377   | AN-125               |

| LM101                  | AN-132, LB-28                | LM378   | AN-125, AN-147       |

| LM104                  | AN-110                       | LM379   | AN-125               |

| LM105                  | AN-110                       | LM380   | AN-146               |

| LM108 .AN-79, AN-88, A | N-110, AN-161, LB-24, LB-28  | LM382   | AN-147               |

| LM111                  | AN-103, LB-32                | LM386   | LB-29                |

| LM113                  | LB-21, LB-23, LB-28          | LM555   | LB-30                |

| LM114                  | LB-21, LB-25                 | LM565   | AN-146               |

| LM216                  | AN-132                       | LM566   | AN-146               |

| LM118 AN-110, A        | N-115, AN-129, LB-21, LB-23  | LM1310  | AN-81                |

| LM119                  | AN-115, LB-23                | LM1558  | AN-103, AN-116       |

| LM120                  | AN-103, AN-115, Appendix III | LM1800  | AN-81, AN-147        |

| LM121                  | AN-79, LB-24, LB-32          | LM1820  | AN-147, LB-29        |

| LM122                  | AN-97                        | LM1900  | LB-33                |

| LM124                  | AN-88, AN-129                | LM2907  | AN-162               |

| LM125                  | AN-82                        | LM2917  | AN-162               |

| LM126                  | AN-82                        | LM3089  | AN-147               |

| LM127                  | AN-82                        | LM3909  | AN-154               |

| LM140                  | AN-103, AN-115               | LM3911  | AN-132, LB-30        |

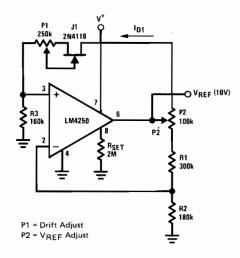

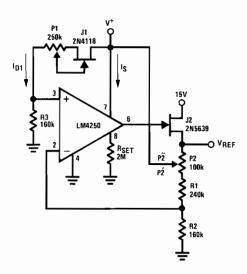

| LM143                  | AN-103, AN-127               | LM4250  | AN-88, LB-34         |

| LM158                  | AN-116                       | LM78LXX | AN-146               |

| LM160                  | AN-87                        | LX5600  | AN-132, LB-27, LB-30 |

| LM161                  | AN-87                        | LX5700  | AN-132, LB-27, LB-30 |

| LM195 AN-110, AN       | I-129, AN-153, AN-161, LB-28 | NSL4944 | AN-153               |

| LM199                  | AN-161, LB-31                | MM74C04 | AN-88                |

|                        |                              |         |                      |

# National Semiconductor APPLICATION NOTES

#### IC PREAMP CHALLENGES CHOPPERS ON DRIFT

Since the introduction of monolithic IC amplifiers there has been a continual improvement in DC accuracy. Bias currents have been decreased by 5 orders of magnitude over the past 5 years. Low offset voltage drift is also necessary in a high accuracy circuits. This is evidenced by the popularity of low drift amplifier types as well as the requests for selected low-drift op amps. However, until now the chopper stabilized amplifier offered the lowest drift. A new monolithic IC preamplifier designed for use with general purpose op amps improves DC accuracy to where the drift is lower than many chopper stabilized amplifiers.

#### INTRODUCTION

Chopper amplifiers have long been known to offer the lowest possible DC drift. They are not without problems, however. Most chopper amps can be used only as inverting amplifiers, limiting their applications. Chopping can introduce noise and spikes into the signal. Mechanical choppers need replacement as well as being shock sensitive. Further, chopper amplifiers are designed to operate over a limited power supply, limited temperature range.

Previous low-drift op amps do not provide optimum performance either. Selected devices may only meet their specified voltage drift under restrictive conditions. For example, if a 741 device is selected without offset nulling, the addition of a offset null pot can drastically change the drift. Low drift op amps designed for offset balancing have another problem. The resistor network used in the null circuit is designed to null the drift when the offset voltage is nulled. The mechanism to achieve nulled drift depends on the difference in temperature coefficient between the internal resistors and the external null pot. Since the internal resistors have a non-linear temperature coefficient and may vary device to device as well as between manufacturers, it can only approximately null offset drift. The problem gets worse if the external null pot has a TC other than zero.

A new IC preamplifier is now available which can give drifts as low as  $0.2\mu V/^{\circ}C$ . It is used with conventional op amps and eliminates the problems associated with older devices. As well as improving the DC input characteristics of the op amp, loopgain is increased when an LM121 is used. This further improves overall accuracy since DC gain error is decreased.

The LM121 preamp is designed to give zero drift when the offset voltage is nulled to zero. The operating current of the LM121 is programmable

by the value of the null network resistors. The drift is independent of the value of the nulling network so it can be used over a wide range of operating currents while retaining low drift. The operating current can be chosen to optimize bias current, gain, speed, or noise while still retaining the low drift. Further, since the drift is independent of the match between external and internal resistors when the offset is nulled, lower and more predictable drifts can be expected in actual use. The input is fully differential, overcoming many of the problems with single ended chopper-amps. The device also has enough common mode rejection ratio to allow the low drift to be fully utilized.

#### CIRCUIT DESCRIPTION

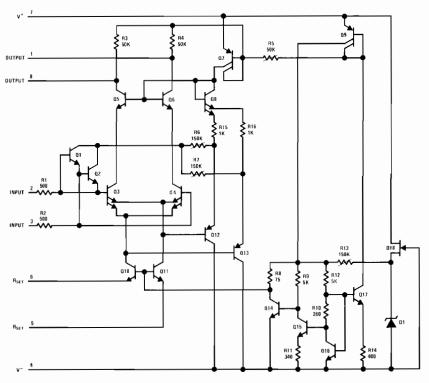

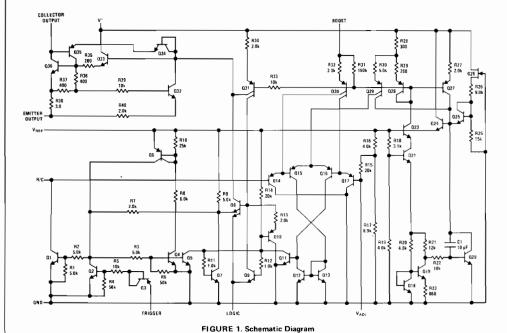

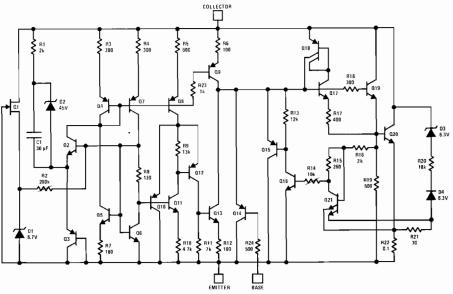

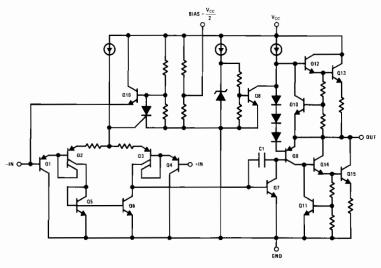

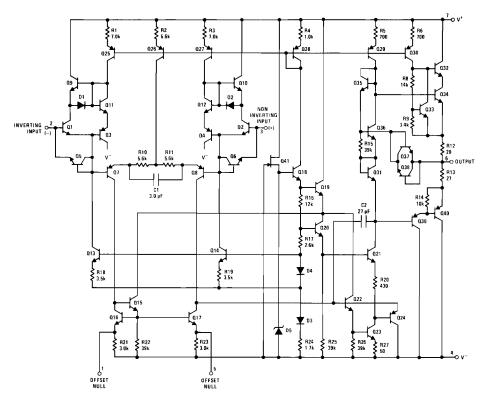

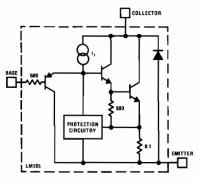

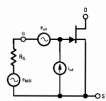

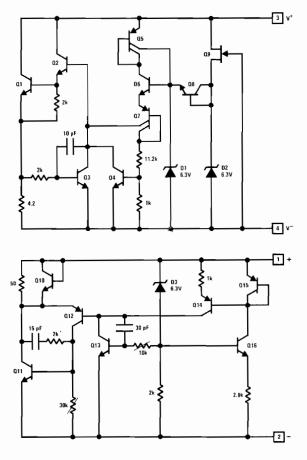

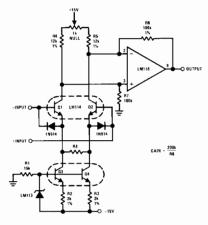

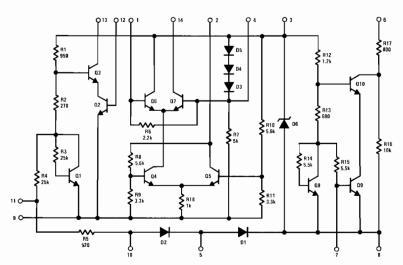

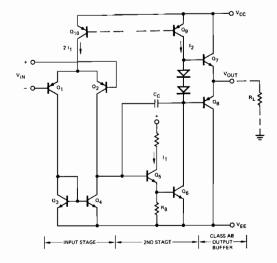

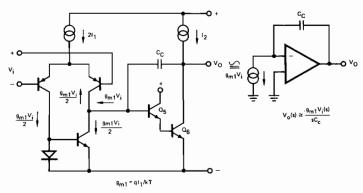

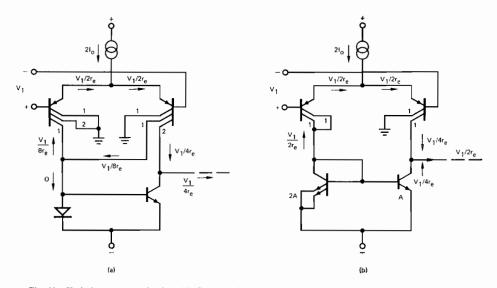

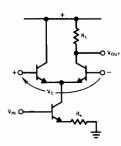

The LM121 is a well matched differential amplifier utilizing super-gain transistors as the input devices. A schematic is shown in Figure 1. The input signal is applied to the bases of  $Q_3$  and  $Q_4$ through protection resistors R1 and R2. Q3 and Q4 have two emitters to allow offset balancing which will be explained later. The operating current for the differential amplifier is supplied by current sources  $Q_{10}$  and  $Q_{11}$ . The operating current is externally programmed by resistors connected from the emitters of  $Q_{10}$  and  $Q_{11}$  to the negative supply. Input transistors  $Q_3$  and  $Q_4$  are cascoded by transistors  $Q_5$  and  $Q_6$  to keep the collector base voltage on the input stage equal to zero. This eliminates leakage at high operating temperatures and keeps the common mode input voltage from appearing across the low breakdown super-gain input transistors. Additionally, the cascode improves the common mode rejection of the differential amplifier. Q1 and Q2 protect the input against large differential voltages.

The output signal is developed across resistive loads R3 and R4. The total collector current of the input is then applied to the base of a fixed gain PNP,  $Q_7$ . The collector current of  $Q_7$  sets the operating current of  $Q_8$ ,  $Q_{12}$ , and  $Q_{13}$ . These transistors are used to set the operating voltage of the cascode,  $Q_5$  and  $Q_6$ . By operating the cascode biasing transistors at the same operating current as the input stage, it is possible to keep collector base voltage at zero; and therefore, collector-base leakage remains low over a wide current range. Further, this minimizes the effects of V<sub>BE</sub> variations and finite transistor current gain. At high operating currents the collector base voltage of the input stage is increased by about 100 mV due to the drop across R<sub>15</sub> and R<sub>16</sub>. This prevents the input transistors from saturating under worst case conditions of high current and high operating temperature.

\*PIN CONNECTIONS SHOWN ON DIAGRAM AND TYPICAL APPLICATIONS ARE FOR TO-5 PACKAGE.

FIGURE 1. Schematic Diagram of the LM121

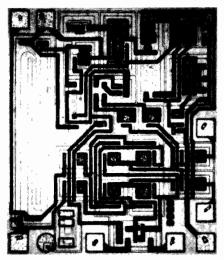

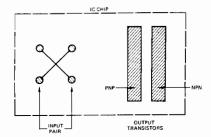

The rest of the devices comprise the turn-on and regulator circuitry. Transistors  $\Omega_{14},\ Q_{15},\ {\rm and}\ Q_{16}$  form a 1.2V regulator for the bases of the input stage current source. By fixing the bases of the current sources at 1.2V, their output current changes proportional to absolute temperature. This compensates for the temperature sensitivity of the input stage transconductance. Temperature compensating the transconductance makes the preamp more useful in some applications such as an instrumentation amplifier and minimizes bandwidth variations with temperature. The regulator is started by  $Q_{18}$  and its operating current is supplied by  $Q_{17}$  and  $Q_{9}$ , Figure 2 shows the LM121 chip.

#### Offset Balancing

The LM121 was designed to operate with an offset balancing network connected to the current source transistors. The method of balancing the offset also minimizes the drift of the preamp. Unlike earlier devices such as the LM725, the LM121 depends only upon the highly predictable emitter base voltages of transistors to achieve low drift. Devices like the LM725 depend on the match between internal resistor temperature coefficient and the external null pot as well as the input stage transistors characteristics for drift compensation.

The input stage of the LM121 is actually two differential amplifiers connected in parallel, each having a fixed offset. The offset is due to different

FIGURE 2. LM121 Chip

areas for the transistor emitters. The offset for each pair is given by:

$$\Delta V_{BE} = \frac{kT}{q} \ln \frac{A_1}{A_2}$$

where k is Boltzmann's constant T is absolute temperature, q is the charge on an electron, and  $A_1$  and  $A_2$  are emitter areas. Because of the offset, each pair has a fixed drift. When the pairs are connected in parallel, if they match, the offsets and drift cancel. However, since matching is not perfect, the emitters of the pairs are not connected in parallel, but connected to independent current sources to allow offset balancing. The offset and drift effect of each pair is proportional to its operating current, so varying the ratio of the current from current sources will vary both the offset and drift. When the offset is nulled to zero, the drift is nulled to below  $1\mu V/^{\circ}C$ .

The offset balancing method used in the LM121 has several advantages over conventional balancing schemes. Firstly, as mentioned earlier, it theoretically zeros the drift and offset simultaneously. Secondly, since the maximum balancing range is fixed by transistor areas, the effect of null network variations on offset voltage is minimized. Resistor shifts of one percent only cause a  $30\mu V$  shift in offset voltage on the LM121, while a one percent shift in collector resistors on a standard diff amp causes a  $300\mu V$  offset change. Finally, it allows the value of the null network to set the operating current.

#### Achieving Low Drift

A very low drift amplifier poses some uncommon application and testing problems. Many sources of error can cause the apparent circuit drift to be much higher than would be predicted. In many cases, the low drift of the op amp is completely swamped by external effects while the amplifier is blamed for the high drift.

Thermocouple effects caused by temperature gradient across dissimilar metals are perhaps the worst offenders. Whenever dissimilar metals are joined, a thermocouple results. The voltage generated by the thermocouple is proportional to the temperature difference between the junction and the measurement end of the metal. This voltage can range between essentially zero and hundred of microvolts per degree, depending on the metals used. In any system using integrated circuits a minimum of three metals are found: copper, solder, and kovar (lead material of the IC).

Nominally, most parts of a circuit are at the same temperature. However, a small temperature gradient can exist across even a few inches — and this is a big problem with low level signals. Only a few degrees gradient can cause hundreds of microvolts of error. The two places this shows up,

generally are the package-to printed circuit board interface and temperature gradients across resistors. Keeping package leads short and the two input leads close together help greatly.

For example, a very low drift amplifier was constructed and the output monitored over a 1 minute period. During the 1 minute it appeared to have input referred offset variations of  $\pm 5\mu V$ . Shielding the circuit from air currents reduced this to  $\pm 0.5\mu V$ . The  $10\mu V$  error was due to thermal gradients across the circuit from air currents.

Resistor choice as well as physical placement is important for minimizing thermocouple effects. Carbon, oxide film and some metal film resistors can cause large thermocouple errors. Wirewound resistors of evenohm or managanin are best since they only generate about  $2\mu V/^{\circ} C$  referenced to copper. Of course, keeping the resistor ends at the same temperature is important. Generally, shielding a low drift stage electrically and thermally will yield good results.

Resistors can cause other errors besides gradient generated voltages. If the gain setting resistors do not track with temperature a gain error will result. For example a gain of 1000 amplifier with a constant 10 mV input will have a 10V output. If the resistors mistrack by 0.5% over the operating temperature range, the error at the output is 50 mV. Referred to input, this is a  $50\mu V$  error. Most precision resistors use different material for different ranges of resistor values. It is not unexpected that resistors differing by a factor of 1000, do not track perfectly with temperature. For best results insure that the gain fixing resistors are of the same material or have tracking temperature coefficients.

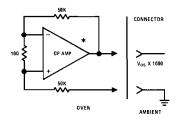

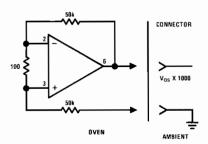

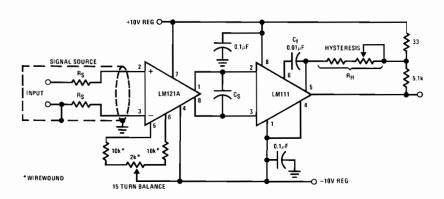

Testing low drift amplifiers is also difficult. Standard drift testing techniques such as heating the device in an oven and having the leads available through a connector, thermoprobe, or the soldering iron method — do not work. Thermal gradients cause much greater errors than the amplifier drift. Coupling microvolt signals through connectors is especially bad since the temperature difference across the connector can be 50°C or more. The device under test along with the gain setting resistor should be isothermal. The circuit in Figure 3 will yield good results if well constructed.

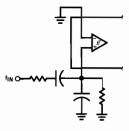

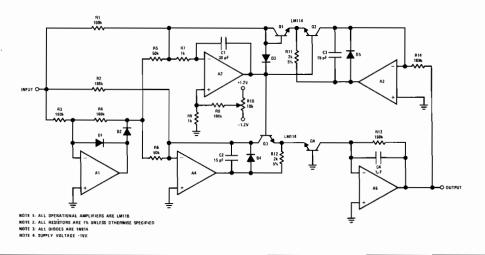

\*OP AMP SHOWN IN FIGURE 9.

FIGURE 3. Drift Measurement Circuit

#### Performance

It is somewhat difficult to specify the performance of the LM121 since it is programmable over a wide range of operating currents. Changing the operating current varies gain, bias current, and offset current – three critical parameters in a high accuracy system. However, offset voltage and drift are virtually independent of the operating current.

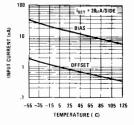

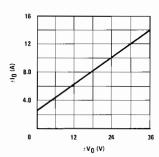

Typical performance at an operating current of  $20\mu A$  is shown in Table I. Figures 4 and 5 show how the bias current, offset current, and gain change as a function of programming current. Drift is guaranteed at  $1\mu V/^{\circ}C$  independent of the operating current.

TABLE I. Typical Performance at an Operating Current of 10µA Per Side

| Offset Voltage                 | Nulled   |

|--------------------------------|----------|

| Bias Current                   | 7 nA     |

| Offset Current                 | 0.5 nA   |

| Offset Voltage Drift           | 0.3μV/°C |

| Common Mode Rejection Ratio    | 125 dB   |

| Supply Voltage Rejection Ratio | 125 dB   |

| Common Mode Range              | ±13V     |

| Gain                           | 20V/V    |

| Supply Current                 | 0.5 mA   |

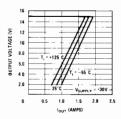

FIGURE 4. Bias and Offset Current vs Set Current

FIGURE 5. Gain vs Set Current

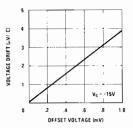

Over a temperature range of  $-55^{\circ}C$  to  $+125^{\circ}C$  the LM121 has less than  $1\mu V/^{\circ}C$  offset voltage drift when nulled. It is important that the offset voltage is accurately nulled to achieve this low drift. The drift is directly related to the offset

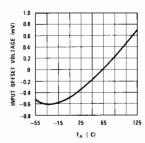

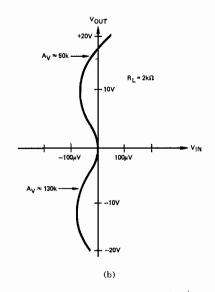

voltage with  $3.8\mu V/^{\circ}C$  drift resulting from every millivolt of offset. For example, if the offset is nulled to  $100\mu V$ , about  $0.4\mu V/^{\circ}C$  will result — or twice the typically expected drift. This drift is quite predictable and could even be used to cancel the drift elsewhere in a system. Figure 6 shows drift as a function of offset voltage. For critical applications selected devices can achieve  $0.2\mu V/^{\circ}C$ .

FIGURE 6. Drift vs Offset Voltage

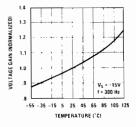

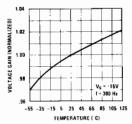

Figures 7 and 8 show the bias current, offset current, and gain variation over a -55°C to +125°C temperature range. These performance characteristics do not tell the whole story. Since the LM121

FIGURE 7. Bias and Offset Current vs Temperature

FIGURE 8. Gain vs Temperature for the LM121

is used with an operational amplifier, the op amp characteristics must be considered for over-all amplifier performance.

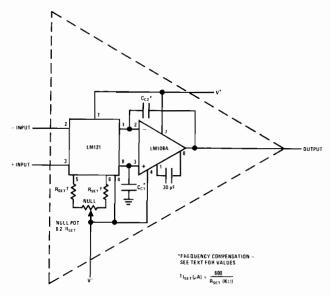

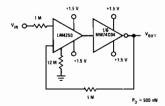

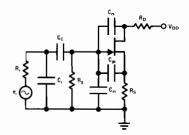

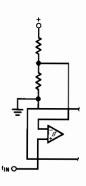

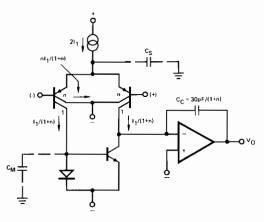

FIGURE 9. General Purpose Amplifier Using the LM121

6 to pin 2 around the op amp acts as an integrating capacitor to roll off the gain. Since the output of the LM121 is differential, a second capacitor is needed to roll off pin 3 of the op amp. These capacitors are  $C_{\text{C1}}$  and  $C_{\text{C2}}$  in Figure 9.

With capacitors equal, the circuit retains good AC power supply rejection. The approximate value of the compensation capacitors is given by:

$$C_C = \frac{8}{10^6 A_{CL} R_{SET}}$$

farads

where  $R_{SET}$  is the current set resistor from each current source and where  $A_{CL}$  is closed loop gain. Table II shows typical capacitor values.

An alternate compensation scheme was developed for applications requiring more predictable and smoother roll off. This is useful where the amplifier's gain is changed over a wide range. In this case  $C_{C1}$  is made large and connected to  $V^+$  rather than ground. The output of the LM121 is rendered single ended by a  $0.01\mu F$  bypass capacitor to  $V^+$ . Overall frequency compensation then is achieved by an integrating capacitor around the op amp:

Bandwidth at unity gain

$$\cong \frac{12}{2\pi R_{SET} C}$$

for 0.5 MHz bandwidth C =

$$\frac{4}{10^6 R_{SET}}$$

TABLE II. Typical compensation capacitors for various operating currents and closed loop gains. Values given apply to LM101A, LM108, and LM741 type amplifiers.

| CLOSED<br>LOOP     | CURRENT SET RESISTOR |              |               |        |              |

|--------------------|----------------------|--------------|---------------|--------|--------------|

| GAIN               | <b>120</b> kΩ        | <b>60</b> kΩ | <b>30 k</b> Ω | 12 kΩ  | <b>6 k</b> Ω |

| A <sub>V</sub> = 1 | 68 pF                | 130 pF       | 270 pF        | 680 pF | 1300 pF      |

| A <sub>V</sub> = 5 | 15 pF                | 27 pF        | 50 pF         | 130 pF | 270 pF       |

| $A_V = 10$         | 10 pF                | 15 pF        | 27 pF         | 68 pF  | 130 pF       |

| $A_V = 50$         | 1 pF                 | 3 pF         | 5 pF          | 15 pF  | 27 pF        |

| $A_{V} = 100$      |                      | 1 pF         | 3 pF          | 5 pF   | 10 pF        |

| $A_{V} = 500$      |                      |              | 1 pF          | 1 pF   | 3 pF         |

| $A_{V} = 1000$     |                      |              |               |        |              |

For use with higher frequency op amps such as the LM118 the bandwidth may be increased to about 2 MHz. If closed loop gain is greater than unity "C" may be decreased to:

$$C = \frac{4}{10^6 A_{CL} R_{SET}}$$

#### **Applications**

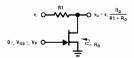

No attempt will be made to include precision op amp applications as they are well covered in other literature. The previous sections detail frequency compensation and drift problems encountered in using very low drift op amps. The circuit shown in Figure 9 will yield good results in almost any op amp application. However, it is important to choose the operating current properly. From the curves given it is relatively easy to see the effects of current changes. High currents increase gain and reduce op amp effects on drift. Bias and offset current also increase at high current. When the operating source resistance is relatively high, errors due to high bias and offset current can swamp offset voltage drift errors. Therefore, with high source impedances it may be advantageous to operate at lower currents.

Another important consideration is output common mode voltage. This is the voltage between the outputs of the LM121 and the positive power supply. Firstly, the output common mode voltage must be within the operating common mode range of the output op amp. At currents above 10µA there is no problems with the LM108, LM101, and LM741 type devices. Higher currents are needed for devices with more limited common mode range, such as the LM118. As the operating current is increased, the positive common mode limit for the LM121 is decreased. This is because there is more voltage drop across the internal 50k load resistors. The output common mode voltage and positive common mode limits are about equal and given by:

Output common mode voltage positive common mode limit

$$\approx V^{+} - 0.6V^{+} \frac{0.65 \times 50 k\Omega}{R_{ext}}$$

If it is necessary to increase the common mode output voltage (or limit), external resistors can be connected in parallel with the internal  $50k\Omega$  resistors. This should only be done at high operating currents (80 $\mu$ A) since it reduces gain and diverts part of the input stage current from the internal biasing circuitry. A reasonable value for external resistors is  $50k\Omega$ .

The external resistors should be of high quality and low drift, such as wirewound resistors, since they will affect drift if they do not track well with temperature. A 20ppm/°C difference in external resistor temperature coefficient will introduce an additional  $0.3\mu V/^{\circ}C$  drift.

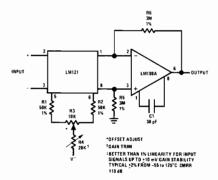

An unusually simple gain of 1000 instrumentation amplifier can be made using the LM121. The amplifier has a floating, full differential, high impedance input. Linearity is better than 1%, depending upon input signal level with maximum error at maximum input. Gain stability, as shown in Figure 10, is about  $\pm 2\%$  over a  $-55^{\circ}$ C to  $\pm 125^{\circ}$ C temperature range. Finally, the amplifier has very low drift and high CMRR.

FIGURE 10. Instrumentation Amplifier Gain vs Temperature

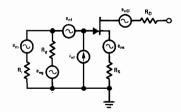

Figure 11 shows a schematic of the instrumentation amplifier. The LM121 is used as the input stage and operated open-loop. It converts an input voltage to a differential output current at pins 1 and 8 to drive an op amp. The op amp acts as a current to voltage converter and has a single-ended output.

FIGURE 11. Gain of 1000 Instrumentation Amplifier

Resistors  $R_1$  and  $R_2$  with null pot  $R_3$  set the operating current of the LM121 and provide offset adjustment.  $R_4$  is a fine trim to set the gain at 1000. There is very little interaction between the gain and null pots.

This instrumentation amplifier is limited to a maximum input signal of ±10 mV for good linearity. At high signal levels the transfer characteristic of the LM121 become rapidly non-linear, as with any differential amplifier. Therefore, it is most useful as a high gain amplifier.

Since feedback is not applied around the LM121, CMRR is not dependent on resistor matching. This eliminates the need for precisely matched resistor as with conventional instrumentation amplifiers. Although the linearity and gain stability are not as good as conventional schemes, this amplifier will find wide application where low drift and high CMRR are necessary.

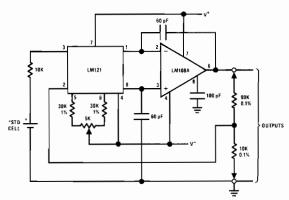

A precision reference using a standard cell is shown in Figure 12. The low drift and low input current of the LM121A allow the reference amplifier to buffer the standard cell with high accuracy. Typical long term drift for the LM121 operating at constant temperature is less than  $2\mu V$  per 1000 hours.

To minimize temperature gradient errors, this circuit should be shielded from air currents. Good

single-point wiring should also be used. When power is not applied, it is necessary to disconnect the standard cell from the input of the LM121 or it will discharge through the internal protection diodes.

#### CONCLUSIONS

A new preamplifier for operational amplifiers has been described. It can achieve voltage drifts as low as many chopper amplifiers without the problems associated with chopping. Operating current is programmable over a wide range so the input characteristics can be optimized for the particular application. Further, using a preamp and a conventional op amp allows more flexibility than a single low-drift op amp.

FIGURE 12. 10V Reference

T. D. Isbell D. S. Mishler JUNE 1973

#### LM1800 (LM1310, LM1310E\*) PHASE LOCKED LOOP FM STEREO DEMODULATOR

#### INTRODUCTION

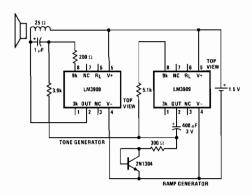

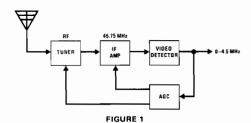

The LM1800 is a phase locked loop FM stereo demodulator built on a single monolithic die. In addition to separating left (L) and right (R) signal information from the detected IF output, the LM1800 features automatic stereo/monaural switching, 45 dB power supply rejection, and a 100 mA stereo indicator lamp driver. Particularly attractive is the low external part count and total elimination of coils. A single inexpensive potentiometer performs all tuning. The resulting FM stereo system delivers high fidelity sound while still meeting the cost requirements of inexpensive stereo receivers.

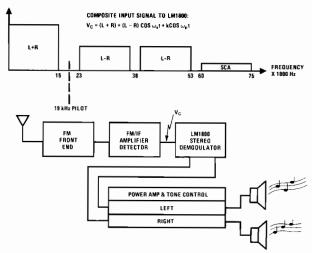

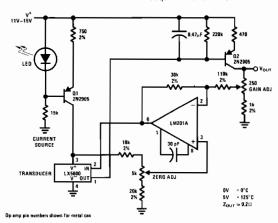

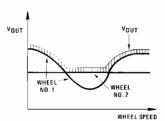

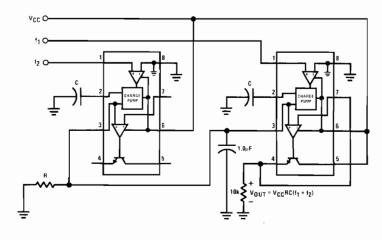

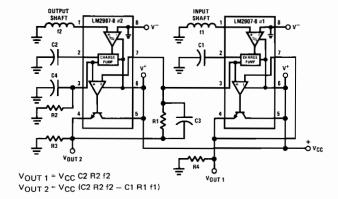

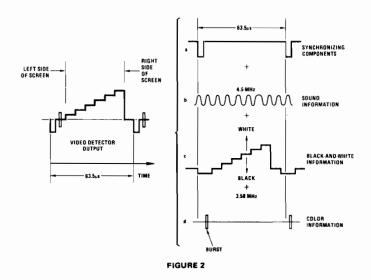

Figures 1 and 2 outline the role played by the LM1800 in the FM stereo receiver. The frequency domain plot shows that the composite input waveform contains L+R information in the audio band and L-R information suppressed carrier modulated on 38 kHz. A 19 kHz pilot tone, locked to the 38 kHz subcarrier at the transmitter, is also included. SCA information occupies a higher band but is of no importance in the consumer FM receiver.

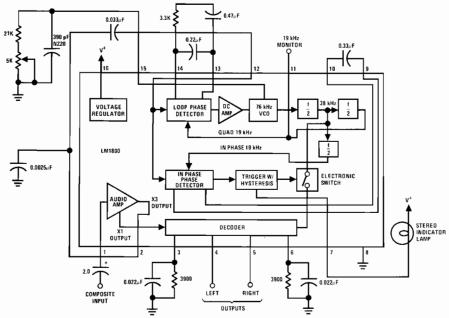

The block diagram of the LM1800 shows the composite input signal applied to the audio frequency amplifier, which acts as a unity gain buffer to the decoder section. A second amplified signal is capacitively coupled to two phase detectors — one in the phase locked loop and the other in the

stereo switching circuitry. In the phase locked loop, the output of the 76 kHz voltage controlled oscillator (VCO) is frequency divided twice (to 38 then 19 kHz), forming the other input to the loop phase detector. The output of the loop phase detector adjusts the VCO to precisely 76 kHz. The 38 kHz output of the first frequency divider becomes the regenerated subcarrier which demodulates L-R information in the decoder section. The amplified composite and an "in phase" 19 kHz signal, generated in the phase locked loop, drive the "in phase" phase detector. When the loop is locked, the DC output voltage of this phase detector measures pilot amplitude. For pilot signals sufficiently strong to enable good stereo reception the trigger latches, applying regenerated subcarrier to the decoder and powering the stereo indicator lamp. Hysteresis, built into the trigger, protects against erratic stereo/monaural switching and the attendant lamp flicker.

In the monaural mode (electronic switch open) the decoder outputs duplicate the composite input signal except that the de-emphasis capacitors (from pins 3 and 6 to ground) roll off with the load resistors at 2 kHz. In the stereo mode (electronic switch closed), the decoder demodulates the L-R information, matrixes it with the L+R information, then delivers buffered separated L and R signals to output pins 4 and 5 respectively.

FIGURE 1. FM Receiver Block Diagram and Frequency Spectrum of LM1800 Input Signal

<sup>\*</sup>The information contained in this application note also generally applies to LM1310, LM1310E.

#### CIRCUIT DESCRIPTION

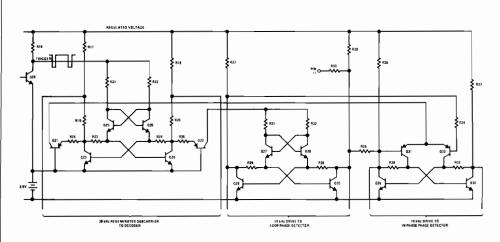

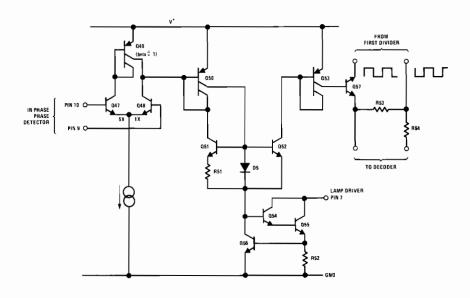

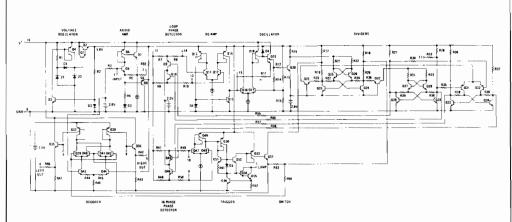

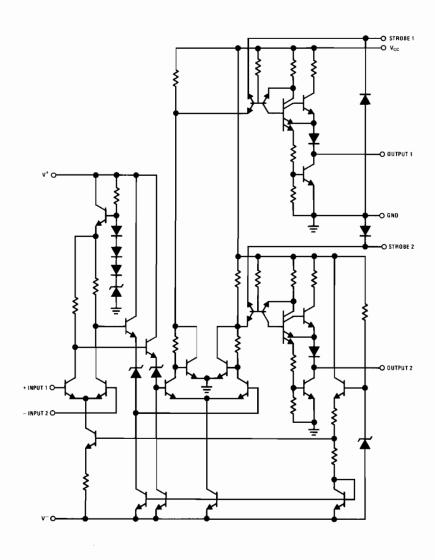

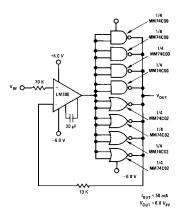

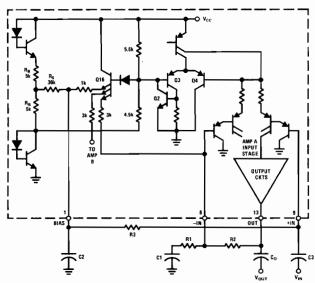

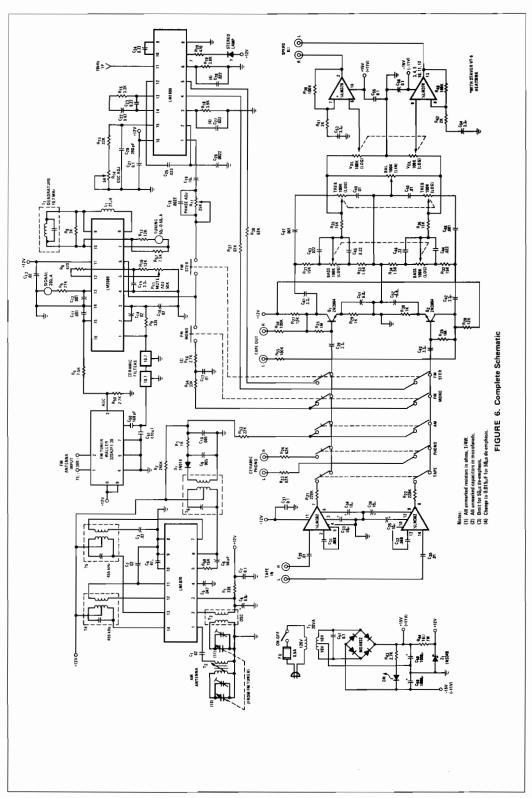

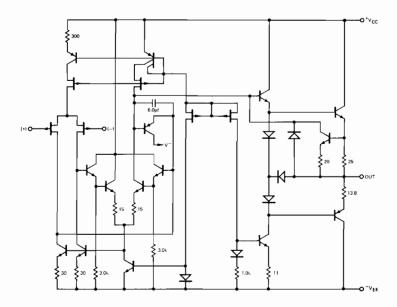

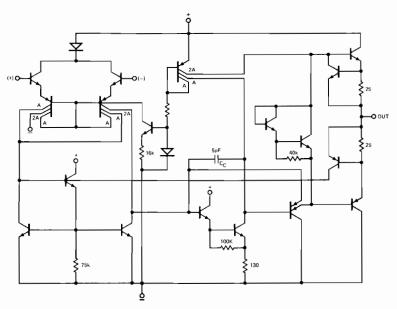

The complex circuit schematic of Figure 13 is more easily understood by reducing it to four subsections:

Regulator and Audio Amplifier Phase Locked Loop Stereo/Monaural Switching Circuitry Decoder and Output Section

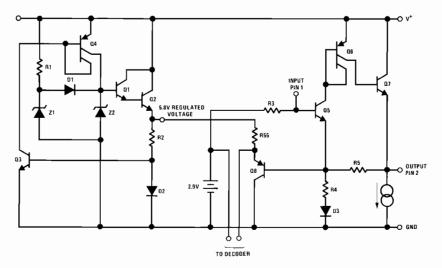

#### Regulator and Audio Amplifier

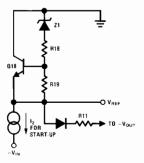

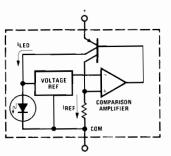

Transmission of power supply ripple and noise has plagued users of integrated FM stereo demodulators in the past. The introduction of a voltage regulator on the chip, along with improvements in the decoder output circuitry, provides excellent supply rejection, eliminating the need for costly supply filtering. Figure 3 shows an equivalent schematic of the 5.8V regulator. Z<sub>2</sub> holds the voltage across

FIGURE 2. LM1800 Block Diagram

FIGURE 3. Regulator and Audio Amplifier

$R_2$  constant, thereby establishing a constant current through  $D_2,\, Q_3$  and  $Q_4.$  The current through  $Z_2$  then depends on the voltage drop across  $Z_2$  and not on the supply line.  $R_1,\, Z_1$  and  $D_1$  assure startup after which the voltage across  $D_1$  drops to zero, disconnecting  $R_1$  from the remainder of the regulator circuitry.

The audio amp is biased internally by 2.9V through  $R_3$  to the base of  $Q_5$ . Since the emitter current of  $Q_5$  is much less than that of  $Q_7$  and the base current of  $Q_8$  is also negligible, current through  $R_4$  approximately equals that through  $R_5$ . The DC quiescent voltage at the output pin becomes:

$$V_{P2} = V_{E5} + (V_{E5} - 0.7) R_5/R_4 = 5.4 \text{ volts}$$

and gain to a dynamic input is:

$$A_{pin,1-pin,2} = 1 + R_5/R_4 = 3.0$$

A second signal path of unity gain exists through  $\Omega_{\rm B}$  and  $\Omega_{\rm B}$ . The potential at  $\Omega_{\rm g}$ 's emitter is also approximately 2.9V, providing conveniently biased drive to the decoder section.  $R_3$  sets the input resistance at typically 45 k $\Omega$ .

#### Phase Locked Loop

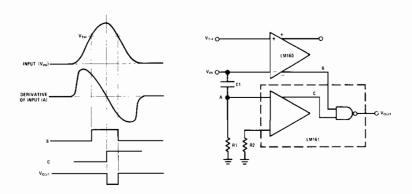

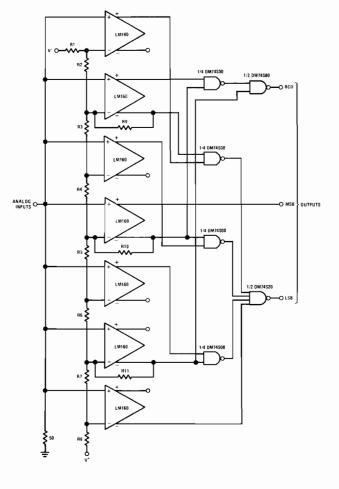

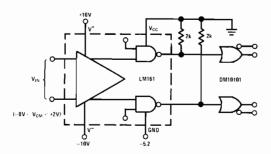

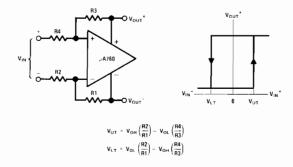

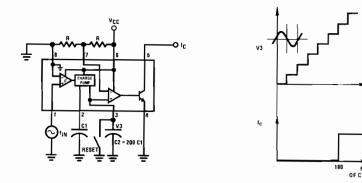

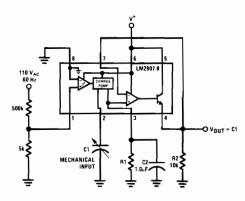

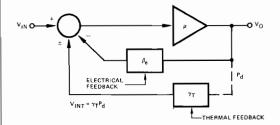

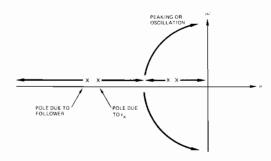

A phase locked loop is a feedback system comprised of a phase detector, a low pass filter, and an error amplifier in the forward transmission path while a voltage controlled oscillator provides the feedback element. Figure 4 illustrates a simplified loop. Without an input signal the error voltage drops to zero. The VCO then oscillates at some free running frequency, fo. As an input signal is introduced, the phase detector compares the phase (and frequency, since frequency is the time derivative of phase) of the input signal with that of the VCO, generating an error voltage related to the frequency difference. The error signal is filtered

FIGURE 4. Basic Phase Locked Loop Block Diagram

and amplified before it is applied to the control input of the VCO. The control voltage forces the VCO frequency to move in the direction that reduces the frequency difference between the input signal and f<sub>O</sub>. For free running frequencies sufficiently close to the incoming signal, the nature of loop feedback causes the VCO to synchronize to exactly the incoming frequency. Some finite phase difference exists between the two signals. This phase difference is necessary to generate the corrective error voltage for the VCO.

The LM1800 operates on precisely this principle except that the VCO free runs at approximately four times the frequency of the incoming pilot. Two frequency dividers provide a signal at the phase detector input sufficiently close in frequency to the 19 kHz pilot tone to accomplish lock. The loop provides sufficient gain to keep the phase error small, and the frequency dividers generate accurate 50% duty cycle waveforms, both necessary requirements for good stereo demodulation.

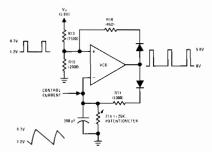

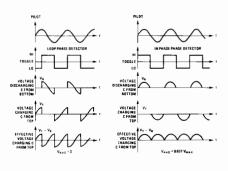

#### vco

Consider the voltage controlled oscillator scheme outlined in Figure 5. At turn-on the non-inverting input rises rapidly to 1.2V as set by the resistor divider (R<sub>13</sub>/R<sub>15</sub>), while the external capacitor holds the inverting input low. The output quickly rises to 5.8V and begins charging the capacitor through R<sub>11</sub>. The output simultaneously lifts the non-inverting input rapidly to 4.7V. When the voltage across the capacitor also reaches 4.7V, the output drops low, reverse biasing the diodes while the capacitor begins discharging through the potentiometer. With the output low, the non-inverting input is again resistively set at 1.2V until the capacitor discharges and the cycle repeats. The capacitor voltage decays about twenty times slower than it charges, resulting in a repetition rate dominated by the external RC time constant.

FIGURE 5. Equivalent Circuit of VCO

When the VCO is in its high state, the output is clamped at the regulated voltage. This causes the temperature coefficient of the trip points to be dependent on only the regulated voltage, resulting in an oscillation frequency quite independent of temperature.

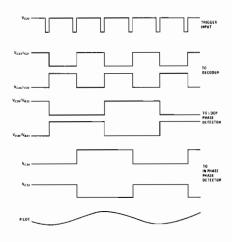

Figure 6 details the frequency dividers used to transform the short duty cycle 76 kHz waveform into precisely 50% duty cycle 38 and 19 kHz waveforms. To understand their operation, first consider  $\Omega_{24}/\Omega_{25}$  saturated while  $\Omega_{23}/\Omega_{26}$  are in cutoff. As the trigger goes low the collector voltage for  $\Omega_{25}/\Omega_{26}$  collapses and conduction in them ceases. Since  $\Omega_{23}/\Omega_{24}$  are bistable by themselves,  $\Omega_{24}$  remains saturated and  $\Omega_{23}$  cutoff. With the trigger in this low state, the base of  $\Omega_{24}$  sits at one base-emitter voltage (0.7V) while the base of  $\Omega_{23}$  is at the saturation voltage of  $\Omega_{24}$

FIGURE 6. Frequency Dividers

(0.2V). On the rising edge of the trigger pulse,  $Q_{26}$  conducts before  $Q_{25}$  because of the different voltages on their emitters.  $Q_{26}$  saturates and drives enough current through  $R_{24}$  to saturate  $Q_{23}$  while  $Q_{24}$  goes to cutoff. Thus  $Q_{23}/Q_{24}$  change state on every rising edge of a trigger pulse, dividing the repetition rate of the trigger signal by two. The other two frequency dividers function similarly except that the third one is slaved in quadrature

FIGURE 7. Frequency Divider Waveforms

with the second. Figure 7 shows the waveforms throughout the divider string.

#### Loop Phase Detector

The loop phase detector is shown equivalently in Figure 8. Consider the loop phase detector where the toggle is driven in quadrature with the pilot.

The waveforms show that zero volts DC appears across the capacitor. Any deviation from this quadrature relationship produces a voltage, which

FIGURE 8. Phase Detector Performance

is a function of phase difference, across the capacitor. A second condition results when the toggle is driven in phase with the pilot. In this case the DC voltage across the capacitor measures pilot tone amplitude and is used to drive the stereo-monaural switching circuitry.

The DC amplifier in the phase locked loop is standard differential with push-pull output, maintaining excellent temperature stability in the loop.

#### Stereo/Monaural Switching Circuitry

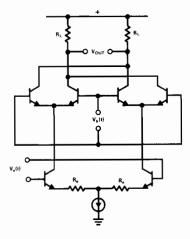

Composite inputs sufficiently large for good quality stereo switch the LM1800 into the stereo mode

via the circuitry of Figure 9. The differential pair Q<sub>47</sub>/Q<sub>48</sub> is driven by the DC output of the "in phase" phase detector. When the phase locked loop is locked, this differential input voltage to Q<sub>47</sub>/Q<sub>48</sub> is proportional to pilot amplitude (as explained in previous section and Figure 8). The emitter area of  $Q_{47}$  is five times larger than that of Q48, building in 40 mV offset voltage. Until the base of Q48 is 40 mV higher than the base of  $Q_{47}$ , collector current in  $Q_{47}$  is larger than collector current in Q48. Transistor design of Q49 constrains its beta to unity. So long as IC47 is larger than  $I_{C48}$ ,  $Q_{49}$  remains in saturation (holding  $Q_{50}$  in cutoff). When the 40 mV offset voltage is overcome in Q<sub>47</sub>/Q<sub>48</sub>, Q<sub>49</sub> comes out of saturation and  $Q_{50}$  enters conduction.  $Q_{50}$ ,  $Q_{51}$ ,  $D_{5}$ , and R<sub>51</sub> form a positive feedback loop which regenerates when Q<sub>50</sub> is allowed to conduct. R<sub>51</sub> is chosen to halt the regeneration process at IC51 = 30µA. The latched loop current drives the lamp driver Darlington ( $Q_{54}/Q_{55}$ ) as well as  $Q_{57}$  (via  $Q_{52}$  and  $Q_{53}$ ). The signal to the decoder switches from common to differential mode 38 kHz and stereo demodulation begins. Should the input composite waveform decrease by 6 dB, the differential voltage back at  $Q_{47}/Q_{48}$  reduces to 20 mV. Under this condition the current flowing from  $Q_{49}$  into  $Q_{51}$  (as  $Q_{49}$  returns toward saturation) is sufficient to unlatch the loop, prohibiting drive to both  $Q_{57}$  and  $Q_{54}/Q_{55}$ . The signal driving the decoder returns to common mode 38 kHz and monaural reception resumes. R<sub>52</sub> and  $Q_{56}$  limit cold lamp surge currents to about 250 mA.

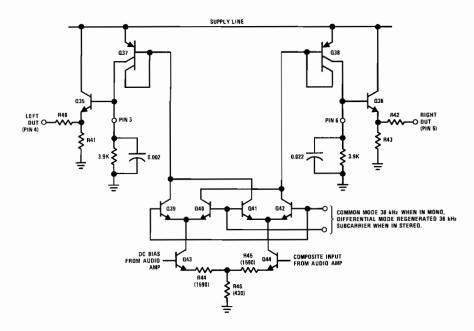

#### **Decoder and Output Section**

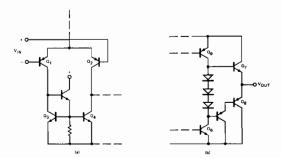

The basic decoder section shown in Figure 10 has been used previously in the LM1304, LM1305, LM1307, LM1307E series, and is well described in reference 2. In an effort to transform the rigor into intuition, consider first Q43, Q44, and the emitter matrix resistors (R44, R45, R46). Under small signal conditions the emitter of Q43 remains at a constant voltage while the emitter of Q44 tracks the composite input waveform applied to its base. Analysis of the simplified circuit shown in Figure 11 produces the current waveforms through R44 and R<sub>45</sub>. These currents are not equal and opposite as in a standard multiplier because R46 in no way approximates a current source. Rather, the currents through R44 and R45 can be shown to be related by a constant:

$$K = I_{R44}/I_{R45} = R_{46}/(R_{45} + R_{46})$$

For NPN transistors operating in their active regions, collector current approximately equals emitter current, then:

$$I_{C43} = KI_{C44}$$

Since the upper quad transistors ( $Q_{39}$ ,  $Q_{40}$ ,  $Q_{41}$ ,  $Q_{42}$ ) operate as antiphase switches, the base current resulting through  $Q_{38}$  becomes the sum of  $I_{C44}$  gated by  $Q_{42}$  and  $I_{C43}$  gated by  $Q_{40}$ . These upper quad transistors alternately pass or block the currents flowing in  $Q_{43}$  and  $Q_{44}$ . This gating

FIGURE 9. Stereo/Monaural Switch

FIGURE 10. Decoder and Output Section

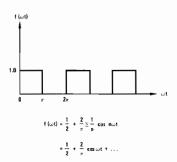

action is represented mathematically in Figure 12. Applying the gating function to the currents in  $Q_{43}$  and  $Q_{44}$ :

$$I_{838} = V_C \left[ \frac{1}{2} - \frac{2}{\pi} \cos \omega_s t \right] - K V_C \left[ \frac{1}{2} + \frac{1}{\pi} \cos \omega_s t \right]$$

where  $V_C$  = composite input signal

and  $\omega_s$  = subcarrier (38 kHz)

Substituting the expression for  $V_C$  (given in Figure 1), carrying out the algebra, and retaining only the low frequency terms gives:

$$I_{B38} = L \left[ 0.5 - 0.5K - \frac{K+1}{\pi} \right] + R \left[ 0.5 - 0.5K + \frac{K+1}{\pi} \right]$$

Equating the coefficient of the left (L) term to zero, yields a value for K of 0.22. Thus designing the matrix resistors  $R_{44}$ ,  $R_{45}$ ,  $R_{46}$  to give this

FIGURE 11. Equivalent Circuit for Decoder Matrix

value for K cancels all left information from the  $\rm Q_{38}$  current. The base current of  $\rm Q_{38}$  then is proportional to the right (R) separated signal.

FIGURE 12. Fourier Analysis of Decoder Switching Waveform

Similar analysis can be performed to show that the base current of  $Q_{37}$  contains only left (L) separated signal. Amplification and level shifting of these base currents occurs in fixed beta transistors  $Q_{37}$  and  $Q_{38}$ , and the resultant currents drive external grounded loads at pins 3 and 6. Since the collector currents of  $Q_{37}$  and  $Q_{38}$  depend only on their respective base currents, supply ripple and noise are rejected from the output pins.  $Q_{35}$  and  $Q_{36}$  serve as output buffers with  $R_{40}$  and  $R_{42}$  setting the output resistance at typically  $1300\Omega$ .

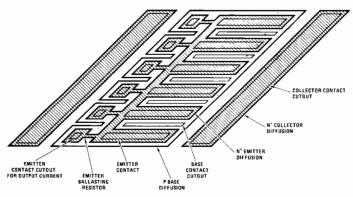

FIGURE 13. LM1800 Equivalent Schematic

In the monaural mode the upper quad transistors are driven by a common mode signal which causes all four transistors to conduct equally. This passes the composite input directly to the outputs where the de-emphasis capacitors serve to roll off the higher frequency unwanted information. Further, the LM1800 offers improved distortion over earlier integrated demodulators. As the signal driving the base of Q44 increases in amplitude, the AC currents through  $Q_{43}$  and  $Q_{44}$  become a significant percentage of the DC bias currents. In this manner the transconductance of  $Q_{43}$  and  $Q_{44}$  is modulated by the incoming signal resulting in second harmonic distortion. To reduce this effect, the base bias potentials of  $Q_{43}$  and  $Q_{44}$  and the matrix resistor values have been raised above the levels used in earlier demodulators. The loss in gain that this implies is recovered in the PNP level shifting transistors.

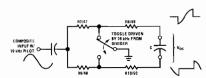

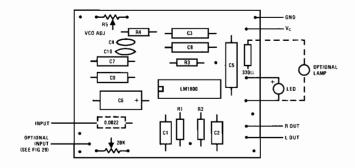

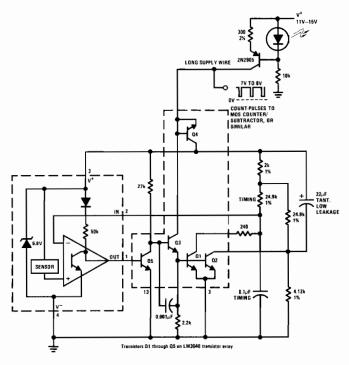

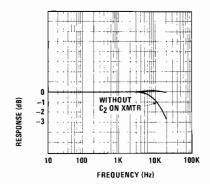

#### CIRCUIT PERFORMANCE

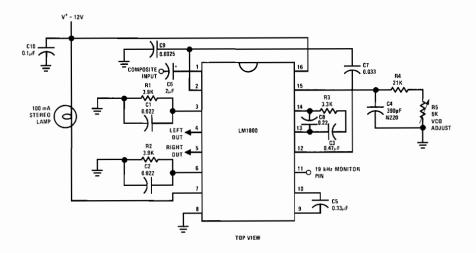

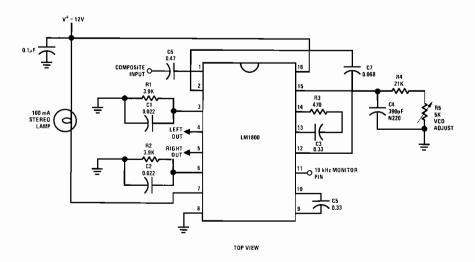

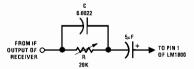

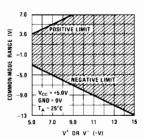

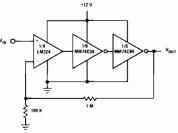

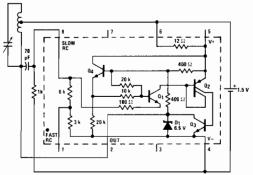

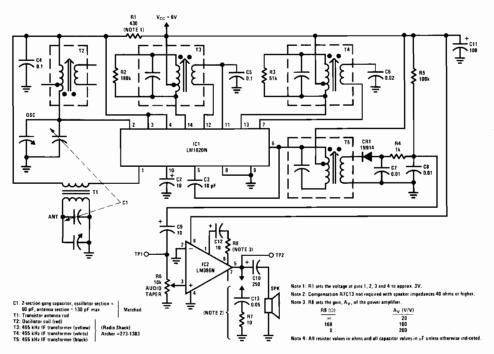

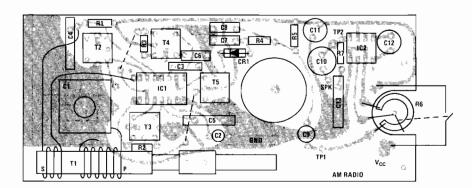

The circuit in Figure 14 illustrates the simplicity of designing an FM stereo demodulation system using the LM1800. R<sub>3</sub> and C<sub>3</sub> establish an adequate loop capture range and a low frequency well damped natural loop resonance. C<sub>8</sub> has the effect of shunting phase jitter, a dominant cause of high frequency channel separation problems. Recall that the 38 kHz subcarrier regenerates by phase locking the output of a 19 kHz divider to the pilot tone. Time delays through the divider result in the 38 kHz waveform leading the transmitted subcarrier. Addition of capacitor Co (0.0025µF) at pin 9 introduces a lag at the input to the phase lock loop, compensating for these frequency divider delays. The output resistance of the audio amplifier is designed at  $500\Omega$  to facilitate this connection.

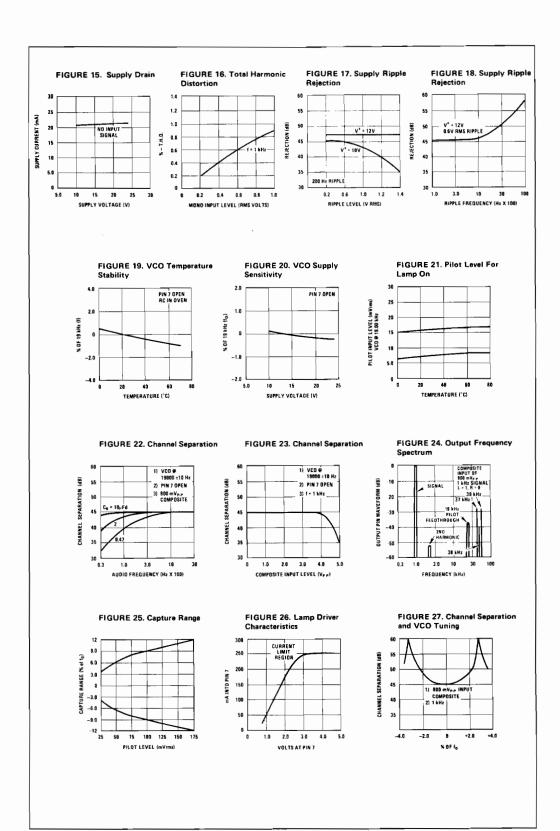

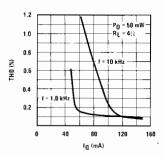

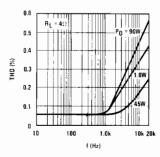

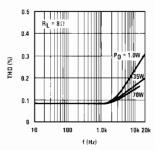

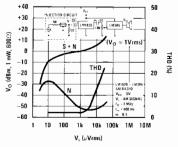

Table I and Figures 15 through 27 detail typical performance resulting from this basic hookup. The excellent supply rejection characteristics shown,

coupled with the fact that supply current drain is nearly independent of supply voltage, somewhat simplifies receiver power supply requirements. The low drain current, even for a 24V supply, results in cooler circuit operation and increased reliability. Figure 22 shows that increasing the size of input coupling capacitor  $C_6$  improves low frequency channel separation by reducing the phase shift of the lower frequency components in the composite waveform.

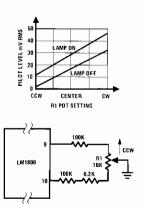

Figure 27 illustrates an interesting characteristic of the LM1800: channel separation increases as the VCO is detuned in either direction. The separation peaks change in size for different signal frequencies and change in position (% detuning) for changing composite amplitudes. If the VCO free running frequency is set at precisely 19 kHz, separation remains constant over a wide range of composite amplitude levels, signal frequencies, temperature changes, and component drifts. The 19 kHz monitor available to the customer at pin 11 can be fed into a frequency counter for accurate adjustment of the VCO free running frequency. If a frequency counter is not available, the VCO can be adjusted by utilizing the fact that capture range is symmetrical about the incoming pilot:

- (a) rotate frequency adjust pot full CCW

- (b) insert weak composite input signal

- (c) rotate pot CW until stereo lamp comes on, note position of pot (R<sub>x</sub>)

- (d) remove composite and rotate pot full CW

- (e) reinsert weak composite input signal

- (f) rotate pot CCW until stereo lamp comes on again, note position of pot (R<sub>v</sub>)

- set pot midway between Ry and Ry.

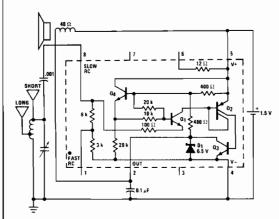

Figure 28 is included for the user who is willing to sacrifice some performance, particularily channel separation at high input levels and low frequencies to eliminate two external capacitors and reduce the electrolytic input coupling cap size.

On either circuit, some improvement in channel separation can be attained by altering the VCO

FIGURE 14. Typical Application Circuit

TABLE 1.

| PARAMETERS                     | CONDITIONS                                               | TYP            | UNITS               |

|--------------------------------|----------------------------------------------------------|----------------|---------------------|

| Supply Current                 | Lamp "OFF"                                               | 21             | mA                  |

| Lamp Driver Saturation Voltage | 100 mA Lamp Current                                      | 1.3            | V                   |

| Lamp Driver Leakage Current    |                                                          | 1              | nA                  |

| Pilot Level for Lamp "ON"      | Pin 11 Adjusted for 19 kHz ±10 Hz                        | 16             | mV                  |

| Pilot Level for Lamp "OFF"     | Pin 11 Adjusted for 19 kHz ±10 Hz                        | 8              | mV                  |

| Stereo Lamp Hysteresis         |                                                          | 6              | dB                  |

| Stereo Channel Separation      | 100 Hz (Note 1)<br>1000 Hz (Note 1)<br>10000 Hz (Note 1) | 40<br>45<br>45 | dB<br>dB<br>dB      |

| Monaural Channel Unbalance     | 200 mVrms, 1000 Hz Input                                 | 0.3            | dB                  |

| Recovered Audio                | 200 mVrms, 400 Hz Input                                  | 190            | mVrms               |

| Total Harmonic Distortion      | 500 mVrms, 1000 Hz Monaural Input                        | 0.5            | %                   |

| Capture Range                  | 25 mV of 19 kHz pilot                                    | ±4             | % of f <sub>0</sub> |

| Supply Ripple Rejection        | 600 mVrms, 200 Hz Ripple                                 | 45             | dB                  |

| Dynamic Input Resistance       |                                                          | 45             | kΩ                  |

| Dynamic Output Resistance      |                                                          | 1300           | Ω                   |

| SCA Rejection                  | 200 mVrms Composite at 67 kHz                            | 50             | dB                  |

| Ultrasonic Frequency Rejection | Combined 19 and 38 kHz                                   | 33             | dB                  |

Note 1: The stereo input signal is made by summing 123 mVrms left or right modulated signal with 25 mVrms of 19 kHz pilot tone, measuring all voltages with an average responding meter calibrated in rms, the resulting waveform is about 800 mVp-p. VCO adjusted to 19kHz ±10Hz.

FIGURE 28. Minimum Parts Count Application Circuit

slightly. The loop gain can be shown to decrease for a decrease in VCO resistance ( $R_4 + R_5$  in Figure 14). Maintaining a constant RC product, while increasing the capacity from 390 pF to 510 pF narrows the capture range by about 25%. Although the resulting system has slightly improved channel separation, it is more sensitive to VCO tuning.

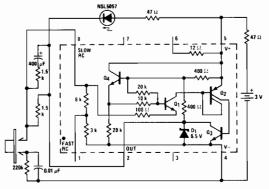

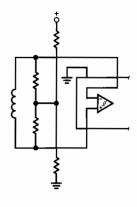

When the circuits so far described are connected in an actual FM receiver, channel separation often suffers due to imperfect frequency response of the IF stage. The input lead network of Figure 29

FIGURE 29. Compensation for Receiver IF Rolloff

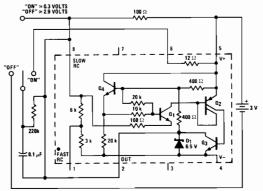

can be used to compensate for roll off in the IF and will restore high quality stereo sound. Should a receiver designer prefer a stereo/monaural switching point different than those programmed into the LM1800 (pilot: 16 mVrms on, 8.0 mVrms off typical), the circuit of Figure 30 provides the desired flexibility.

The user who wants slightly increased voltage gain through the demodulator can increase the size of the load resistors ( $R_1$  and  $R_2$  of Figure 14 or 28), being sure to correspondingly change the de-emphasis capacitors ( $C_1$  and  $C_2$ ). Loads as high as  $5600\Omega$  may be used (gain of 1.4). Performance of the LM1800 is virtually independent of the supply voltage used (from 10 to 24V) due to the on chip regulator.

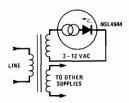

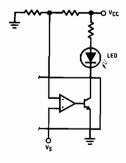

Although the circuit diagrams show a 100 mA indicator lamp, the user may desire an LED. This presents no problem for the LM1800 so long as a resistor is connected in series to limit current to a safe value for the LED. The lamp or LED can be powered from any source (up to 24V), and need not necessarily be driven from the same supply as the LM1800.

FIGURE 30. Stereo/Monaural Switch Point Adjustment

Utilization of the phase locked loop principle enables the LM1800 to demodulate FM stereo signals without the use of troublesome and expensive coils. The numerous features available on the demodulator make it extremely attractive in a variety of home and automotive receivers. Indeed the LM1800 represents a new generation in integrated stereo FM demodulators.

#### REFERENCES

- Blaser, L. and Cocke, W., "The μΑ758, A Phase Locked Loop FM Stereo Multiplex Decoder." Fairchild Application Note 319, June 1972.

- Hector Gasquet, "A Monolithic Integrated FM Stereo Decoder System." Motorola Application Note AN-432A.

- 3. Michael J. Gay, "A Monolithic Phase-Lock-Loop Stereo Decoder." IEEE Transactions on Broad-

- cast and TV Receivers, Vol. BTR-17, No. 3, August 1971.

- Thomas B. Mills, "The Phase Locked Loop IC as a Communication System Building Block." National Semiconductor Application Note AN-46, June 1971.

- "Phase Locked Loops Applications Book," Signetics Corporation, 1972.

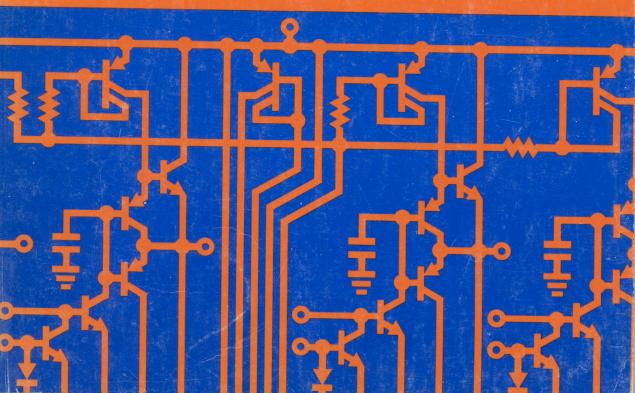

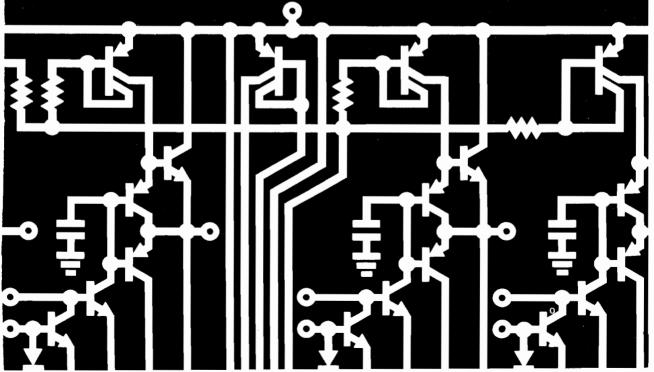

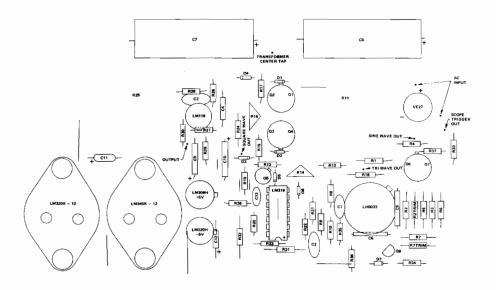

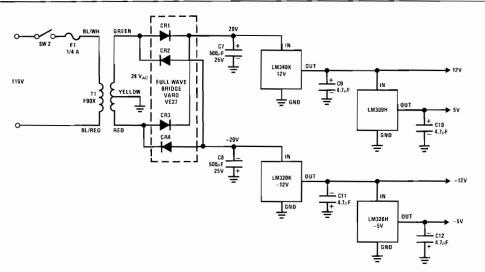

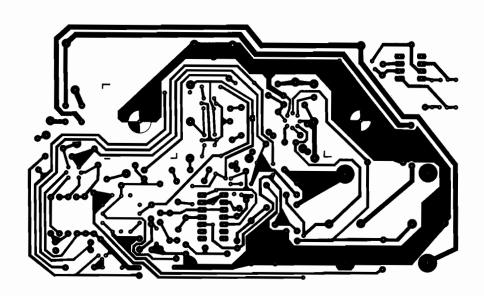

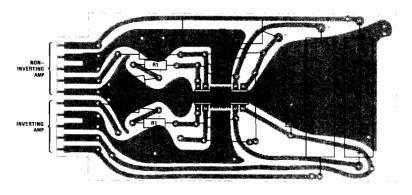

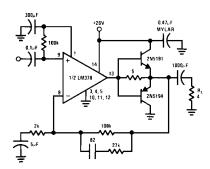

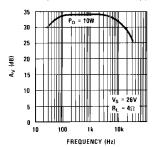

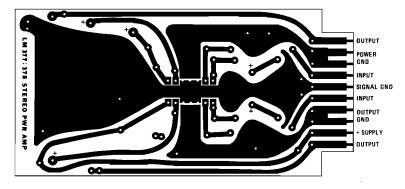

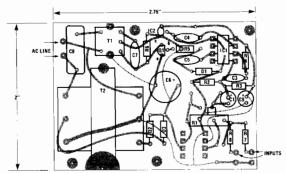

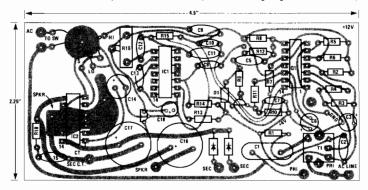

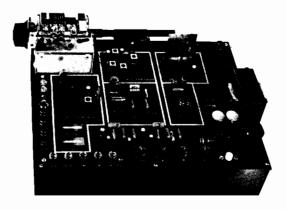

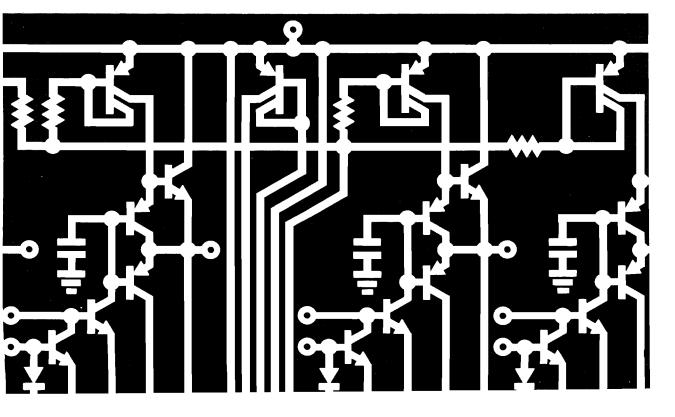

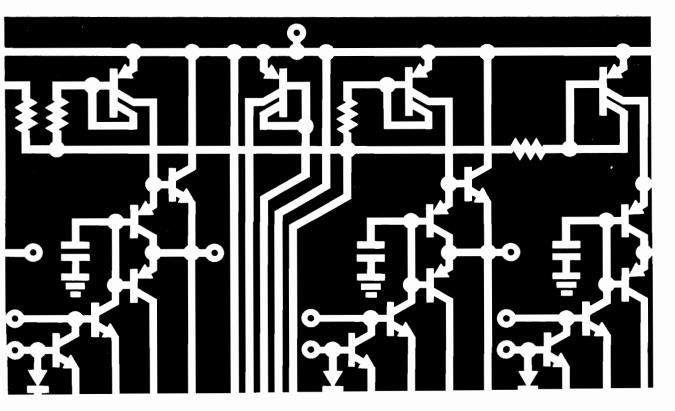

Printed Circuit Board Layout for Circuit of Figure 14.

Todd Smathers Nello Sevastopoulos MAY 1974

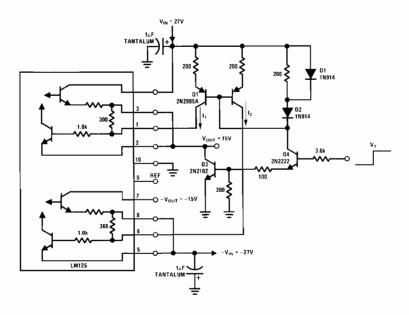

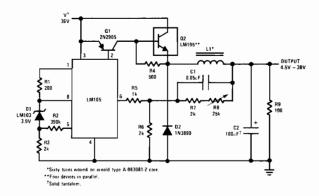

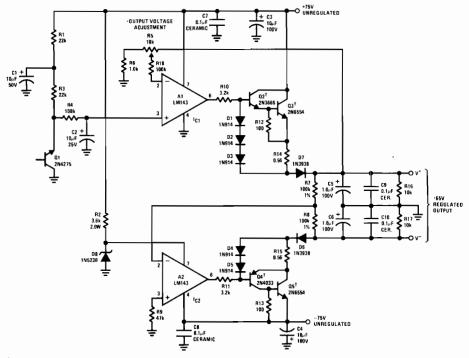

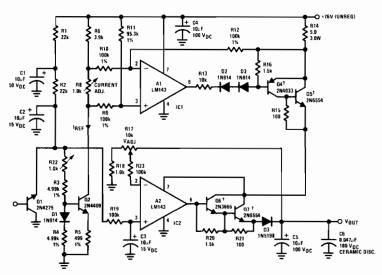

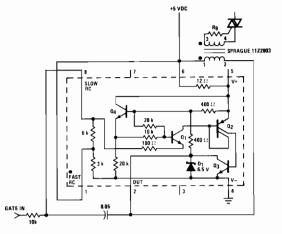

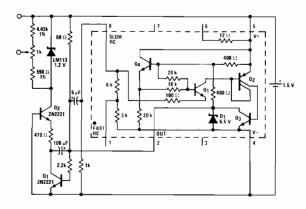

# LM125/LM126/LM127 PRECISION DUAL TRACKING REGULATORS

#### INTRODUCTION

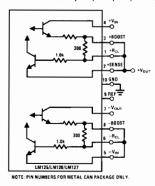

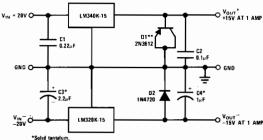

The LM125, LM126, and LM127 family of devices are precision, dual, tracking, monolithic voltage regulators. Each provides separate positive and negative regulated outputs, thus simplifying dual power supply designs. Operation requires few or no external components depending on the application. Internal settings provide fixed output voltages: the LM125 at ±15V, the LM126 at ±12V, and the LM127 at +5.0V and -12V for use in MOS applications.

Each regulator is protected from excessive internal power dissipation by a thermal shutdown circuit which turns off the regulator whenever the chip reaches a preset maximum temperature. Other features include both internal and external current limit sensing for device protection while operating with or without external current boost. For applications requiring more current than the internal current limit will allow, boosted operation is possible with the addition of a one NPN pass transistor per regulator. External resistors sense load current for controlling the limiting circuitry. Internal frequency compensation is provided on both positive and negative regulators. The internal voltage reference pin is brought out to facilitate noise filtering when desired.

#### CIRCUIT DESCRIPTION

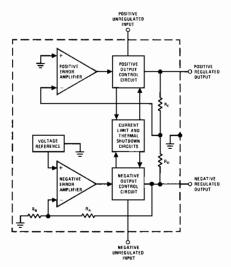

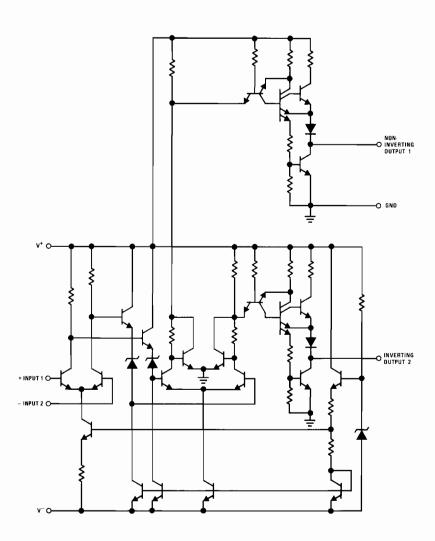

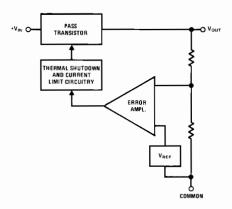

Figure 1 shows a block diagram of the basic dual tracking regulator. A voltage reference establishes a fixed dc level, independent of supply or temperature variations, at the non-inverting input to the negative regulator Error Amplifier. The Error Amplifier drives the Output Control Circuit which includes the high current output transistors, current limiting, and thermal shutdown circuitry.

The negative regulator output voltage is established by comparing the Voltage Reference against a fraction of the output as set by R<sub>A</sub> and R<sub>B</sub>.

To achieve the desired tracking action of the positive regulator, a voltage established between the positive and negative regulator outputs by resistors  $R_{\rm C}$  and  $R_{\rm D}$  is compared to ground by the positive regulator Error Amplifier. This insures

FIGURE 1. Block Diagram for the Basic Dual Tracking Regulator

that the positive regulator output voltage will always equal the negative regulator output voltage multiplied by the ratio of  $R_C$  to  $R_D$ . This ratio is unity for the LM125 ( $V_O=\pm15 V_I$ ), and LM126 ( $V_O=\pm12 V_I$ ), and equals 5/12 for the LM127. The positive regulator Output Control Circuit is essentially the same as that in the negative regulator.

The current limit and thermal shutdown circuitry sense the output load current and die temperature

respectively and switch off all output drive capability upon reaching their predetermined limits.

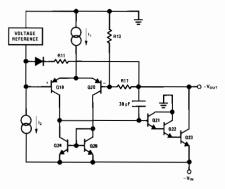

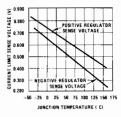

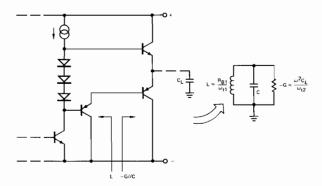

Figure 2 gives a more detailed picture of the negative regulator circuitry. The temperature compensated reference voltage appears at the non-inverting input of the differential amplifier, Q19 and Q20, while an error signal proportional

FIGURE 2. Simplified Negative Regulator

to any change in output voltage is applied to the other input. This error signal is amplified by the differential amplifier, Q19 and Q20, and by the triple Darlington Q21, Q22, Q23 to produce a current change through R13 and R17 which brings the output voltage back to its original value. Loop gain is high, typically 88 dB at low output currents, so a 30 pF compensating capacitor is used to guarantee stability. Since  $-V_{OUT}$  is the output of a high gain feedback amplifier, high supply rejection is ensured.

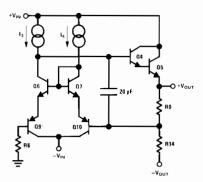

Figure 3 shows the basic positive regulator. This is actually an inverting operational amplifier.

FIGURE 3. Simplified Positive Regulator

The negative regulated voltage ( $\neg V_{OUT}$ ) is applied to the current summing input through R14 while the output ( $+V_{OUT}$ ) is fed-back via R9. Then

+V<sub>OUT</sub> is simply — (R9/R14) (-V<sub>OUT</sub>). Any change in the positive regulator output will create an error signal at the base of Q10 which will be amplified and sent to the voltage follower, Q4 and Q5, forcing the output voltage to track the input voltage. Here the loop gain is on the order of 66 dB so a compensating capacitor of approximately 20 pF is used to ensure amplifier stability.

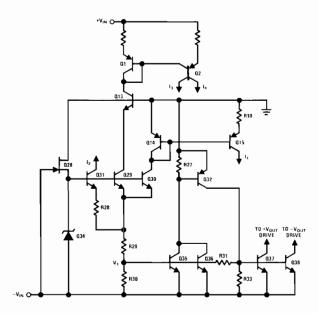

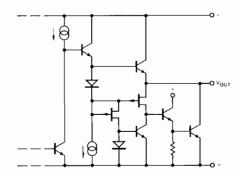

The circuitry used for regulator start up, biasing, temperature sensing, and thermal shutdown is shown in Figure 4. The field effect transistor Q28, is initially ON allowing the negative input voltage to force current through zener diode Q34. When enough current flows to fully establish the zener voltage, transistor Q29, Q30 and Q31 turn on and bias up all current sources. The zener voltage also decreases the gate to source voltage of the FET, pinching it off to a lower current value to reduce quiescent power dissipation.

The thermal sensing and shutdown circuitry is comprised of Q34, Q29, Q35, Q32, Q37, Q38, R27, R29, R30, R31, and R33. The voltage divider made up of R29 and R30 provides a relatively fixed bias voltage V1 at the bases of Q35 and Q36, holding them in the OFF state. When the chip temperature increases to a maximum permissible level, the base to emitter voltage of Q35 and/or Q36 will have decreased sufficiently so that V<sub>1</sub> is now high enough to turn them ON. This causes a voltage drop across R27 sufficient to turn on Q32 which switches Q37 and Q38 to a conducting state shunting all output drive current to -V<sub>IN</sub>. The regulator output voltages are then clamped to zero. Transistors Q35 and Q36 are located on the chip near the regulator output devices so they will see the maximum temperatures reached on the chip, ensuring that neither regulator will ever see more than this preset maximum temperature. The collectors of Q35 and Q36 are tied together so that if either regulator reaches the thermal shutdown temperature, both regulators will shutdown. This ensures that the device can never be destroyed because of excessive internal power dissipation in either regulator.

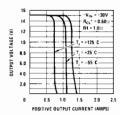

Figure 5 shows the current limiting circuitry used in the positive regulator; the negative regulator current limiter is identical. The internal current limiter is comprised of Q8 and R5; the external current limiter is comprised of Q11 and an external resistor  $R_{\rm CL}$ . Both operate in a similar manner. As the output current through Q5 increases, the voltage drop across resistor R5 eventually turns ON Q8 and shunts all base drive away from the output devices, Q4 and Q5. The maximum load current available with this circuit is approximately 250 mA at  $T_{\rm i}=25^{\circ}{\rm C}$  (see Figure 9).

The external current limiting circuit works in a similar manner. Here the output current is sensed across the external resistor  $R_{CL}$ . When the voltage

FIGURE 4. Start-up, Biasing and Thermal Shutdown Circuitry

drop across  $R_{CL}$  is sufficient to turn ON transistor Q11, the output drive current is switched away from the output devices Q4 and Q5. This externally set current limit is particularly valuable when used with an external current boosting pass transistor where the current limit could be set to protect that transistor from excessive power dissipation.

1 DRIVE

1 D

FIGURE 5. Positive Regulator Current Limiting Circuitry

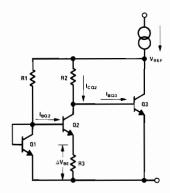

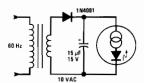

The constant voltage reference circuit is shown in Figure 6. Zener diode  $Z_1$  has a positive temperature coefficient of known value.  $V_{BE}$  of Q18 (negative temperature coefficient) is multiplied by the ratio

of R18 and R19 and added to the positive TC of  $Z_1$  to produce a near zero TC voltage reference. Current source  $I_2$  is used only during start-up.

FIGURE 6. Voltage Reference Circuitry

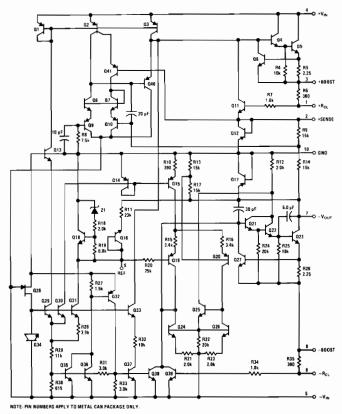

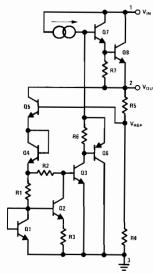

Figure 7 shows the complete schematic of the LM125, LM126, LM127 family of dual regulators. Diodes Q12 and Q17 protect the output transistors, plus any external pass devices used, from breakdown in the event the positive and negative regulated outputs become shorted. Transistors Q6 and Q7 offer full differential voltage gain with the convenience of single ended output. Transistors Q13 and Q33 insure that operation with ±30V input is possible. Q24 and Q26 in the negative regulator amplifier provide single ended output from a differential input with no loss in gain.

FIGURE 7. LM125/LM126/LM127

#### **APPLICATIONS**

The basic dual regulator is shown connected in Figure 8. The only connections required other than plus and minus inputs, outputs, and ground

FIGURE 8. Basic Dual Regulator

are to complete the output current paths from  $+R_{CL}$  to  $+V_{OUT}$  and from  $-R_{CL}$  to  $-V_{IN}$ . These may be a direct shorts if the internal preset current

limit is desired, or resistors may be used to set the maximum current at some level less than the internal current limit. The internal 300 $\Omega$  resistors from pins 3 to 1 and pins 8 to 6 should be shorted as shown when no external pass transistors are used. To improve line ripple rejection and transient response, filter capacitors may be added to the inputs, outputs, or both, depending on the unregulated input available. If a very low noise output voltage is desired, a capacitor may be connected from the reference voltage pin to ground. Thus shunting noise generated by the reference zener. Figure 9 shows the internal current limiting characteristics for the basic regulator circuit of Figure 8.

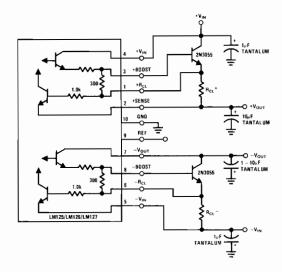

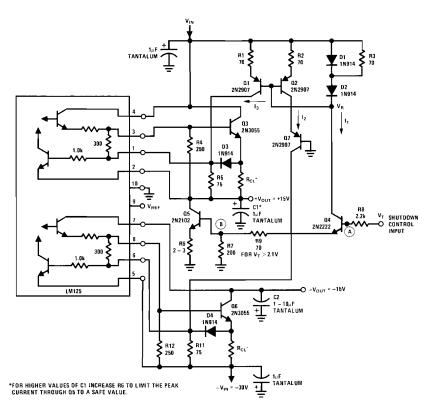

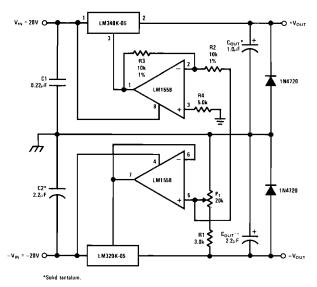

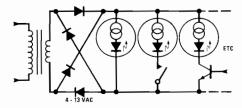

#### HIGH CURRENT REGULATOR

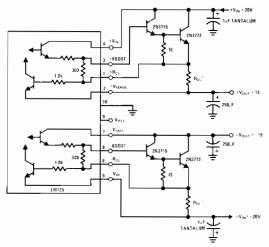

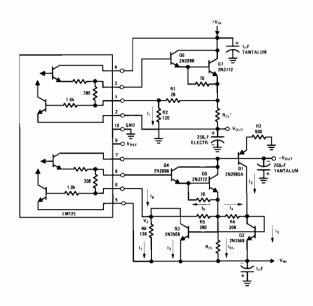

For applications requiring more supply current than can be delivered by the basic regulator, an external NPN pass transistor may be added to each regulator. This will increase the maximum output current by a factor of the external transistor beta. The circuit for current boosted operation is shown in Figure 10.

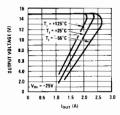

FIGURE 9. Internal Current Limiting Characteristics

FIGURE 10. Boosted High Current Regulator

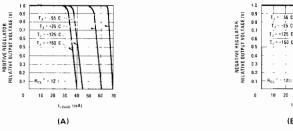

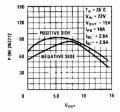

In the boosted mode, current limiting is often a necessary requirement to insure that the external pass device is not overheated or destroyed. Experience shows this to be the usual cause of IC regulator failure. If the regulator output is grounded the pass device may fail and short, destroying the regulator. To limit the maximum output current, a series resistor ( $R_{\rm CL}$  in Figure 10) is used to sense load current. The regulator will current limit when the voltage drop across  $R_{\rm CL}$  equals the current limit sense voltage found in Figure 11. Figure 12 shows the external current limiting characteristics unboosted and Figure 13 shows the external current limiting characteristics in the boosted mode.

To ensure circuit stability at high currents in this configuration, it may be necessary to bypass each input with low inductance, tantalum capacitors to prevent forming resonant circuits with long input leads. A C  $\geq$  1µF is recommended. The same problem can also occur at the regulator

output where a  $C \geq 10 \mu F$  tantalum will ensure stability and increase ripple rejection.

FIGURE 11. Current Limit Sense Voltage for a 0.1% Change in Regulated Output Voltage

The 2N3055 pass device is low in cost and maintains a reasonably high beta at collector currents up to several amps. The devices 2N3055 may be of either planar or alloy junction construction. The planar devices, have a high  $f_{\rm T}$  providing more stable operation due to low phase shift. The

alloy devices, with f<sub>T</sub> typically less than 1.0 MHz, may require additional compensation to guarantee stability. The simplest of compensation for the slower devices is to use output filter capacitor values greater than  $50\mu F$  (tantalum). An alternative is to use an RC filter to create a leading phase response to cancel some of the phase lag of the devices. The stability problem with slower pass transistors, if it occurs at all, is usually seen only on the negative regulator. This is because the positive regulator output stage is a conventional Darlington while the negative output stage contains three devices in a modified triple

Darlington connection giving slightly more internal phase shift. Additional compensation may be added to the negative regulator by connecting a small capacitor in the 100 pF range from the negative boost terminal to the internal reference. Since the positive regulator uses the negative regulator output for a reference, this also offers some additional indirect compensation to the positive regulator.

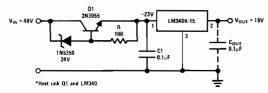

#### 7 AMP REGULATOR

In Figure 14 the single external pass transistor has been replaced by a conventional Darlington

> 30 60

(B)

hoap (mA)

20 40

FIGURE 12. External Current Limiting Characteristics- Unboosted

FIGURE 13. External Current Limiting Characteristics- Boosted

FIGURE 14. High Current Regulator Using a Darlington Pair for Pass Elements

using a 2N3715 and a 2N3772. With this configuration the output current can reach values to 10A with very good stability. The external Darlington stage increases the minimum input-output voltage differential to 4.5V. When current limit protection resistor is used, as in Figure 14, the maximum output current is limited by power dissipation of the 2N3772 (150W at 25°C). During normal operation this is  $(V_{\rm IN}-V_{\rm OUT})$   $I_{\rm OUT}$  (W), but it increases to  $V_{\rm IN}$   $I_{\rm SC}$  (W) under short circuit conditions. The short circuit output current is then:

$$I_{SC} = \frac{P_{MAX} (T_C = 25^{\circ}C)}{V_{1N}}$$

$$= \frac{150W}{20V (min)} = 7.5A \text{ max.}$$

$I_{L}$  could be increased to 10A or more only if  $I_{SC} \le I_{L}$ . A foldback current limit circuit will accomplish this. The typical load regulation 40 mV from no load to a full load. ( $T_{j} = 25^{\circ}\text{C}$ , pulsed load with 20 ms  $t_{ON}$  and 250 ms  $t_{OFF}$ .)

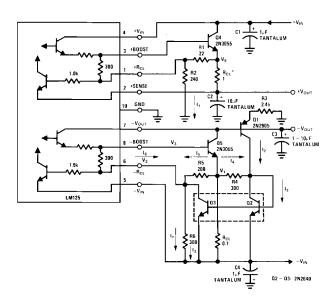

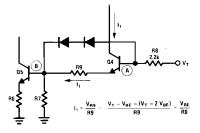

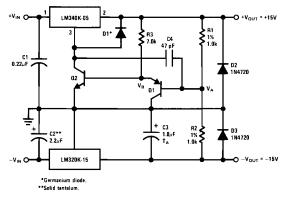

#### FOLDBACK CURRENT LIMITING

In many regulator applications, the normal operation power dissipation in the pass device can easily be multiplied by a factor of ten or more when the output is shorted. This may destroy the pass device, and possibly the regulator, unless the heat sink is oversized to handle this fault condition. A foldback current limiting circuit reduces short circuit output current to a fraction of the full load output current thus avoiding the

need for larger heat sink. Figure 15 shows a foldback current limiting circuit on both positive and negative regulators.

The foldback current limiting, a fraction of the output voltage must be used to oppose the voltage across the current limit sense resistor. Current limiting does not occur until the voltage across the sense resistor is higher than this opposing voltage by the amount shown in Figure 11. When the output is grounded, the opposing voltage is no longer present so current limiting occurs at a lower level. This is accomplished in Figure 15 by using a programmable current source to give a constant voltage drop across R5 for the negative regulator, and by a simple resistor divider for the positive regulator. The reason for the difference between the two is that the negative regulator current limiting circuit is located between the output pass transistor and the unregulated input while the positive regulator current limiter is between the output pass transistor and the regulated output.

The operation of the positive foldback circuit is similar to that described in NSC application note AN-23. A voltage divider R1 and R2 from  $V_{\rm E}$  to ground creates a fixed voltage drop across R1 opposite in polarity to the drop across  $R_{\rm CL}^+$ . When the load current increases to the point where the drop across  $R_{\rm CL}^+$  is equal to the drop across R1 plus the current limit sense voltage given in Figure 11, the positive regulator will begin to current limit. As the positive output begins to drop, the voltage across R1 will also decrease so that it now requires less load current to produce the current limit sense voltage. With

FIGURE 15. Foldback Current Limiting Circuit

the regulator output fully shorted to ground ( $+V_{OUT}=0$ ) the current limit will be set by the value of  $+R_{CL}$  alone.

If

$$\frac{I_{FB}}{I_{SC}} \le 5$$

then the following equations can be used for calculating the positive regulator foldback current limiting resistors.

$$R_{CL}^{+} = \frac{V_{SENSE}}{I_{SC}} \tag{1}$$

where  $V_{\text{SENSE}}$  is from Figure 11.

At the maximum load current foldback point:

$$V_{RCL}^{+} = I_{FB} R_{CL}^{+}$$

(2)

$$V_{R1} = V_{RCL}^{+} - V_{SENSE}$$

(3)

$$V_{B1} = I_{EB} R_{CI}^{+} - V_{SENSE}$$

(4)

Then

$$R1 = \frac{V_{R1}}{I_1} \tag{5}$$

and

$$R2 = \frac{+V_{OUT} + V_{SENSE}}{I_1}$$

(6)

The only point of caution is to ensure that the total current ( $I_1$ ) through R2 is much greater than the current contribution from the internal  $300\Omega$  resistor. This can be checked by:

$$\frac{I_{FB} R_{CL}^{\dagger}}{300} << I_1 \tag{7}$$

Note: The current from the internal  $300\Omega$  resistor is  $V_{3.1}/300\Omega$ , but  $V_{3.1}=V_{BE}+V_{RCL}-V_{SENSE}^+$  assuming  $V_{BE}\approx V_{SENSE}^+$  at the foldback point,  $V_{3.1}\approx V_{RCL}^+=I_{FB}\,R_{CL}^+.$

Design example: 2 amp regulator LM125 positive foldback current limiting (see Figure 15).

Given:

V<sub>SENSE</sub> (See Figure 11)

$$\theta_{AA} = 150^{\circ} \text{C/W}$$

$$T_{\Lambda} = 50^{\circ} C$$

With a beta of 70 in the pass device and a maximum output current of 2.0A the regulator must deliver:

$$\frac{2A}{\beta} = \frac{2A}{70} = 29 \text{ mA}$$

The LM125 power dissipation will be calculated ignoring any negative output current for this example.

$$P_{LM125} = (V_{IN} - V_{OUT}) I_{OUT}$$

= (25 - 15) 29 mA

= 290 mW

$$T_{RISE} @ \theta_{JA} = 150^{\circ} C/W = 150^{\circ} C \times 0.29 = 44^{\circ} C$$

$$T_{J} = T_{A} + T_{RISE} = 50^{\circ} C + 44^{\circ} C = 94^{\circ} C$$

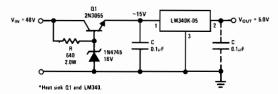

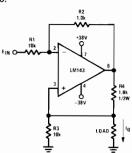

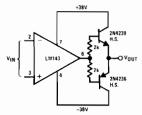

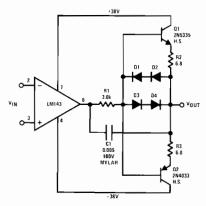

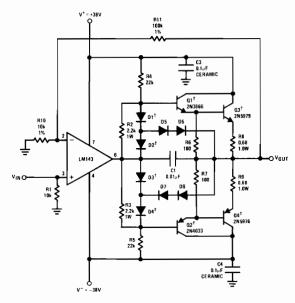

From Figure 11: